Page 1

DiVA

DV79 DVD Player

Service

Manual

Issue 1.0

ARCAM

Bringing music & movies to life

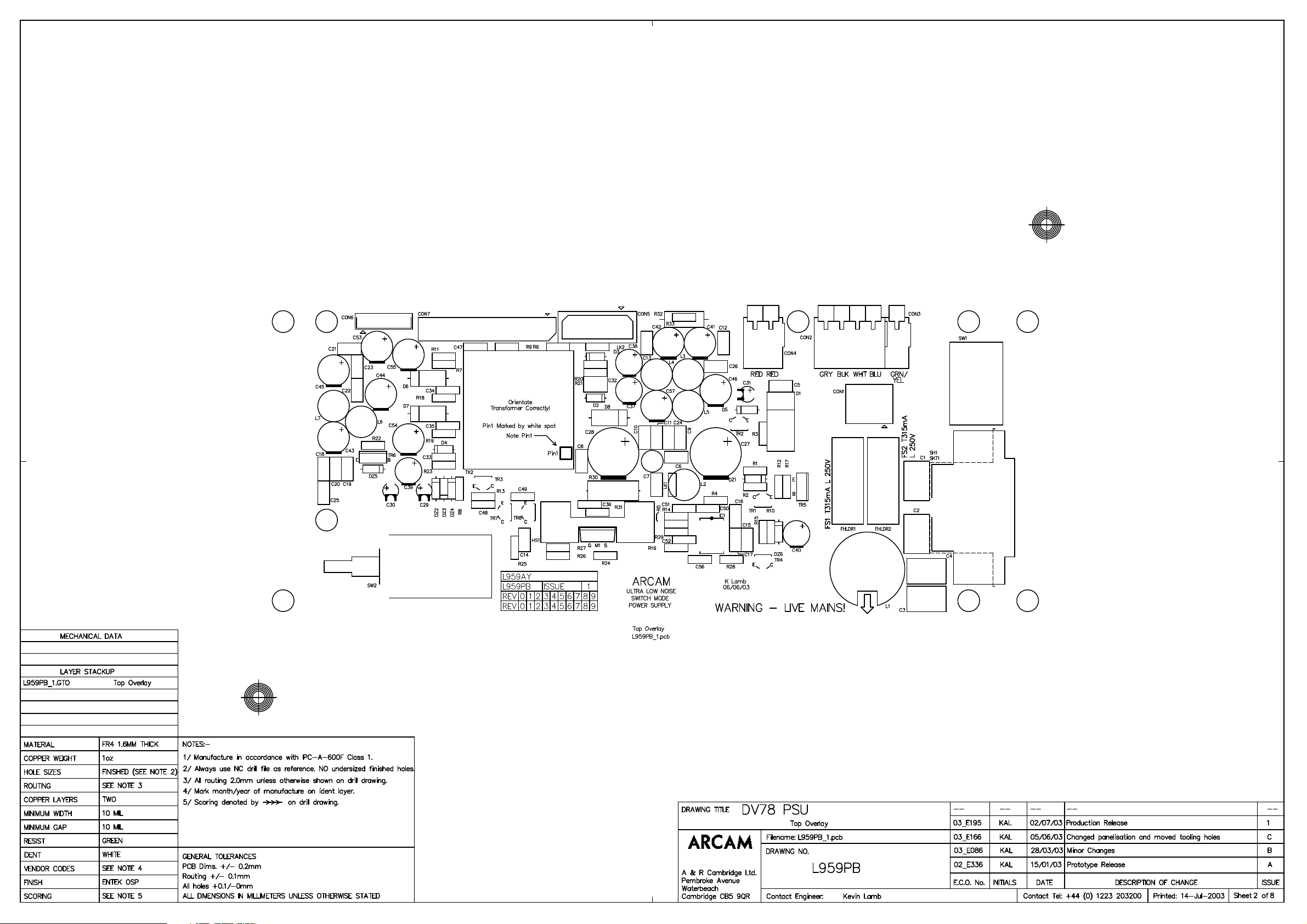

Page 2

DV79

Contents List

Circuit Description

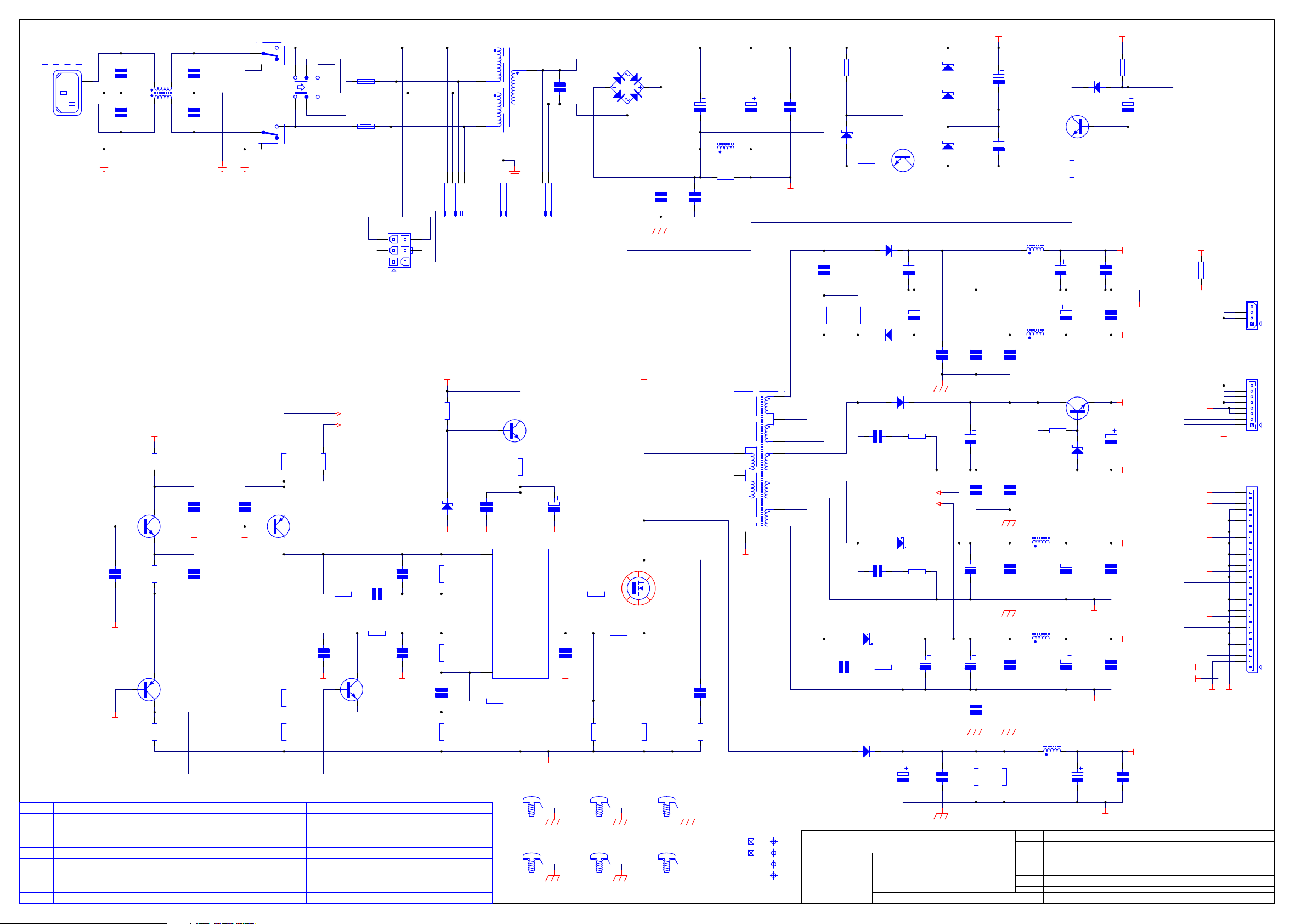

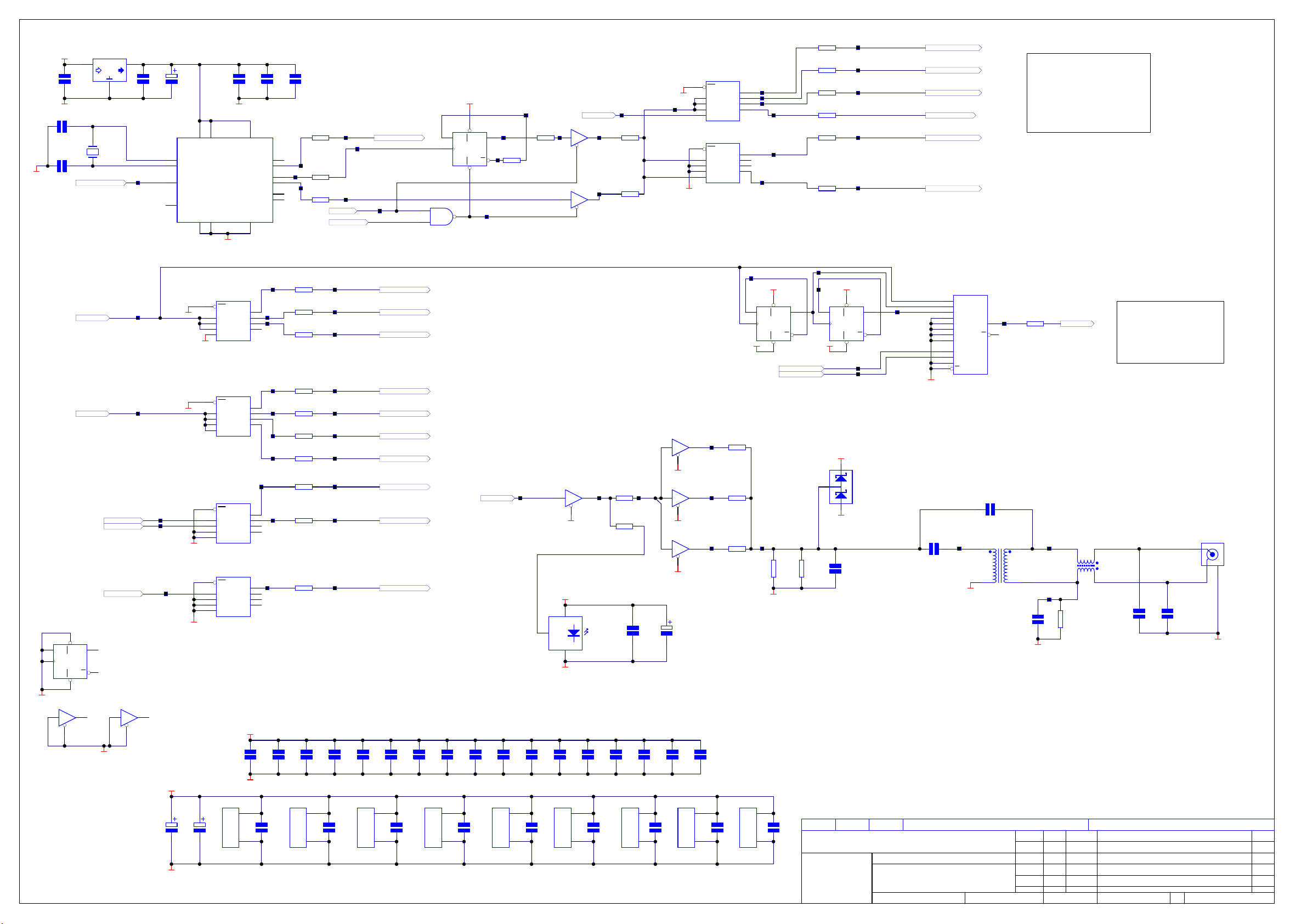

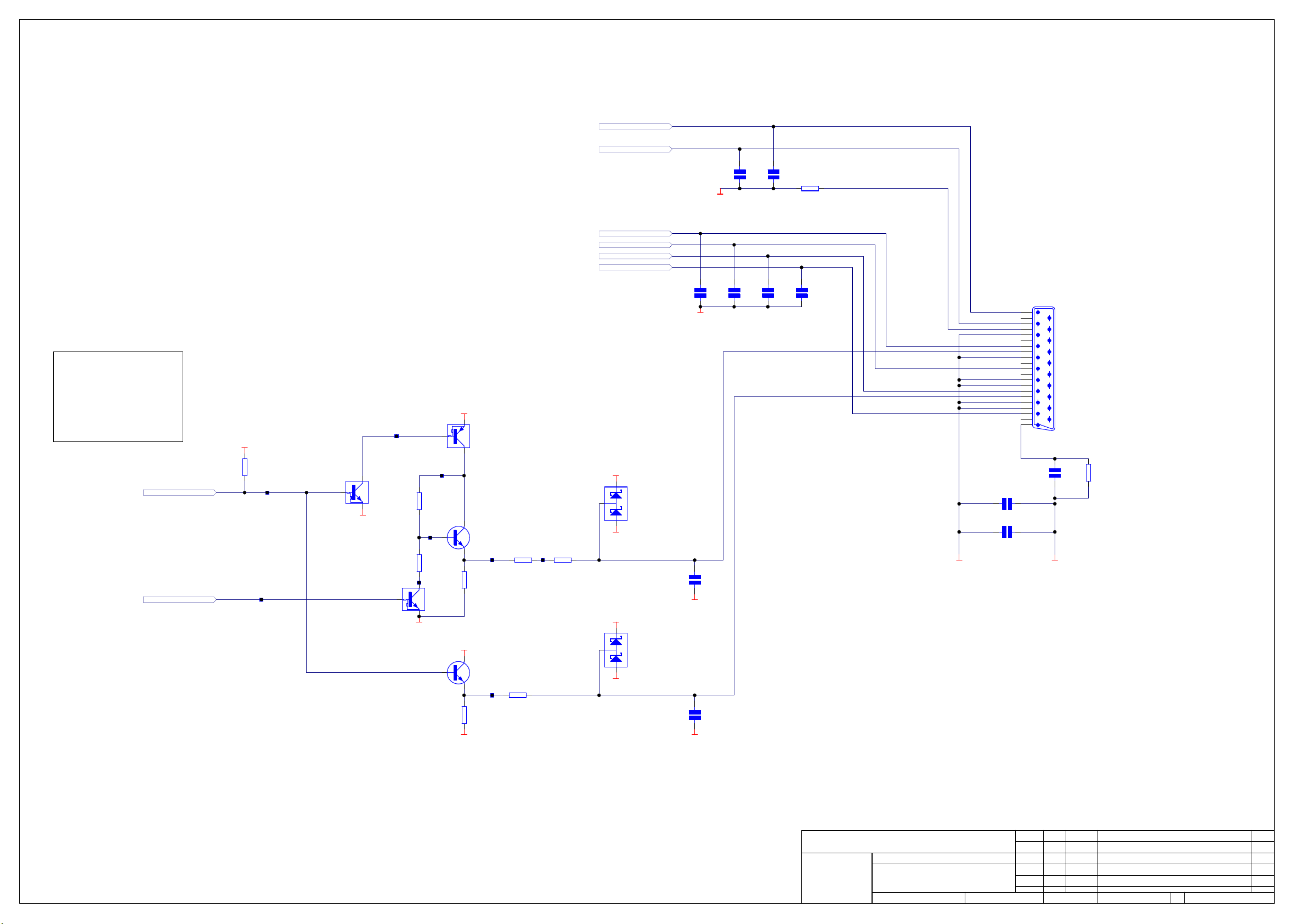

Power Supply L959AY

! CCT diagram

! Component layout diagram

! Parts list

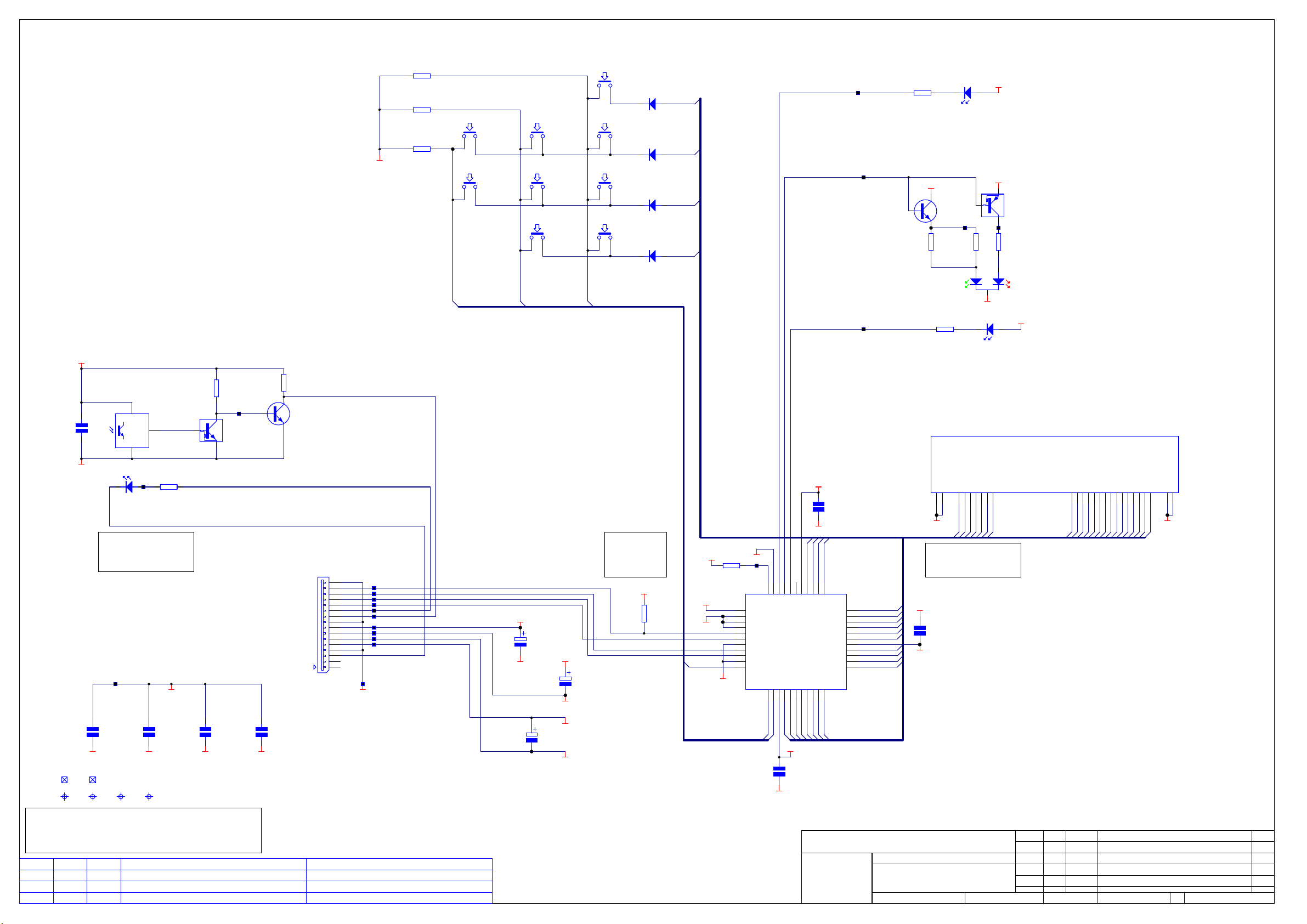

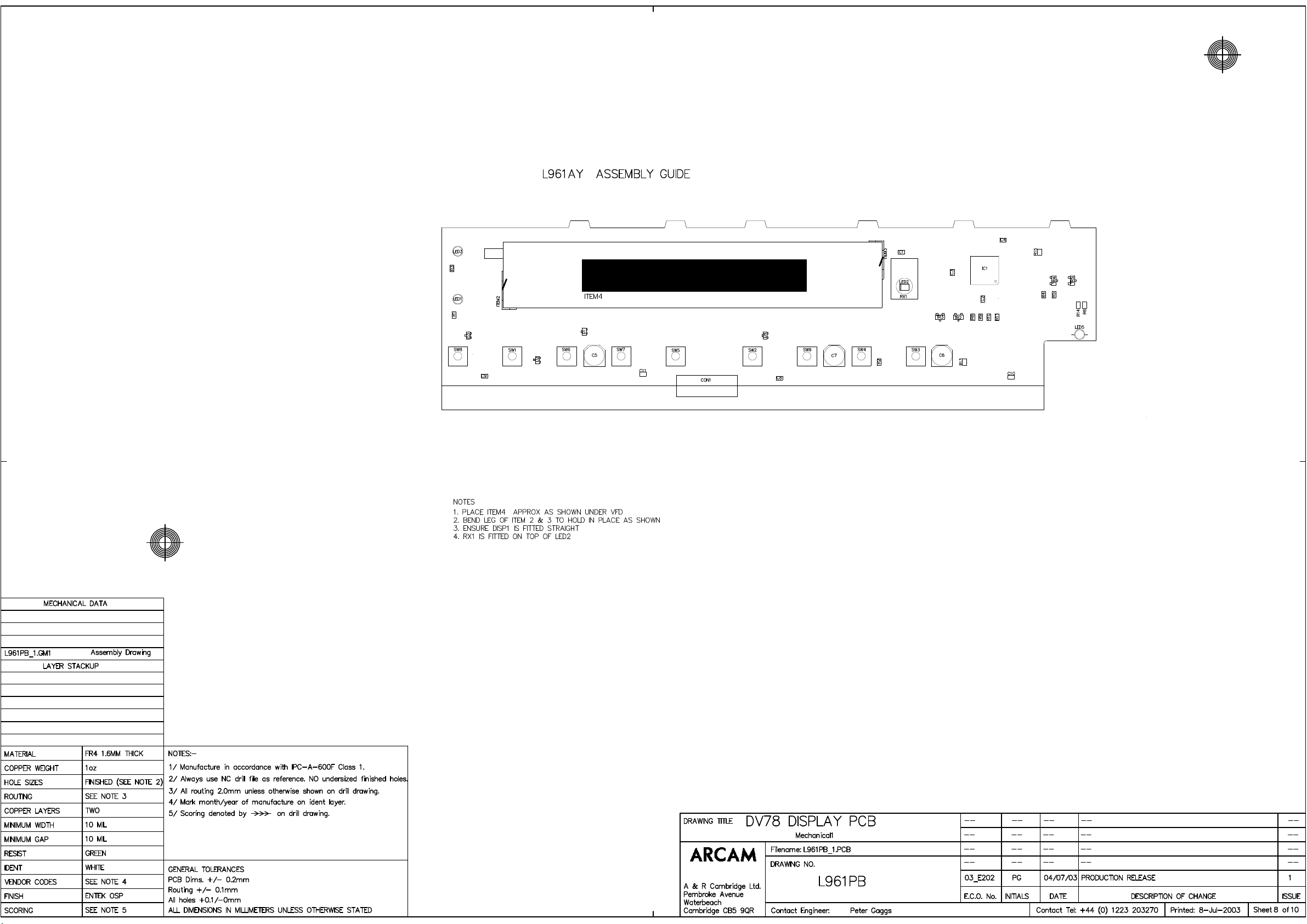

Display Board L961AY

! CCT diagram

! Component layout diagram

! Parts list

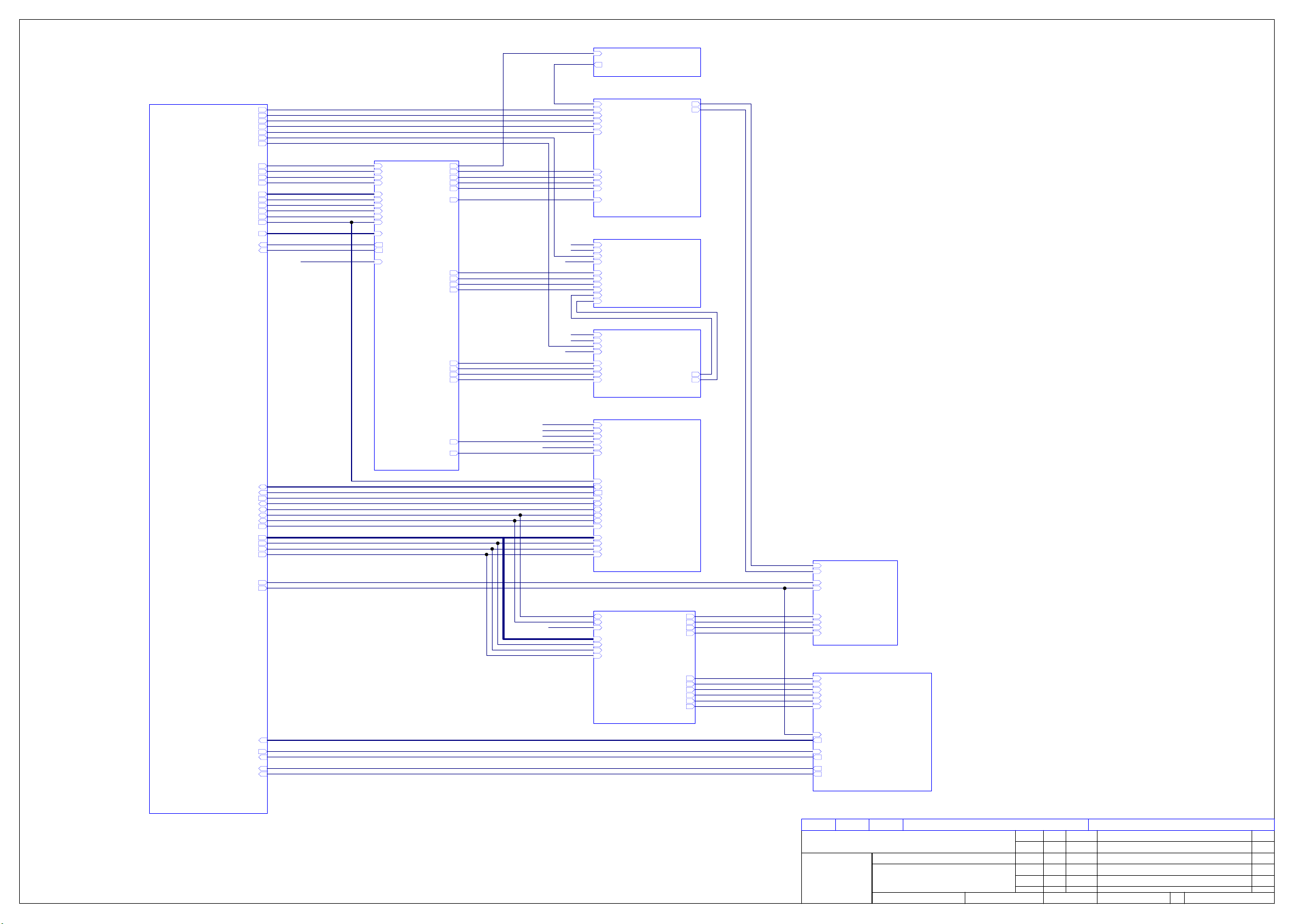

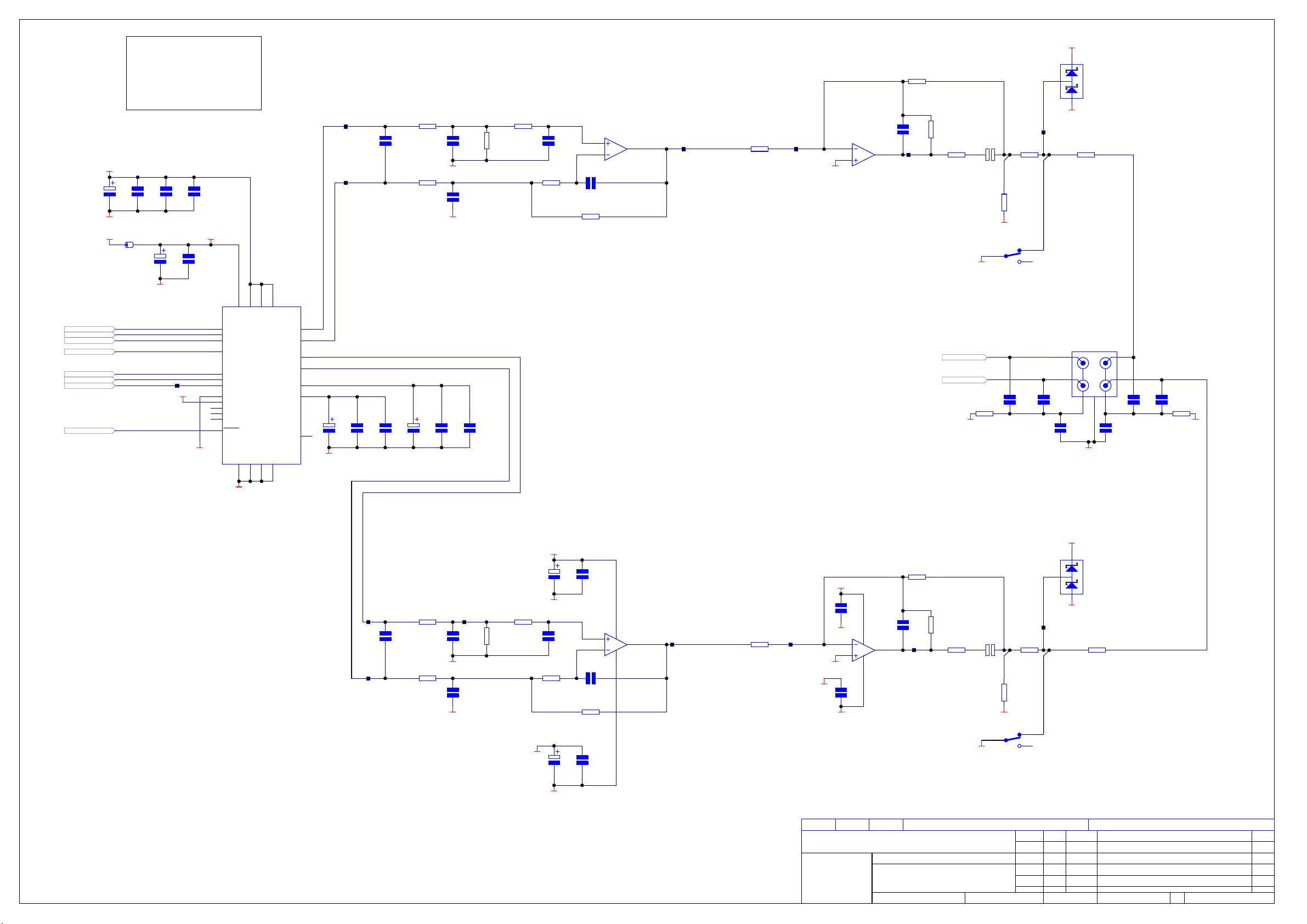

Main Board L967AY (for serial numbers below D79V03175)

! CCT diagram

! Component layout diagram

! Parts list

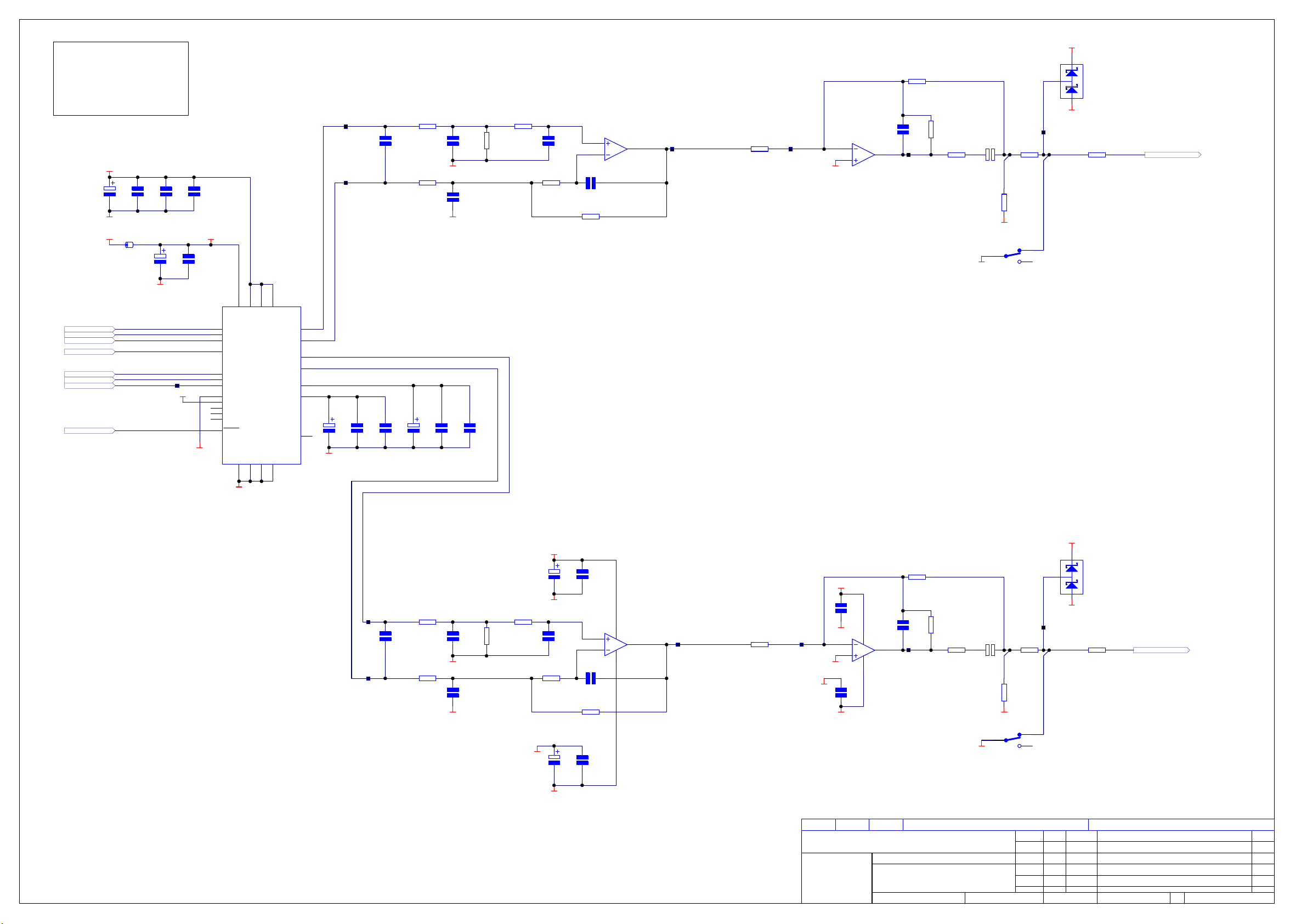

Main Board L974AY (for serial numbers above D79V03174)

! CCT diagram

! Component layout diagram

! Parts list

Transformers

! L924TX

! L925TX

Mechanical Assembly

! Exploded view diagram

! Mechanical and packing part list

Page 3

Diva Dv79 Circuit description.

Overview

DiVa DV/79

The

and only shares it power supply board and display

board with the

The player is based around acclaimed

V

chipset coupled to high specification

converters for all six audio output channels and a

extremely high quality digital video encoder also

featured in this design is a HDMI output digital Video.

Power supply board.

Non-switching

Mains power arrives at

filtered by EMC choke LI and Y caps C3 and C4,

mains switch SW2a/b switches both Negative and Live

phases before the power reaches the mains select

switch at location SW1 the switch allows the primary

windings of the transformer TX1 to be wired in either

Parallel or Series configuration.

The Bridge rectifying Diode package at location D1

forms the basis of the conventional power stage and

supplies a VN35V6 (-35.6v) to the Switch mode

stage, transistor

DZ1

and allows for the series Zener diodes DZ2, DZ3,

DZ3 to supply the VN13V5 and VN19V rails.

We will also see a simple A.C present circuit this is

used for delayed output relay operation and fast relay

closure under interrupted supply conditions thus

preventing power down op-amp offsets from reaching

the Audio output sockets.

Switch mode

The switch mode supply is formed around the

Driver/Control chip

mode). The chip is referenced the –36.5V supply line

and the Digital ground DGND, the supply for the chip

is formed by the 12v Zener at location

seen on Pin 7 as VCC. The power supply allows for

the switch-mode to be tied the to Audio sampling

frequency for any given compatible format

is a completely new design platform

DV78

.

Zoran Vaddis

Wolfson

IEC

inlet socket

TR1

is biased by 2v7 Zener diode

IC1

UC3843 (used in regulating

SKT1

DZ6

D to A

and is

and can be

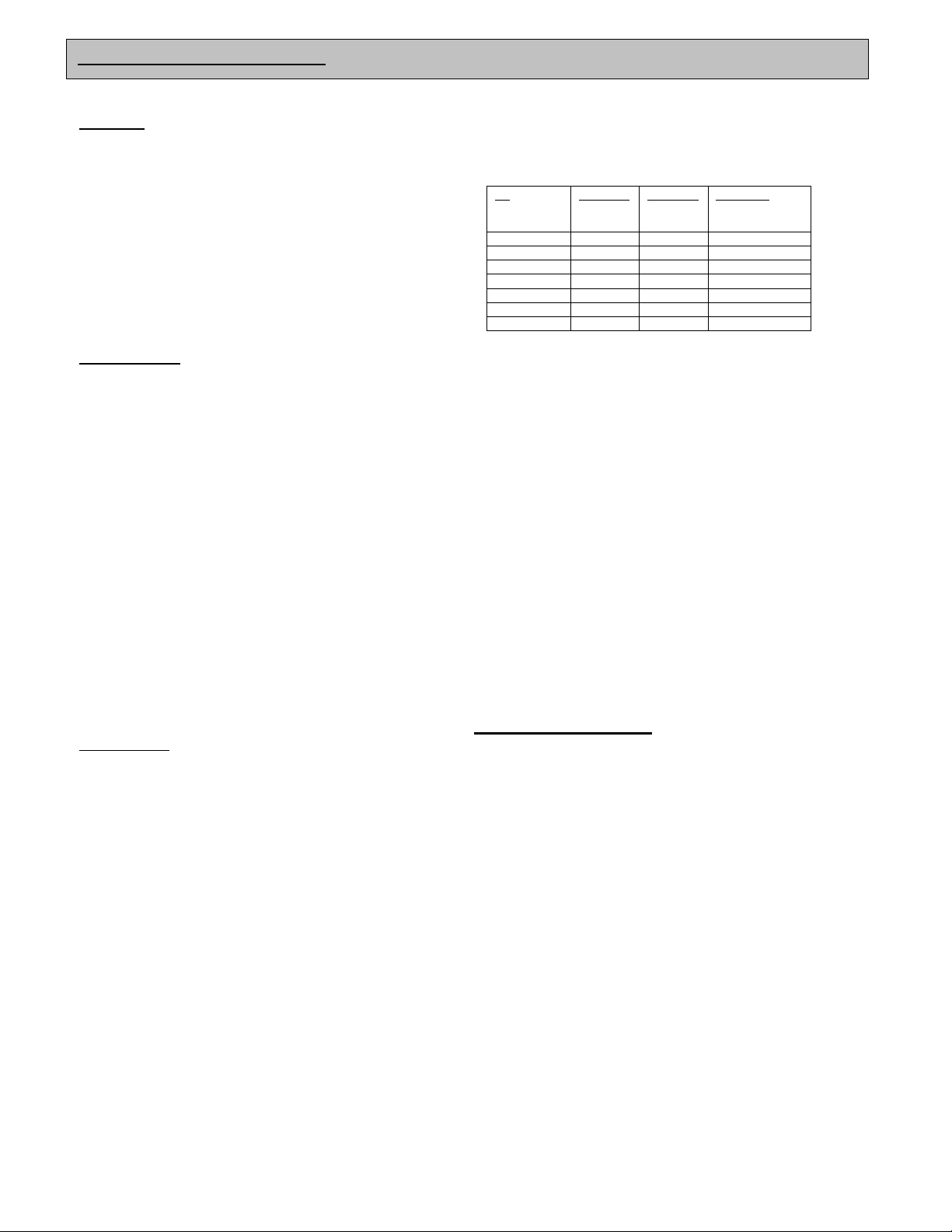

see Fig 1

.

Fig 1 PSU clock control

Fs

Frequency

select

44.1 kHz 0 0 44.1 kHz

48 kHz 0 0 48 kHz

88.2 kHz 0 1 44.1kHz

96 kHz 0 1 48 kHz

176.4 kHz 1 0 44.1 kHz

192 kHz 1 0 48 kHz

Others 1 1 OFF

PSUFS1

Pin 11

IC305a

PSUFS0

Pin 12

IC305a

PSUCLK

Output Pin 5

of IC305a

The PSU sync signal is driven into the power supply via

Resistor R9 if no Sync is present the unit is set to free run at

xxxx due to the RT/RC network attached to Pin 4.

IC1

is running in regulated mode and monitors the voltage

output on the +5V and +3V3 D.C lines, the two voltages are

summed by TR8 and Driven into the VFB and Comp inputs

of IC1, the Voltage is then regulated by changing the time

base of the PWM output at pin 6 (longer the time base the

lower the voltage), the PWM switching frequency is driven

into the switch-mode transformer by the high speed Nmos

device at position M1, R5 is used to sense the Current

across the gate of the Nmosfet and in the event of a short

circuit will safely shut the power supply down. We derive the

12v Mech supply from the output of M1 using the Ultra-fast

Diode at location D8 to rectify the

PWM line

.

The D.C outputs from the switch mode have extensive

switch mode noise removing filters these are seen as 100n

caps down to ground and Wire wound inductors in series

with the supply rail.

Power supply main board

All the power supply rails are supplied to the main board via

the 32 way FFC conector at location

CON1001

.

Digital

The

supplies from the switch mode stage of the

power supply arrive as 3V3D, +5VD and +12VD we also see

the Display board power supplies arrive as –19V, -9 and

–13.5V all of the supplies have a second stage of

implemented on the board to remove all traces of ultra-sonic

noise.

The 3V3D rail is the main 3V3 rail used to power the digital

circuitry; +5VD is used for all 5v Digital/Video supplies the

+12VD is used for Scart switching and to power the HDMI

circuit.

The 1V8 rail is derived from the 3V3 rail and is regulated by

the adjustable regulator at location

REG1003

.

Page 4

Analogue

The

as +15V3 and –15V3 rails these are filtered L1002 and

L1015 before being regulated by the adjustable

regulators at locations

provide +/- 12V rails for the Analogue output stage.

Regulator

forms the Audio DAC supply.

The Display board requires several supply voltages

these are simply passed through the main board,

being filtered on the way to prevent transmission of

noise through to the surrounding electronics. The

display takes the +5V, -19V, -13V5 and -9V the –13V5

and –9V form a floating 4.5V supply biased relative to

the –19V grid voltage.

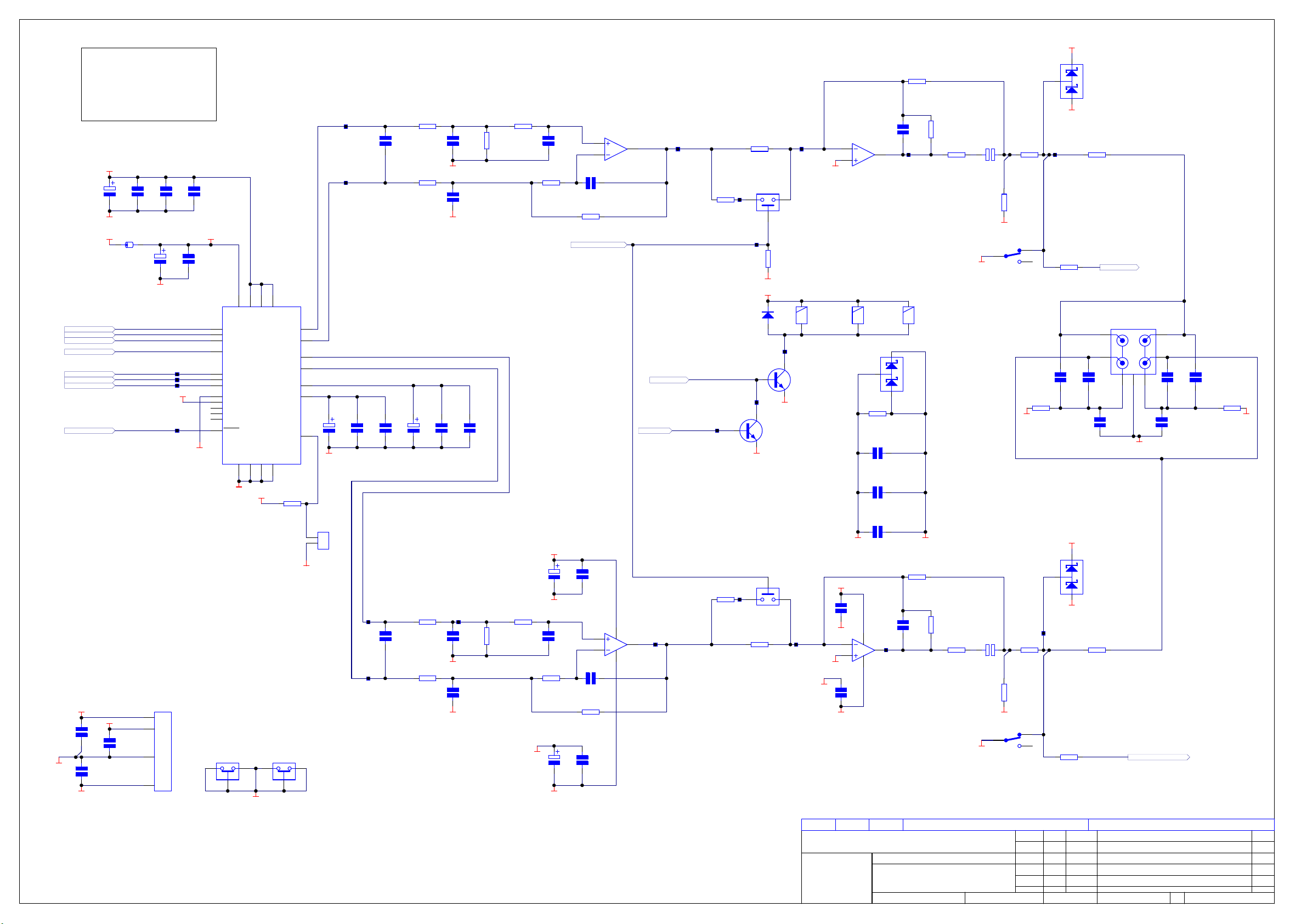

Display Board

The main component of the Display board is

a Vacuum Florescent Display driver with keyboard san

and a serial data in/out interface.

The Chip receives display drive serial data from the

Vaddis V

13 and 14 these will be seen a DIN, STS and CLK this

data is used to drive the VFD a

with the VADDIS V and supplies Keyboard Scan

information. The keyboard scan is a 6 x 4 matrix with

the Key Source appearing at S3, S4, S5, S6 and the

Keyscan

Please see:

Infra red

The

data and send the data to the Vaddis V on the main

board via transistors TR2 and TR3, LED 2 is used to

mix the rear panel RC5, this is covered in-depth within

the Coms and Video output section of this guide.

supply stages arrive at the main board

REG1000

REG1001

chip on the main board via Con1 on pins 12,

data returns appearing a K2, K3 and K4.

above for

is fed from the +15V3 rail and

power supply

pick-up at location RXI receives RC5

REG1002

and

DOUT

line interfaces

information.

IC1

to

this is

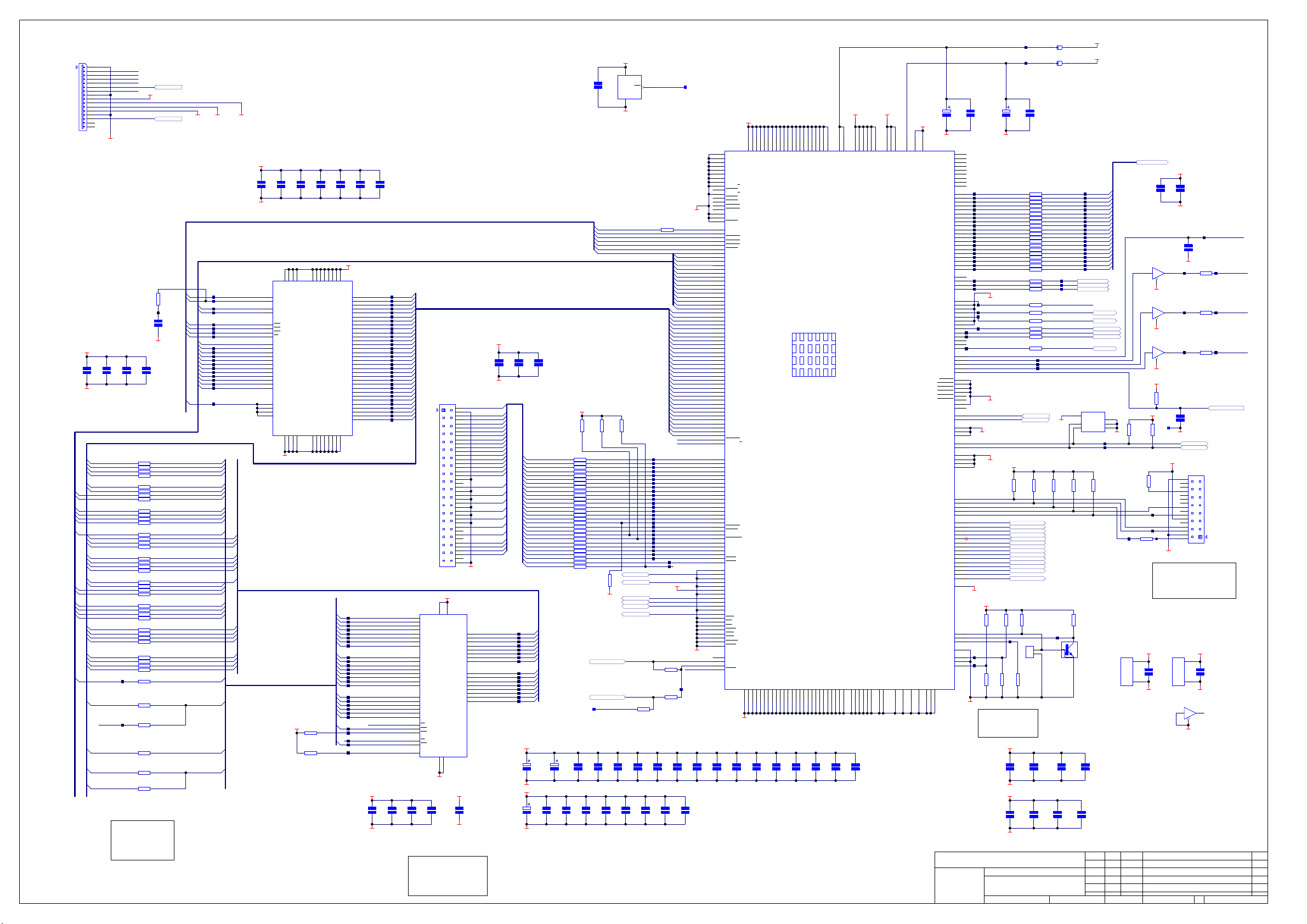

Main Board electronics.

Zoran Vaddis V.

The main processor/control chip on the main board is the

Zoran Vaddis V at location

incarnation of the very popular Vaddis range of processors

and allows for a much lower component count when

compared to our earlier players as many of the playback

functions have moved onto the Vaddis V silicon.

Below you will see the

o 20 Bit digital video output for external Video

DAC’s and HDMI output stage.

Decoded Analogue Video output (internal

o

DAC) used on the DV78 only.

o Digital Audio output 3 data lines 6 channels for

internal L + R DAC’s and L + R + C + LS + RS

for DV79 and DV29 also used for HDMI for the

DV79 and DV29.

SPDIF output.

o

o Internal display interface.

Internal ATAPI interface.

o

o Internal IR interface.

Serial in/out for RS232

o

A more detailed explanation of the Vaddis V and

peripheral components follows.

Vaddis Power

The Vaddis V is powered by two separate supplies the

Vaddis requires a 1.8v supply for the core, this is regulated

from the 3.3v rail by

supply power to the I/P – O/P ports of the chip.

ATAPI interface

CON203

connector. This is decoupled from the Drive via an array of

decoupling resistors as required by the ATAPI spec.

is an ATAPI interface on a 40 way IDE

IC202

major functions

REG1003

, the 3.3v rail is used to

, this is the latest

of the Vaddis V

Page 5

Display Board interface

The display board interface is on the 16 way FFC flexi

foil connector at location CON202. Power for the

display also travels on the connector. There are 4 –

wires to interface with the VFD driver chip these are

seen as.

XFPDIN - Data to the display board

o

o FPDOUT - Data from the display board

o XFPCLK - Clock

o XFPSEL - Chip select

The above control lines are level shifted to 5v logic

from 3.3v levels by

IC200

(74HCT125) these are the

levels required by the VFD drive chip.

The IR output from the Display board arrives as

IRRCV

this is an open collector signal, which can be

wire-Ord with the re-panel remote input.

Digital Audio

The Digital audio leaves the chip 3 sets of data lines

labelled as.

o ADAT0 - Left and Right channel data

o ADAT1 - Left and Right surround

ADAT2 - Centre and Sub

o

Along with the ADAT line we will also see the

ALRCK

and

as required for IS2 data conversion.

ABCLK

The Vaddis V also supplies a direct SPDIF output for

interfacing with ancillary processing equipment.

Digital Video

The Digital Video output from the Vaddis V consists of

the following signals:

o VIDPO to 19 - 20 Bit wide digital video data

o CLK_27M - 27 Mhz Video clock

o VSYNC - Vertical sync

HSYNC - Horizontal Sync

o

The 20 bit wide bus

VIDP0

to 19 provides video data

as follows.

Interlaced video mode: VIDP0 to 7 provide

multiplexed 8 bit Y, Cb and Cr data with VIDPO being

the Isb.

Progressive scan video mode: VIDP0 to 9 provide

10 bit multiplexed Cb, Cr data with VIDP0 being the

VIDP10 to 19

Isb.

being the Isb.

provide 10 bit Y data with VIDP10

Flash/ SDRAM

IC203

is a 64Mbit (32 bit x 2Meg) SDRAM. It runs at

135MHz

IC205

is a 16Mbit (16 bit x 1Meg) intel type flash IC for

program storage (Player software).

The flash interfaces to the Vaddis V using the SDRAM bus

it may appear that the bus connects to the flash in a

random manner, however this is simply because the

Vaddis bus is multiplexed that way. The Flash will be

accessed at power up and the contents are copied to the

SDRAM the program will then be run from the SDRAM.

Series resistors are employed to isolate the flash bus from

the main SDRAM bus.

EEPROM

IC204 is a 8kBit (1K x 8) Serial EEPROM. This is used for

storage of non-volatile storage of player settings, region

settings and bookmark data.

Clocks

CLK27MV

is the 27Mhz clock for video. It is used to

generate the 135Mhz clock for the Vaddis microprocessor

and DSP. The MCLKV is the audio master clock for the

Vaddis.

We run the Vaddis in

PLL bypass

mode and generate or

own master clock (see main clock section of manual) for

higher accuracy and improved performance across Audio

and Video.

RESET

IC201

is a reset generator chip that monitors the +3.3V rail

and ensures a reset signal PWR_ON_RESET* is

generated on power up, or if the mains power dips below

an operational level.

This signal is used to reset the Vaddis V and Flash micro

only. The Vaddis V line labelled as RESET* resets the

remaining circuitry of the player apart from the HDMI chip,

this has it’s own reset line labelled as HDMI_RESET this is

necessary if we require to reset the HDMI chip only (for

example when the HDMI sink is connected and then

disconnected).

Serial Port

The VADDIS V can interface with the external world via

the RS232 connector at location CON900 and the RS232

Transceiver at location IC900, the serial data lines are

shown as SERIAL RX and SERIAL TX these lines allow

for direct control over the unit via RS232.

Page 6

O/P

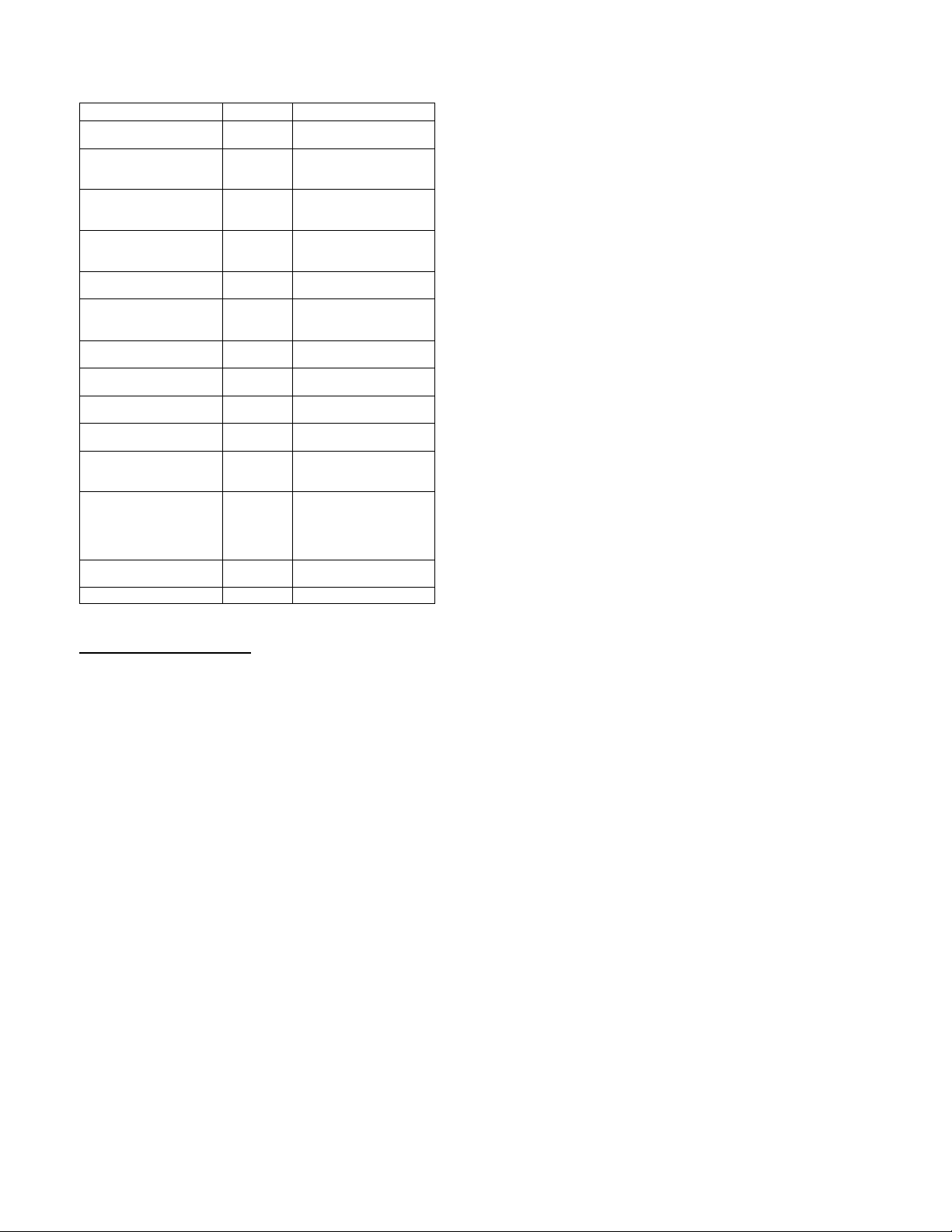

Fig 2. GPIO control signals from the Vaddis V

Single Name I/P-

PSUFSO-1 Output

ENABLE_AV Output

16/9 Output

9190INT* Input

GAIN_SCALING Output

ML_8740_0-2 Output

MC Output

MD Output

FSELE0-1 Output

MUTE* Output

DDC_SDA,DDC,SCL I/O

PROG_INT* Output

HDMI_RESET* Output

RESET* Output

Function

Control PSU Clock

divider

SCART control High

in normal operation

and low in standby

Scart 16/9

anamorphic control

line

Interrupt signal

from SII9190 HDMI

transmitter

High for HDCD gain

scaling

SPI load signal for

Audio DACs 0,1 and

2 (see note 1)

SPI clock signal for

DAC control

SPI data signal for

DAC control

Frequency select

generator

Active low audio

mute signal

12C bus for DDC

channel on HDMI

interface

High for Progscan

mode, Low for

interlaced mode.

Controls Sil9130

data mux

Reset signal for

HDMI transmitter

System reset

Clocks and SPDIF stage.

IC300 is a SM8707E clock generator IC. This IC is

sensitive to noise on it’s power supply, which causes

clock jitter for this reason we have a independent Low

dropout – low noise

+3v3

power supply for the chip

based around the regulator at location REG300.

X300

is a

27Mhz

crystal that

IC300

uses to generate

all the video and audio clocks required by the system

the crystal sits on the XTI and XTO pins of the chip,

the 27Mhz output at Pin 4 (MO2) is used to drive the

Vaddis chip directly bypassing the internal PLL.

The frequency of the audio master is dependent on

the on the current audio sample rate (I.e the sample

rate required by the format CD=44.1Khz and

DVD=48khz etc) and this is set by the system micro

via the FSLO and FSEL1 this selects either the

22.5792Mhz

IC300 this may then be divided by 2 by the clock

divide chip at location IC306 depending on the status

24.576Mhz

or

clock from frequency from

of FSEL1. Therefore 4 clock frequencies may be

obtained to support all required audio samples rates.

Nand gate

IC303 is used to gate

FSEL1

with

ENABLE_AV (which is low in standby mode) as such

when in standby mode the audio clock is disabled.

Clock Buffer

IC301

us used to buffer the audio master clock. The circuit

is arranged so that each device that requires the audio

master clock has it’s own driver these are seen as.

o MCLK_DAC0 - Pin 18

o MCLK_DAC1 – Pin 16

MCLK_DAC2 – Pin 14

o

o MCLK_VADDIS – Pin 3

o MCLK_HDMI – Pin 9

We also run the

Mute Line

from the Vaddis V

IC301

this

can be seen on Pin 12 and drives transistor TR401, the

transistor pulls the relays

RLY400, RLY500, RLY600

to

ground and un-mutes the audio outputs.

IS2 Audio Data

IC302

and

IC309

are buffers for the 12S signals these

ensure that the signals travelling to the DAC’s are point to

point. IC302 deals with the ALRCK and ABCLK and

C309

I

ADAT0,1,2

the

all signal are split into three

separate lines for the three stereo DACS.

PSU Clock Divider

IC304

the PSU clock is always either 44.1kHz or 48Khz (

and

IC305

form a clock divide by 1, 2 or 4 to ensure

See fig

1 within the power supply description section).

This circuit will also switch the

PSUCLK

off when

switching between sample rates (the PSU will free run

when the PSUCLK is not present).

SPDIF Output

The SPDIF output consists of

IC308

implemented as a

inline buffer and parallel output buffer. Gate A buffers the

signal so that the SPDIF line from the VADDIS sees fewer

loads and form a feed to the Optical output transmitter,

gates B,C and D drive the SPDIF in parallel so that we can

drive a 75ohm load adequately. The resistors at the output

of IC308 are arrange so that the output will be

pk

when the output is terminated with a 75 ohm load at the

500mV pk-

same time the output impedance of the circuit is 75ohms

as required by the Sony Philips Digital Interface

specification, C315 provides AC coupling and L301

provides common mode noise rejection for EMC

performance.

Page 7

Left and Right channel D to A stages

Wolfson WM8740

The

and a +3V3 supply along with the Digital Audio data

lines already described in this guide.

Left channel output only

The

section as all audio output stages are the identical (all

six channels of a DV79) apart from the HDCD gain

switching for L + R only.

IC400B

Bessel filter with a differential input and a gain of 1 this

follow by a output buffer IC401B, the gain of IC401B is

control by the switching chip at location

normal use the Gain of IC401B is set to 1.1 but in

HDCD

in parele with R413 and the gain is set to 2.2 allowing

for the higher audio output required by the HDCD

standard.

C436 is a A.C coupling capacitor used to remove the

few mV of offset that the DAC produces, D400

provides protection against from ESD.

The all output relays are under control of the Vaddis

V chip but will also mute the outputs instantly under

mains failure conditions. Switching drive is provided

by TR401 (MUTE_BUF) and TR400 (AC_PRES) the

relays are in mute mode if either the input to TR401 is

Low or if the input to TR400 is high.

Please note:

outputs of the left/right audio stages.

Video Encoder

The video encoder at location IC703 is an Analogue

devices

interlaced and progressive scan video. It runs on a

2.5V supply provided by REG700 the voltage

reference for the chip of 1.225V is provided by

REF700 and should be seen on Pin 46. C730-731 and

R736 form an external PLL filter.

The Data lines into the encoder arrive as VIDP0 – 19

from the outputs of the VADDIS V chip.

The external current setting resistors for the internal

DACS are seen as R721-R722 and R738-R739 these

set the correct output level for the DACS.

The encoder gives out

S-Video (Y and C) and shared YUV/RGB signals. The

setting of the RGB or YUV mode is select with the

Video settings page of the Setup menu.

and associated components for a 2nd order

mode the

The

ADV7310

stereo DAC requires +5V(A)

will be described in this

IC402

IC402

switches a second 10k resistor

Scart

left/right audio is fed from the

video encoder, supporting

6 video signals

, for composite,

, in

six analogue output

The

o DAC_A = Composite

o DAC_B = SVID Y

DAC_C = SVID C

o

o DAC_D = Y or Green

o DAC_E = U or Blue

o DAC_F = V or Red

Please note: When the player is in Progressive scan

mode the composite and S-Video signals will be

switched off.

The Video outputs from IC703 are filtered by six identical

filters. For instance if we look at the Composite stage we

will see a very slow roll off filter comprising of C719,

C721 with L701 and L703 the

stage is around 40Mhz, resistors R700 and R702 form a

load for the current output DAC and as such set the

relative output level.

The outputs are driven by the Video op-amp at location

IC700A

75ohm resistor,

These signals now travel to the COMMS and Video

extension card on Con 901.

page 7.

SCART Output

RGB and Composite video signals as well as Left and

Right audio signals are all present on the SCART output

socket. As the RGB and YUV signals share the same

output port at the Vaddis V the player must be set to

RGB SCART

SCART.

RGB does not contain a Sync signal and the sync must

be taken from the Composite out (4 wire RGB).

Also present at the Scart are a number of control flags

for the monitor these include 2 GPIO control lines direct

from the Vaddis.

o

o 16/9

These are seen at the SCART output pins as.

o O/6/12

o RGB STAT

The 0/6/12 line (SCART pin 8) is used to inform the

monitor of the screen format being sent by the player as

set in the video set-up section of the software.

o

o 16:9 aspect ratio = 6V

o 4:3 aspect ration = 12V

The RGB status line (SCART pin 16) will be seen as 0v

= no RGB and >1v is RGB present.

this has a gain of

D701

operation to have a RGB output on the

Please note

ENABLE_AV

Standby = 0V

signals are seen as.

–3dB

point of the filter

2.15

and is terminated by a

forms protection against ESD.

See description

: When in RGB SCART mode the

on

Page 8

HDMI output stage

Please note:

Due to the plug and play nature of the

HDMI/DVI interface, if presented with a reported no

HDMI problem it is worth checking all set-up

parameters of both the DVD player and the

Plasma/Projector in use before performing component

level diagnostics on this product.

HDMI is a system that transmits uncompressed digital

video and digital audio over a high speed encrypted

interface.

IC1102 is an SII9190 HDMI transmitter IC in essence

the chip takes the Digital Video and Audio information

and sends the Data out in HDMI format.

REG1100 is used to generate a clean regulated 3V3

power supply to Pins 18 and 33 of the HDMI chip.

IC1100 –IC1101 are 3 state octal/line drivers these

form a multiplex that switches between the 2 groups of

signals for the video data input stage of the SII9190

the multiplexer is control by the Signal from the Vaddis

V labelled as PROG/INT this will sit at logic 1 for

Progressive scan and logic 0 for interlaced.

interlaced mode

In

VIDP7-0

are passed to input port pins

the 8 bit Y/Cb/Cr video data on

D15 – D8

of the

SII9190.

Progressive scan mode

In

all 20 bits of the Video

data bus are used and get mapped as follow.

VIDP 19 -12 provide 8 msbits of Y data to pins D15-8

VIDP 11 -10 provide 2Isbits of Y data to pins D2-3

VIDP 9 - 2 provide 8 msbits of Cb/Cr data to pins D23 – 16

VIDP 1 – 0 provide 2 Isbits of Cb/Cr data to pins D7 - 6

Along with the VIDP video data lines we must also see

VSYNC – Vertical sync data

HSYNC – Horizontal sync

CLK27M_VID – 27Mhz video clock.

SPDIF – Digital audio data

MCLK_HDMI – Used to strobe HDMI dig audio

output

At the

of the HDMI chip we will see the

following signals at SKT100.

TMDS

(Transistion Minimised Differential Signalling)

this consists of a clock signal (TXC+/TXC-) and

signals

(TX0+/TX0-, TX1+/TX1- and TX2+/TX2-)

3 data

.

All signals are differential and use current switching

techniques therefore

no signals

will be observed

unledd the output is correctly terminated. In this

application the clock signal will always be 27MHz and

the data signals will be clock X10 so 270Mbit/s.

DDC Channel

this is a 12C interface on DDC_SCL and

DDC_SDA. These signals connect to the VADDIS V

which is the I2C bus master, The DDC channel is used

to read back information from the HDMI sync regarding

it’s Video and Audio capabilities and is also used for

HDCP encryption authentication.

+5V Power, the HDMI interface requires a 5V supply

capable of delivering around 50mA, the supply is

provided by REG 1101 which delivers the required

current and will shut down in the event of a short circuit.

Hotplug.

The HDMI `Hot plug’ signal HDPIN is a +5V to

signal the presence of equipment being connected, this

converted to 3v3 logic 1 as IC1100 is not +5V tolerant.

CEC.

The CEC (Consumer Electronics Control) signal is

a 1-wire bidirectional control signal. It connects to the

Vaddis via an ESD protection circuit D1102 at the

moment this line is not used at present and is a optional

part of the HDMI specification.

Comms and Final video output stage

The signals from the main board travel up to the Comms

board on connector

CON902

.

The Video signals simply travel via an A-C coupling net

before exiting the player via the RCA-phono sockets at

locations

SKT902

and

SKT903

.

The RS232 interface is on 9 way “D” type CON900, with

IC900 providing the level translation and static protection

between the RS232 levels and the

required by the VADDIS V,

CON900

3.3V

CMOS levels

also supplies a

+5V

Status level when ever the unit is not in standby this

generated from a buffered version of the

AV_ENABLE

signal as used within the SCART output stage (0V in

standby).

We have two remote input bus’s on this board, the first

can be seen to arrive at

signal received should be a

SK901

on a 3.5mm mono jack

36Khz

modulated RC5

signal, the RC5 data then travels to the front panel and

is fed to IR led that is sited just behind the front panel

Sensor

, we use the sensor to demodulate the and opto-

IR

isolate the signal due to the fact that the signal is floating

up from ground.

The 3.5mm socket at location

un-modulated RC5 signals these take the form of a

5V/0V RC5 signal, with 5V representing a mark

SKT900

is used to receive

(equivalent to a burst of 36Khz carrier on infrared) and

the 0V representing a space (equivalent to no-infra-red

carrier), this input is effectively wire-Ord with the front

panel IR receiver on IRRCV.

Page 9

SW2A

DGND

SDDFC30400

SW1

18-000-0019

SW2B

SDDFC30400

C49

22N

100V

MKS2

5V_NFB

3V3_NFB

R7

6K8

0W25

MF

R4

4K7 0W25

MF

C15

100N

100V

MKS2

FHLDR1

20mm HLDR

FS1 T315mA

S504

FHLDR2

20mm HLDR

FS2

T315mA

S504

CON1

3

2

1

MOLEX

44472

(NFB From PSU Outputs)

C50

22N 100V

MKS2

R10

1K0 0W25

MF

TR4

BC546B

TO-92

VN35V6

2A22B

115V 230V

1A11B

MA NS SUPPLY

FOR EXT. AUDIO

SUPPLY TX

R11

9K1

0W25

MF

TR8

BC556B

TO-92

VN35V6

R26

68R

0W25

MF

R27

2K7

0W25

MF

USED TO SECURE TRANSFORMER CABLES TO PCB NEAR CON1

6

5

4

C51

22N

100V

MKS2

C16

100N

100V

MKS2

GREY

BLACK

3

4

GREY

DK GREY

CON2

WAGO

256

NOTE TRANSFORMER TX1 IS MOUNTED ON

THE CHASSIS AND CONNECTED TO THE PSU

PCB BY CON2,3,4. TX1 IS SHOWN ABOVE FOR

CIRCUIT OPERATION

DGND

R12

10K

0W25

MF

R14

NF

R15

10K

0W25

MF

C56

4N7

100V

CER

R28

22R

0W25

MF

SKT1

BULGIN

SH1

PX0580

NF

EMC Shield

N

E

L

QTY DESCRIPTIONPART No. NOTESITEM

R9

1K0 0W25

MF

PSU CLK

ITEM1 1 Clip For SW Profile HeatsinkF006

ITEM2 1 Sil Pad For TO-220 HS InsulatorF082

ITEM3 2 Fuseholder Cover For 20mm FuseholderF022

ITEM4 1 Blank PCB DV78 PSUL959PB

ITEM6 1 Cable Tie 100MM X 2.5MMF044

ITEM5 1 Earth Lead Assy 75MM8M101 SAFETY EARTH WIRE FROM IEC INLET SK1 TO METAL CHASSIS

ITEM7 2 Rivet CopperHP007S RIVETS TO SECURE IEC INLET TO PCB

C1 C3

NF

4

1

C2

NF

VP5V

C47

22P

100V

N150

DGND

DGND

R8

1K0

0W25

MF

TR3

BC546B

TO-92

R13

10K

0W25

MF

TR7

BC556B

TO-92

R25

100R

0W25

MF

3N3

250V

3

CER

L1

250U

2

C4

3N3

250V

CER

C14

100N

100V

MKS2

VN35V6

C48

1N0

100V

CER

WH TE

BLUE

2

1

BLUE

LT GREY

DZ6

BZX79C

12V

DO-35

1

115V

2

3

115V

4

C17

100N

100V

MKS2

VN35V6 VN35V6VN35V6

2

VFB

1

COMP

8

VREF

4

RT/CT

R29

82K 0W25

MF

TX1

Small Toroidal Mains

L924TX

7

1

GREEN

CON3

WAGO

256

7

VCC

GND

5

FIX1

Dia 3.5mm

FIX2

Dia 3.5mm

5

6

TR5

BD179

TO-126

R17

10R

0W25

MF

OUT

ISEN

1

GREY2GREY

CON4

WAGO

256

VN35V6

1

1

C40

220UF

16V

YXF

IC1

UC3843AN

DIP-8

6

3

VN35V6

C5

NF

33R 0W25

C52

330P

100V

N750

R24

MF

R16

47K

0W25

MF

FIX3

Dia 3.5mm

FIX4

Dia 3.5mm

HS1B

SW38-2

10 2C/W

R5

4K7 0W25

MF

1

1

D1

2KBP02

DGND

M1

IRF640N

TO-220

R30

0R22

3W

SPRX

FIX5

Dia 3.5mm

FIX6

Dia 3.5mm

C6

100N

100V

MKS2

1

1

C27

1000UF

63V

YK

L2

NF

LK1

0R0 0W 25 MF

C7

100N

100V

MKS2

TX2

Ferrite Switch Mode

L925TX

C36

1N0

100V

CER

R31

10R

0W25

MF

C28

1000UF

63V

YK

1 11

16T

2

16T

3

SCR

DGND

FD1

FD2

41T

41T

22T

14T

10T

VN35V6

4

5

6

12

9

10

7

8

TOOL1

TOOL2

TOOL3

TOOL4

C8

100N

100V

MKS2

C32

470pF

1kV

DE

R20

470R

0W25

MF

1N0 100V

DRAWING TITLE

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9PB

R1

22K

0W25

MF

DZ1

BZX79C

2V7

DO 35

R2

220R

0W25

MF

D6

31DQ10 DO-201AD

C34

CER

D8

UF5406

DO-201AD

TR1

BC547B

TO-92

D2

UF4003

DO-41

R21

470R

0W25

D3

MF

UF4003

DO-41

D4

UF4003

DO-41

C33

1N0 100V

CER

NFB (To Controller E/A)

D7

31DQ06 DO-201AD

C35

1N0 100V

CER

R18

10R 0W25

MF

DV78 SERIES PSU

Filename:

Notes:

Contact Engineer:

C37

100UF

50V

YXF

C38

100UF

50V

YXF

R23

33R 0W 25

MF

5V_NFB

3V3_NFB

R19

10R 0W 25

MF

C57

470UF

25V

YXF

L959_1.1.sch

C53

1000UF

16V

YXF

C9

100N

100V

MKS2

C24

100N

100V

MKS2

DZ2

BZX79C

10V

DO 35

DZ3

BZX79C

3V3

DO 35

DZ4

BZX79C

5V6

DO 35

DGND

C29

22UF

63V

YK

VN13V5_F1

C30

22UF

63V

YK

VN19V

L3

33U 1.17A 8RHT2

L4

33U 1.17A 8RHT2

C10

100N

100V

MKS2

C39

220UF

16V

YXF

C18

100N

100V

MKS2

C54

1000UF

16V

YXF

C55

1000UF

16V

YXF

C25

100N

100V

MKS2

R32

NF

Contact Tel: (01223) 203200Kevin Lamb

C11

100N

100V

MKS2

470R 0W25

C19

100N

100V

MKS2

L6

6U8 2.1A 8RHT2

C20

100N

100V

MKS2

L7

6U8 2.1A 8RHT2

C21

100N

100V

MKS2

33U 1.17A 8RHT2

R33

1K0

0W25

MF

ECO No. DESCRIPTION OF CHANGE

L5

INITIALS

Printed:

R22

MF

R3

4K7

0W25

MF

C41

470UF

25V

YK

C42

470UF

25V

YK

C44

470UF

25V

YK

C45

470UF

25V

YK

DATE

22 Apr2004

D5

1N4148

DO 35

TR2

BC546B

TO-92

TR6

BD179

TO-126

DZ5

BZX79C

5V1

DO 35

DGND

DGND

C46

470UF

25V

YK

DGND

Make CON1 fitted (used in DV29)22/04/04PG04_E046

Production release02/07/03KAL03_E195

VP5V

C12

100N

100V

MKS2

DGND

C13

100N

100V

MKS2

C43

470UF

25V

YK

C22

100N

100V

MKS2

C23

100N

100V

MKS2

1 1Sheet of

R6

6K8

0W25

MF

C31

22UF

63V

YK

VP15V5

AGND

VN15V5

VN9V_F2

VN13V5_F1

VP5V

VP3V3

VP12V

C26

100N

100V

MKS2

AC_PRES*

AGND

DGND

VP5V

VP12V

VP5V

VP3V3

SPARE1

SPARE2

VN19V

VN9V_F2

VN13V5_F1

VP3V3

VP3V3

VP3V3

VP3V3

VP3V3

VP3V3

SPARE3

SPARE4

VP5V

VP5V

VP5V

PSU_CLK

AC_PRES*

VP12V

VP15V5

VN15V5

DRAWING NO.

LK2

NF

DGND

DGND

DGNDAGND

L959CT

CON5

4

3

2

1

Amp

HD Pwr Con

CON6

8

7

6

5

4

3

2

1

AMP

CT

NF

CON7

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

MOLEX

52045

1.1

1.0

ISSUE

Page 10

Page 11

DV79 DVD player PSU board L959AY issue 1.1.1

Designator Part Description

C1 2J410 Capacitor SM 0805 X7R Ceramic 10% 50V 100N

C2 2J410 Capacitor SM 0805 X7R Ceramic 10% 50V 100N

C3 2J410 Capacitor SM 0805 X7R Ceramic 10% 50V 100N

C4 2J410 Capacitor SM 0805 X7R Ceramic 10% 50V 100N

C5 2MA610 Capacitor Surface Mount Electrolytic 10UF 50V 6.3 X 4.5MM

C6 2MA610 Capacitor Surface Mount Electrolytic 10UF 50V 6.3 X 4.5MM

C7 2MA610 Capacitor Surface Mount Electrolytic 10UF 50V 6.3 X 4.5MM

C8 2L210 Capacitor SM 0805 NPO Ceramic 5% 100V 1N0

C9 2L210 Capacitor SM 0805 NPO Ceramic 5% 100V 1N0

C10 2L210 Capacitor SM 0805 NPO Ceramic 5% 100V 1N0

C11 2L210 Capacitor SM 0805 NPO Ceramic 5% 100V 1N0

CON1 8K8616 Con 1.0MM Horiz FFC 16WAY 52807 Series

D1 3AS16W Diode Surface Mount Small Signal BAS16W SOT-23 Package

D2 3AS16W Diode Surface Mount Small Signal BAS16W SOT-23 Package

D3 3AS16W Diode Surface Mount Small Signal BAS16W SOT-23 Package

D4 3AS16W Diode Surface Mount Small Signal BAS16W SOT-23 Package

DISP1 B1014 Display DV88

IC1 5H6312 IC VFD Driver PT6312LQ SM LQFP-44 package

LED1 3D007 LED 3.1mm Green SLR-37MG3T

LED2 3D010 LED SM Red SML-010LT

LED3 3D007 LED 3.1mm Green SLR-37MG3T

LED5 3D006 LED 3mm Red/Green Tri-Colour L-93WEGW

R1 1M133 Resistor 0805 Surface Mount 0.125W 1% 330R

R2 1M133 Resistor 0805 Surface Mount 0.125W 1% 330R

R3 1M133 Resistor 0805 Surface Mount 0.125W 1% 330R

R4 1M122 Resistor 0805 Surface Mount 0.125W 1% 220R

R5 1M118 Resistor 0805 Surface Mount 0.125W 1% 180R

R6 1M139 Resistor 0805 Surface Mount 0.125W 1% 390R

R8 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

R9 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

R10 1M247 Resistor 0805 Surface Mount 0.125W 1% 4K7

R11 1M356 Resistor 0805 Surface Mount 0.125W 1% 56K

R13 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

R14 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

R15 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

RX1 B2109 IR Receiver Module Kodenshi KSM-902TM1N

SW1 A1511 Switch Tact Low Profile No Gnd Pin

SW2 A1511 Switch Tact Low Profile No Gnd Pin

SW3 A1511 Switch Tact Low Profile No Gnd Pin

SW4 A1511 Switch Tact Low Profile No Gnd Pin

SW5 A1511 Switch Tact Low Profile No Gnd Pin

SW6 A1511 Switch Tact Low Profile No Gnd Pin

SW7 A1511 Switch Tact Low Profile No Gnd Pin

SW8 A1511 Switch Tact Low Profile No Gnd Pin

SW9 A1511 Switch Tact Low Profile No Gnd Pin

TR2 4D10KN Digital Transistor MMUN2211LT1 SOT23 Package

TR3 4A849B Transistor BC849B SOT23 Package

TR4 4A849B Transistor BC849B SOT23 Package

TR5 4D10KP Digital Transistor MMUN2111LT1 SOT23 Package

Page 12

IR REMOTE SENSOR

Pins 1-4 (SW1-4) are set

When creating BOM, import CSV into database then manually change quantity t o 0.07 for ITEM4 (F238

+5VD

C1

100N

50V

0805

DGND

C8

1N0

100V

0805

DGND DGND DGNDDGND

FD1 FD2

TOOL1 TOOL2 TOOL3 TOOL4

+5V

GND

LED2

SM

RED

SML-010

LED2 is underneath infra red receiver.

The LED is lit by the remote bus signal,

allowing the infra red receiver to

demodulate the remote bus signal.

P18

RX1

O/P

KSM-902TM1N

P19

C10

1N0

100V

0805

R2

330R

0W125

0805

CHS

R8

10K

0W125

0805

TR2

MMUN2211LT1

SOT-23

C9

1N0

100V

0805

P16

C11

1N0

100V

0805

R9

10K

0W125

0805

TR3

BC849B

SOT-23

C6

10UF

50V

SM

SW6

1

2

SW7

1

2

SW8

1

2

SW9

1

2

K4

to read 0001, to be read

by display self test in

software

PLAY

STOP

LOAD

>>

D1

D2

BAS16

SOT-323

D3

BAS16

SOT-323

D4

BAS16

SOT-323

+5VD

BAS16

SOT 323

R10

4K7

0W125

0805

R1

330R

0W125

0805

DGND

-19V

+5VD

GR434GR335GR236GR1

C2

100N

50V

0805

GR5

GR6

VEE

SG11

SG10

SG9

P12

P13

P17

G5

33

G6

32

31

G7

S15

30

S14

29

S13

28

27

26

S12

25

S11

S10

24

S9

23

DVDA_LED*

S3

S4

ON/STBY*_LED

S5

S6

NAV_LED*

+5VD

DGND

+5VD DGND

K2

+5VD

DGND

K[2..4]

DGND

R11

56K

0W125

0805

P20

1

SW1

2

SW2

3

SW3

4

SW4

5

DOUT

6

DIN

7

GND

8

CLK

9

STB

10

K1

11

K2

44

K312K413VDD14SG1/KS115SG2/KS216SG3/KS317SG4/KS418SG5/KS519SG6/KS620SG721SG8

K4

K3

DGND

42

GND43OSC

IC1

PT6312LQ

LQFP-44

S1S2S3S4S5S6S7

+5VD

C4

100N

50V

0805

G1G2G3

G4

37

38

VDD

LED439LED340LED241LED1

SG16/GR7

SG15/GR8

SG14/GR9

SG13/GR10

SG12/GR11

22

S8

LED1

TR4

BC849B

SOT-23

R4

220R

0W125

0805

NF

R3

330R

0W125

0805

F11F12G15G26G37G48G59G610G7

Note that G1..7 are deliberately

reversed here, to be the same as

previous design (software takes it into

account)

C3

100N

50V

0805

P14

+5VD

3mm

GRN

LED 3mm

+5VD

R5

180R

0W125

0805

DGND

LED3

DISP1

SAMSUNG

SVV-07MS09

11

G1G2G3G4G5G6G7

DVD-A

TR5

MMUN2111LT1

SOT-23

P15

R6

390R

0W125

0805

REDGRN

+5VD

3mm

GRN

LED 3mm

LED5

3mm

BICOL

LED 3mm

VFD

POWER

NAV

S125S226S327S428S529S630S731S832S933S1034S1135S1236S1337S1438S1539F242F2

S1S2S3S4S5S6S7S8S9

S10

43

-9V_F2-13V5_F1

S11

S12

S13

S14

S15

R13

10K

0W125

0805

R14

10K

0W125

0805

R15

10K

DOUT

CLK

STB

D N

REM_P

IRRCV

REM N

0W125

0805

DGND

NF

CON1

16

MOLEX

52807

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

DGND

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P1

SW1

MODE

1

2

SW2

<<

1

2

K2

K3

+5VD

DGND

C5

10UF

50V

SM

SW3

1

SW4

1

SW5

1

>|

2

|<

2

PAUSE

2

C7

10UF

50V

SM

DGND

-19V

-9V_F2

-13V5_F1

NOTE TO ENG NEERS:

tape)

This is the only way to ensure it appears as 0.07m on the BOM report

ITEM1 BLANK PCB DV78 DISPLAY BOARD1 L961PB

ITEM2 1

ITEM3 1

ITEM4 1 Foam D/S ADH BK 3MM Thk 10MM Wide RA106 10M ReelF238

F231

F231

VFD CORNER LOCATOR

VFD CORNER LOCATOR

70mm of 10mm wide double sided tape under VFD

DRAWING TITLE

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

DV78/DV79 DISPLAY BOARD

Filename:

L961_1.3.Sch

Notes:

Contact Engineer:

Contact Tel: (01223) 203270Peter Gaggs

PG 17-09-04 CHANGE RX1 TO KSM-902TM1N FOR BETTER PERFORMANCE 1.304_E140

PG 12-01-04 ADD DVD-A LED FOR DV79 1 204_E007

PG 02-09-03 CHANGE FOAM TAPE FROM F163 TO F238 (DOUBLE SIDED) 1.103_E260

PG 04-07-03 NITIAL SCH 1.003_E202

INITIALS

Printed:

DATE

17 Sep 2004

1 1Sheet of

ECO No. DESCRIPTION OF CHANGE

A2

DRAWING NO.

ISSUE

L961

Page 13

Page 14

DV79 DVD player Display board L961AY issue 1.3.0

Designator Part Description

C1 2J410 Capacitor SM 0805 X7R Ceramic 10% 50V 100N

C2 2J410 Capacitor SM 0805 X7R Ceramic 10% 50V 100N

C3 2J410 Capacitor SM 0805 X7R Ceramic 10% 50V 100N

C4 2J410 Capacitor SM 0805 X7R Ceramic 10% 50V 100N

C5 2MA610 Capacitor Surface Mount Electrolytic 10UF 50V 6.3 X 4.5MM

C6 2MA610 Capacitor Surface Mount Electrolytic 10UF 50V 6.3 X 4.5MM

C7 2MA610 Capacitor Surface Mount Electrolytic 10UF 50V 6.3 X 4.5MM

C8 2L210 Capacitor SM 0805 NPO Ceramic 5% 100V 1N0

C9 2L210 Capacitor SM 0805 NPO Ceramic 5% 100V 1N0

C10 2L210 Capacitor SM 0805 NPO Ceramic 5% 100V 1N0

C11 2L210 Capacitor SM 0805 NPO Ceramic 5% 100V 1N0

CON1 8K8616 Con 1.0MM Horiz FFC 16WAY 52807 Series

D1 3AS16W Diode Surface Mount Small Signal BAS16W SOT-23 Package

D2 3AS16W Diode Surface Mount Small Signal BAS16W SOT-23 Package

D3 3AS16W Diode Surface Mount Small Signal BAS16W SOT-23 Package

D4 3AS16W Diode Surface Mount Small Signal BAS16W SOT-23 Package

DISP1 B1014 Display DV88

IC1 5H6312 IC VFD Driver PT6312LQ SM LQFP-44 package

LED1 3D007 LED 3.1mm Green SLR-37MG3T

LED2 3D010 LED SM Red SML-010LT

LED3 3D007 LED 3.1mm Green SLR-37MG3T

LED5 3D006 LED 3mm Red/Green Tri-Colour L-93WEGW

R1 1M133 Resistor 0805 Surface Mount 0.125W 1% 330R

R2 1M133 Resistor 0805 Surface Mount 0.125W 1% 330R

R3 1M133 Resistor 0805 Surface Mount 0.125W 1% 330R

R4 1M122 Resistor 0805 Surface Mount 0.125W 1% 220R

R5 1M118 Resistor 0805 Surface Mount 0.125W 1% 180R

R6 1M139 Resistor 0805 Surface Mount 0.125W 1% 390R

R8 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

R9 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

R10 1M247 Resistor 0805 Surface Mount 0.125W 1% 4K7

R11 1M356 Resistor 0805 Surface Mount 0.125W 1% 56K

R13 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

R14 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

R15 1M310 Resistor 0805 Surface Mount 0.125W 1% 10K

RX1 B2109 IR Receiver Module Kodenshi KSM-902TM1N

SW1 A1511 Switch Tact Low Profile No Gnd Pin

SW2 A1511 Switch Tact Low Profile No Gnd Pin

SW3 A1511 Switch Tact Low Profile No Gnd Pin

SW4 A1511 Switch Tact Low Profile No Gnd Pin

SW5 A1511 Switch Tact Low Profile No Gnd Pin

SW6 A1511 Switch Tact Low Profile No Gnd Pin

SW7 A1511 Switch Tact Low Profile No Gnd Pin

SW8 A1511 Switch Tact Low Profile No Gnd Pin

SW9 A1511 Switch Tact Low Profile No Gnd Pin

TR2 4D10KN Digital Transistor MMUN2211LT1 SOT23 Package

TR3 4A849B Transistor BC849B SOT23 Package

TR4 4A849B Transistor BC849B SOT23 Package

TR5 4D10KP Digital Transistor MMUN2111LT1 SOT23 Package

Page 15

AC_PRES*

L967C10

L967C10.Sch

PSUCLK

AC_PRES*

POWER

SHEET 10

L967C2

L967C2.sch

VADDIS V

SHEET 2

GA N_SCAL NG

RESET*

ML_8740_0

ML_8740_1

ML_8740_2

FSEL0

FSEL1

PSUFS0

PSUFS1

ADAT0

ADAT1

ADAT2

ABCLK

ALRCLK

SPDIF

MUTE*

CLK27M_VADDIS

MCLK_VADDIS

MD

MC

GAIN_SCAL NG

RESET*

MD

MC

ML_8740_0

ML_8740_1

ML_8740_2

FSEL0

FSEL1

PSUFS0

PSUFS1

ADAT0

ADAT1

ADAT2

ABCLK

ALRCLK

SPDIF

MUTE*

CLK27M_VADDIS

MCLK_VADDIS

ENABLE_AV

L967C3

L967C3.Sch

FSEL0

FSEL1

PSUFS0

PSUFS1

ADAT0

ADAT1

ADAT2

ABCLK

ALRCLK

SPDIF

MUTE*

CLK27M_VADDIS

MCLK_VADDIS

ENABLE_AV

CLOCKS

SHEET 3

PSUCLK

ADAT_DAC0

ABCLK_DAC0

ALRCLK_DAC0

MCLK_DAC0

MUTE_BUF*

ADAT_DAC1

ABCLK_DAC1

ALRCLK_DAC1

MCLK_DAC1

ADAT_DAC2

ABCLK_DAC2

ALRCLK_DAC2

MCLK_DAC2

PSUCLK

ADAT_DAC0

ABCLK_DAC0

ALRCLK_DAC0

MCLK_DAC0

MUTE_BUF*

ADAT_DAC1

ABCLK_DAC1

ALRCLK_DAC1

MCLK_DAC1

ADAT_DAC2

ABCLK_DAC2

ALRCLK_DAC2

MCLK_DAC2

MD

MC

RESET*

MD

MC

RESET*

L967C4

L967C4.Sch

AC_PRES* SCART_LEFT

GA N_SCAL NG

RESET*

MD

MC

ML_8740_0

SCART_RIGHT

DAC L&R

SHEET 4

ADAT_DAC0

ABCLK_DAC0

ALRCLK_DAC0

MCLK_DAC0

MUTE_BUF*

L967C5

L967C5.Sch

MD

MC

ML_8740_1

RESET*

ADAT_DAC1

ABCLK_DAC1

ALRCLK_DAC1

MCLK_DAC1

CENTRE_OUT

SUB_OUT

L967C6

L967C6.Sch

MD

MC

ML_8740_2

RESET*

ADAT_DAC2

ABCLK_DAC2

ALRCLK_DAC2

MCLK_DAC2

DAC LS&RS

SHEET 5

DAC C & SUB

SHEET 6

CENTRE_OUT

SUB_OUT

SCART_LEFT

SCART_RIGHT

CEC

9190INT*

PROG/ NT*

DDC_SDA

DDC_SCL

SDA

SCL

HDMI_RESET*

VIDP[0..19]

HSYNC*

VSYNC*

CLK_27M_VID

16/9

ENABLE_AV

IRRCV

SERIAL_TX

SERIAL_RX

REM_BUS_P

REM_BUS_N

CEC

9190 NT*

PROG/INT*

DDC_SDA

DDC_SCL

SDA

SCL

HDMI_RESET*

VIDP[0..19]

HSYNC*

VSYNC*

CLK_27M_VID

16/9

ENABLE_AV

IRRCV

SERIAL_TX

SERIAL_RX

REM_BUS_P

REM_BUS_N

ABCLK_HDMI

MCLK_HDMI

ABCLK_HDMI

MCLK_HDMI

ADAT0

ADAT1

ADAT2

ALRCLK

RESET*

L967C11

L967C11.Sch

ADAT0

ADAT1

ADAT2

ABCLK_HDMI

ALRCLK

MCLK_HDMI

HDMI

SPDIF

CEC

9190_ NT*

PROG/ NT*

DDC_SDA

DDC_SCL

SDA

SCL

HDMI_RESET*

VIDP[0..19]

HSYNC*

VSYNC*

CLK27M_VID

L967C7

L967C7.Sch

SDA

SCL

RESET*

VIDP[0..19]

HSYNC*

VSYNC*

CLK27M_VID

SHEET 11

SCART_COMPOSITE

SCART_RED

SCART_GREEN

SCART_BLUE

VIDEO ENCODER

SHEET 7

COMPOSITE

SVID_Y

SVID_C

SCART_COMPOSITE

SCART_RED

SCART_GREEN

SCART_BLUE

COMPOSITE

Y

Y

U

U

V

V

SVID_Y

SVID_C

L967C8

L967C8.Sch

SCART_LEFT

SCART_RIGHT

16/9

ENABLE_AV

SCART

SHEET 8

SCART_COMPOSITE

SCART_RED

SCART_GREEN

SCART_BLUE

L967C9

L967C9.Sch

COMPOSITE

Y

U

V

SVID_Y

SVID_C

COMMS, VIDEO OUT

ENABLE_AV

IRRCV

SERIAL_TX

SERIAL_RX

REM_BUS_P

REM_BUS_N

SHEET 9

ITEM100 1 Blank PCB DV79 Main BoardL967PB

DRAWING TITLE

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

DV79 MAIN BOARD TOP LEVEL

Filename:

Notes:

Contact Engineer:

L967C1.Prj

03_E020 19-02-04 Production release

PG 1.0

INITIALS

Printed:

DATE

19 Feb 2004

1 11Sheet of

A2

DRAWING NO.

Contact Tel: (01223) 203270Peter Gaggs

ECO No. DESCRIPTION OF CHANGE

ISSUE

L967C1

Page 16

FRONT PANEL

CON202

1

2

FPDOUT

XFPCLK

3

XFPSEL

4

XFPDN

5

REM BUS P

6

IRRCV

7

8

9

10

11

12

13

14

REM_BUS_N

15

16

MOLEX

DGND

52806

SDRAM DECOUPL NG

+3V3D

C212

C213

100N

100N

16V

16V

0603

0603

DGND

address

data

RAMDAT5

RP200A

RAMDAT6

RP200B

RAMDAT11 FRAMDAT11

RP200C

RAMDAT10 FRAMDAT10

RP200D

RAMDAT9

RP201A

RAMDAT8

RP201B

RAMADD9

RP201C

RAMADD8

RP201D

RAMADD7

RP202A

RAMADD6

RP202B

RAMADD5

RP202C

RAMADD4 FRAMADD4

RP202D

RAMADD3 FRAMADD3

RP203A

RAMDAT31

RP203B

RAMDAT30

RP203C

RAMDAT29

RP203D

RAMDAT28

RP204A

RAMDAT27

RP204B

RAMDAT26

RP204C

RAMDAT25

RP204D

RAMDAT24

RP205A

RAMDAT7

RP205B

RAMBA0

RP205C

RAMBA1

RP205D

RAMADD10

RP206A

RAMADD0

RP206B

RAMADD1

RP206C

RAMADD2 FRAMADD2

RP206D

RAMDAT16

RP207A

RAMDAT17

RP207B

RAMDAT18

RP207C

RAMDAT19

RP207D

RAMDAT20

RP208A

RAMDAT21

RP208B

RAMDAT22

RP208C

RAMDAT23

RP208D

PR252

RAMADD11

PNVMRB* NF(AMD)

PF243

RAMDAT3

RAMDAT4 NF(AMD 16Mb)

RAMDAT12 NF (Intel 64Mb)

Use these resistors o confgure for

ntel/AMD 8Mbit 16Mbit 32Mbit or

64Mbit devices

ntel 32Mb t is used for DV79

+5V_DSPLAY

PR253

C214

100N

16V

0603

1 8

2 7

1 8

2 7

1 8

2 7

1 8

2 7

1 8

2 7

1 8

2 7

1 8

2 7

1 8

2 7

1 8

2 7

R206

56R

0W125 0805

R207

56R

0W125 0805

R252

56R

0W125 0805

R208

56R

0W125 0805

R253

56R

0W125 0805

R209

56R

0W125 0805

DGND

C215

100N

16V

0603

63

54

63

54

63

54

63

54

63

54

63

54

63

54

63

54

63

54

NF(32Mb+)

REM_BUS_P

REM_BUS_N

R225

1K0

0W063

0603

NF

C217

100N

16V

0603

NF

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

56R

FRAMDAT5

FRAMDAT6

FRAMDAT9

FRAMDAT8

FRAMADD9

FRAMADD8

FRAMADD7

FRAMADD6

FRAMADD5

FRAMDAT31

FRAMDAT30

FRAMDAT29

FRAMDAT28

FRAMDAT27

FRAMDAT26

FRAMDAT25

FRAMDAT24

FRAMDAT7

FRAMBA0

FRAMBA1

FRAMADD10

FRAMADD0

FRAMADD1

FRAMDAT16

FRAMDAT17

FRAMDAT18

FRAMDAT19

FRAMDAT20

FRAMDAT21

FRAMDAT22

FRAMDAT23

FRAMADD11

FLASHA19

FRAMDAT3

FLASHA21

19V_OUT13V5_OUT9V_OUT

PR200

PR201

PR202

PR203

PR204

PR205

PR206

PR207

PR208

PR209

PR210

PR211

PR212

PR213

PR214

PR215

PR216

PR217

PR218

PR219

address data

RAMCKE

PCLK

RAMBA0

RAMBA1

RAMWE*

RAMCAS*

RAMRAS*

RAMCS*

RAMADD11

RAMADD10

RAMADD9

RAMADD8

RAMADD7

RAMADD6

RAMADD5

RAMADD4

RAMADD3

RAMADD2

RAMADD1

RAMADD0

RAMDQM

+3V3D

DGND

SDRAM decouplng on bottom of board

C256

C257

1N0

50V

0603

67

68

22

23

17

18

19

20

21

24

66

65

64

63

62

61

60

27

26

25

16

71

28

59

C258

1N0

1N0

50V

50V

0603

0603

1

15

29

43

VDD

VDD

VDD

VDD

CKE

CLK

BA0

BA1

IC203

WE

CAS

RAS

CS

SDRAM

A11 (NC)

A10/AP

A9

A8

A7

A6

C MEM SDRAM 512KX32BTX4 7NS

A5

A4

A3

A2

A1

A0

DQM0

DQM1

DQM2

DQM3

VSS

VSS

VSS

VSS

44

58

72

86

DGND

R210

56R

0W125

0805

R222

0R0

0W125

0805

P279

C245

1N0

50V

0603

VIDP0

VIDP1

VIDP2

VIDP3

VIDP4

VIDP5

VIDP6

VIDP7

VIDP8

VIDP9

VIDP10

VIDP11

VIDP12

VIDP13

VIDP14

VIDP15

VIDP16

VIDP17

VIDP18

VIDP19

PV236

PV237

PV238

AMCLK OUT

ALRCLK

ABCLK

ADAT0

ADAT1

ADAT2

SPDIF

C246

1N0

50V

0603

+3V3D

+1V8D

PV223

PV224

PV225

PV226

PV227

PV228

PV229

PV230

PV231

PV232

PV233

PV234

PV235

PV239

PV240

PV241

PV242

PV243

PV244

PV245

CLK 27M VID

VSYNC*

HSYNC*

C204A

7

WP

6

SCL

5

24LC08BT/SN

SO8

RP215C

4K7

62mW

1206

6 3

5 4

R231

1K0

0W125

0805

BOOT SELECT

TR200

MMUN2211LT1

SOT23

C247

1N0

50V

0603

C255

1N0

50V

0603

ALRCLK

ABCLK

ADAT0

ADAT1

ADAT2

SPDF

A0

A1

A23SDA

RP215D

4K7

62mW

1206

1

2

P201

P282

VDP[0 19]

DGND

IC204B

24LC08BT SN

SO8

R232

4K7

0W125

0805

PJ200

VCC

GND

VIDP[0 19]

IC200A 74HCT125D

2 3

5 6

9 8

+3V3D

R251

33R

0W125

0805

+3V3D

8

4

DGND

+3V3D

C204

C206

100N

100N

16V

16V

0603

0603

DGND

C200

47P

100V

0805

DGND

SO14

1

DGND

IC200B 74HCT125D

SO14

4

DGND

IC200C 74HCT125D

SO14

10

DGND

+5VD

R234

4K7

0W125

0805

R233

4K7

0W125

0805

R204

10K

0W125

0805

PJ203

PJ205

DGND

NOTE: JTAG port is for softwae debug on y

Boundary scan is not supported

C218

100N

16V

0603

P242

+3V3D

DGND

IC200E

74HCT125D

SO14

VCC

GND

12 11

C205

47P

100V

0805

SDA

SCL

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

DGND

P294

P295

P296

CON201

HARWIN

M20972

14

7

13

R218

100R

0W125 0805

R254

100R

0W125 0805

R255

100R

0W125 0805

RRCV

+5VD

DGND

IC200D

74HCT125D

SO14

FRONT PANEL

FPDOUT

P200

XFPDN

P202

XFPCLK

P203

XFPSEL

P204

IRRCV

EJTAG DEBUG

Not Ftted

C219

100N

16V

0603

L200 120R@100MHz

RESET

+3V3D

C226

100N

16V

0603

R250

5K6

0W125

0805

VCC

GND

DGND

R228

1K0

0W125

0805

DDC_SDA

HDMI_RESET*

CEC

DDC_SCL

PROG/INT*

C227

100N

16V

0603

IC201

RST

LM809M3 2 63

SOT23

RESET*

MCLK_VADDS

R223

0R0

0W125

0805

NF

C229

100N

16V

0603

C228

100N

16V

0603

PWR_ON_RESET*

R202 22R 0603

RAMBA1

RAMBA0

RAMADD11

RAMADD10

RAMADD9

RAMADD8

RAMADD7

RAMADD6

RAMADD5

RAMADD4

RAMADD3

RAMADD2

RAMADD1

RAMADD0

RAMDAT0

RAMDAT1

RAMDAT2

RAMDAT3

RAMDAT4

RAMDAT5

RAMDAT6

RAMDAT7

RAMDAT8

RAMDAT9

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

RAMDAT16

RAMDAT17

RAMDAT18

RAMDAT19

RAMDAT20

RAMDAT21

RAMDAT22

RAMDAT23

RAMDAT24

RAMDAT25

RAMDAT26

RAMDAT27

RAMDAT28

RAMDAT29

RAMDAT30

RAMDAT31

PNVMCE*

PNVMR/B*

P243

P244

P245

P246

P247

P248

P249

P250

P251

P252

P253

P254

P255

P256

P257

P258

P259

P260

P261

P262

P263

P264

P265

P266

P267

P268

P269

P270

ATRESET*

DDC_SDA

RESET*

+3V3D

HDMI_RESET*

CEC

DDC_SCL

PROG/INT*

CLK27M_VADDIS

R219

0R0

0W125

0805

NF

R224

0R0

0W125

0805

C231

100N

16V

0603

C230

C201

100N

100N

16V

16V

0603

0603

P239

DGND

DGND

PWR ON RESET*

P275

C232

100N

16V

0603

C202

100N

16V

0603

+1V8D

+3V3D

NVMDA0

NVMDA1

NVMDA2

NVMDA3

NVMDA4

NVMDA5

NVMDA6

NVMDA7

NVMRB

NVMCE

NVMRB1

NVMCE1

NVMRE

NVMWP

NVMWE

NVMALE

NVMCLE

NVMCD

PCLK

RAMCKE

RAMWE

RAMCAS

RAMRAS

RAMCS

RAMDQM

RAMBA1

RAMBA0

RAMADD11

RAMADD10

RAMADD9

RAMADD8

RAMADD7

RAMADD6

RAMADD5

RAMADD4

RAMADD3

RAMADD2

RAMADD1

RAMADD0

RAMDAT0

RAMDAT1

RAMDAT2

RAMDAT3

RAMDAT4

RAMDAT5

RAMDAT6

RAMDAT7

RAMDAT8

RAMDAT9

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

RAMDAT16

RAMDAT17

RAMDAT18

RAMDAT19

RAMDAT20

RAMDAT21

RAMDAT22

RAMDAT23

RAMDAT24

RAMDAT25

RAMDAT26

RAMDAT27

RAMDAT28

RAMDAT29

RAMDAT30

RAMDAT31

PNVMCE

PNVMR/B

ATDD0

ATDD1

ATDD2

ATDD3

ATDD4

ATDD5

ATDD6

ATDD7

ATDD8

ATDD9

ATDD10

ATDD11

ATDD12

ATDD13

ATDD14

ATDD15

ATDMARQ

ATIOW

ATIOR

ATIORDY

ATDMACK

ATINTRQ

ATDA0

ATDA1

ATDA2

ATCS0

ATCS1

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HA0

HA1

HA2

HA3

HWR

HRD

HCS

HIRQ

HACK

HCS1

HIRQ1

HACK1

XO

GCLKP

GCLKA

RESET

DGND

C235

100N

16V

0603

VDDPE5VDDPF5VDDP

GNDPT5GNDPT6GNDPT8GNDP

H5

VDDPK5VDDPN5VDDPR5VDDPE7VDDPT7VDDPU7VDDPT9VDDP

GNDP

GNDP

GNDP

T10

T12

T13

V13

C236

100N

16V

0603

GNDP

GNDP

GNDP

T14

T16

U15

C237

100N

16V

0603

N3

P4

P3

R3

R4

P1

P2

N4

N1

L4

M3

L3

M1

N2

M2

L1

L2

M4

U12

V11

Y14

W13

Y13

Y12

W14

Y11

W11

U10

W9

V10

U9

V9

U8

V8

W7

Y7

Y8

W8

Y9

W18

Y18

W17

Y17

W16

Y16

W15

Y15

V14

U14

V15

V16

V17

U17

V18

U18

W6

Y6

W5

Y5

W4

Y4

Y3

Y2

W2

W3

V4

U4

V5

V6

U6

V7

Y1

W1

D2

C2

A1

B2

D3

C3

D4

C4

A4

B4

A3

B3

A2

E4

E3

F4

B1

C1

D1

F3

E2

E1

G3

F1

F2

G1

G2

B7

A7

B8

A8

B9

A9

B10

A10

B5

A5

B6

A6

C6

D6

D7

C7

C5

D8

C8

D5

C14

A14

B15

B14

C234

C233

100N

100N

16V

16V

0603

0603

K16

E10

T11

U11

E12

U13

E15

M16

R16

U16

T15

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

IC202

ZORAN VADDIS V

HS202

3319B+T410 01

209C/W

GNDPJ9GNDPK9GNDPL9GNDPM9GNDP

GNDP

GNDP

GNDP

GNDP

GNDP

GNDP

L10

J11

J12

J10

L11

K11

K12

K10

C239

C238

100N

100N

16V

16V

0603

0603

D12

U5

VDDP

VDDP-A

VDDP-A

GNDP

GNDP

GNDP

GNDP

GNDP

L12

M10

M11

M12

C240

100N

16V

0603

+3V3D

E13

L17

V12

W10

L5

A18

E9

VDDC

GNDC

GNDC

E8

E14

A19

VDDC

VDDC

VDDC

VDDC

VDDC

VDD_DAC

GNDC

GNDC

GNDC

GNDCM5GNDA

GNDA

L16

Y10

A12

A11

W12

C249

100N

16V

0603

C207

100N

16V

0603

C259

C260

C261

1N0

1N0

50V

50V

0603

0603

+3V3D

3

9

35

41

49

55

75

81

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

6

12

32

38

46

52

78

84

PF200

PF201

PF202

PF203

PF204

PF205

PF206

PF207

PF208

PF209

PF210

PF211

PF212

PF213

PF214

PF215

PF228

PF229

PF230

PF231

PF232

PF233

PF234

PF235

PF236

PF237

PF238

C262

1N0

1N0

50V

50V

0603

0603

PCLK

RAMCKE

RAMWE*

RAMCAS*

RAMRAS*

RAMCS*

RAMDQM

2

RAMDAT0

RAMDAT1

RAMDAT2

RAMDAT3

RAMDAT4

RAMDAT5

RAMDAT6

RAMDAT7

RAMDAT8

RAMDAT9

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

RAMDAT16

RAMDAT17

RAMDAT18

RAMDAT19

RAMDAT20

RAMDAT21

RAMDAT22

RAMDAT23

RAMDAT24

RAMDAT25

RAMDAT26

RAMDAT27

RAMDAT28

RAMDAT29

RAMDAT30

RAMDAT31

+3V3D

DGND

PR220

PR221

PR222

PR223

PR224

PR225

PR226

PR227

PR228

PR229

PR230

PR231

PR232

PR233

PR234

PR235

PR236

PR237

PR238

PR239

PR240

PR241

PR242

PR243

PR244

PR245

PR246

PR247

PR248

PR249

PR250

PR251

FRAMADD5

FRAMADD6

FRAMADD7

FRAMADD8

FRAMADD9

FRAMADD11

FRAMDAT8

FRAMDAT9

FRAMDAT5

FRAMDAT6

FRAMDAT7

FRAMBA0

FRAMBA1

FRAMADD10

FRAMADD0

FRAMADD1

FRAMADD2

FRAMDAT10

FRAMDAT11RAMDAT4

FLASHA19

FRAMDAT3

FLASHA21

PWR_ON_RESET*

FRAMADD4+3V3D

PNVMCE*

FRAMADD3

FLASH DECOUPLNG

C220

100N

16V

0603

+3V3D

Near ATAPI conn

C251

C264

100N

100N

16V

16V

0603

0603

DGND

C203

100N

16V

0603

DRIVE

CON203

1

XATRESET*

2

3

ATDD7

4

ATDD8

5

ATDD6

6

ATDD9

7

ATDD5

8

ATDD10

9

ATDD4

10

ATDD11

11

ATDD3

12

ATDD12

13

ATDD2

14

ATDD13

ATDD1

15

ATDD14

16

ATDD0

17

ATDD15

18

19

20

21

ATDMARQ

22

23

ATDOW*

24

25

ATDOR*

26

27

ATIORDY

28

29

ATDMACK*

30

31

ATINTRQ

32

33

ATDA1

34

35

ATDA0

36

ATDA2

37

ATCS0*

38

ATCS1*

39

40

Dublier

C3

25

A0

24

A1

23

A2

22

A3

21

A4

20

A5

19

A6

18

IC205

A7

FLASH

8

A8

7

A9

6

A10

5

A11

4

A12

3

A13

2

A14

1

A15

48

A16

17

A17

16

A18

15

A19

10

A20

9

A21

12

RP

11

WE

14

WP

26

CE

28

OE

13

VPP

C209

C211

100N

100N

16V

16V

0603

0603

DGND

C216

100N

16V

0603

+3V3D

37

VCC

GND

GND

46

27

47

VCCQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

+3V3D

DGND

On botom of board

DGND

TE28F160

L967SW

TSOP48

C263

1N0

50V

0603

29

FRAMDAT31

31

FRAMDAT29

FRAMDAT27

33

FRAMDAT25

35

FRAMDAT23

38

FRAMDAT21

40

FRAMDAT19

42

FRAMDAT17

44

FRAMDAT30

30

FRAMDAT28

32

FRAMDAT26

34

FRAMDAT24

36

FRAMDAT22

39

FRAMDAT20

41

FRAMDAT18

43

FRAMDAT16

45

PF216

PF217

PF218

PF219

PF220

PF221

PF222

PF223

PF224

PF225

PF226

PF227

PF239

PF240

PF241

PF242

+3V3D

DGND

+1V8D

DGND

ATDD0

ATDD1

ATDD2

ATDD3

ATDD4

ATDD5

ATDD6

ATDD7

ATDD8

ATDD9

ATDD10

ATDD11

ATDD12

ATDD13

ATDD14

ATDD15

ATDMARQ

ATDOW*

ATDOR*

ATIORDY

ATDMACK*

ATINTRQ

ATDA0

ATDA1

ATDA2

ATCS0*

ATCS1*

XATRESET*

C253

100UF

10V

YXF

C254

100UF

10V

YXF

+5VD

R226

1K0

0W125

0805

33R

2 7

1 8

2 7

1 8

1 8

2 7

1 8

2 7

54

33R

63

33R

33R

33R

54

33R

63

33R

33R

33R

33R

33R

63

33R

54

33R

33R

33R

63

33R

54

CLK27M_VADDIS

RP209D

RP209C

RP209B

RP209A

RP210D

RP210C

RP210B

RP210A

RP211A

RP211B

RP211C

RP211D

RP212A

RP212B

RP212C

RP212D

R238 82R 0805

R241 22R 0805

R242 22R 0805

R239 82R 0805

R243 22R 0805

R240 82R 0805

R244 33R 0805

R245 33R 0805

R246 33R 0805

R247 33R 0805

R248 33R 0805

R249 33R 0805

CLOCKS

Audio master clock (input)

Can be configured as an output or testing

MCLK_VADDIS

C252

C223

NF

100UF

100N

10V

16V

YXF

0603

C221

C222

100N

16V

0603

C224

100N

100N

16V

16V

0603

0603

VADDIS DECOUPLNG

P274

R227

1K0

0W125

0805

DGND

AMCLK OUT

C225

100N

16V

0603

4

5

7

8

10

11

13

74

76

77

79

80

82

83

85

31

33

34

36

37

39

40

42

45

47

48

50

51

53

54

56

VDDP_A

VDD_PLL

C208

C248

100N

10UF

16V

50V

0603

A16

GNDDAC-SB

VDDADC

GNDDAC-D

B20

DAC_A_B/U

DAC_B_R/V

DAC_C_G/Y

DAC_D_CVBS

DAC_E_Y

DAC_F_C

COSYNC

VIDP_10

VIDP_11

VIDP_12

VIDP_13

VIDP_14

VIDP_15

VIDP_16

VIDP_17

VIDP_18

VIDP_19

VCLKx2

ALRCLKI

ABCLKI

ALRCLKO

ABCLKO

FPCDOUT

FPCDIN

FPCCLK

FPCSTB

MODDCD

MODDSR

MODCTS

MODDTR

MODRTS

MODRD

MODTD

DUPRD

SPDATI

SPIDATO

SPICLK

SERADC0

SERADC1

SERADC2

EJTRST

GPCIO6

GPCIO7

GPCIO8

GPCIO9

GPCO10

GPCO11

GPCO12

GPCO13

GPCO14

GPCO15

GPCO16

GPCO17

GPCO18

GPCO19

GPCO20

GPAIO0

BOOTSEL0

BOOTSEL1

BOOTSEL2

TESTMODE

PLLSEL

PLLCFGP

PLLCFGA

GNDDAC-D

GNDDAC-D

C20

D20

DGND

RSET

VREF

VDP_0

VDP_1

VDP_2

VDP_3

VDP_4

VDP_5

VDP_6

VDP_7

VDP_8

VDP_9

VCLK

VSYNC

HSYNC

AMCLK

AOUT0

AOUT1

AOUT2

AOUT3

AOUT4

SPDF

RRCV

MODRI

DUPTD

2CDAT

2CCLK

PWM

EJTDI

EJTDO

EJTMS

EJTCK

YK

E17

F17

F18

G17

G18

H17

K17

D16

D17

K19

PV200

K20

PV201

L19

PV202

L20

PV203

L18

PV204

M19

PV205

M20

PV206

M18

PV207

M17

PV208

N20

PV209

N19

PV210

N18

PV211

N17

PV212

P20

PV213

P19

PV214

P18

PV215

P17

PV216

R20

PV217

R19

PV218

R18

PV219

T19

K18

PV220

R17

PV221

T20

PV222

DGND

E19

E20

P287

F20

F19

P288

G19

P289

C17

AN0

C16

AN1

J17

P290

J19

P284

H20

P285

H19

G20

J20

P286

G4

H4

H3

H1

H2

W19

U20

V20

V19

U19

Y20

Y19

W20

T3

U3

B13

C13

D13

B17