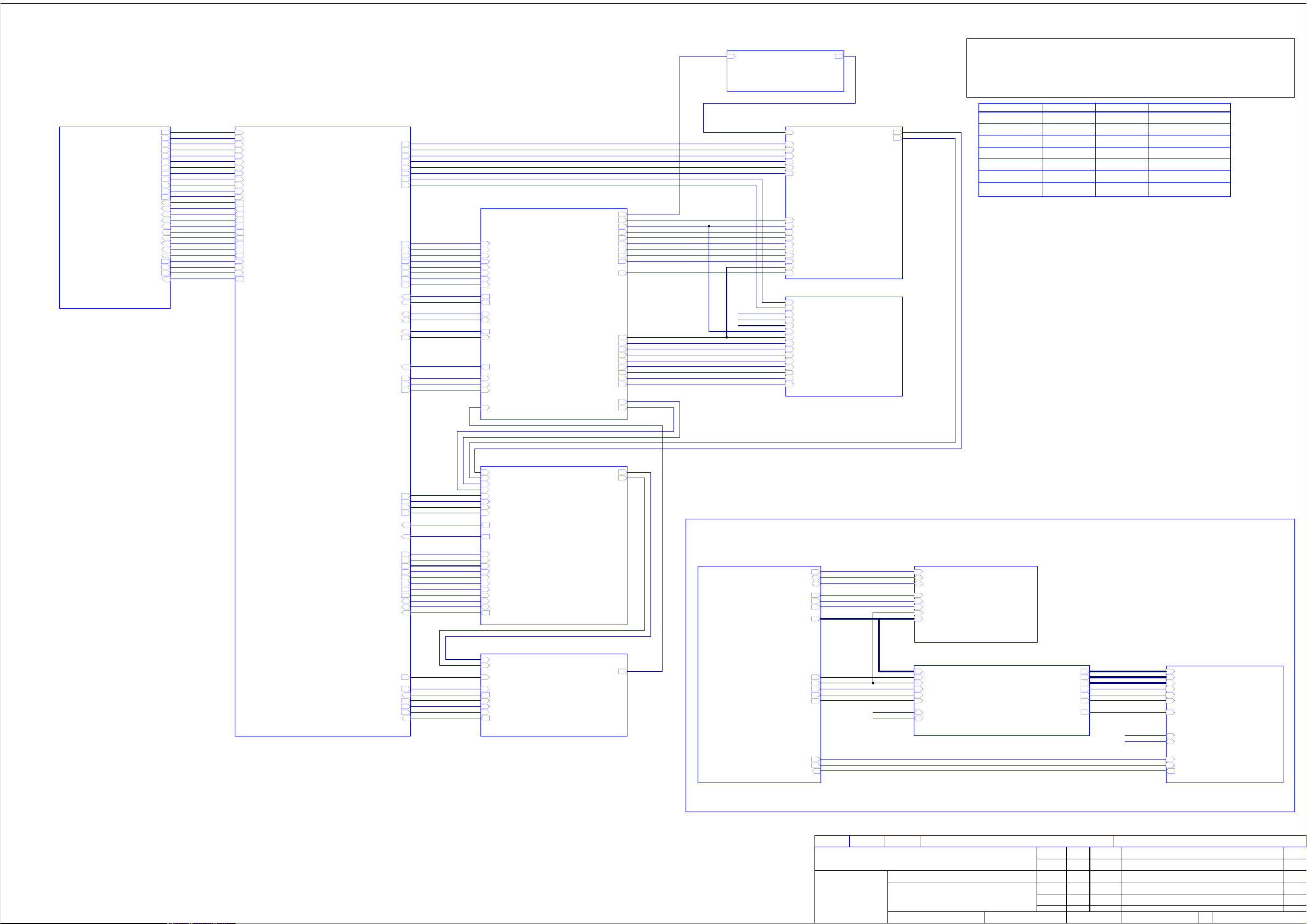

Page 1

L988C03 Front End

L988C03 Front End.Sch

FRONT END

SHEET 3

RFA

RFB

RFC

RFD

RFE

RFF

ADC_H

SPDL_SENSE-

SPDL_SENSE+

CD_MD

DVD_MD

CD_LD

DVD_LD

CD*_DVD

TRACK_S

SLED_S

SPINDLE_S

FOCUS_S

OPEN

CLOSE

IN_SW

OUT_SW

HOME_SW

DRVSB*

L988C08 Power

L988C08 Power.Sch

PSUCLK AC_PRES*

POWER

SHEET 8

AC_PRES*

L988C02 Vaddis 8

RF

VC

RF

RFA

RFB

RFC

RFD

RFE

RFF

ADC_H

SPDL_SENSESPDL_SENSE+

CD_MD

DVD_MD

CD_LD

DVD_LD

VC

CD*_DVD

TRACK_S

SLED_S

SPINDLE_S

FOCUS_S

OPEN

CLOSE

IN_SW

OUT_SW

HOME_SW

DRVSB*

L988C02 Vaddis 8.Sch

RF

RFA

RFB

RFC

RFD

RFE

RFF

ADC_H

SPDL_SENSESPDL_SENSE+

CD_MD

DVD_MD

CD_LD

DVD_LD

VC

CD*_DVD

TRACK_S

SLED_S

SPINDLE_S

FOCUS_S

OPEN

CLOSE

IN_SW

OUT_SW

HOME_SW

DRVSB*

VADDIS 8

SHEET 2

RESET*

ML_8740_0

ML_8740_3

MUTE*

ML_8740_1

ML_8740_2

PCM/DSD0

PCM/DSD1

PCM/DSD2

PCM/DSD3

DSD4

DSD5

ABCLK

ALRCLK

CLK27M_VADDIS

MCLK_VADDIS

SDA

SCL

SERIAL_RX

SERIAL_TX

HDMI_INT*

595_DATA

595_CLK

595_LATCH

RESET*

MD

MC

MD

MC

ML_8740_0

ML_8740_3

MUTE*

ML_8740_1

ML_8740_2

PCM/DSD0

PCM/DSD1

PCM/DSD2

PCM/DSD3

DSD4

DSD5

ABCLK

ALRCLK

CLK27M_VADDIS

MCLK_VADDIS

SDA

SCL

SERIAL_RX

SERIAL_TX

HDMI_INT*

595_DATA

595_CLK

595_LATCH

L988C04 Clocks & Buffers

L988C04 Clocks & Buffers.Sch

PCM/DSD0

PCM/DSD1

PCM/DSD2

PCM/DSD3

DSD4

DSD5

ABCLK

ALRCLK

CLK27M_VADDIS

MCLK_VADDIS

SDA

SCL

SERIAL_RX

SERIAL_TX

HDMI_INT*

595_DATA

595_CLK

595_LATCH

SPDIF_HDMI

PCM_DAC3/DSD3

ABCLK_DAC0

ABCLK_DAC3

ALRCLK/DSD0

ALRCLK_DAC3

MCLK_DAC0

MCLK_DAC3

GAIN_SCALING

CLOCKS

BUFFERS

SHEET 4

PCM_DAC1/DSD1

ABCLK_DAC1

ABCLK_DAC2

ALRCLK/DSD2

ALRCLK/DSD4

MCLK_DAC1

MCLK_DAC2

DSD5_DAC3

ENABLE_AV

PSUCLK

PCM_DAC0

PCM_DAC2

16/9

PSU_CLK

PCM_DAC0

PCM_DAC3/DSD3

ABCLK_DAC0

ABCLK_DAC3

ALRCLK/DSD0

ALRCLK_DAC3

MCLK_DAC0

MCLK_DAC3

GAIN_SCALING

PCM_DAC1/DSD1

PCM_DAC2

ABCLK_DAC1

ABCLK_DAC2

ALRCLK/DSD2

ALRCLK/DSD4

MCLK_DAC1

MCLK_DAC2

DSD5_DAC3

ENABLE_AV

16/9

RESET*

MD

MC

L988C05 DAC L & R

L988C05 DAC L & R.Sch

AC_PRES* SCART_LEFT

RESET*

MD

MC

ML_8740_0

ML_8740_3

MUTE*

SCART_RIGHT

DAC

L,R,Lt,Rt

SHEET 5

PCM_DAC0

PCM_DAC3/DSD3

ABCLK_DAC0

ABCLK_DAC3

ALRCLK/DSD0

ALRCLK_DAC3

MCLK_DAC0

MCLK_DAC3

PCM_DAC1/DSD1

GAIN_SCALING

L988C06 DAC LS RS C SUB

L988C06 DAC LS RS C SUB.Sch

ML_8740_1

ML_8740_2

RESET*

MD

MC

PCM_DAC3/DSD3

PCM_DAC1/DSD1

PCM_DAC2

ABCLK_DAC1

ABCLK_DAC2

ALRCLK/DSD2

ALRCLK/DSD4

MCLK_DAC1

MCLK_DAC2

DSD5_DAC3

LS,RS,C,SUB

SHEET 6

DAC

SCART_LEFT

SCART_RIGHT

SCART_RED

SCART_GREEN

SCART_BLUE

COMPOSITE

COMPOSITE_B

TRIGGER_IN*

TMDS_D2+

TMDS_D2-

TMDS_D1+

TMDS_D1-

TMDS_D0+

TMDS_D0TMDS_CK+

TMDS_CK-

DDC_SDA

DDC_SCL

HDMI_DET

SPDIF

FPDIN

FPDOUT

FPCLK

FPSEL_VFD

FPSEL_SW

IRRCV

SCART_RED

SCART_GREEN

SCART_BLUE

COMPOSITE

COMPOSITE_B

TRIGGER_IN*

TMDS_D2+

TMDS_D2TMDS_D1+

TMDS_D1TMDS_D0+

TMDS_D0TMDS_CK+

TMDS_CKDDC_SDA

DDS_SCL

HDMI_DET

REM_BUSP

REM_BUSN

SPDIF

FPDIN

FPDOUT

FPCLK

FPSEL_VFD

FPSEL_SW

IRRCV

L988C07 HDMI 1 SCART Remote

L988C07 HDMI 1 SCART Remote.Sch

SCART_LEFT

SCART_RIGHT

ENABLE_AV

16/9

SCART_RED

SCART_GREEN

SCART_BLUE

COMPOSITE

COMPOSITE_B

TRIGGER_IN*

TMDS_D2+

TMDS_D2TMDS_D1+

TMDS_D1TMDS_D0+

TMDS_D0TMDS_CK+

TMDS_CKDDC_SDA

DDC_SCL

HDMI_DET

L988C12 SPDIF & Front panel interface

L988C12 SPDIF & Front panel interface.Sch

REM_BUSP

REM_BUSN

SPDIF

FPDIN

FPDOUT

FPCLK

FPSEL_VFD

FPSEL_SW

IRRCV

HDMI 1 O/P

SCART

REMOTE IN

SHEET 7

SHEET 12

SPDIF

FRONT PANEL I/F

REM_BUSP

REM_BUSN

SPDIF_HDMI

SPDIF_HDMI

SNAP-OFF VIDEO SECTION

L988C09 Buffer & PLD

L988C09 Buffer & PLD.Sch

COMPOSITE_BA

SDA_A

SCL_A

ENC_RESET*

VIDCLK_ENC

HSYNC_ENC*

VIDB[0..7]

DIG VIDEO BUFFER

CPLD

RS232

SHEET 9

HSYNC_861B*

VSYNC_861B*

VIDCLK_SCALER

SYSCLK

SCALER_RESET*

HDMI_RESET*

SERIAL_RX_A

SERIAL_TX_A

COMPOSITE_BA

SDA_A

SCL_A

ENC_RESET*

VIDCLK_ENC

HSYNC_ENC*

VIDB[0..7]

HSYNC_861B*

VSYNC_861B*

VIDCLK_SCALER

SYSCLK

SCALER_RESET*

HDMI_RESET*

SERIAL_RX_A

SERIAL_TX_A

VIDB[0..7]

SDA_A

SCL_A

L988C10 Video Encoder

L988C10 Video Encoder.Sch

COMPOSITE_BA

SDA_A

SCL_A

VIDEO ENCODER

ENC_RESET*

VIDCLK_ENC

HSYNC_ENC*

VSYNC_861B*

VIDB[0..7]

Scaler

L988C13 Scaler.sch

VIDB[0..7]

HSYNC_861B*

VSYNC_861B*

VIDCLK_SCALER

SYSCLK

SCALER_RESET*

SDA_A

SCL_A

SHEET 10

SCALER

SHEET 13

RED[0..7]

GREEN[0..7]

BLUE[0..7]

HSYNC_HDMI*

VSYNC_HDMI*

DE_HDMI

VIDCLK_HDMI

RED[0..7]

GREEN[0..7]

BLUE[0..7]

HSYNC_HDMI*

VSYNC_HDMI*

DE_HDMI

VIDCLK_HDMI

SDA_A

SCL_A

L988C11 HDMI 2

L988C11 HDMI 2.Sch

RED[0..7]

GREEN[0..7]

BLUE[0..7]

HSYNC_HDMI*

VSYNC_HDMI*

DE_HDMI

VIDCLK_HDMI

SDA_A

SCL_A

HDMI_RESET*

SERIAL_RX_A

SERIAL_TX_A

HDMI O/P 2

SHEET 11

ITEM100 1 Blank PCB DV137 Main BoardL988PB

DRAWING TITLE

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

DV137 Top Level

Filename:

Notes:

Contact Engineer:

L988C01 Top Level.Sch

Contact Tel:

06_E029 PG 15/03/06 Issue 2 PCB ( changes only affect DV139) 2.0

05_E242 PG 08/12/05 Production R elease 1.0

INITIALS

ECO No.

Printed:

DATE

12-Jun-2006

DESCRIPTION OF CHANGE

113Sheet of

A2

DRAWING NO.

L988CT

ISSUE

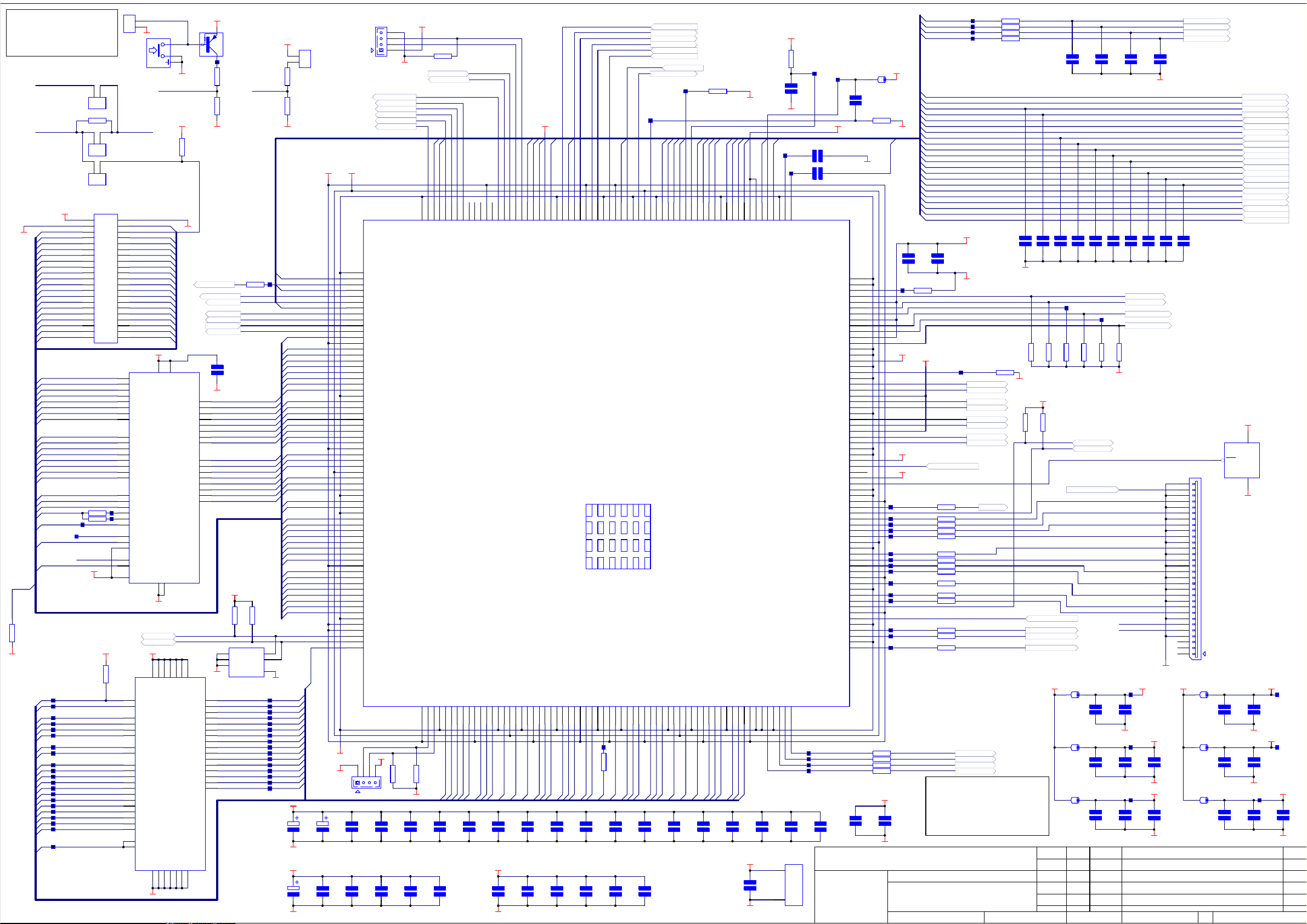

Page 2

Normal Program Debug

A

A

A

FLASH MEMCS0* MEMCS0*

MEMCS1*

SRAM not used not used MEMCS0*

DD0 pull-down pull-up pull-down

DD1 pull-down pull-down pull-up

DEBUG CONFIG

MEMCS1*

CON200

NF

CON201

NF

CON202

NF

0R0 0603

MEMCS0* FLASHCS*

DEBUG SRAM I/F

+3V3D

MEMADD19

MEMRD*

MEMDAT8

MEMDAT9

MEMDAT10

MEMDAT11

MEMDAT12

MEMDAT13

MEMDAT14

MEMDAT15

MEMADD1

MEMADD3

MEMADD5

MEMADD7

MEMADD18

MEMWR*

MEMADD12

MEMADD10

MEMADD14

MEMADD0

MEMADD1

MEMADD2

MEMADD3

MEMADD4

MEMADD5

MEMADD6

MEMADD7

MEMADD8

MEMADD9

MEMADD10

MEMADD11

MEMADD12

MEMADD13

MEMADD14

MEMADD15

MEMADD16

MEMADD17

MEMADD18

MEMADD19

NF

MEMADD20

P245

P246

P247

P248

P249

P250

P251

P252

P253

P254

P255

P256

P257

P258

P259

P260

P261

P262

P263

P264

P265

P211

FLASHCS*

RAMCKE

PCLK

RAMWE*

RAMCAS*

RAMRAS*

RAMCS*

RAMBA0

RAMBA1

RAMADD11

RAMADD10

RAMADD9

RAMADD8

RAMADD7

RAMADD6

RAMADD5

RAMADD4

RAMADD3

RAMADD2

RAMADD1

RAMADD0

RAMDQM

MEMWR*

MEMRD*

SST

R201 0R0

R202 0R0

Intel

MEMADD20

DGND

DGND

R244

4K7

0603

1

R200

1

1

CON204

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

P212

PRESET*

+3V3D

2

2

2

+3V3D

R237

4K7

0603

P213

P214

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

25

24

23

22

21

20

19

18

48

17

16

15

10

12

11

14

26

28

13

PROGRAM SWITCH

CON208

1

2

DGND

SDTA-620-N

NF

debug mode

Normal/program

SRAMCS*

Debug mode

MEMADD0

SRAMCS*

MEMDAT0

MEMDAT1

MEMDAT2

MEMDAT3

MEMDAT4

MEMDAT5

MEMDAT6

MEMDAT7

MEMADD16

MEMADD2

MEMADD4

MEMADD6

MEMADD17

MEMADD9

MEMADD8

MEMADD11

MEMADD15

MEMADD13

+3V3D

A0

A1

A2

A3

A4

A5

A6

A7

IC202

8

A8

FLASH

7

A9

6

A10

5

A11

4

A12

3

A13

2

A14

1

A15

A16

A17

A18

9

A19/NC

NC/A19

A20

RST*

WE*

WP*

CE*

OE*

NC/VPP

DGND

SDA

SCL

+3V3D

1

37

CKE

38

CLK

16

WE*

17

CAS*

18

RAS*

19

CS*

20

BA0

21

BA1

35

A11

22

A10

34

A9

33

A8

32

A7

31

A6

30

A5

29

A4

26

A3

25

A2

24

A1

23

A0

15

LDQM

39

UDQM

28

DGND

PROGRAM*

SW200

1

2

DGND

MEMADD0

+3V3D

DGND

37

47

VDD

NC/VCCQ

VSS

VSS

39VF3201

46

27

L988SW

TSOP-48

SDA

SCL

27

14

3

9

43

VDD

VDD

VDD

VDDQ

VDDQ

SDRAM

IC204

IC42S16800-6T(G)

TSOP-2 54

VSS

VSS

VSS

VSSQ

VSSQ

6

54

46

41

12

R242

4K7

0603

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

49

VDDQ

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VSSQ52VSSQ

+3V3D

DGND

DSD4

ML_8740_3

FPDIN

FPSEL_SW

FPCLK

FPDOUT

FPSEL_VFD

DGND

29

31

33

35

38

40

42

44

30

32

34

36

39

41

43

45

DGND

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

TR200

MMUN2111LT1

SOT-23

P200

R203

1K0

0603

R205

4K7

0603

Front panel

C209

100N

16V

0603

MEMDAT0

MEMDAT1

MEMDAT2

MEMDAT3

MEMDAT4

MEMDAT5

MEMDAT6

MEMDAT7

MEMDAT8

MEMDAT9

MEMDAT10

MEMDAT11

MEMDAT12

MEMDAT13

MEMDAT14

MEMDAT15

+3V3D

R224

2K2

0603

IC203A

A23SDA

2

A1

1

A0

24LC08BT/SN

SO-8

RAMDAT0

RAMDAT1

RAMDAT2

RAMDAT3

RAMDAT4

RAMDAT5

RAMDAT6

RAMDAT7

RAMDAT8

RAMDAT9

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

BOOT SELECT

+3V3D

R204

1K0

5

6

7

DGND

P266

P267

P268

P269

P270

P271

P272

P273

P274

P275

P276

P277

P278

P279

P280

P281

DGND

P288

+3V3D

DGND

+1V8D

DGND

0603

R206

4K7

0603

MEMADD1

R240

33R

FPDIN

FPSEL_SW

FPCLK

FPDOUT

FPSEL_VFD

R225

2K2

0603

SCL

WP

NF

CON203

2

debug mode

1

IN_SW

HOME_SW

OUT_SW

MEMCS1*

MEMADD15

MEMADD16

MEMADD14

MEMADD13

MEMADD12

MEMDAT15

MEMADD11

MEMDAT7

MEMADD10

MEMDAT14

MEMADD9

MEMDAT6

MEMADD8

MEMDAT13

MEMDAT5

MEMADD20

MEMDAT12

MEMWR*

MEMDAT4

MEMDAT11

MEMDAT3

MEMADD19

MEMDAT10

MEMADD18

MEMDAT2

MEMADD17

MEMDAT9

MEMADD7

MEMDAT1

MEMADD6

MEMDAT8

MEMADD5

MEMDAT0

MEMADD4

MEMRD*

MEMADD3

MEMADD2

MEMCS0*

MEMADD1

MEMADD0

RAMCKE

C259

100UF

10V

YXF

C260

100UF

10V

YXF

NF

+3V3D +1V8D

DGND

DGND

USB

C261

100UF

10V

YXF

C213

100N

16V

0603

Port 0 download

CON205

AMP

CT

RESET*

MD

MC

ML_8740_0

ML_8740_1

ML_8740_2

0

THERMAL PADS

1

GPCIO52

2

AOUT4/GPCIO53

3

GPCIO54

4

GPCIO55

5

GPCIO56

6

GPCIO57

7

GPCIO58

8

GPCIO59

9

GPCIO60

10

GPCIO17

11

MEMCS1*

12

VDDP

13

MEMAD15

14

MEMAD16

15

MEMAD14

16

MEMAD13

17

MEMAD12

18

MEMDA15

19

MEMAD11

20

MEMDA7

21

GNDP

22

MEMAD10

23

MEMDA14

24

MEMAD9

25

MEMDA6

26

MEMAD8

27

MEMDA13

28

MEMDA5

29

MEMAD20

30

VDDP

31

MEMDA12

32

MEMWR*

33

MEMDA4

34

VDDC

35

MEMDA11

36

MEMDA3

37

MEMAD19

38

GNDC

39

MEMDA10

40

MEMAD18

41

GNDP

42

MEMDA2

43

MEMAD17

44

MEMDA9

45

MEMAD7

46

MEMDA1

47

MEMAD6

48

MEMDA8

49

MEMAD5

50

VDDP

51

MEMDA0

52

MEMAD4

53

MEMRD*

54

MEMAD3

55

MEMAD2

56

MEMCS0*

57

MEMAD1

58

MEMAD0

59

GNDP

60

VDD-IP

61

VDDP

62

GPCIO61

63

GPCIO62

64

RAMCKE

USBDP

USBDN

+5VD

123

4

NF

CON206 AMP CT

VADDIS DECOUPLING

C214

100N

16V

0603

VADDIS DECOUPLING SDRAM DECOUPLING

C215

100N

16V

0603

4

3

2

1

C216

100N

16V

0603

C217

100N

16V

0603

DGND

R214

15K

0603

DGND

+5VD

C218

100N

16V

0603

C219

100N

16V

0603

R207

10K 0603

SERIAL_RX

SERIAL_TX

Port 1 debug & remote control

OPEN

CLOSE

253

254

255

256

GNDP

GPCIO51

GPCIO47

GPCIO16

VDDUSB

USBDP

USBDN

GNDUSB

65

66

67

68

R215

15K

0603

252

69

RAMADD4

C220

100N

16V

0603

C221

100N

16V

0603

GPCIO50

RAMADD4

251

70

RAMADD3

GPCIO49

RAMADD3

250

71

RAMADD5

249

GPCIO48

RAMADD5

72

RAMADD2

GPCIO13

RAMADD2

248

73

RAMADD6

247

GPCIO34

RAMADD6

74

SERIAL_RX

SERIAL_TX

246

GPCIO33

VDDP

75

RAMADD1

C222

100N

16V

0603

GPCIO42

RAMADD1

245

VDDP

RAMADD7

76

RAMADD7

243

244

GPCIO40

RAMADD0

77

78

RAMADD0

+3V3D

DGND

GPCIO39

GNDP

242

79

RAMADD8

C224

100N

16V

0603

C225

100N

16V

0603

DUPTD1

RAMADD8

+3V3_PWM

DOWNLOAD_RX

DOWNLOAD_TX

SLED_PWM

FOCUS_PWM

DRVSB*

235

236

237

238

240

239

241

DUPTD0

DUPRD0

DUPRD1

PWMCO6

PWMCO0

VDDPWMS

PWMCO5/GPCIO46

VDDC

RAMADD10

GNDC

RAMADD9

VDDP

RAMADD11

80

RAMBA1

81

82

83

84

85

86

RAMADD10

RAMADD9

RAMADD11

RAMBA1

C226

100N

16V

0603

C227

100N

16V

0603

SPINDLE_PWM

234

233

PWMCO4

GNDPWMS

RAMBA0

GNDP

87

88

RAMBA0

TRACK_PWM

231

232

PWMCO3/GPCIO44

225

228

230

226

227

229

GNDP

VDD-IP

GPCIO4

GPCIO15

PWMCO2

ICGPCIO6

ICGPCIO7

VADDIS 8

IC200

ZR36888-HLCGS

LQFP256

HS200

3319B+T410-01

20.9C/W

RAMCS1*

RAMRAS*

RAMCAS*

VDDP

RAMWE*

RAMDQM

GNDPCLK

91

RAMCAS*

PCLK

92

93

94

95

96

R236 22R

RAMWE*

RAMDQM

PCLK

C230

100N

16V

0603

C231

100N

16V

0603

89

RAMCS*

C228

100N

16V

0603

C229

100N

16V

0603

90

RAMRAS*

R210 27K 0603TRACK_PWM

P206

R212 18K 0603SLED_PWM

+3V3_VDAC

C211

100N

16V

0603

DGND

63

54

63

54

P210

P207

P208

P209

R221

TMDS_D2+

TMDS_D2-

TMDS_D1+

TMDS_D1-

TMDS_D0+

TMDS_D0-

TMDS_CK+

TMDS_CK-

33R

33R

33R

33R

33R

33R

33R

33R

MCLK_VADDIS

R213 15K 0603SPINDLE_PWM

R211 27K 0603FOCUS_PWM

DSD5

ABCLK

ALRCLK

430R 0603

DGND

C248

33P

0603

DGND

R222

4K7

0603

MCLK_VADDIS

ABCLK

ALRCLK

PCM/DSD0

R217

75R

0603

+3V3D

C249

33P

0603

R223

4K7

0603

R218

75R

0603

C202

1N0

0603

C250

C251

33P

33P

0603

0603

P241

R219

75R

0603

HDMI

DDC_SCL

DDC_SDA

COMPOSITE_B

R220

75R

0603

C203

1N0

0603

NF

C252

33P

0603

P242

R238

75R

0603

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

VID_CLK

HSYNC*

VSYNC*

C253

33P

0603

DGND

IRRCV

595_DATA

595_CLK

595_LATCH

HDMI_INT*

TRIGGER_IN*

HDMI_DET

CD*_DVD

223

220

224

221

222

VPPD

GNDC

GPCIO11

ICGPCIO4

ICGPCIO5

HDMI_DET

MUTE*

R208

P202

20K

0603

DGND

P296

DVD_LD

CD_LD

DVD_MD

CD_MDVCVC

RFF

SPDL_SENSE+

RFE

SPDL_SENSE-

RFD

ADC_H

RFC

216

214

215

217

218

219

VDDC

DVDLD

GNDADC

GPCIO32

GNDAFER

208

213

210

207

209

211

212

CDLD

BGCAP

CD_MD

ADCINF

DVDMD

OPUREF

RESLOAD

201

202

203

205

204

206

ADCINJ

ADCINE

ADCINK

ADCINH

ADCIND

GNDADC

+3V3_AFE

R209

100K

0603

P205

C208

100N

0603

DGND

P203

C200

RFA

197

196

VDDAFE

193

195

194

RFINN

ACDINA

ADCING

C201

P204

RFINP

SPDIFIN0/GPCIO65

RFB

199

200

198

ADCINB

ADCINC

VDDAFE

VDDSAFE

P297

+3V3_AFE

GNDDACBS2

GNDDAC

RSET

DAC1_U/B

VDDDAC

DAC2_V/R

DAC3_Y

VDDDAC

DAC4_Y/G

DAC5_C

VDDDAC

DAC6_CVBS

GNDDAC

GNDDAC

AVDDT18

AGNDC

HDCSET

AGNDP

HDTXD2+

HDTXD2-

AVDDP

HDTXD1+

HDTXD1-

AGNDP

HDTXD0+

HDTXD0-

AVDDP

HDTXC+

HDTXC-

AGNDP

AHGND

AHVDD

GCLKP

VDDA

RESET*

GNDA

GNDP

VDDP

AOUT5/GPCIO10

GPCIO31

VID0

VID1

VID2

VID3

VDDC

GNDC

VID4

VID5

VID6

VID7

VDDP

VCLKX2

GNDP

HSYNC*

VSYNC*

AIN0/GPCIO23

VDDP-A2

AMCLK

GNDP-A2

ABCLK

ALRCLK

AOUT0

1N00603

1N00603

XO

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

C268

10N

50V

0603

DGND

+3V3_PWM

L206

600R@100MHz

R243

0R0 0805

RF

+1V8_HD

+1V8_HDPLL

+1V8_PLL

DRVSB*

CD*_DVD

DVD_LD

CD_LD

DVD_MD

DGND

P295

P289

P215

P216

P217

P218

P219

P220

P221

P222

P223

P224

P225

P227

P228

P229

CD_MD

RFF

SPDL_SENSE+

RFE

SPDL_SENSERFD

ADC_H

RFC

RFB

RFA

RF

OPEN

CLOSE

IN_SW

OUT_SW

HOME_SW

C210

100N

16V

0603

R216 390R 0603

+3V3_HD

TMDS_D2+

TMDS_D2-

TMDS_D1+

TMDS_D1-

TMDS_D0+

TMDS_D0-

TMDS_CK+

TMDS_CK-

CLK27M_VADDIS

R241 33R

1 8

RP200A

2 7

RP200B

RP200C

RP200D

1 8

RP201A

2 7

RP201B

RP201C

RP201D

R226 33R

R227 33R

R228 33R

R229 33R

R230 33R

R231 33R

DIGITAL AUDIO

600R@100MHz

+1V8D

L200

VDDPCLK

RAMDAT8

GNDP

RAMDAT7

RAMDAT9

RAMDAT6

VDDP

RAMDAT10

RAMDAT5

RAMDAT11

GNDP

RAMDAT4

VDDC

RAMDAT12

GNDC

RAMDAT3

VDDP

RAMDAT13

RAMDAT2

RAMDAT14

GNDP

RAMDAT1

RAMDAT15

RAMDAT0

VDDP

GPCIO20/AIN4

GNDP

AOUT3

SPDIFIN1/GPCIO70

SPDIFOUT

AOUT2

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

RAMDAT8

RAMDAT7

RAMDAT9

RAMDAT6

RAMDAT10

RAMDAT5

RAMDAT11

RAMDAT4

RAMDAT12

RAMDAT3

RAMDAT13

RAMDAT2

RAMDAT14

RAMDAT1

RAMDAT15

RAMDAT0

C232

C234

C236

C237

100N

16V

0603

C233

100N

16V

0603

100N

16V

0603

C235

100N

16V

0603

100N

16V

0603

100N

16V

0603

C239

100N

16V

0603

+3V3D

DGND

C238

100N

16V

0603

123

124

C240

100N

16V

0603

125

AOUT1

126

127

128

IC203B

8

VCC

4

GND

24LC08BT/SN

SO-8

C241

100N

16V

0603

P283

P284

P285

P286

R232 33R

R233 33R

R234 33R

R235 33R

C269

100N

16V

0603

DRAWING TITLE

C270

100N

16V

0603

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

udio channel PCM mode DSD mode

0 L / R (of 5.1 o/p) L

+3V3D

+1V8D

C271

100N

16V

0603

1 LS / RS R

2 Centre / Sub LS

3 2 ch downmix RS

4 not used Centre

5 not used SUB

DV137 Vaddis 8

L988C02 Vaddis 8.Sch

Filename:

Notes:

Contact Engineer:

Mark Tweedale

markt@arcam.co.uk

PCM/DSD1

PCM/DSD2

SPDIF

PCM/DSD3

Contact Tel:

L202 600R@100MHz

L203 600R@100MHz

06_E093 MJT 12/06/06 Add heatsink to top of Vaddis 3.1

06_E036 PG 20/03/06 Add thermal attac h pads to IC200 3.0

06_E029 PG 15/03/06 Issue 2 PCB ( changes only affect DV139) 2.0

05_E242 PG 08/12/05 Production R elease 1.0

ECO No.

01223 203210 (direct)

01223 203200 (switch)

INITIALS

Printed:

C262

10uF

10V

1206

C263

10uF

10V

1206

C264

10uF

10V

1206

DATE

12-Jun-2006

TRACK_S

SLED_S

SPINDLE_S

FOCUS_S

C258

27N

0603

DGND

C254

C255

33P

33P

0603

0603

SCART_BLUE

SCART_RED

SCART_GREEN

COMPOSITE

R239

75R

0603

SDA

SCL

Spare

Spare

Spare

+1V8_PLL

P290

C242

100N

16V

0603

DGND

+1V8_HDPLL

P287

C243

100N

16V

0603

DGND

+1V8_HD

P292

C244

100N

16V

0603

DGND

DESCRIPTION OF CHANGE

213Sheet of

TRACK_S

SLED_S

SPINDLE_S

FOCUS_S

C204

1N0

0603

C256

C257

33P

33P

0603

0603

Place C257 and C248 very close to V888

RESET

DGND

C205

1N0

50V

0603

C206

1N0

50V

0603

PRESET*

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

+3V3D

CON207

RST

To video board

MOLEX

52806

L201 600R@100MHz

L204 600R@100MHz

L205 600R@100MHz

DRAWING NO.

A2

C265

10uF

10V

1206

C266

10uF

10V

1206

C267

10uF

10V

1206

+3V3D

DGND

DRVSB*

CD*_DVD

DVD_LD

CD_LD

DVD_MD

CD_MD

VC

RFF

SPDL_SENSE+

RFE

SPDL_SENSERFD

ADC_H

RFC

RFB

RFA

RF

OPEN

CLOSE

IN_SW

OUT_SW

HOME_SW

IC201

VCC

LM809M3-2.93

SOT-23

GND

+3V3_AFE

C245

100N

16V

0603

DGND

+3V3_PWM

C246

100N

16V

0603

DGND

+3V3_HD

P293

C247

100N

16V

0603

L988CT

P291

P294

DGND

C207

1N0

50V

0603

ISSUE

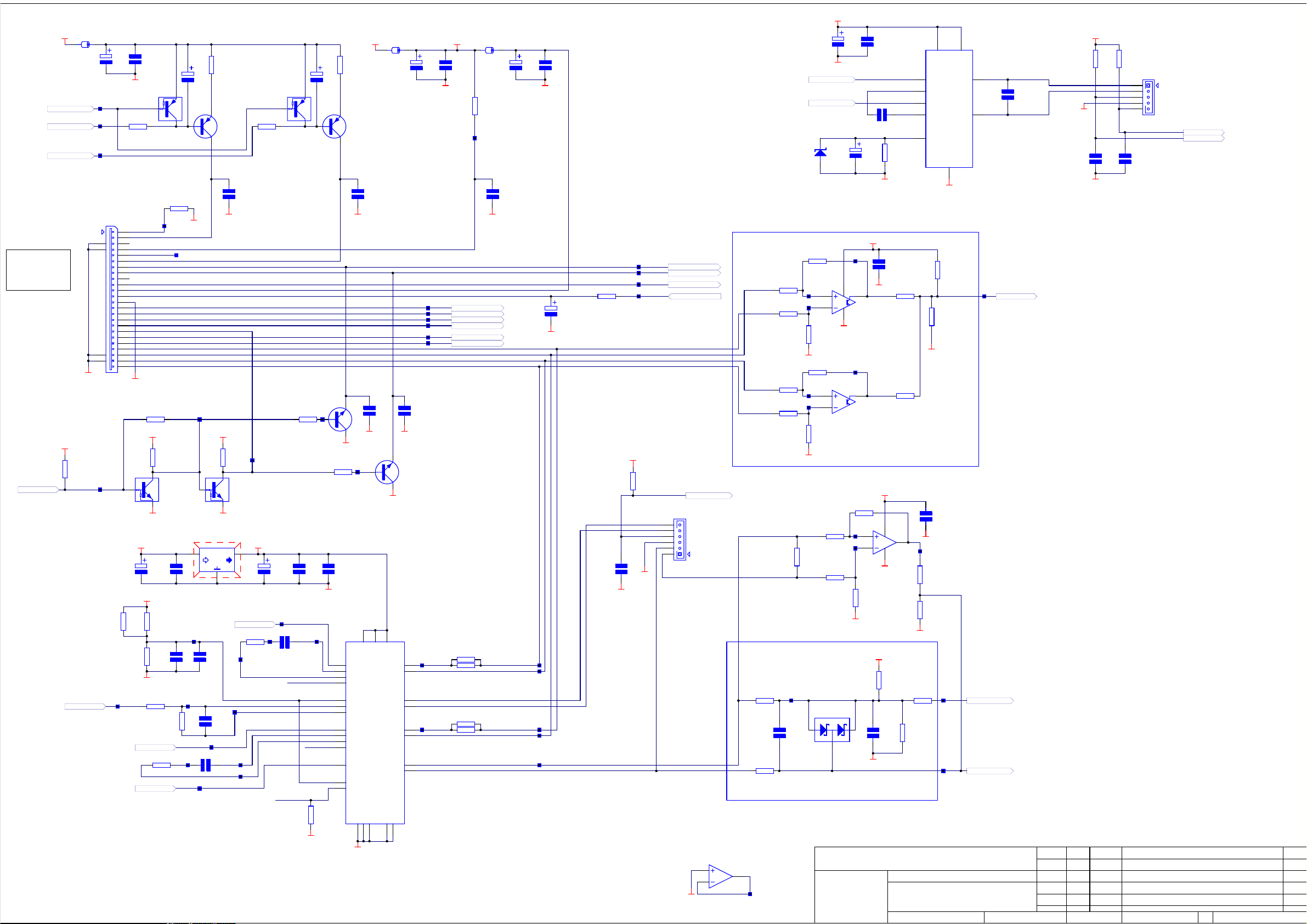

Page 3

LASER DRIVERS

+3V3D

DRVSB*

DVD_LD

CD_LD

L300 600R@100MHz

P300

P301

P302

C300

100UF

10V

YXF

DGND

MMUN2111LT1

SOT-23

DVRSB*

R300

220R

0603

+3V3_LD

C303

100N

16V

0603

TR300

OPU

CON300

1

GND_LD

2

DVDLD_OUT

3

28

4

R322

4K7

0603

NF

SLED_S

DGND

27

26

25

MOLEX

52559

OPU connector pin out

is reversed with respect

to OPU, since FFC

cable has contact

surfaces on SAME

+3V3D DGND

CD*_DVD

0=DVD,1=CD DGND

Motor driver now has its own regulator

Use +3V3D because Vc must be = VDDPW M/2

OPU_HFM

5

OPU_MD

CDLD_OUT

6

7

CD_MD

DVD_MD

8

9

10

RFE

11

+5V_OPU

12

OPU_VREF

13

14

RFF

15

RFB

16

RFA

17

RF

18

CD_DVD_SW

19

RFD

20

RFC

21

22

23

24

DGND

R313

0R0 0603

+5VD

P310

DGND

+12VD

C335

220UF

16V

YXF

+3V3D

R345

R343

100R

47K

0W063

0603

0603

NF

R346

100R

0W063

0603

DGND

R318

P343 P344

10K 0603

TRACK_S

R319

10K 0603

SPINDLE_S

R312

0R0 0805

P361

P305

NF

R314

470R

0805

0W125

TR304

MMUN2211LT1

SOT-23

DVD

DGND

C334

100N

16V

0603

C310

100N

16V

0603

R351

6K8

0603

C317

47UF

35V

YK

P304

HS300A

PF752

23.7C/W

P328

0603

C325

P346

R302

10R

0W125

0805

TACTTACT+

FACT+

FACT-

C311

100N

16V

C327

4N7

50V

0603

100P

0603

TR302

BC327

TO-92

DGND

+5VD

R321

470R

0805

0W125

TR310

MMUN2211LT1

SOT-23

DGND

REG300

L7805CV

TO-220

+5

P347

C320

47P

50V

0603

FOCUS_S

P329

P348

P349P345

P350

R301

220R

0603

P306

1=CD,0=DVD

+5VM

R344

47K 0603

TR301

MMUN2111LT1

SOT-23

C326

220UF

16V

YXF

P331

C324

DVRSB*

R323

3K3

0603

100P

0603

FACT-

C312

100N

16V

0603

VC2

TACT-

DGND

P307

KTC2875

SOT-23

DGND

P332P330

R320

1K0

0603

CD

C318

47UF

35V

YK

TR308

R309

3K3

0603

C313

100N

16V

0603

26

25

24

20

23

27

28

R303

10R

0W125

0805

1

3

7

4

5

6

+5VD

TR303

BC327

TO-92

C321

47P

50V

0603

DGND

DGND DGND

P309

9

8

VCC

VINFC

CFCERR12VOFC+

CFCERR2

VNFFC

VINSL+

VINSLVOSL

VINTK

CTKERR1

CTKERR2

VNFTK

VINLD

BIAS

STBY

PGND

PGND

PREGND

19

10

22

DGND

L302 600R@100MHz

C301

100UF

10V

YXF

C307

100N

16V

0603

C308

100N

16V

0603

TR309

KTC2875

SOT-23

MOTOR DRIVER

21

IC301

PVCC1

PVCC2

13

VOFC-

14

11

VOSL-

12

VOSL+

16

VOTK-

15

VOTK+

18

VOLD-

17

VOLD+

GNDHS29GNDHS

30

BA5954FP-E2

HSOP-28

+5VRFA

DGND

P311

P312

P313

P314

P315

P316

R304 1R0 0805

R305 1R0 0805 FACT-

P333

SLEDSLED+

R306 1R0 0805

R307 1R0 0805

P351

C304

100N

16V

0603

RFF

RFB

RFA

RF

RFD

RFC

L303 600R@100MHz

R308

10R

0W063

0603

P303

C305

100N

16V

0603

DGND

SPDLSPDL+

C302

100UF

10V

YXF

P335

FACT+

TACTTACT+

P336

DGND

DGND

P356

+5V_OPU

C306

100N

16V

0603

C319

47UF

35V

YK

P354

P355

Close to OPU

R325

33R

0603

P317

P318

P319

P320

+3V3D

R317

10K

0603

SLED & SPINDLE

C314

100N

16V

DGND

0603

DGND

CD_MD

DVD_MD

RFE

VC

CON302

6

5

4

3

2

1

JST

PH

HOME_SW

SPDL_OUT-

DGND

+12VD

C332

C329

100N

100UF

16V

25V

0603

YK

DGND

R311

15K

0W063

0603

R339

3K3

0603

NF

R340

3K3

0603

NF

IC302A

1

LM358AM

SO-8

NF

R352

120R

0W125

0805

NF

Filename:

Notes:

Contact Engineer:

5

3

6

9

4

DGND

DGND

P342

R333

1K0

0603

R324

6K8

0603

DGND

R310

2K2

0W063

0603

NF

L988C03 Front End.Sch

Mark Tweedale

markt@arcam.co.uk

CLOSE

OPEN

DZ300

BZX84C

5V6

SOT-23

OFFSET CANCELLATION CCT NOT USED

R335

220K

0603

NF

R326

TACT+

1K0 0603

NF

R327

TACT-

1K0 0603

NF

R328

FACT+

1K0 0603

NF

R329

FACT-

1K0 0603

NF

BEMF CCT 2

BEMF CCT 1 NOT USED

R330

1K0

0W063

0603

NF

C328

22N

16V

0603

NF

R334

1K0

0W063

0603

NF

IC302B

5

7

6

LM358AM

SO-8

P308

P358

DGND

DGND

R347

1R0

0805

R336

220K

0603

P321

P322

R337

220K

0603

NF

P323

P324

R338

220K

0603

NF

D300

BAT54S

SOT-23

NF

3 1

2

DGND

NF

5 7

6

R331

0R0

0603

R332

0R0

0603

DRAWING TITLE

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

C333

10N 50V

0603

C331

47UF

35V

YK

DGND

+5VM

C309

P325

100N

16V

0603

R348

470K

0603

NF

P340

P326

P341

R349

470K

0603

NF

DGND

3

2

+3V3D

DGND

+5VD

DGND

R350

39R

0W125

0805

C316

100N

16V

0603

NF

NF

84

84

IC300A

LM393M

SO-8

NF

IC300B

LM393M

SO-8

NF

DGND

DV137 Front End

8

IC303

VCC17VCC2

2

OUT1

IN1

P1

IN2

P2

Vz

C315

100N

16V

0603

DGND

R342

360R

0W063

0603

NF

R341

360R

0W063

0603

10

OUT2

GND

1

LB1641

SIP-10

P327

BACK-EMF CIRCUIT

P359

SPDL_SENSE-

P360

SPDL_SENSE+

Contact Tel:

C330

100N

16V

0603

ADC_H

01223 203210 (direct)

01223 203200 (switch)

06_E093 MJT 12/06/06 None to this sheet. Add heats ink to top of Vaddis 3.1

06_E036 PG 20/03/06 Add thermal attac h pads to IC200 3.0

06_E029 PG 15/03/06 Issue 2 PCB ( changes only affect DV139) 2.0

05_E242 PG 08/12/05 Production R elease 1.0

ECO No.

TRAYTRAY+

INITIALS

Printed:

DGND

+3V3D

DGND

12-Jun-2006

R315

10K

0603

C322

1N0

50V

0603

DATE

R316

10K

0603

TRAY

CON301

1

2

3

4

5

JST

PH

C323

1N0

50V

0603

DESCRIPTION OF CHANGE

313Sheet of

IN_SW

OUT_SW

A2

DRAWING NO.

ISSUE

L988CT

Page 4

A

REG400

C402

100N

16V

0603

LM1117MPX-3.3

SOT-223

+3V3

X400

27MHz

HC49

PLLSEL

+5VD

DGND DGND

C400

27P

100V

0805

C401

DGND

27P

100V

0805

CLOCK GENERATOR

+3V3PLL

C423

100UF

10V

YXF

12

1

VDD3

VDD1

7

XTI

8

XTO

14

FSEL

16

NC

2

VSS1

IC401

SM8707E

VSOP-16

VSS3

11

C404

100N

16V

0603

DGND

C405

100N

16V

0603

5

6

VDD2

VSS2

MO1

MO2

AO1

AO2

SO1

SO2

C406

100N

16V

0603

3

4

9

10

13

15

R400

75R 0603

P402

R410

P401

100R 0603

P403

R411

100R

0603

P404

CLK27M_VADDIS

P406

STOP_DIV2* STOP_DIV8*

P405

+3V3D

P411

4

D

CLK

Q

SD*

!Q

RD*

74LVC74AD

1

S0-14

IC403A

5

P409

6

P410

100R 0603

R412

100R 0603

udio master clock frequency for differ ent sample rates

Fs Master clock frequency PLLSEL DIV0* DIV2* DIV8*

32kHz 12.288MHz (384 x Fs) 1 1 0 1

44.1kHz 11.2896MHz (256 x Fs) 0 1 0 1

48kHz 12.288MHz (256 x Fs) 1 1 0 1

88.2kHz 22.5792MHz (256 x Fs) 0 0 1 1

96kHz 24.576MHz (256 x Fs) 1 0 1 1

176.4kHz 22.5792MHz (128 x Fs) 0 0 1 1

192kHz 24.576MHz (128 x Fs) 1 0 1 1

DSD 44.1k 2.8224MHz (64 x Fs) 0 1 1 0

2

3

CLOCK DIVIDER

P412

R413

AUDIO CLOCK BUFFERS

DGND

54

RP402D

33K

R404

75R 0603

R405

75R 0603

R406

75R 0603

R407

75R 0603

MCLK_DAC0

MCLK_DAC1

MCLK_DAC2

MCLK_DAC3

Close to DACs

DGND

IC408B

19

OE*

17

A0

15

A1

13

A2

11

A3

74LVC244APW

TSSOP-20

MCLK_DACS

IC407B

19

OE*

17

A0

15

A1

13

A2

11

A3

74LVC244APW

TSSOP-20

R434

0R0

To allow testing with Vaddis PLL enabled

0603

NF

I2S_MODE*

2 3

IC405A

SO-14

1

74LVC125AD

SO-14

5 6

IC405B

4

74LVC125AD

SO-14

9 8

74LVC125AD

10

IC405C

R418

Option to allow 5.6448MHz clock if required

+3V3D

10

12

D

SD*

11

CLK

RD*

74LVC74AD

13

S0-14

Q

!Q

IC403B

9

P467

8

P469

P468

R408

100R 0603

100R 0603

NF

R409

100R 0603

P470

+3V3D

P473

4

2

D

3

CLK

Q

SD*

!Q

RD*

74LVC74AD

1

S0-14

IC400A

5

P471

6

P472

R427

100R 0603

R428

100R 0603

DIV2*

P474

DIV8*

DIV0*

P475

P413

P414

R436

47R 0603

R432

47R 0603

R433

47R 0603

DGND

P415

R437

10K

0603

P422

3

P424

Y0

5

Y1

7

P425

Y2

9

Y3

P423

P416 P419

3

Y0

5

Y1

7

Y2

9

Y3

P417 P421

P418

R401

75R 0603

R402

75R 0603

R403

75R 0603

MCLK_HDMI

MCLK_VADDIS

RP402A

33K

1 8

RP402B

33K

2 7

63

RP402C

33K

PCM_DAC0/DSD0

R440

0R0

0603

Close to IC413

20

10

+3V3D

DGND

P407

R438

10K

0603

I2S_MODE*

TR400

MMUN2211LT1

SOT-23

DGND

P496

R441

0R0

0603

NF

IC403C

VCC

C416

100N

16V

GND

0603

74LVC74AD

S0-14

DGND

DGND

14

7

P400

I2S/DSD MUX

Close to DACs

IC411A

1

OE*

2

A0

4

A1

6

A2

8

A3

74LVC244APW

TSSOP-20

IC411B

19

OE*

17

A0

15

A1

13

A2

11

A3

74LVC244APW

TSSOP-20

PCM_DAC0

PCM_DAC2

Close to DACs

IC413A

1

OE*

2

A0

4

A1

6

A2

8

A3

74LVC244APW

TSSOP-20

IC413B

19

OE*

17

A0

15

A1

13

A2

11

A3

74LVC244APW

TSSOP-20

C417

100N

16V

0603

18

P452

Y0

16

P453

Y1

14

P454

Y2

12

P455

Y3

3

Y0

5

Y1

7

Y2

9

Y3

18

P456

Y0

16

P457

Y1

14

P458

Y2

12

P459

Y3

3

Y0

5

Y1

7

Y2

9

Y3

Could use IC408B for this - depends on layout

Setting DIRECT_MCLK* low allows

master clock to be sent direct to DAC in

DSD mode (instead of via vaddis) f or

improved jitter in DSD mode.

This may be removed from the design if it

is found to adversly affect jitter in PCM

IC412B

16

VCC

GND

74HC151D

SO-16

C418

100N

16V

8

0603

RP400A

RP400B

RP400C

RP400D

RP401A

RP401B

RP401C

RP401D

IC413C

20

VCC

10

GND

74LVC244APW

TSSOP-20

1 8

2 7

1 8

2 7

C408

100N

16V

0603

100R

100R

100R

63

100R

54

100R

100R

100R

63

100R

54

+3V3D

DGND

IC406C

20

VCC

10

GND

74LVC244APW

TSSOP-20

ALRCLK/DSD0

ALRCLK/DSD2

ALRCLK/DSD4

ALRCLK_DAC3

C403

100N

16V

0603

C409

100N

16V

0603

ABCLK_DAC0

ABCLK_DAC1

ABCLK_DAC2

ABCLK_DAC3

C419

100N

16V

0603

IC404C

14

VCC

7

GND

74LVC74AD

S0-14

DAC3 is PCM only

C420

C424

100N

100N

16V

16V

0603

0603

IC411C

VCC

C421

100N

16V

GND

0603

74LVC244APW

TSSOP-20

P460

2

3

+3V3D

20

10

D

CLK

+3V3D

4

1

C427

100N

16V

0603

C422

100N

16V

0603

P477

Q

SD*

!Q

RD*

74LVC74AD

S0-14

PSU CLOCK DIVIDER

P461

+3V3D

P462

IC404A

5

6

595_DATA

595_CLK

595_LATCH

C428

100N

16V

0603

ITEM400 1 Pad Dam ping 7.5x6x3MM RubberE828AP Fit on one side of XTAL (see assembly drawing)

ITEM401 1 INSULATING PAD FOR HC49 CRYSTALSF087 Fit to X400 to insulate from PCB

DRAWING TITLE

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

10

D

CLK

SD*

!Q

RD*

74LVC74AD

13

S0-14

C430

100N

16V

0603

Q

P493

IC404B

9

8

P494

P495

+3V3D

DGND

+3V3D

DGND

C431

100N

16V

0603

12

11

+3V3D

C429

100N

16V

0603

DV137 Clocks & Buffers

Filename:

Notes:

Contact Engineer:

P465

PSUFS0

PSUFS1

IC414A

DS14Q0

SHCP11Q2

STCP12Q3

MR10Q5

OE13Q6

74HC595D

SO-16

IC415A

DS14Q0

SHCP11Q2

STCP12Q3

MR10Q5

OE13Q6

74HC595D

SO-16

DGND

L988C04 Clocks & Buffers.Sch

Mark Tweedale

markt@arcam.co.uk

DGND

Q1

Q4

Q7

Q7'/DO

Q1

Q4

Q7

Q7'/DO

IC406B

19

17

15

13

11

74LVC244APW

TSSOP-20

OE*

A0

A1

A2

A3

4

3

2

1

15

14

13

12

11

10

9

7

15

1

2

3

4

5

6

7

9

15

1

2

3

4

5

6

7

9

IC412A

I0

I1

I2

I3

I4

I5

I6

I7

S0

S1

S2

E

74HC151D

SO-16

P408

P486

P487

P488

P489

P490

P491

P492

P420

P463

P464

Y0

Y1

Y2

Y3

Contact Tel:

5

Y

6

!Y

PLLSEL

DIV0*

DIV2*

DIV8*

STOP_DIV2*

STOP_DIV8*

DSD_MODE*

MCLK_DIRECT*

PSUFS0

PSUFS1

3

5

7

9

DGND

01223 203210 (direct)

01223 203200 (switch)

R426

P466

100R 0603

PSUCLK SHOULD BE 44.1kHz OR 48kHz

Fs PSUFS1 PSUFS0 PSUCLK

44.1kHz 0 0 44.1kHz

48kHz 0 0 48kHz

88.2kHz 0 1 44.1kHz

96kHz 0 1 48kHz

176.4kHz 1 0 44.1kHz

192kHz 1 0 48kHz

others 1 1 OFF

(use this for 32kHz & DSD mode)

GAIN_SCALING

16/9

ENABLE_AV

10

12

D

SD*

11

CLK

RD*

74LVC74AD

13

S0-14

06_E093 MJT 12/06/06 None to this sheet. Add heats ink to top of Vaddis 3.1

06_E036 PG 20/03/06 Add thermal attac h pads to IC200 3.0

06_E029 PG 15/03/06 Issue 2 PCB ( changes only affect DV139) 2.0

05_E242 PG 08/12/05 Production R elease 1.0

ECO No.

!Q

Q

IC400B

9

8

INITIALS

Printed:

PSUCLK

DGND

12-Jun-2006

IC407A

1

OE*

2

A0

4

A1

6

A2

8

A3

74LVC244APW

TSSOP-20

DATE

SPDIF_HDMI

HDMI_INT*

SERIAL_RX

SERIAL_TX

1

18

Y0

2

16

Y1

4

14

Y2

6

12

Y3

8

DGND

DESCRIPTION OF CHANGE

413Sheet of

DSD5_HDMI

DSD4_HDMI

SPDIF_HDMI

PCM/DSD2_HDMI

PCM/DSD3_HDMI

PCM/DSD1_HDMI

PCM/DSD0_HDMI

ALRCLK_HDMI

ABCLK_HDMI

MCLK_HDMI

HDMI_INT*

Check power

IC408A

OE*

A0

A1

A2

A3

74LVC244APW

TSSOP-20

+5VD

+3V3D

Y0

Y1

Y2

Y3

A2

Spare

18

16

14

12

DGND

DRAWING NO.

To video board

DGND

12 11

13

CON400

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

IC405D

74LVC125AD

SO-14

L988CT

MOLEX

52806

ISSUE

I2S/DSD BUFFERS

IC409A

1

14

7

OE*

2

A0

4

A1

6

A2

8

A3

74LVC244APW

TSSOP-20

IC409B

19

OE*

17

A0

15

A1

13

A2

11

A3

74LVC244APW

TSSOP-20

IC410A

1

OE*

2

A0

4

A1

6

A2

8

A3

74LVC244APW

TSSOP-20

IC410B

19

OE*

17

A0

15

A1

13

A2

11

A3

74LVC244APW

TSSOP-20

IC406A

1

OE*

2

A0

4

A1

6

A2

8

A3

74LVC244APW

TSSOP-20

C407

100N

16V

0603

C412

100N

16V

0603

+3V3D

DGND

C426

100UF

10V

YXF

P426

P427

P428

P429

P430

P431

P478

P479

IC415B

VCC

GND

74HC595D

SO-16

IC405E

VCC

GND

74LVC125AD

SO-14

DGND

DGND

DGND

DGND

DGND

16

8

ALRCLK

ABCLK

PCM/DSD0

PCM/DSD1

PCM/DSD2

PCM/DSD3

DSD4

DSD5

+3V3D

C425

100UF

10V

YXF

DGND

IC414B

VCC

GND

74HC595D

SO-16

18

Y0

16

Y1

14

Y2

12

Y3

3

Y0

5

Y1

7

Y2

9

Y3

18

Y0

16

Y1

14

Y2

12

Y3

3

Y0

5

Y1

7

Y2

9

Y3

18

Y0

16

Y1

14

Y2

12

Y3

16

8

IC410C

20

VCC

10

GND

74LVC244APW

TSSOP-20

R444

P476

R414 100R 0603

P432

P433

R415 100R 0603

P434

P435

R416 47R 0603

R417 47R 0603

P436

P437

P438

P439

P440

P441

P442

P443

P480

P481

P482

P483

IC400C

VCC

C410

100N

16V

GND

0603

74LVC74AD

S0-14

C413

100N

16V

0603

RP403A

1 8

RP403B

2 7

RP403C

RP403D

RP404D

RP404C

RP404B

2 7

RP404A

1 8

RP405A

1 8

RP405B

2 7

RP405C

RP405D

14

7

IC409C

VCC

GND

74LVC244APW

TSSOP-20

100R0603

100R

100R

100R

63

100R

54

100R

54

100R

63

100R

100R

100R

100R

100R

63

100R

54

C411

100N

16V

0603

20

10

ALRCLK_PSU

P444

P446

P485

MCLK_DIRECT*

C414

100N

16V

0603

ALRCLK_DACS

ALRCLK_HDMI

ABCLK_DACS

ABCLK_HDMI

PCM/DSD0_HDMI

PCM_DAC1/DSD1

PCM/DSD1_HDMI

PCM_DAC2/DSD2

PCM/DSD2_HDMI

PCM_DAC3/DSD3

PCM/DSD3_HDMI

DSD4_DAC

DSD4_HDMI

DSD5_DAC3

DSD5_HDMI

MCLK_DACS

IC407C

20

VCC

10

GND

74LVC244APW

TSSOP-20

DSD_MODE*

+3V3D

R439

10K

0603

DGND

C415

100N

16V

0603

TR401

MMUN2211LT1

SOT-23

IC408C

VCC

GND

74LVC244APW

TSSOP-20

Page 5

+5VA

DGND

ALRCLK_DAC3

PCM_DAC3/DSD3

RESET*

C500

10UF

35V

SGET

+3V3A

600R@100MHz

ABCLK_DAC3

MCLK_DAC3

MD

MC

ML_8740_3

RESET*

P511

C512

C513

100N

16V

0603

C501

10UF

35V

SGET

P500

P501

P502

P503

P520

+3V3_DAC3

P504

P505

P506

DGND

C514

100N

16V

0603

C515

100N

16V

0603

26

27

28

23

24

25

22

1

2

3

5

4

6

100N

16V

0603

L500

DGND

MD

MC

+3V3_DAC3

Fit for 8740

R564

0R0

0603

This design can accept WM8741. Fir st

prototypes will use WM8740

LRCKIN

DIN

BCKIN

SCLK

MD/DM0

MC/DM1

ML/I2S

CSBIOW

MODE

MODE8X

DIFFHW

MUTEB

RSTB*

DGND

NOTE Audio outputs are not inverted like

they were in previous designs, so

software must not invert phase

DAC 3

9

20

15

8

AVDD

DVDD

AVDDL

AVDDR

VOUTL+

VOUTL-

VOUTR+

VOUTR-

VMIDL

VMIDR

ZERO

DGND

AGNDL

AGNDR

AGND

7

XWM8740EDS

19

10

14

SSOP-28

IC500

17

16

12

13

18

11

21

DGND

R530

10K

0603

DGND

35V

SGET

1

2

C504

10UF

+3V3_DAC3

NF

C521

100N

100N

100V

16V

0603

MKS2

Useful for drop-out test

CON500

HARWIN

M20-973

NF

C563

10UF

35V

C505

SGET

C522

100N

16V

0603

C564

100N

100V

MKS2

P507

C535

100P

100V

0805

P508

C536

100P

100V

0805

P509

P522

2nd order Bessel filter, Av=1

R500

3K3

0805

DGND

R501

3K3

0805

DGND

R502

3K3

0805

DGND

R507

3K3

0805

DGND

FILTER

C539

2N2

100V

FKP2

C540

2N2

100V

FKP2

C541

2N2

100V

FKP2

C543

2N2

100V

FKP2

R503

3K3

0805

R504

3K3

0805

R516

R517

680R

0805

680R

0805

+12VA

C502

10UF

35V

SGET

DGND

R518

680R

0805

DGND

C506

10UF

35V

SGET

-12VA

R520

680R 0805

C547

680P

100V

FKP2

C548

680P

100V

FKP2

C516

100N

16V

0603

C523

100N

16V

0603

3

2

5

6

IC502A

84

1

OPA2134UA

SO-8

C549

680P

FKP2

100V

R505

3K3 0805

GAIN_SCALING

1=HDCD gain, 0=normal

IC502B

OPA2134UA

SO-8

7

C551

680P

100VFKP2

R509

3K3 0805

OUTPUT BUFFER

Gain of -2.2 for HDCD, otherwise -1.1

R525

10K

0805

IC506A

DG413DY

P512

P525

P513

R526

10K

0805

SO-16

1

R527

10K

0805

DGND

IC506B

DG413DY

SO-16

8

23

67

R524

10K

0805

R532

10K

0805

+12VA

DGND

P514

DGND

DGND

-12VA

P515

DGND

C517

100N

16V

0603

2

3

C524

100N

16V

0603

6

5

IC503A

84

1

OPA2134UA

SO-8

IC503B

7

OPA2134UA

SO-8

R546

11K

R534

C555

33P

100V

0805

P516 P518

C556

33P

100V

0805

P517

1M0

0805

R535

1M0

0805

R538

47R

0805

R539

47R

0805

0805

R547

11K

0805

C559

100UF

16V

NONP

C560

100UF

16V

NONP

DGND

DGND

R550

47K

0805

R551

47K

0805

R540

47R

0805

R541

47R

0805

+12VA

+12VA

D500

BAT54S

SOT-23

DGND

D501

BAT54S

SOT-23

DGND

RLY500A

RLY500B

-12VA

-12VA

P519

0R0 0805

NEC

EB2-5NU

0R0 0805

NEC

EB2-5NU

R528

1K0

0805

R554

R529

1K0

0805

R555

SCART_LEFT

LT_OUT

SCART_RIGHT

RT_OUT

+5VA

C503

10UF

35V

SGET

DGND

600R@100MHz

ALRCLK/DSD0

PCM_DAC0

ABCLK_DAC0

MCLK_DAC0

ML_8740_0

RESET*

PCM_DAC1/DSD1

+3V3A

C518

100N

16V

0603

L501

MD

MC

Fit for 8740

R565

0R0

0603

R566

0R0

0603

NF

Fit for 8741

C519

100N

16V

0603

C507

10UF

35V

SGET

DGND

+3V3_DAC0

P532

+3V3_DAC0

P528

P529

P530

P531

P535

DGND

C520

100N

16V

0603

C525

100N

16V

0603

26

27

28

23

24

25

22

1

2

3

5

4

6

LRCKIN

DIN

BCKIN

SCLK

MD/DM0

MC/DM1

ML/I2S

CSBIOW

MODE

MODE8X

DIFFHW

MUTEB

RSTB*

DGND

+12VA

NOTE: ALL PARTS FOR LEFT/RIGHT OU TPUTS ARE

NOT FITTED FOR DV135

FILTER

2nd order Bessel filter, Av=1

R506

P521

DGND

DGND

DGND

DGND

C542

2N2

100V

FKP2

C544

2N2

100V

FKP2

C545

2N2

100V

FKP2

C546

2N2

100V

FKP2

3K3

C537

0805

C566

100N

100V

MKS2

100P

100V

0805

P536

C538

P537

P538

100P

100V

0805

R510

3K3

0805

R511

3K3

0805

R512

3K3

0805

DAC 0

20

15

8

7

9

IC501

AVDD

DVDD

AVDDL

AVDDR

17

VOUTL+

16

VOUTL-

12

VOUTR+

13

VOUTR-

18

VMIDL

11

VMIDR

C526

C508

21

DGND

35V

SGET

10UF

ZERO

DGND

AGNDL

AGNDR

AGND

XWM8740EDS

19

10

14

SSOP-28

100N

16V

0603

100N

100V

MKS2

C565

10UF

35V

C509

SGET

C527

100N

16V

0603

R508

3K3

0805

R513

3K3

0805

R519

R521

680R

0805

680R

0805

+12VA

C510

10UF

35V

SGET

DGND

R523

680R

0805

DGND

C511

10UF

35V

SGET

-12VA

R522

680R 0805

C550

680P

100V

FKP2

C552

680P

100V

FKP2

C528

100N

16V

0603

C534

100N

16V

0603

IC504A

84

3

1

2

OPA2134UA

SO-8

C553

R514

3K3 0805

IC504B

OPA2134UA

5

SO-8

7

6

R515

3K3 0805

680P

100VFKP2

C554

680P

100VFKP2

10K

0805

10K

0805

R531

R533

P524

P540

DGND

DGND

DGND

-12VA

DGND

C529

100N

16V

0603

2

3

C530

100N

16V

0603

6

5

IC505A

84

1

OPA2134UA

SO-8

IC505B

7

OPA2134UA

SO-8

R548

11K

R536

C557

33P

100V

0805

P526 P527

C558

33P

100V

0805

P541

1M0

0805

R537

1M0

0805

R542

47R

0805

R544

47R

0805

0805

R549

11K

0805

C561

100UF

16V

NONP

C562

100UF

16V

NONP

DGND

DGND

R552

47K

0805

R553

47K

0805

R543

47R

0805

R545

47R

0805

+12VA

+12VA

D502

BAT54S

SOT-23

DGND

D503

BAT54S

SOT-23

DGND

RLY501A

RLY501B

-12VA

-12VA

P542

R556

0R0 0805

NEC

EB2-5NU

R559

0R0 0805

NEC

EB2-5NU

LEFT_OUT

RIGHT_OUT

FITTED FOR DV135 ONLY

R557

0R0 0805

R558

0R0 0805

SKT500

LEFT

RIGHT

C567

C568

100P

100P

100V

100V

0805

0805

R560

0R0

DGND DGND

0805

KUNMING GOLD

SCRN

C571

1N0

50V

0603

EMC_GND

C569

100P

100V

0805

OUT_GND1OUT_GND2

C572

1N0

50V

0603

LEFT DOWNMIX

RIGHT DOWNMIX

C570

100P

100V

0805

R561

0R0

0805

DGND

+12VA

-12VA

C531

100N

16V

0603

C532

100N

16V

0603

+5VA

C533

100N

16V

0603

13

12

5

4

IC506E

V+

VL

GND

V-

DG413DY

SO-16

IC506C

DG413DY

SO-16

9

1011

DGND

IC506D

DG413DY

SO-16

16

R562

100R 0805

C573

1N0

50V 0603

C574

1N0

C575

50V 0603

1N0

50V 0603

1415

DGND EMC_GND

D504

BAT54S

SOT-23

+5VD

MUTE*

D505

BAS16

SOT-323

AC_PRES*

RLY500C

NEC

EB2-5NU

P510

R563

1K0 0603

P543

Base resistor on PSU

MUTING

RLY501C

NEC

EB2-5NU

DGND

RLY600C

NEC

EB2-5NU

P544

TR500

BC849B

SOT-23

DGND

RLY601C

NEC

EB2-5NU

P545

TR501

FMMT497

SOT-23

ITEM500 1 Pad Dam ping 7.5x6x3MM RubberE828AP Fit on top of relay

ITEM501 1 Pad Dam ping 7.5x6x3MM RubberE828AP

DRAWING TITLE

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

DV137 DAC Left / Right

Filename:

Notes:

Contact Engineer:

L988C05 DAC L & R.Sch

Mark Tweedale

markt@arcam.co.uk

Contact Tel:

06_E093 MJT 12/06/06 None to this sheet. Add heats ink to top of Vaddis 3.1

06_E036 PG 20/03/06 Add thermal attac h pads to IC200 3.0

06_E029 PG 15/03/06 Issue 2 PCB ( changes only affect DV139) 2.0

05_E242 PG 08/12/05 Production R elease 1.0

INITIALS

ECO No.

01223 203210 (direct)

01223 203200 (switch)

Printed:

DATE

12-Jun-2006

Fit on top of relay

DESCRIPTION OF CHANGE

513Sheet of

A2

DRAWING NO.

ISSUE

L988CT

Page 6

+5VA

C600

10UF

35V

SGET

DGND

600R@100MHz

ALRCLK/DSD2

PCM_DAC1/DSD1

ABCLK_DAC1

MCLK_DAC1

MD

MC

ML_8740_1

+5VA

DGND

ALRCLK/DSD4

RESET*

RESET*

C603

10UF

35V

SGET

600R@100MHz

PCM_DAC2

ABCLK_DAC2

MCLK_DAC2

ML_8740_2

RESET*

PCM_DAC3/DSD3

DSD5_DAC3

+3V3A

+3V3A

P640

C612

100N

16V

0603

L600

MD

MC

Fit for 8740

R654

0R0

0603

R655

0R0

0603

NF

Fit for 8741

C618

100N

16V

0603

L601

MD

MC

Fit for 8740

R656

0R0

0603

R657

0R0

0603

NF

Fit for 8741

C613

100N

16V

0603

C601

10UF

35V

SGET

DGND

P600

P601

P602

P603

+3V3_DAC1

P618

C619

100N

16V

0603

C607

10UF

35V

SGET

DGND

P625

P626

P627

P628

+3V3_DAC2

P629

+3V3_DAC1

P606

DGND

+3V3_DAC2

P632

DGND

C614

100N

16V

0603

C615

100N

16V

0603

26

27

28

23

24

25

22

C620

100N

16V

0603

C625

100N

16V

0603

26

27

28

23

24

25

22

1

2

3

5

4

6

1

2

3

5

4

6

LRCKIN

DIN

BCKIN

SCLK

MD/DM0

MC/DM1

ML/I2S

CSBIOW

MODE

MODE8X

DIFFHW

MUTEB

RSTB*

DGND

LRCKIN

DIN

BCKIN

SCLK

MD/DM0

MC/DM1

ML/I2S

CSBIOW

MODE

MODE8X

DIFFHW

MUTEB

RSTB*

DGND

NOTE Audio outputs are not inverted like

they were in previous designs, so

software must not invert phase

DAC 1

9

20

15

8

AVDD

DVDD

AVDDL

AVDDR

VOUTL+

VOUTL-

VOUTR+

VOUTR-

VMIDL

VMIDR

ZERO

DGND

AGNDL

AGNDR

AGND

7

XWM8740EDS

19

10

14

SSOP-28

DAC 2

20

15

8

7

9

AVDD

DVDD

AVDDL

AVDDR

VOUTL+

VOUTL-

VOUTR+

VOUTR-

VMIDL

VMIDR

ZERO

DGND

AGNDL

AGNDR

AGND

XWM8740EDS

19

10

14

SSOP-28

IC600

17

16

12

13

18

11

21

IC601

17

16

12

13

18

11

21

DGND

DGND

35V

SGET

35V

SGET

C604

10UF

C608

10UF

C621

100N

16V

0603

C626

100N

16V

0603

100N

100V

MKS2

100N

100V

MKS2

C660

C662

10UF

35V

10UF

35V

C605

SGET

C609

SGET

C622

100N

16V

0603

C627

100N

16V

0603

C661

100N

100V

MKS2

C663

100N

100V

MKS2

C632

100P

100V

0805

C634

C633

100P

100V

0805

C635

P607

P608

P620

P619

P633

P634

2nd order Bessel filter, Av=1

R600

3K3

0805

DGND

R601

3K3

0805

DGND

P609

R602

3K3

0805

100P

100V

0805

DGND

R607

3K3

0805

DGND

2nd order Bessel filter, Av=1

R606

3K3

0805

DGND

R610

3K3

0805

DGND

P635

R611

3K3

0805

100P

100V

0805

DGND

R612

3K3

0805

DGND

FILTER

C636

2N2

100V

FKP2

C637

2N2

100V

FKP2

C638

2N2

100V

FKP2

C639

2N2

100V

FKP2

FILTER

C640

2N2

100V

FKP2

C641

2N2

100V

FKP2

C642

2N2

100V

FKP2

C643

2N2

100V

FKP2

R603

3K3

0805

R604

3K3

0805

R608

3K3

0805

R613

3K3

0805

R616

R617

R619

R621

680R

0805

680R

0805

680R

0805

680R

0805

+12VA

C602

10UF

35V

SGET

DGND

R618

680R

0805

DGND

C606

10UF

35V

SGET

-12VA

R620

680R 0805

+12VA

C610

10UF

35V

SGET

DGND

R623

680R

0805

DGND

C611

10UF

35V

SGET

-12VA

R622

680R 0805

C644

680P

100V

FKP2

C645

680P

100V

FKP2

C647

680P

100V

FKP2

C649

680P

100V

FKP2

C616

100N

16V

0603

C623

100N

16V

0603

C628

100N

16V

0603

C631

100N

16V

0603

+12VA

C617

100N

16V

0603

DGND

IC602A

84

3

1

2

OPA2134UA

SO-8

IC602B

OPA2134UA

5

SO-8

7

6

IC604A

84

3

1

2

OPA2134UA

SO-8

IC604B

OPA2134UA

SO-8

5

7

6

C646

680P

100VFKP2

R605

3K3 0805

C648

680P

100VFKP2

R609

3K3 0805

C650

680P

R614

3K3 0805

C651

680P

100VFKP2

R615

3K3 0805

R624

10K

0805

R625

10K

0805

R626

10K

0805

100VFKP2

R627

10K

0805

DGND

-12VA

C624

100N

16V

0603

P612

DGND

P613

DGND

+12VA

DGND

P622

DGND

DGND

-12VA

P637

DGND

2

3

6

5

C629

100N

16V

0603

2

3

C630

100N

16V

0603

6

5

IC603A

84

1

OPA2134UA

SO-8

IC603B

7

OPA2134UA

SO-8

IC605A

84

1

OPA2134UA

SO-8

IC605B

7

OPA2134UA

SO-8

OUTPUT BUFFER

Gain of -1.1

R640

11K

R628

C652

33P

100V

0805

P614 P616

C653

33P

100V

0805

P615

C654

33P

100V

0805

P623 P624

C655

33P

100V

0805

P638

1M0

0805

R629

1M0

0805

R630

1M0

0805

R631

1M0

0805

R632

47R

0805

R633

47R

0805

R636

47R

0805

R638

47R

0805

0805

R641

11K

0805

R642

11K

0805

R643

11K

0805

C656

100UF

16V

NONP

C657

100UF

16V

NONP

C658

100UF

16V

NONP

C659

100UF

16V

NONP

DGND

DGND

DGND

DGND

R644

47K

0805

R645

47K

0805

R646

47K

0805

R647

47K

0805

R634

47R

0805

R635

47R

0805

R637

47R

0805

R639

47R

0805

+12VA

+12VA

+12VA

+12VA

D600

BAT54S

SOT-23

DGND

D601

BAT54S

SOT-23

DGND

D602

BAT54S

SOT-23

DGND

D603

BAT54S

SOT-23

DGND

RLY600A

RLY600B

RLY601A

RLY601B

-12VA

-12VA

P617

-12VA

-12VA

P639

R648

0R0 0805

NEC

EB2-5NU

R649

0R0 0805

NEC

EB2-5NU

R650

0R0 0805

NEC

EB2-5NU

R653

0R0 0805

NEC

EB2-5NU

LS_OUT

RS_OUT

CENT_OUT

SUB_OUT

SKT600

CENTRE

SUB

C664

C665

100P

100P

100V

100V

0805

0805

R651

0R0

DGND DGND

0805

KUNMING GOLD

SCRN

C668

1N0

50V

0603

EMC_GND

C666

100P

100V

0805

OUT_GND3OUT_GND4

C669

1N0

50V

0603

LEFT SURROUND

RIGHT SURROUND

C667

100P

100V

0805

R652

0R0

0805

NOTE: ALL PARTS ON THIS SHEET ARE NOT FITTED FOR DV135

ITEM600 1 Pad Dam ping 7.5x6x3MM RubberE828AP Fit on top of relay

ITEM601 1 Pad Dam ping 7.5x6x3MM RubberE828AP

DRAWING TITLE

ARCAM

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

DV137 DAC LS RS C SUB

Filename:

Notes:

Contact Engineer:

L988C06 DAC LS RS C SUB.Sch

Mark Tweedale

markt@arcam.co.uk

Contact Tel:

06_E093 MJT 12/06/06 None to this sheet. Add heats ink to top of Vaddis 3.1

06_E036 PG 20/03/06 Add thermal attac h pads to IC200 3.0

06_E029 PG 15/03/06 Issue 2 PCB ( changes only affect DV139) 2.0