Page 1

MICROTECHNOLOGY

FEATURES

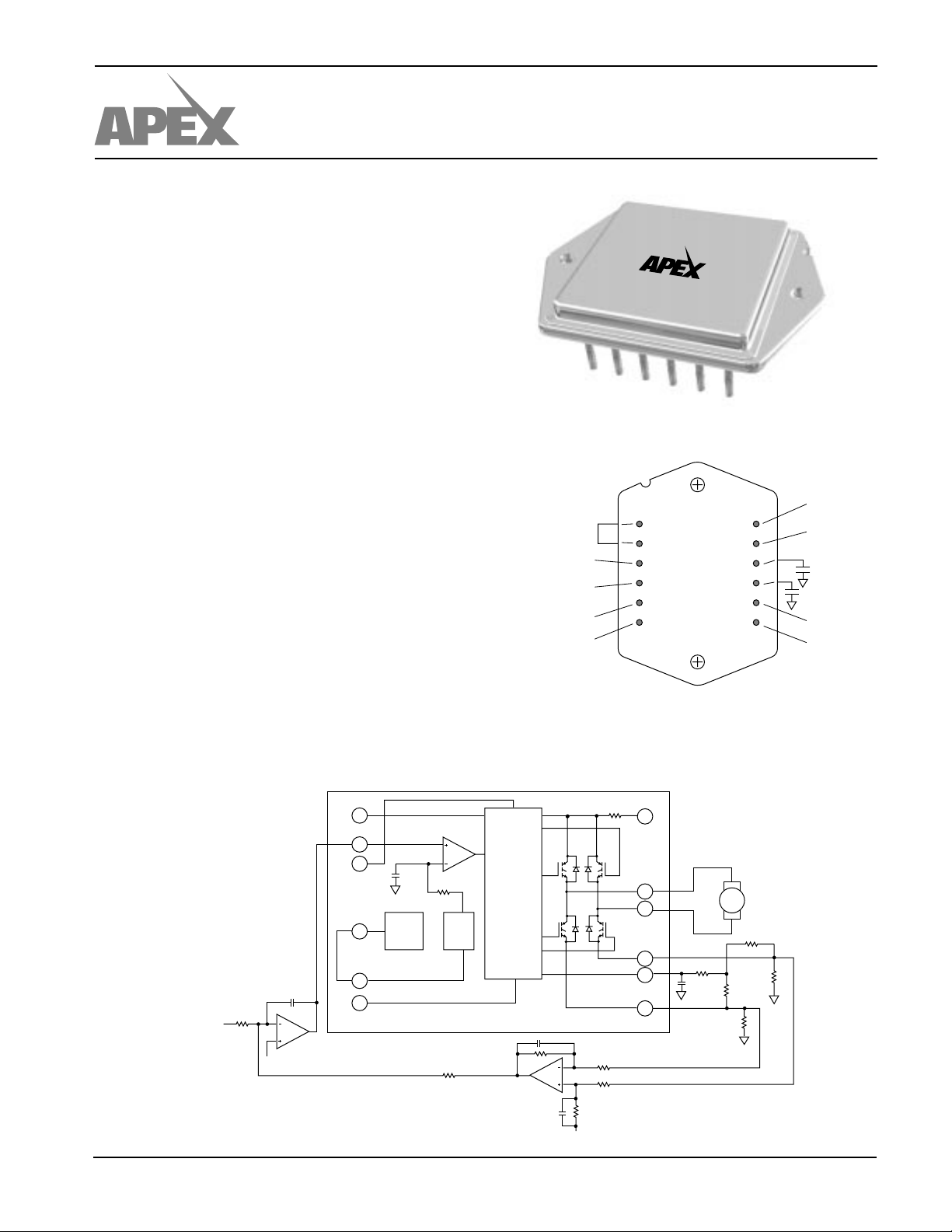

PULSE WIDTH MODULATION AMPLIFIER

SA08

HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

• IGBT OUTPUTS

• WIDE SUPPLY RANGE—16-500V

• 20A TO 100°C CASE

• 3 PROTECTION CIRCUITS

• SYNCHRONIZED OR EXTERNAL OSCILLATOR

• FLEXIBLE FREQUENCY CONTROL

APPLICATIONS

• MOTORS

• REACTIVE LOADS

• MAGNETIC BEARINGS

• LARGE PIEZO ELEMENTS

• OFF-LINE DRIVERS

• C-D WELD CONTROLLER

DESCRIPTION

The SA08 is a pulse width modulation amplifier that can

supply 10KW to the load. An internal oscillator requires no

external components. The clock input stage divides the oscillator frequency by two, which provides the switching frequency of 22.5 kHz. The oscillator may also be used to

synchronize multiple amplifiers. Current sensing is provided

for each half of the bridge giving amplitude and direction data.

A shutdown input turns off all four drivers of the H-bridge

output. A high side current limit and the programmable low

side current limit protect the amplifier from shorts to supply or

ground in addition to load shorts. The H-bridge output IGBTs

are protected from thermal overloads by directly sensing the

temperature of the die. The 12-pin hermetic MO-127 power

package occupies only 3 square inches of board space.

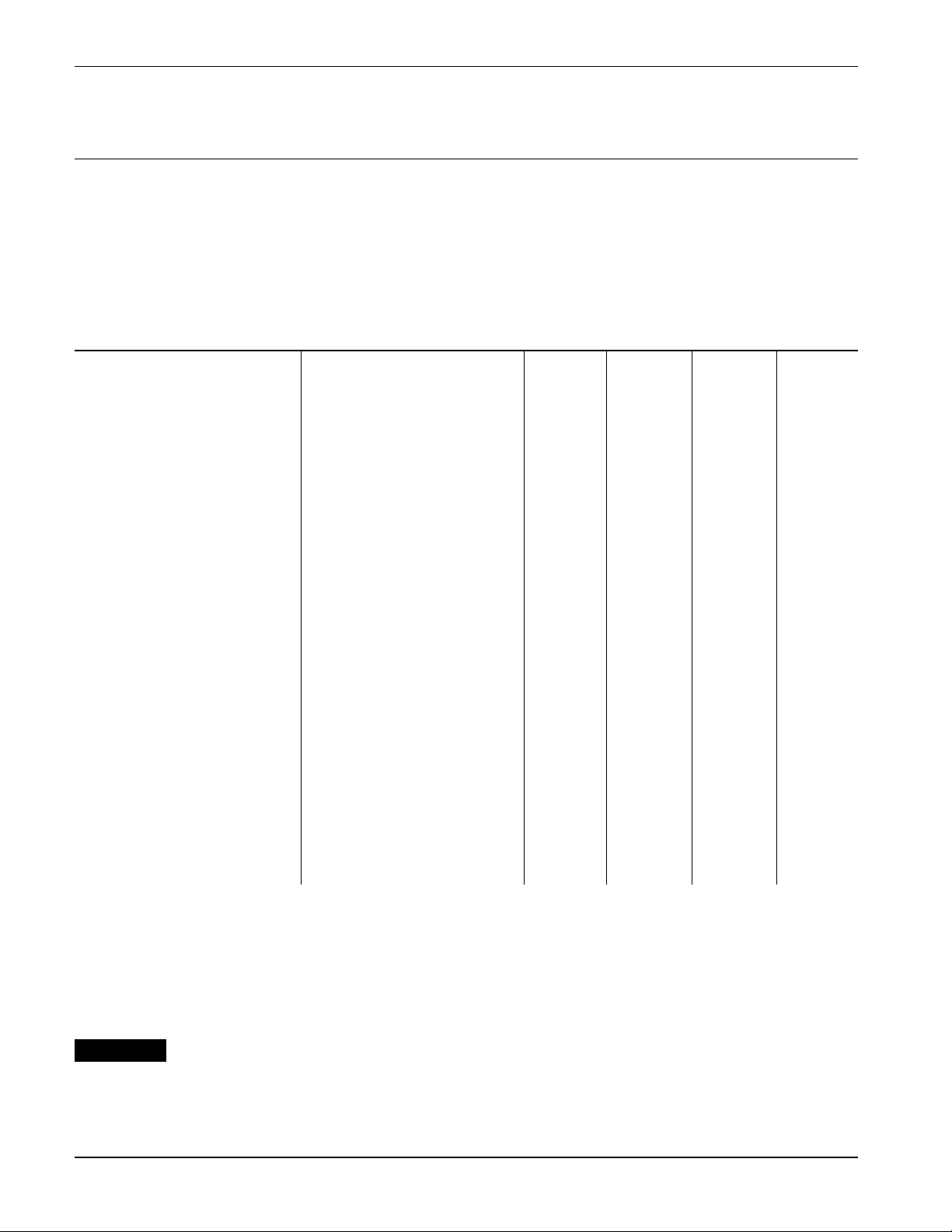

BLOCK DIAGRAM AND TYPICAL APPLICATION

MOTOR TORQUE CONTROL

Vcc

10

+PWM

3

4

CONTROL

SIGNAL

3/7V

FLAG

CLK OUT

CLK IN

GND

470pF

45K

2

1

5

÷2OSC

SA08

∆

USA BeO

TE949311

EXTERNAL CONNECTIONS

ISENSE A

CLK IN

CLK OUT

+PWM

FLAG

GND

1

2

3

TOP

TOP

VIEW

VIEW

4

5

6

ILIM/SHDN

Case tied to pin 5. Allow no current in case. Bypassing of supplies

is required. Package is Apex MO-127 (STD). See Outline

Dimensions/Packages in Apex data book.

*See text. As +PWM goes more positive, A OUT duty cycle

increases.

CURRENT

LIMIT

PWM

OUTPUT

DRIVERS

SHUTDOWN

CONTROL

9

+V

S

B OUT

8

11

A OUT

I SENSE A

12

6

ILIM/SHDN

7

I SENSE B RSENSE

.1µF

12

11

10

9

8

7

*

A OUT

*

VCC

+VS

B OUT

I SENSE B

MOTOR

5K

5K

RSENSE

5K

5V

5V

APEX MICROTECHNOLOGY CORPORATION • TELEPHONE (520) 690-8600 • FAX (520) 888-3329 • ORDERS (520) 690-8601 • EMAIL prodlit@apexmicrotech.com

Page 2

SA08

ABSOLUTE MAXIMUM RATINGS

SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS

SUPPLY VOLTAGE, +V

SUPPLY VOLTAGE, V

POWER DISSIPATION, internal

TEMPERATURE, pin solder - 10s 300°C

TEMPERATURE, junction

S

CC

1

2

500V

16V

250W

150°C

TEMPERATURE, storage –65 to +150°C

OPERATING TEMPERATURE RANGE, case –55 to +125°C

INPUT VOLTAGE, +PWM 0 TO +11V

SPECIFICATIONS

INPUT VOLTAGE, I

PARAMETER TEST CONDITIONS

LIM

2

MIN TYP MAX UNITS

0 TO +10V

CLOCK (CLK)

CLK OUT, high level

CLK OUT, low level

CLK IN, low level

CLK IN, high level

4

4

4

4

I

≤ 1mA 4.8 5.3 V

OUT

I

≤ 1mA 0 .4 V

OUT

0.9V

3.7 5.4 V

FREQUENCY 44.10 45.00 46.90 kHz

ANALOG INPUT (+PWM)

center voltage 5V

P-P voltage 0/100% modulation 4 V

FLAG

FLAG, high level 10 V

FLAG, low level 0V

OUTPUT

TOTAL DROP I = 20A 5.4 V

EFFICIENCY, 20A output VS = 380V 98 %

SWITCHING FREQUENCY OSC in ÷ 2 22.05 22.50 22.95 kHz

CURRENT, continuous

CURRENT, peak

4

4

100°C case 20 A

28 A

POWER SUPPLY

VOLTAGE, V

VOLTAGE, V

CURRENT, V

CURRENT, V

CURRENT, V

I

/SHUTDOWN

LIM

S

CC

CC

shutdown 50 mA

CC,

S

Full temperature range 16

Full temperature range 14 15 16 V

I

= 0 80 mA

OUT

No Load 90 mA

5

240 500 V

TRIP POINT 90 110 mV

INPUT CURRENT 100 nA

THERMAL

3

RESISTANCE, junction to case Full temperature range, for each die 1 °C/W

RESISTANCE, junction to air Full temperature range 12 °C/W

TEMPERATURE RANGE, case Meets full range specifications –25 +85 °C

NOTES: 1. Each of the two active output transistors can dissipate 125W.

2. Unless otherwise noted: TC = 25°C, VS, VCC at typical specification.

3. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power

dissipation to achieve high MTTF. For guidance, refer to the heatsink data sheet.

4. Guaranteed but not tested.

5. If 100% duty cycle is not required V

CAUTION

The SA08 is constructed from static sensitive components. ESD handling procedures must be observed.

S(MIN)

= 0V.

The internal substrate contains beryllia (BeO). Do not break the seal. If accidentally broken, do not crush,

machine, or subject to temperatures in excess of 850°C to avoid generating toxic fumes.

APEX MICROTECHNOLOGY CORPORATION • 5980 NORTH SHANNON ROAD • TUCSON, ARIZONA 85741 • USA • APPLICATIONS HOTLINE: 1 (800) 546-2739

APEX MICROTECHNOLOGY CORPORATION • 5980 NORTH SHANNON ROAD • TUCSON, ARIZONA 85741 • USA • APPLICATIONS HOTLINE: 1 (800) 546-2739

Page 3

TYPICAL PERFORMANCE

GRAPHS

SA08

125

POWER DERATING

100

75

50

25

EACH ACTIVE

OUTPUT TRANSISTOR

0

INTERNAL POWER DISSIPATION, (W)

0 75 100

25 50 125

CASE TEMPERATURE, (°C)

20

16

12

8

4

FORWARD CURRENT, (A)

0

DIODE FORWARD VOLTAGE DROP, (V)

REVERSE DIODE

Tc = 100°C Tc = 25°C

1.0 1.5 2.0 3.02.5

0.5

100

CLOCK LOADING

99

98

97

96

NORMALIZED FREQUENCY, (%)

95

CLOCK LOAD RESISTANCE, (Ω)

6

CASE TEMPERATURE

5

4

3

2

TOTAL VOLTAGE DROP, (V)

048121620

F NOMINAL = 45kHz

10K

TOTAL VOLTAGE DROP

100°C

OUTPUT CURRENT, I(A)

25°C

CLOCK FREQUENCY OVER TEMP

102.0

101.5

101.0

100.5

100

99.5

99.0

98.5

NORMALIZED FREQUENCY, (%)

98.0

–50

1M100K

–25 0 25 50 75 100 125

CASE TEMPERATURE, (°C)

CONTINUOUS AMPS

20

18

16

14

12

CONTINUOUS AMPS, (A)

10

25 50 75 100 125

CASE TEMPERATURE, (°C)

Vcc QUIESCENT CURRENT

115

110

105

100

NORMALIZED Vcc QUIESCENT CURRENT, (%)

Vcc = 15V

F = 22.5 kHz

NORMAL

OPERATION

95

90

85

80

–50 –25 0 25 50 75 100 125

CASE TEMPERATURE, (°C)

SHUTDOWN

OPERATION

DUTY CYCLE VS ANALOG INPUT

100

B OUT

80

60

40

DUTY CYCLE, (%)

20

A OUT

0

35476

ANALOG INPUT, (V)

Vs QUIESCENT VS VOLTAGE

150

125

100

75

50

0 100 200 300 400 500

NORMALIZED Vs QUIESCENT CURRENT, (%)

Vs, (V)

Vcc QUIESCENT CURRENT

100

96

92

88

84

5

NORMALIZED QUIESCENT CURRENT, (%)

SWITCHING FREQUENCY, F (kHz)

Vs QUIESCENT VS FREQUENCY

100

90

80

70

60

50

525

10 15 20

SWITCHING FREQUENCY, F (kHz)

NORMALIZED Vs QUIESCENT CURRENT, (%)

2510 15 20

APEX MICROTECHNOLOGY CORPORATION • TELEPHONE (520) 690-8600 • FAX (520) 888-3329 • ORDERS (520) 690-8601 • EMAIL prodlit@apexmicrotech.com

Page 4

OPERATING

CONSIDERATIONS

SA08

GENERAL

Helpful information about power supplies, heatsinking and

mounting can be found in the “General Operating Considerations” section of the Apex data book. For information on the

package outline, heatsinks, and mounting hardware see the

“Package Outlines” and “Accessories” section of the data

book. Also see Application Note 30 on “PWM Basics.”

CLOCK CIRCUIT AND RAMP GENERATOR

The clock frequency is internally set to a frequency of

approximately 45kHz. The CLK OUT pin will normally be tied

to the CLK IN pin. The clock is divided by two and applied to an

RC network which produces a ramp signal. An external clock

signal can be applied to the CLK IN pin for synchronization

purposes, but must be 45 kHz +/- 2%.

FLAG OUTPUT

Whenever the SA08 has detected a fault condition, the flag

output is set high (10V). When the programmable low side

current limit is exceeded, the FLAG output will be set high. The

FLAG output will be reset low on the next clock cycle. This

reflects the pulse-by-pulse current limiting feature. When the

internally-set high side current limit is tripped or the thermal

limit is reached, the FLAG output is latched high. See PROTECTION CIRCUITS below.

PROTECTION CIRCUITS

A fixed internal current limit senses the high side current.

Should either of the outputs be shorted to ground the high side

current limit will latch off the output transistors. The temperature of the output transistors is also monitored. Should a fault

condition raise the temperature of the output transistors to

165°C the thermal protection circuit latch off the output transistors. The latched condition can be cleared by either recycling

power or by toggling the I LIMIT/SHDN input with a 10V

the V

cc

pulse. See Figures A and B. The outputs will remain off as long

as the shutdown pulse is high (10V).

CURRENT LIMIT

There are two load current sensing pins, I SENSE A and I

SENSE B. The two pins can be shorted in the voltage mode

connection but both must be used in the current mode connection (see figures A and B). It is recommended that R

resistors be non-inductive. Load current flows in the I SENSE

pins. To avoid errors due to lead lengths connect the I LIMIT/

SHDN pin directly to the R

network and shutdown

divider resistor) and

connect the R

LIMIT

resistors directly to the

GND pin.

resistors (through the filter

LIMIT

I SENSE A

R

I SENSE B

LIMIT

Switching noise

spikes will invariably be

found at the I SENSE

pins. The noise spikes

could trip the current

I LIMIT/SHDN

R

FILTER

C

FILTER

5K

IN4148

limit threshold which is

only 100 mV. R

FIGURE A. CURRENT LIMIT WITH

FILTER

SHUTDOWN VOLTAGE MODE.

LIMIT

SHUTDOWN

SIGNAL

0/10V

I SENSE A

I SENSE B

R

LIMIT

I LIMIT/SHDN

R

FILTER

C

R

FILTER

5K

LIMIT

5K

SHUTDOWN

SIGNAL

IN4148

and C

be adjusted so as

to reduce the

switching noise

well below 100 mV

to prevent false current limiting. The

sum of the DC level

plus the noise peak

will determine the

current limiting

0/10V

value. As in most

switching circuits it

FILTER

should

may be difficult to

FIGURE B. CURRENT LIMIT WITH

SHUTDOWN CURRENT MODE.

determine the true

noise amplitude

without careful attention to grounding of the oscilloscope

probe. Use the shortest possible ground lead for the probe and

connect exactly at the GND terminal of the amplifier. Suggested starting values are C

The required value of R

LIMIT

= .1uF, R

FILTER

in voltage mode may be calcu-

FILTER

= 5k .

lated by:

R

where R

= .1 V / I

LIMIT

is the required resistor value, and I

LIMIT

LIMIT

LIMIT

is the

maximum desired current. In current mode the required value

of each R

divided down by 2 (see Figure B). If R

is 2 times this value since the sense voltage is

LIMIT

is used it will further

SHDN

divide down the sense voltage. The shutdown divider network

will also have an effect on the filtering circuit.

BYPASSING

Adequate bypassing of the power supplies is required for

proper operation. Failure to do so can cause erratic and low

efficiency operation as well as excessive ringing at the outputs.

The Vs supply should be bypassed with at least a 1µF ceramic

capacitor in parallel with another low ESR capacitor of at least

10µF per amp of output current. Capacitor types rated for

switching applications are the only types that should be considered. The bypass capacitors must be physically connected

directly to the power supply pins. Even one inch of lead length

will cause excessive ringing at the outputs. This is due to the

very fast switching times and the inductance of the lead

connection. The bypassing requirements of the Vcc supply are

less stringent, but still necessary. A .1µF to .47µF ceramic

capacitor connected directly to the Vcc pin will suffice.

STARTUP CONDITIONS

The high side of the IGBT output bridge circuit is driven by

bootstrap circuit and charge pump arrangement. In order for

the circuit to produce a 100% duty cycle indefinitely the low

side of each half bridge circuit must have previously been in the

ON condition. This means, in turn, that if the input signal to the

SA08 at startup is demanding a 100% duty cycle, the output

may not follow the command and may be in a tri-state condition. The ramp signal must cross the input signal at some point

to correctly determine the output state. After the ramp crosses

the input signal level one time, the output state will be correct

thereafter.

This data sheet has been carefully checked and is believed to be reliable, however, no responsibility is assumed for possible inaccuracies or omissions. All specifications are subject to change without notice.

SA08U REV. A MAY 1999 © 1999 Apex Microtechnology Corp.

Loading...

Loading...