APW8813/A

DDR2 And DDR3 Power Solution Synchronous Buck Controller With 1.5A LDO

Features General Description

Buck Controller (VDDQ)

• High Input Voltages Range from 3V to 28V Input

Power

• Provide 1.8V (DDR2), 1.5V (DDR3) or Adjustable

Output Voltage from 0.75V to 5.5V

- ±1% Accuracy Over-Temperature

• Integrated MOSFET Drivers and Bootstrap Diode

• Excellent Line and Load Transient Responses

• PFM Mode for Increased Light Load Efficiency

• Constant-On-Time Controller Scheme

- Switching Frequency Compensation for PWM

Mode

- Adjustable Switching Frequency from 100kHz

to 550kHz in PWM Mode with DC Output Current

• Integrated MOSFET Drivers and Bootstrap Diode

• S3 and S5 Pins Control The Device in S0, S3, or

S4/S5 State

• Power Good Monitoring

• 70% Under-Voltage Protection (UVP)

• 125% Over-Voltage Protection (OVP)

• Adjustable Current-Limit Protection

- Using Sense Low-Side MOSFET R

±1.5A LDO Section (VTT)

DS(ON)

• Souring or Sinking Current up to 1.5A

• Fast Transient Response for Output Voltage

• Output Ceramic Capacitors Support at Least

10µF MLCC

• VTT and VTTREF Track at Half the VDDQSNS by

Internal Divider

• ±20mV Accuracy for VTT and VTTREF

• Independent Over-Current-Limit (OCL)

The APW8813/A integrates a synchronous buck PWM

controller to generate VDDQ, a sourcing and sinking LDO

linear regulator to generate VTT. It provides a complete

power supply for DDR2 and DDR3 memory system. It

offers the lowest total solution cost in system where space

is at a premium.

The APW8813/A provides excellent transient response

and accurate DC voltage output in either PFM or PWM

Mode. In Pulse Frequency Mode (PFM), the APW8813/A

provides very high efficiency over light to heavy loads with

loading-modulated switching frequencies. On TQFN4x424A package, the Forced PWM Mode works nearly at constant frequency for low-noise requirements.

The APW8813/A is equipped with accurate current-limit,

output under-voltage, and output over-voltage protections.

A Power-On-Reset function monitors the voltage on V

prevents wrong operation during power on.

The LDO is designed to provide a regulated voltage with

bi-directional output current for DDR-SDRAM termination.

The device integrates two power transistors to source or

sink current up to 1.5A. It also incorporates current-limit

and thermal shutdown protection.

The output voltage of LDO tracks the voltage at VTTREF

pin. An internal resistor divider is used to provide a half

voltage of VDDQ for VTTREF and VTT Voltage. The VTT

output voltage is only requiring 20µF of ceramic output

capacitance for stability and fast transient response. The

S3 and S5 pins provide the sleep state for VTT (S3 state)

and suspend state (S4/S5 state) for device, when S5 and

S3 are both pulled low the device provides the soft-off for

VTT and VTTREF.

The APW8813/A is available in 4mmx4mm 24-pin TQFN

package, and the APW8813A is available in 3mmx3mm

20-pin TQFN package.

• Thermal Shutdown Protection

• QFN-24 4mmx4mm Thin Package (TQFN4x4-24A)

for APW8813 and QFN-20 3mmx3mm Thin

Package (TQFN3x3-20) for APW8813A

• Lead Free and Green Devices Available

(RoHS Compliant)

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and

advise customers to obtain the latest version of relevant information to verify before placing orders.

Applications

• DDR2, and DDR3 Memory Power Supplies

• SSTL-2 SSTL-18 and HSTL Termination

CC

Copyright ANPEC Electronics Corp.

Rev. A.6 - Sep., 2012

www.anpec.com.tw1

APW8813/A

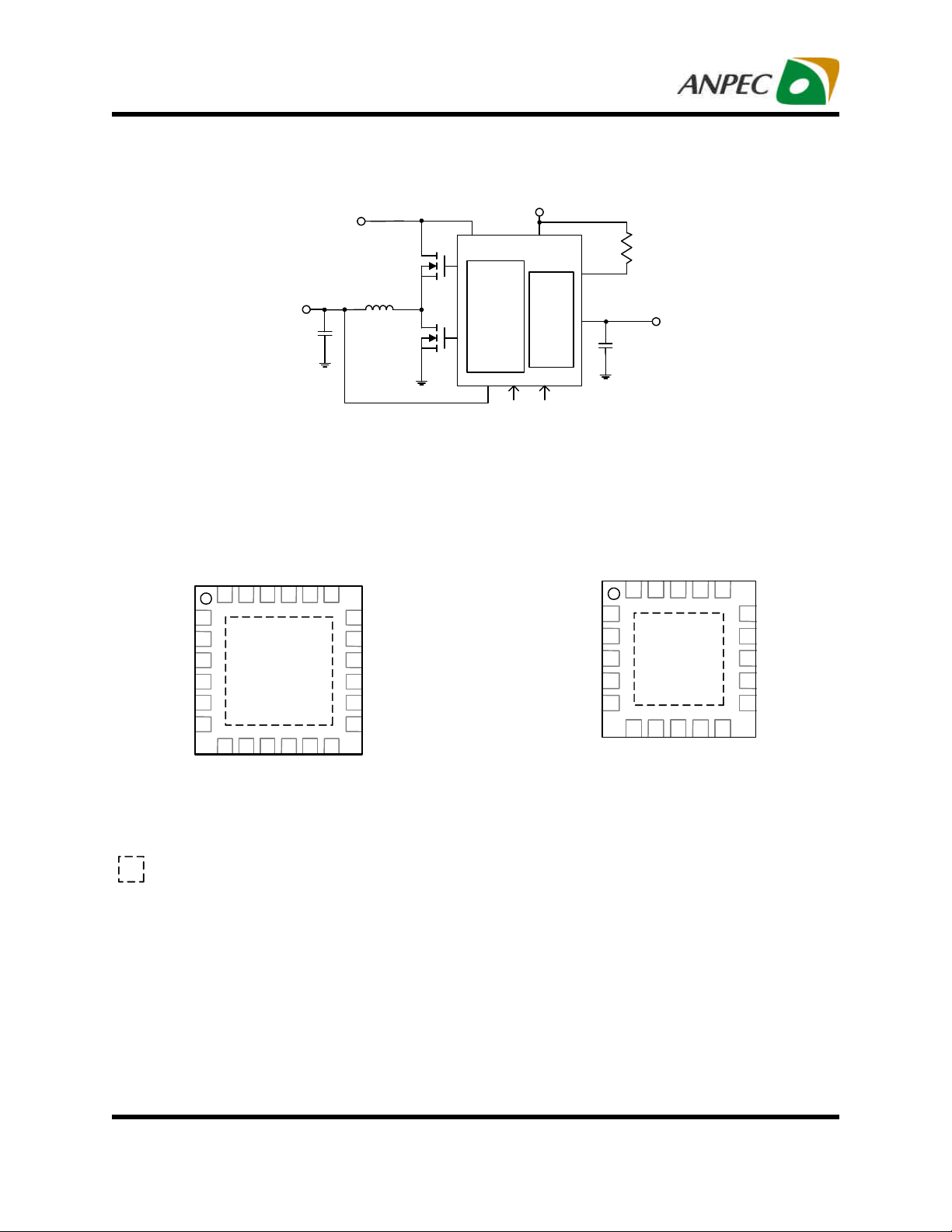

Simplified Application Circuit

V

IN

+3V~28V

VDDQ

L

OUT

Pin Configuration

APW8813

PHASE

BOOT

VTT

LDOIN

23 22 21 20 1924

GND

MODE

FCCM

1

2

3

4

5

6

NC

25

PGND

8 9 10 11 127

VDDQSET

VDDQSNS

VTTGND

VTTSNS

VTTREF

TQFN4x4-24A

(Top View)

= Thermal Pad (connected to GND plane for better heat dissipation)

LGATE

UGATE

18

PGND

CS_GND

17

CS

16

PVCC

15

14

VCC

13

PGOOD

S3

S5

TON

Q1

Q2

PWM

S3

5V

DDR

LDO

S5

VTTGND

VTTSNS

VTTREF

VDDQSNS

GND

R

VDDQ/2

1

2

3

4

5

VDDQSET

TQFN3x3-20

CS

VTT

APW8813A

BOOT

VTT

LDOIN

19 18 17 1620

21

PGND

7 8 9 106

S5

S3

(Top View)

PHASE

UGATE

15

LGATE

14

PGND

13

CS

12

PVCC

11

VCC

TON

PGOOD

Copyright ANPEC Electronics C orp.

Rev. A.6 - Sep., 2012

www.anpec.com.tw2

APW8813/A

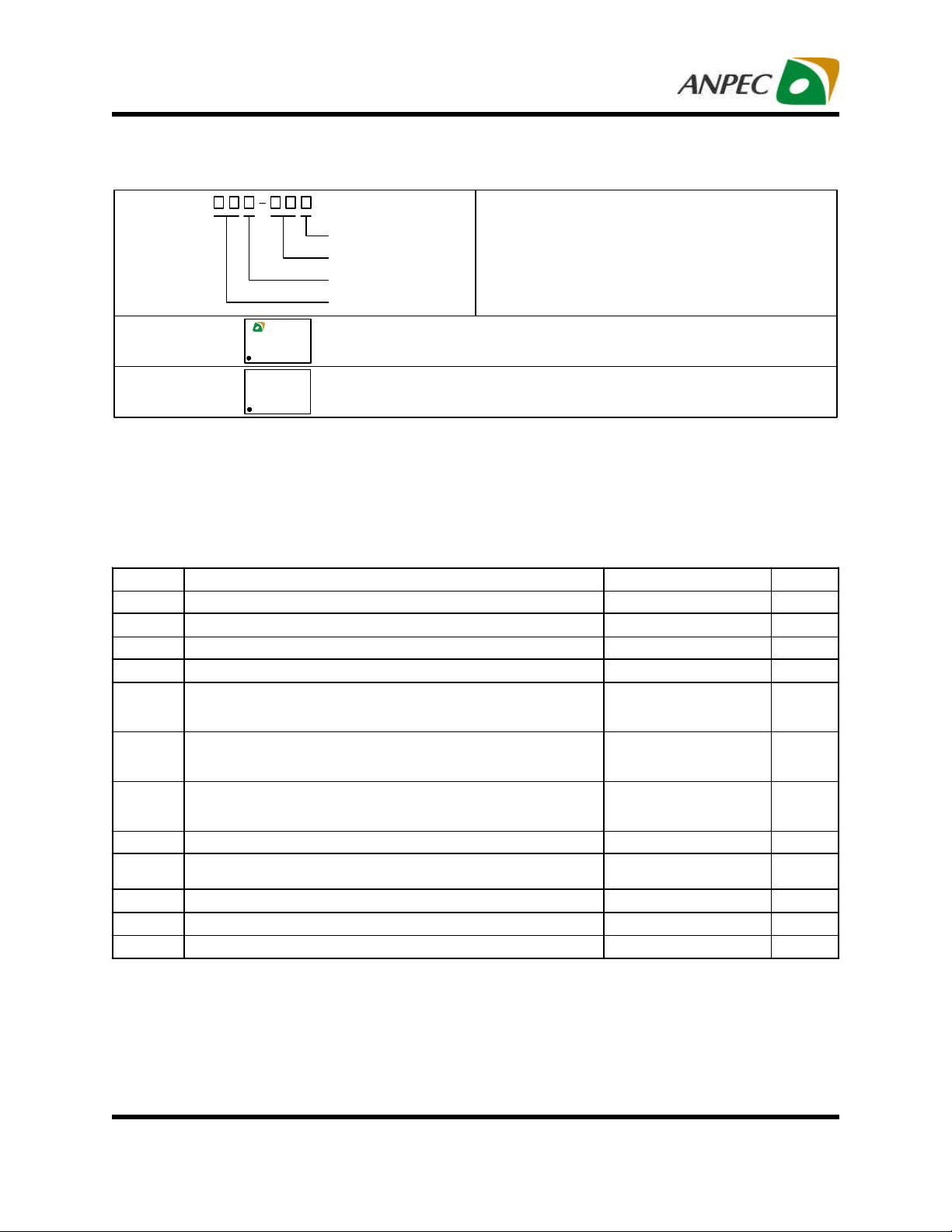

Ordering and Marking Information

APW8813/A

Package Code

QB : TQFN4x4-24A QB : TQFN3x3-20

Temperature Range

I : -40 to 85 oC

Handling Code

TR : Tape & Reel

Assembly Material

G : Halogen and Lead Free Device

XXXXX - Date Code

APW8813 QB :

APW8813

XXXXX

Assembly Material

Handling Code

Temperature Range

Package Code

APW

APW8813A QB : XXXXX - Date Code

8813A

XXXXX

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which

are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for

MSL classification at lead-free peak reflow temperature. ANPEC defines “Green” to mean lead-free (RoHS compliant) and halogen

free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by

weight).

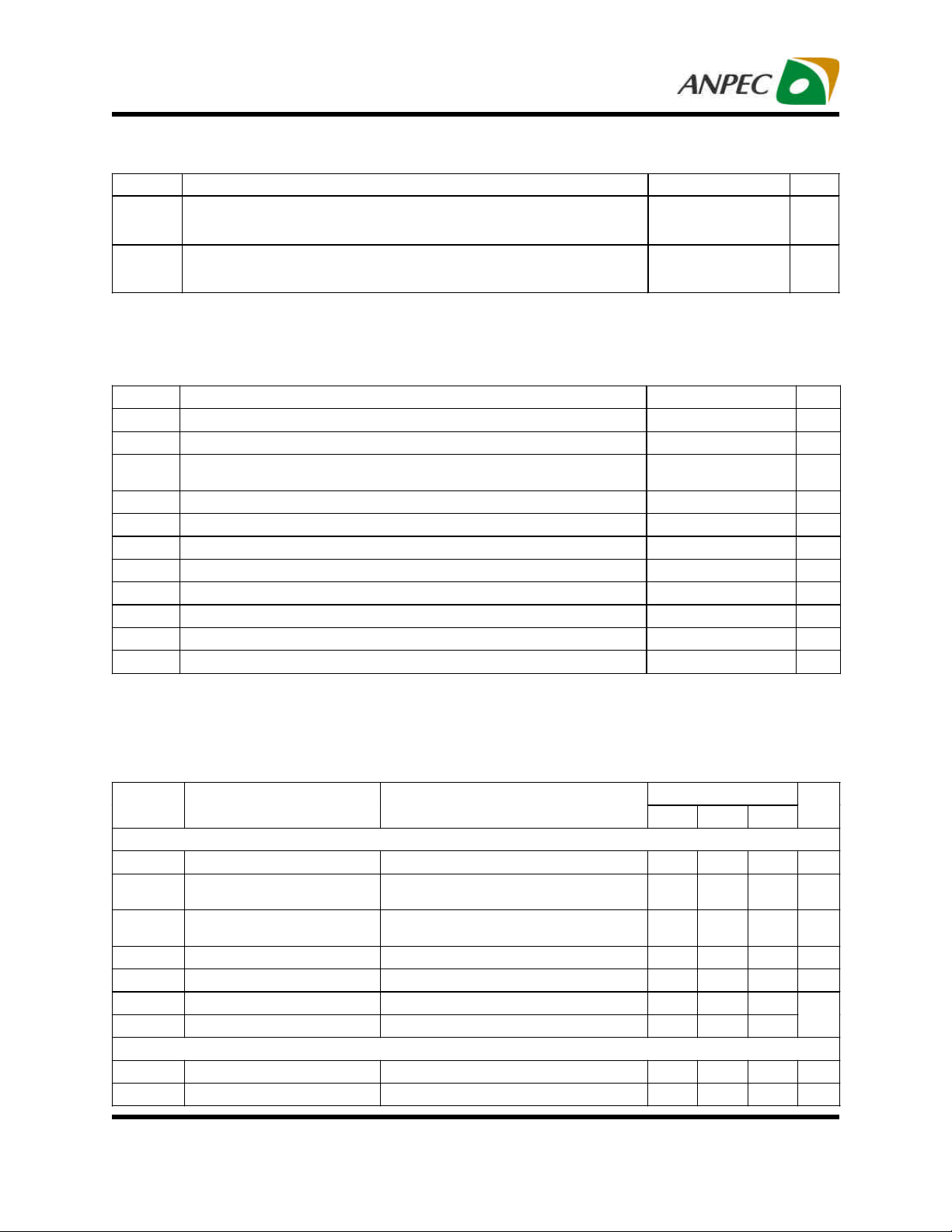

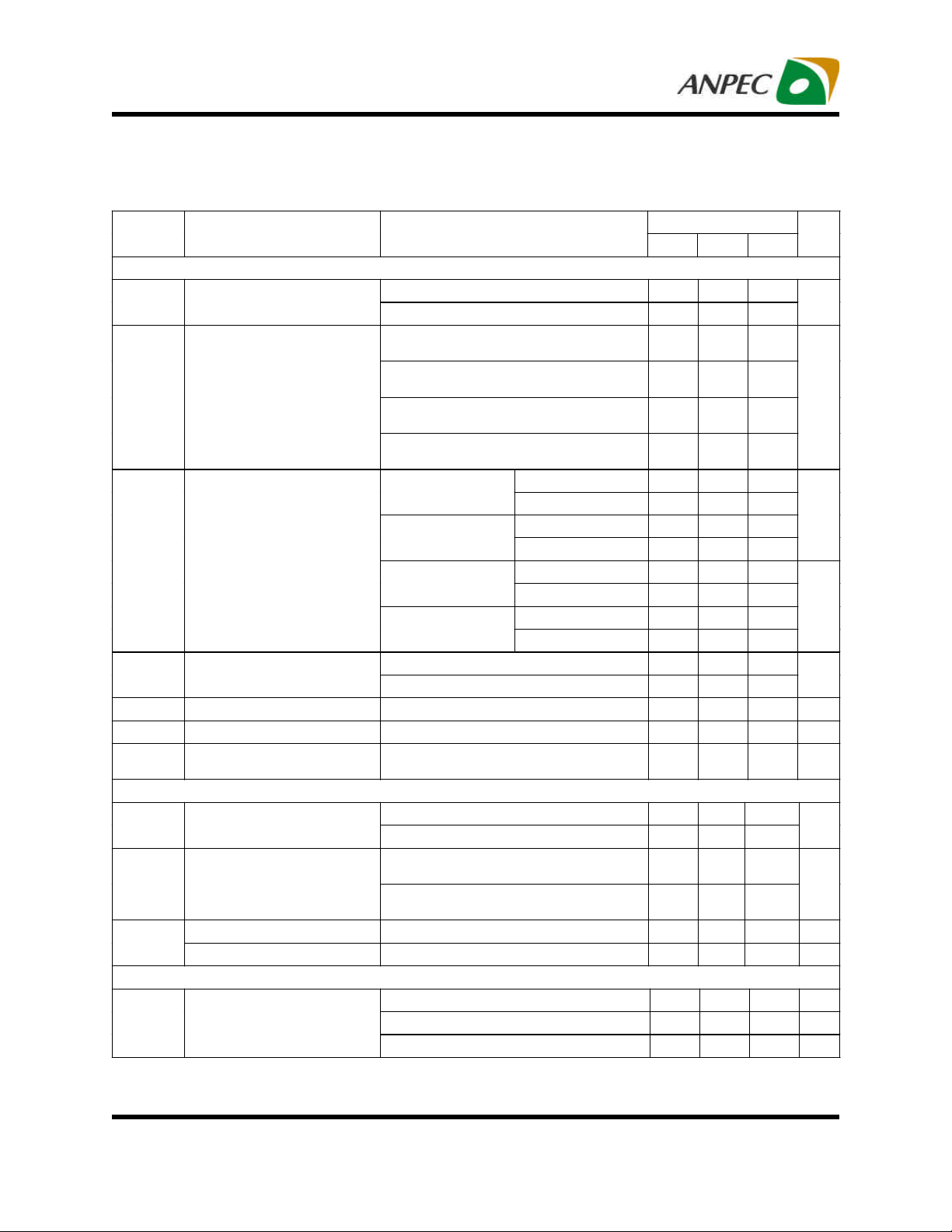

Absolute Maximum Ratings (Note 1, 2)

Symbol

VCC VCC Supply Voltage (VCC to GND) -0.3 ~ 7 V

V

PVCC Supply Voltage (PVCC to GND) -0.3 ~ 7 V

PVCC

V

BOOT Supply Voltage (BOOT to PHASE) -0.3 ~ 7 V

BOOT

V

BOOT-GND

BOOT Supply Voltage (BOOT to GND) -0.3 ~ 35 V

UGATE Voltage (UGATE to PHASE)

<400ns Pulse Width

>400ns Pulse Width

LGATE Voltage (LGATE to GND)

<400ns Pulse Width

>400ns Pulse Width

PHASE Voltage (PHASE to GND)

<400ns Pulse Width

>400ns Pulse Width

PGND, VTTGND and CS_GND to GND Voltage -0.3 ~ 0.3 V

All Other Pins (CS, MODE, S3, S5, VTTSNS, VDDQSNS, LDOIN, FCCM,

VDDQSET, PGOOD, VTT, VTTREF GND)

TJ Maximum Junction Temperature 150

T

Storage Temperature -65 ~ 150

STG

T

Maximum Soldering Temperature, 10 Seconds 260

SDR

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are

stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device

reliability

Note 2: The device is ESD sensitive. Handling precautions are recommended.

Parameter Rating Unit

-5 ~ V

-0.3 ~ V

BOOT

BOOT

+0.3

+0.3

V

-5 ~ PVCC+0.3

V

-0.3 ~ PVCC+0.3

-5 ~ 35

V

-0.3 ~ 28

-0.3 ~ 7 V

o

C

o

C

o

C

Copyright ANPEC Electronics C orp.

www.anpec.com.tw3

Rev. A.6 - Sep., 2012

APW8813/A

Thermal Resistance

- Junction to Ambient

1.8V)/

Thermal Characteristics (Note 3)

Symbol

θ

JA

Thermal Resistance - Junction to Case

θ

JC

Note 3: θJA and θJC are measured with the component mounted on a high effective the thermal conductivity test board in free air. The

Parameter Typical Value Unit

TQFN4x4-24A

TQFN3x3-20

52

68

°C/W

TQFN4x4-24A

TQFN3x3-20

7

°C/W

8

exposed pad of package is soldered directly on the PCB.

Recommended Operating Conditions (Note 4)

Symbol

VCC, V

V

V

C

VCC

C

C

VTTREF

Note 4: Refer to the typical application circuit.

VCC and PVCC Supply Voltage 4.5 ~ 5.5 V

PVCC

VIN

Converter Input Voltage 3 ~ 28 V

Converter Output Voltage

VDDQ

LDO Output Voltage 0.375 ~ 2.75 V

VTT

I

Converter Output Current 0 ~ 15 A

OUT

I

LDO Output Current -1.5 ~ +1.5 A

VTT

, C

VCC and PVCC Capacitance 1~

PVCC

VTT Output Capacitance 10~100

VTT

VTTREF Output Capacitance 0.01~0.1

TA

Ambient Temperature -40 ~ 85

TJ

Junction Temperature -40 ~ 125

Parameter Range Unit

0.75 ~5.5V/ DDR2 (

DDR3 (1.5V)

V

µF

µF

µF

o

C

o

C

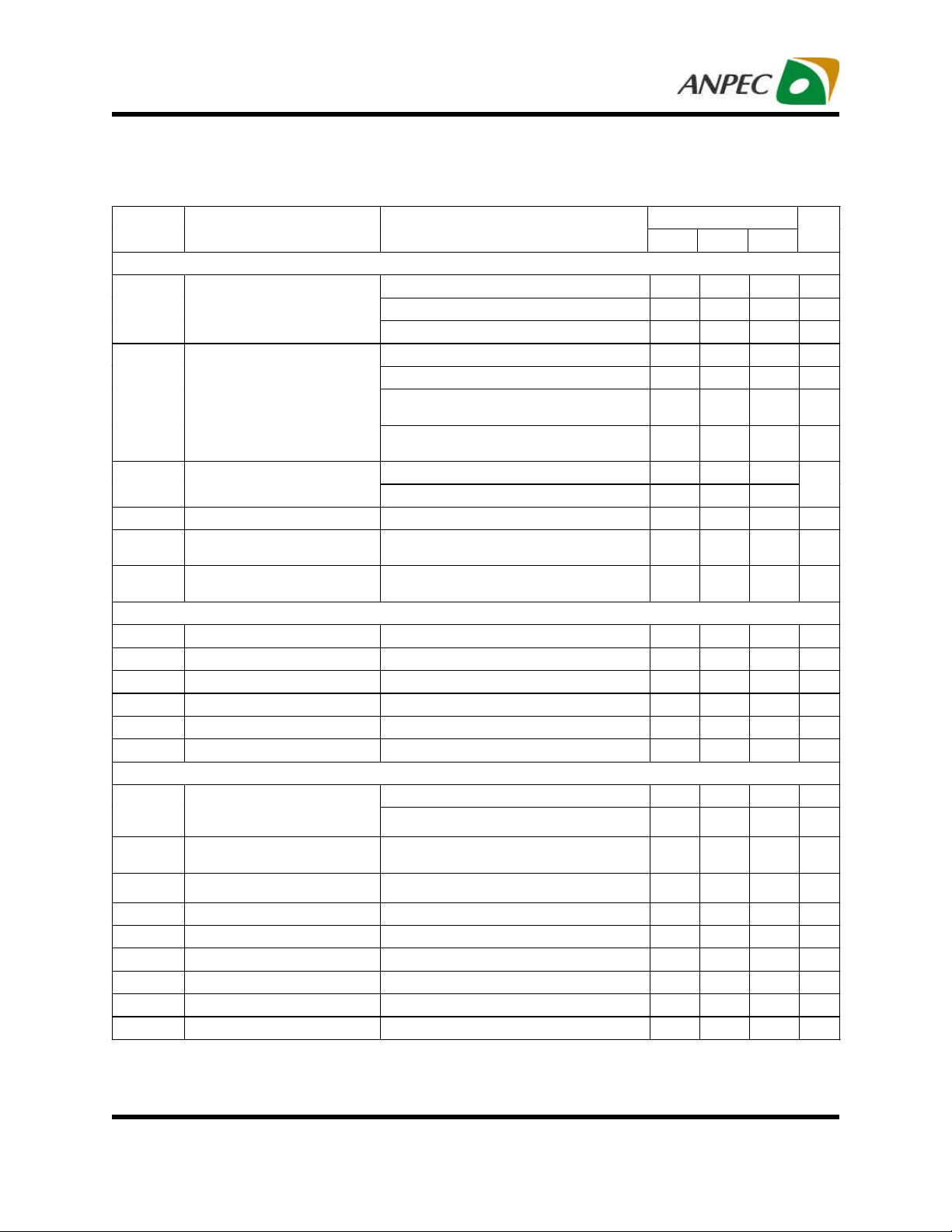

Electrical Characteristics

Refer to the typical application circuits. These specifications apply over V

VCC=VPVCC=VBOOT

otherwise s pecified. Typical values are at TA=25°C.

Symbol

Parameter Test Conditions

SUPPLY CURRENT

I

PVCCSDN

I

VCC

I

VCCSTB

I

VCCSDN

I

LDOIN

I

LDOINSTB

I

LDOINSDN

PVCC Shutdown Current TA =25oC, VS3 = V

VCC Supply Current

VCC Standby Current

TA = 25oC, VS3 = VS5 = 5V, no load,

PVCC Plus VCC Current, No Switching

TA = 25oC, VS3 = 0V, VS5 = 5V, no load,

PVCC Plus VCC Current, No Switching

VCC Shutdown Current TA =25oC, VS3 = V

= 0V, no load - 0.1 1

S5

= 0V, no load - 0.1 1

S5

LDOIN Supply Current TA = 25oC, VS3 = VS5 = 5V, no load - - 40

LDOIN Standby Current TA = 25oC, VS3 = 0V, VS5 = 5V, no load - 0.1 10

LDOIN Shutdown Current TA = 25oC, VS3 = VS5 = 0V, no load - 0.1 1

POWER-ON-RESET

VCC POR Threshold VCC Rising 4.0 4.2 4.4 V

VCC POR Hysteresis - 100 - mV

Copyright ANPEC Electronics C orp.

Rev. A.6 - Sep., 2012

=5V, VIN=12V and TA= -40 ~ 85 °C, unless

APW8813/A

Min. Typ. Max.

- 0.8 3 mA

- 240 800

www.anpec.com.tw4

Unit

µA

µA

µA

µA

µA

APW8813/A

µA

Electrical Characteristics (Cont.)

Refer to the typical application circuits. These specifications apply over V

otherwise s pecified. Typical values are at TA=25°C.

VCC=VPVCC=VBOOT

=5V, VIN=12V and TA= -40 ~ 85 °C, unless

Symbol

VTT OUTPUT

V

VTT Output Voltage

VTT

V

VTT Output Tolerance

VTT

I

Current-Limit

LIM

R

VTT Power MOSFETs R

DS(ON)

I

VTT Leakage Current V

VTTLK

I

VTTSNSLK

I

VTTDIS

VTTSNS Leakage Current V

VTT Discharge Current

VTTREF OUTPUT

V

VTTREF Output Voltage

VTTREF

VTTREF Tolerance

I

VTTREF

VTTREF Source Current V

VTTREF Sink Current V

VDDQ OUTPUT

V

VDDQ

1.8V VDDQ Output Voltage

Parameter Test Conditions

V

DS(ON)

= V

LDOIN

V

= V

LDOIN

V

= V

LDOIN

I

= 0A

VTT

V

= V

LDOIN

I

= 1.5A

VTT

V

= V

LDOIN

I

= 0A

VTT

V

= V

LDOIN

I

= 1.5A

VTT

Sourcing Current

(VIN = 1.8V)

Sinking Current

(VIN = 1.8V)

Sourcing Current

(V

= 1.5V)

IN

Sinking Current

(V

= 1.5V)

IN

Upper MOSFET - 350 500

Lower MOSFET - 350 500

= 1.25V, VS3 = 0V, VS5 = 5V, TA = 25oC -1.0

VTT

= 1.25V, TA = 25oC -1.00 0.01 1.00

VTT

V

= 0.5V, VS3 = VS5 = 0V, TA = 25oC,

VTT

V

= 0V

VREF

V

= V

LDOIN

V

= V

LDOIN

0mA < I

VTTREF

V

= V

LDOIN

0mA < I

VTTREF

V

= V

LDOIN

= 0V 10 20 40 mA

VTTREF

= 1.5V, VTT=0.75V -10 -20

VTTREF

V

= 5V, No load, TA = 25oC 1.787 1.8 1.813 V

VDDQSET

V

= 5V, No load, TA = -40oC to 85oC 1.782 1.8 1.818 V

VDDQSET

V

= 5V, Load = 0 to 10A, TA = 25oC 1.764 1.8 1.836 V

VDDQSET

= 1.8V - 0.9 -

VDDQSNS

= 1.5V - 0.75

VDDQSNS

= 1.8V, V

VDDQSNS

VDDQSNS

VDDQSNS

VDDQSNS

= 1.8V, V

= 1.5V, V

= 1.5V, V

VDDQSNS

VDDQSNS

VDDQSNS

VDDQSNS

TJ = 25oC 1.8 2 3

TJ = 125oC 1.6 - TJ = 25oC -2 -2.2

TJ = 125oC -1.6

TJ = 25oC 1.6 1.8 2.6

TJ = 125oC 1.1 - TJ = 25oC -1.6 -1.8 -2.6

TJ = 125oC -1.1

= 1.8V, V

VDDQSNS

VDDQSNS

< 10mA, V

VTTREF

< 10mA, V

VDDQSNS

= 1.5V, V

=1.8V

= 1.5V

VDDQSNS

VDDQSNS

VDDQSNS

VDDQSNS

APW8813/A

Min. Typ. Max.

/2 - V

,

/2 - V

/2 - V

/2 - V

VTT

VTT,

VTT,

VTT,

-20 - 20

-30 - 30

-20 - 20

-30 - 30

- -

- -

- 1.0

15 25 35 mA

/2 - 0.9 /2 - 0.75

/2 - V

/2 - V

VTTREF

VTTREF

-18 - +18

-20 - +20

Unit

V

-

mV

A

-3

A

mΩ

µA

V

-

mV

-40 mA

Copyright ANPEC Electronics C orp.

www.anpec.com.tw5

Rev. A.6 - Sep., 2012

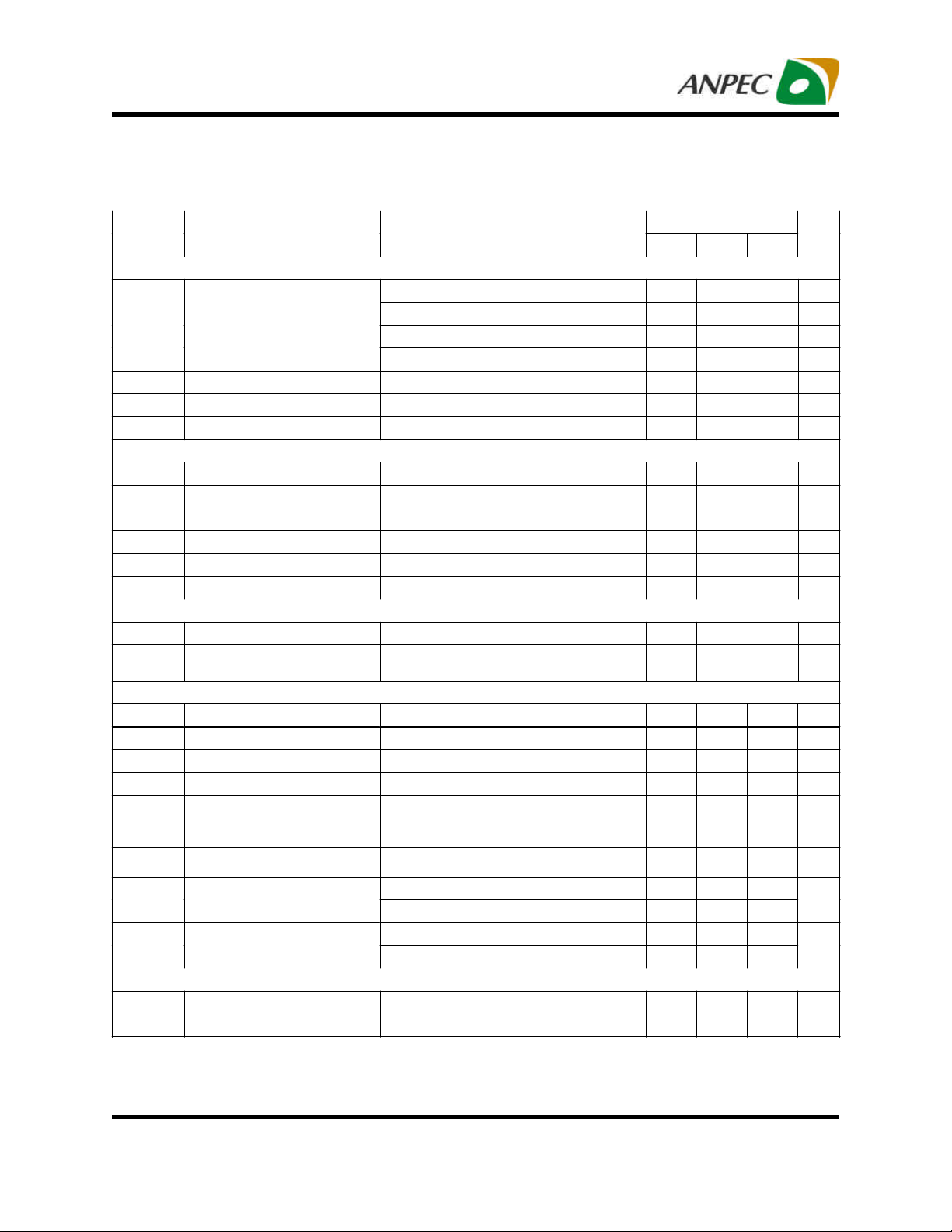

APW8813/A

µA

Electrical Characteristics (Cont.)

Refer to the typical application circuits. These specifications apply over V

VCC=VPVCC=VBOOT

otherwise s pecified. Typical values are at TA=25°C.

Symbol

Parameter Test Conditions

VDDQ OUTPUT (CONT.)

V

= 0V, No load, TA = 25oC 1.488 1.5 1.512 V

VDDQSET

V

1.5V VDDQ Output Voltage

VDDQ

V

= 0V, No load, TA = -40oC to 85oC 1.485 1.5 1.515 V

VDDQSET

V

= 0V, Load = 0 to 10A, TA = 25oC 1.47 1.5 1.53 V

VDDQSET

Adjust Mode, TA = 25oC 0.745 0.75 0.755 V

Adjust Mode, TA = -40oC to 85oC 0.7425 0.75 0.7575 V

V

VDDQSET

VDDQSET Regulation Voltage

Adjust Mode, TA = 25oC,

V

= 4.5V to 5.5V, VIN = 3V to 28V

VCC

Adjust Mode, TA = 25oC,

R

VDDQSNS

VDDQSNS Input Impedance

VDDQSET Input Current V

VDDQ Discharge Current

LDOIN Discharge Current

Load = 0 to 10A, V

V

= 0V (DDR3) - 240

VDDQSET

V

= 5V (DDR2) - 288

VDDQSET

= 0.78V -0.1

VDDQSET

VS3 = VS5 = 0V, V

V

= 0V (Non-Tracking)

MODE

VS3 = VS5 = 0V, V

V

= 0.5V (Tracking, only for APW8813)

MODE

= 4.5V to 5.5V

VCC

= 0.5V,

VDDQSNS

= 0.5V,

VDDQSNS

PWM CONTROLLERS

FSW Operating Frequency Adjustable Frequency 100

TSS Internal Soft-Start Time S5 is High to V

TO On Time VIN = 19V, V

T

Minimum off Time - 300

OFF(MIN)

T

Minimum on Time 80 110 140 ns

ON(MIN)

Regulation 0.9 1.2 1.5 ms

VDDQ

= 1.5V, R

VDDQ

= 1.2M 235 277 320 ns

TON

Zero-Crossing Threshold -9.5 0.5 10.5 mV

VDDQ PROTECTIONS

TA = 25oC 9 10 11

CS Pin Sink Current

OCP Comparator Offset

VDDQ Current-Limit Setting

Range

VDDQ OVP Trip Threshold V

Temperature Coefficient, On The Basis of 25°C - 4500

(V

- VCS) - (V

PVCC

V

- VCS = 60mV

PVCC

V

30 - 200 mV

PVCC-VCS

Rising 120 125 130 %

VDDQ

PHASE

- PGND),

VDDQ OVP Debounce Delay VFB Rising, DV = 10mV - 1.5 VDDQ UVP Trip Threshold V

Falling 60 70 80 %

VDDQ

VDDQ UVP Trip Hysteresis - 3 - %

VDDQ UVP Debounce - 10 -

VDDQ UVP Enable Delay - 2 - ms

=5V, VIN=12V and TA= -40 ~ 85 °C, unless

APW8813/A

Min. Typ. Max.

-0.1

- +0.1 %

Unit

-1 - +1 %

kΩ

-

- +0.1

15 25 - mA

400 550

- mA

- 550 kHz

- ns

µA

ppm/

-

-15 0 +15 mV

o

µs

µs

C

Copyright ANPEC Electronics C orp.

www.anpec.com.tw6

Rev. A.6 - Sep., 2012

APW8813/A

Electrical Characteristics (Cont.)

Refer to the typical application circuits. These specifications apply over V

otherwise s pecified. Typical values are at TA=25°C.

VCC=VPVCC=VBOOT

=5V, VIN=12V and TA= -40 ~ 85 °C, unless

Symbol

Parameter Test Conditions

APW8813/A

Min. Typ. Max.

Unit

PGOOD

PGOOD in from Lower (PGOOD Goes High) 87 90 93 %

V

PGOOD Threshold

PGOOD

PGOOD Low Hysteresis (PGOOD Goes Low) - 3 - %

PGOOD in from Higher (PGOOD Goes Low) 120 125 130 %

PGOOD High Hysteresis (PGOOD Goes High) - 3 - %

I

PGOOD Leakage Current V

PGOOD

PGOOD Sink Current V

PGOOD Debounce Time - 63 -

= 5V - 0.1 1.0

PGOOD

= 0.5V 2.5 7.5 - mA

PGOOD

µA

µs

GATE DRIVERS

UGATE Pull-Up Resistance BOOT-UGATE = 0.5V - 5 7

UGATE Sink Resistance UGATE-PHASE = 0.5V - 1 2.5

LGATE Pull-Up Resistance PVCC-LGATE = 0.5V - 5 7

LGATE Sink Resistance LGATE-PGND = 0.5V - 1 2.5

UGATE to LGATE Dead Time UGATE falling to LGATE rising, no load - 40 - ns

LGATE to UGATE Dead Time LGATE falling to UGATE rising, no load - 40 - ns

BOOTSTRAP DIODE

Forward Voltage V

Reverse Leakage

- V

PVCC

V

= 30V, V

BOOT

TA = 25oC

, IF = 10mA, TA = 25oC - 0.5 0.8 V

BOOT

PHASE

= 25V, V

PVCC

= 5V,

- - 0.5

µA

LOGIC THRESHOLD

VIH S3, S5 High Threshold Voltage S3, S5 Rising 1.6 - - V

VIL S3, S5 Low Threshold Voltage S3, S5 Falling - - 0.3 V

S5 to S3 Debounce Time S5 from L to H, VDDQ, VREF are on - 90 S3 to S0 Debounce Time S3 from L to H, VTT is on - 10 -

I

Logic Input Leakage Current VS3 = VS5 = V

ILEAK

V

FCCMTHR

V

FCCMTHF

V

THMODE

FCCM High Threshold (Only for

APW8813)

FCCM Low Threshold (Only for

APW8813)

MODE Threshold (Only for

APW8813)

VDDQSET Threshold

In Automatic PFM/PWM Mode 4.7 - - V

In Force PWM Mode - - 0.1 V

No Discharge 4.7 - Non-tracking Discharge - - 0.1

V

= 1.5V 0.08 0.15 0.4

VDDQ

V

= 1.8V 3.5 4 4.5

VDDQ

= 5V, TA = 25oC -1 - 4.7

MODE

µs

µs

µA

THERMAL SHUTDOWN

TSD Thermal Shutdown Temperature TJ Rising - 160 -

Thermal Shutdown Hysteresis - 25 -

o

oC

Ω

Ω

Ω

Ω

V

V

C

Copyright ANPEC Electronics C orp.

www.anpec.com.tw7

Rev. A.6 - Sep., 2012

APW8813/A

this pin connects to VDDQ, it is tracking discharge state. When this pin connects to GND, it is

Also it is current sense comparator positive input terminal and the ground

as

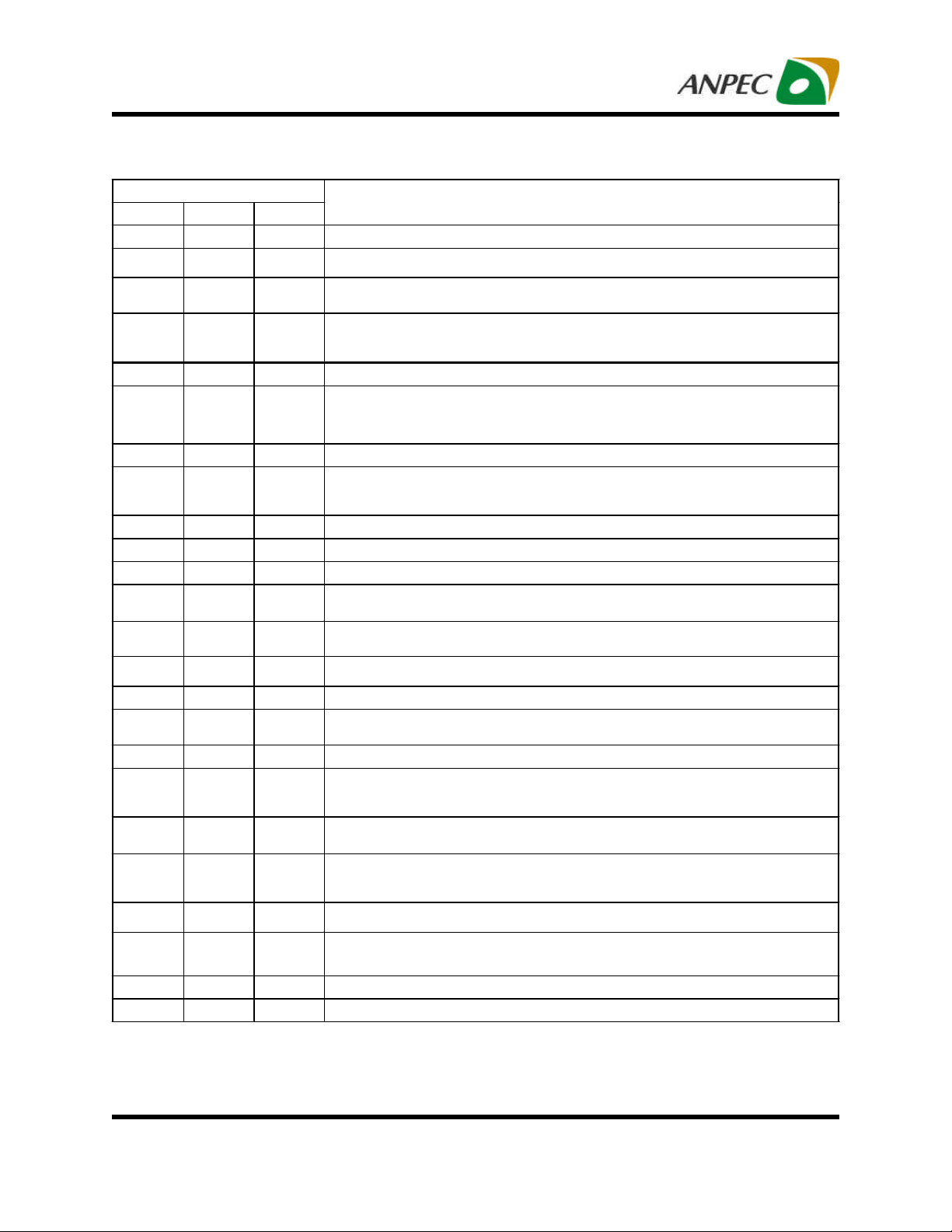

Pin Description

PIN

APW8813 APW8813A NAME

1 1 VTTGND Power ground output for the VTT LDO.

2 2 VTTSNS

3 3 GND

4 - MODE

5 4 VTTREF VTTREF buffered reference output.

6 - FCCM

7 - NC No Connection.

8 5 VDDQSNS

9 6 VDDQSET VDDQ output voltage setting pin.

10 7 S3 S3 signal input.

11 8 S5 S5 signal input.

12 9 TON

13 10 PGOOD

14 11 VCC

15 12 PVCC 5V power supply voltage input pin for low-side MOSFET gate driver on TQFN-24 package.

16 13 CS

17 - CS_GND Current sense comparator positive input terminal and the ground for power good circuit.

18 14 PGND

19 15 LGATE

20 16 PHASE

21 17 UGATE

22 18 BOOT

23 19 LDOIN Supply voltage input for the VTT LDO.

24 20 VTT Power output for the VTT LDO .

Voltage sense input for the VTT LDO. Connect to plus terminal of the VTT LDO output

capacitor.

Signal ground for the PWM controller and VTT LDO. Connect to minus terminal of the VTT

LDO output capacitor.

Discharge mode setting pin. When this pin connects to VCC, it is no discharge state. When

non-tracking discharge state.

Selection pin for PWM controller to operate in either forced PWM or automatic PWM/PFM

mode. Force PWM mode is enable when FCCM pin is pulled below the falling threshold

voltage V

threshold voltage V

VDDQ reference input for VTT and VTTREF. Power supply for the VTTREF. Discharge

current sinking terminal for VDDQ non-tracking discharge. Output voltage feedback input for

VDDQ output if VDDQSET pin is connected to VCC or GND.

This Pin is Allowed to Adjust The Switching Frequency. Connect a resistor R

pin to PHASE VIN terminal.

Power-good output pin. PGOOD is an open drain output used to Indicate the status of the

output voltage. When VDDQ output voltage is within the target range, it is in high state.

Filtered 5V power supply input for internal control circuitry. Connect R-C network from PVCC

to VCC.

Over-current trip voltage setting input for R

through the voltage setting resistor.

Power ground of the LGATE low-side MOSFET driver. Connect the pin to the Source of the

low-side MOSFET.

of power good circuit on SSOP-20 package.

Output of the low-side MOSFET driver for PWM. Connect this pin to Gate of the low-side

MOSFET. Swings from PGND to VCC.

Junction point of the high-side MOSFET Source, output filter inductor and the low-side

MOSFET Drain. Connect this pin to the Source of the high-side MOSFET. PHASE serves

the lower supply rail for the UGATE high-side gate driver.

Output of the high-side MOSFET driver for PWM. Connect this pin to Gate of the high-side

MOSFET.

Supply Input for the UGATE Gate Driver and an internal level-shift circuit. Connect to an

external capacitor and diode to create a boosted voltage suitable to drive a logic-level

N-channel MOSFET.

, and force PWM is disabled when the FCCM pin is pulled above the rising

FCCMTHF

FCCMTHR

.

FUNCTION

current sense scheme if connected to VCC

DS(ON)

TON

from TON

Copyright ANPEC Electronics C orp.

Rev. A.6 - Sep., 2012

www.anpec.com.tw8

APW8813/A

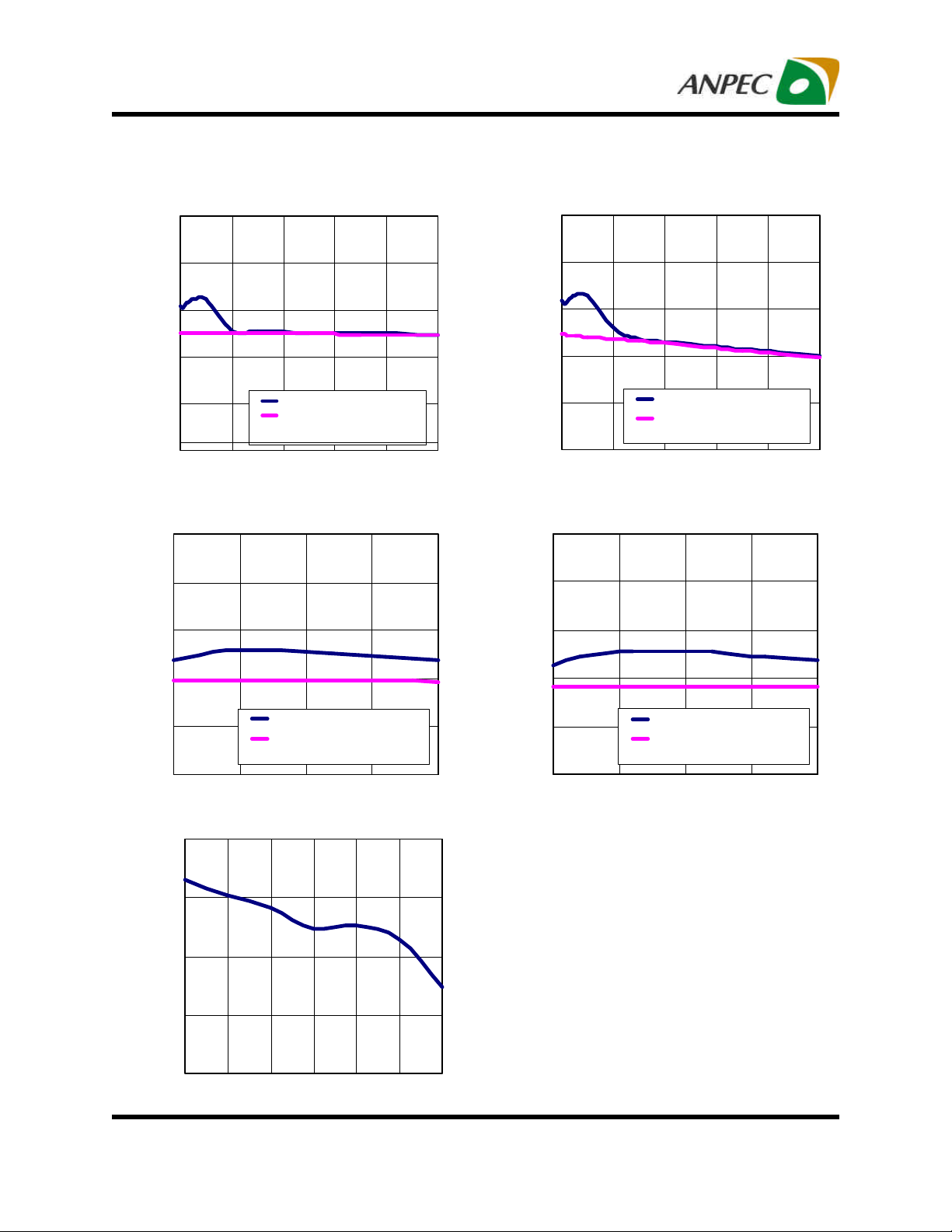

Typical Operating Characteristics

VDDQ Voltage Regulation vs.

Junction Temperature

VDDQ Voltage Regulation vs.

Junction Temperature

1.55

1.53

1.51

1.49

1.47

VDDQ Output Voltage (V)

1.45

-40 -20 0

VDDQSET = GND, VDDQ = 1.5V

20 40 60 80 100 120

Junction Temperature, TJ (oC)

Supply Current vs. Junction

3.0

Temperature

2.5

2

(mA)

VCC

1.5

Plus I

1

Supply Current,

PVCC

I

Shutdown Current,

0.5

1.85

1.83

1.81

1.79

VDDQ Output Voltage (V)

1.77

1.75

-40 -20 0

VDDQSET = VCC, VDDQ = 1.8V

20 40 60 80 100 120

Junction Temperature, TJ (oC)

Shutdown Current vs. Junction

Temperature

1.0

0.8

(uA)

VCC

0.6

Plus I

0.4

PVCC

I

0.2

0

-40 -20 0

20 40 60 80 100 120

Junction Temperature, TJ (oC)

CS Pin Sink Current vs. Junction

16

14

12

10

8

6

CS Sink Current (uA)

4

2

0

-40 -20 0

Copyright ANPEC Electronics C orp.

Rev. A.6 - Sep., 2012

Temperature

20 40 60 80 100 120

Junction Temperature, TJ (oC)

0

-40 -20 0

330

320

(KHz)

310

SW

300

290

280

Switching Frequency,F

270

-40 -20 0

20 40 60 80 100 120

Junction Temperature, TJ (oC)

Frequency vs. Junction

Temperature

20 40 60 80 100 120

Junction Temperature, TJ (oC)

www.anpec.com.tw9

APW8813/A

Typical Operating Characteristics

Load Regulation, V

FSW=300kHz

1.55

VDDQ

=1.5V

1.85

Load Regulation, V

FSW=300kHz

VDDQ

=1.8V

(V)

VDDQ Voltage, V

(V)

VDDQ

1.53

VDDQ

1.51

1.49

1.47

1.45

1.55

1.53

1.51

1.49

PFM Mode

Force PWM Mode

(Only for APW8813)

VDDQ Current (A)

Line Regulation, V

FSW=300kHz

VDDQ

=1.5V

1.83

(V)

VDDQ

1.81

1.79

VDDQ Voltage, V

1.77

PFM Mode

Force PWM Mode

(Only for APW8813)

1086420

1.75

1086420

VDDQ Current (A)

Line Regulation, V

VDDQ

=1.8V

FSW=300kHz

1.85

1.83

(V)

VDDQ

1.81

1.79

VDDQ Voltage, V

1.47

PFM Mode

Force PWM Mode

(Only for APW8813)

1.45

5 10

15 20 25

Input Voltage (V)

VTT Load Regulation

0.76

(V)

0.755

VTT

0.75

VTT Voltage, V

0.745

0.74

-1.5

Copyright ANPEC Electronics C orp.

Rev. A.6 - Sep., 2012

-1 -0.5

VTT Current, I

0

VTT

0.5 1 1.5

(A)

VDDQ Voltage, V

1.77

1.75

5 10

PFM Mode

Force PWM Mode

(Only for APW8813)

15 20 25

Input Voltage (V)

www.anpec.com.tw10

Loading...

Loading...