ANPEC APW7037RC-TR, APW7037KC-TU, APW7037KC-TR, APW7037ARC-TU, APW7037ARC-TR Datasheet

...

APW7037/A

8-PIN Synchronous Buck PWM Controller

Features

••

•

Operating with Single 5V or 12V Input

••

••

•

Drives N-Channel MOSFETs

••

••

•

Simple Single-Loop Control Design

••

− Voltage-Mode PWM Control

− Full 0% to 100% Duty Ratio

− Fast Transient Response

••

• ±2% Output Voltage Accuracy Over Temperature

••

••

• Under-Voltage Protection for Output

••

••

• 200kHz Constant Frequency Operation

••

(400kHz for APW7037A)

••

• Small size, 8-PIN Package (SOIC or TSSOP)

••

Applications

••

• Graphics Cards

••

••

• DDR Memory Power Supply

••

••

• DDR Memory Termination Voltage

••

General Description

The APW7037/A controller IC is designed to provide

a low cost synchronous Buck regulator for on-board

DC to DC converter applications. The APW7037 to-

gether with dual N-channel MOSFETs such as

APM7313, provide a low cost solution for such

applications. This device features an internal 200KHz

oscillator (400KHz for “A” version), Power-On-Reset

(POR) for both VCC and VC supplies, an external

programmable soft-start function as well as output

under-voltage detection that latches off the device

when an output short is detected.

Pin Description

1

VCC

LDRV

GND HDRV

2

3

45

8FB

SS

7

COMP

6

VC

••

• Low-Voltage Distributed Power Supplies

••

Ordering and Marking Information

APW7037/A

Handling Code

Temp. Range

Package Code

APW 7037/A K :

APW 7037/A R :

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise

customers to obtain the latest version of relevant information to verify before placing orders.

Copyright ANPEC Electronics Corp.

Rev. A.4 - May, 2003

APW 7037/A

XXXXX

APW 7037/A

XXXXX

Package Code

K : S O-8 R : TS SO P-8

Operating Junction Temp. Range

C : 0 to 70°C

Handling Code

TU : Tube

TR : Tape & R eel

XXXXX - Date Code

XXXXX - Date Code

www.anpec.com.tw1

APW7037/A

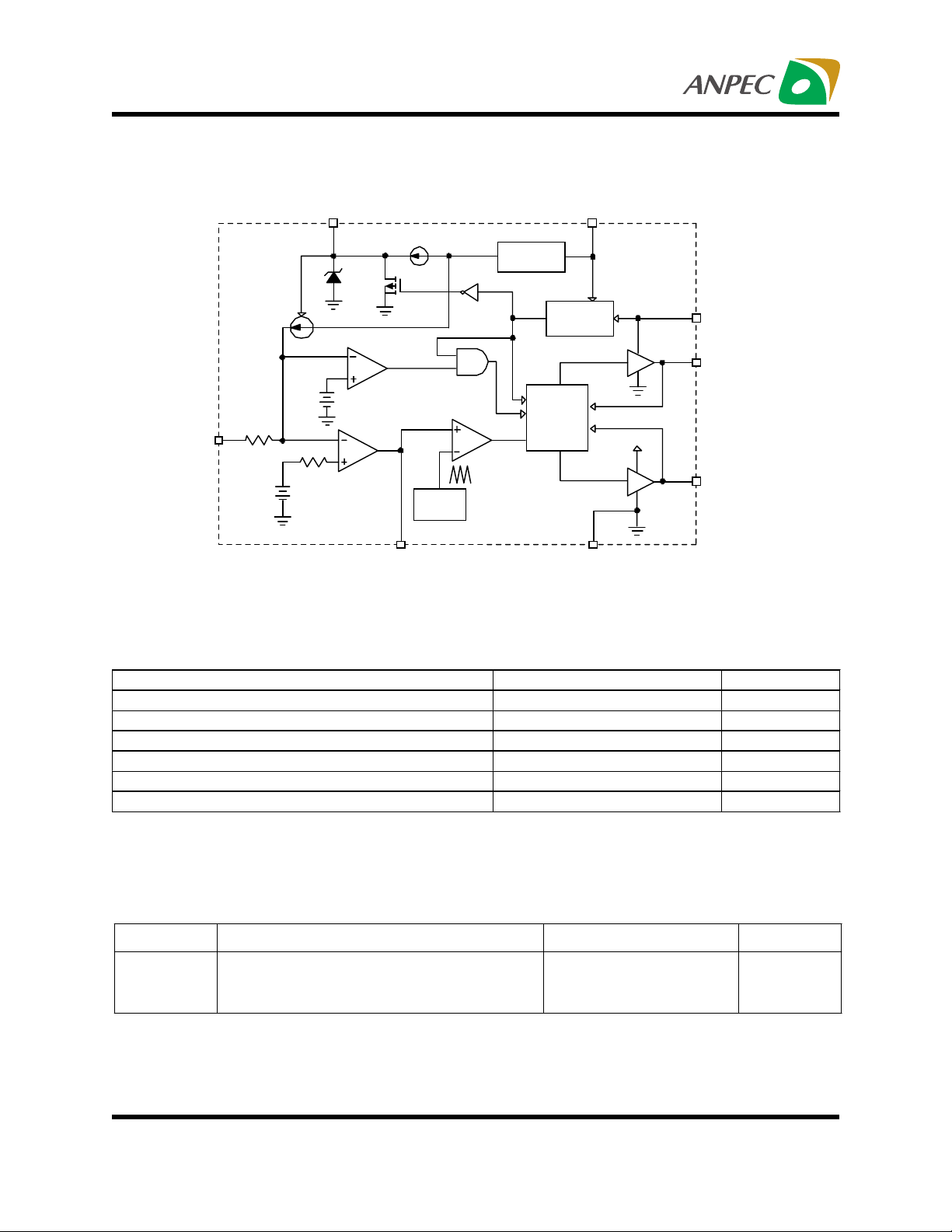

Block Diagram

SS

20uA

3.3V

Max .

64uA

Under-Voltage

V

FBUV

FB

25k

25k

V

REF

Error

Amp.

COMP

OSC

F

OSC

Absolute Maximum Ratings

4.5V

Regulator

PW M

POR

Po w e r

On Reset

Gate

Control

VCC

VC

HDRV

VCC

LDRV

GND

Description Rating Unit

VCC to GND -0.2~30 V

VC to GND -0.2~30 V

Operating Junction Temperature 0~125 °C

Storage Temperature -65~150 °C

Soldering Temperature (10 Seconds) 300 °C

Minimum ESD Rating ±2 kV

Thermal Characteristics

Symbol Parameter Value Unit

θ

JA

Copyright ANPEC Electronics Corp.

Rev. A.4 - May, 2003

Thermal Resistance in Free Air

8-pin SOIC

8-pin TSSOP

160

124

°

www.anpec.com.tw2

C/W

APW7037/A

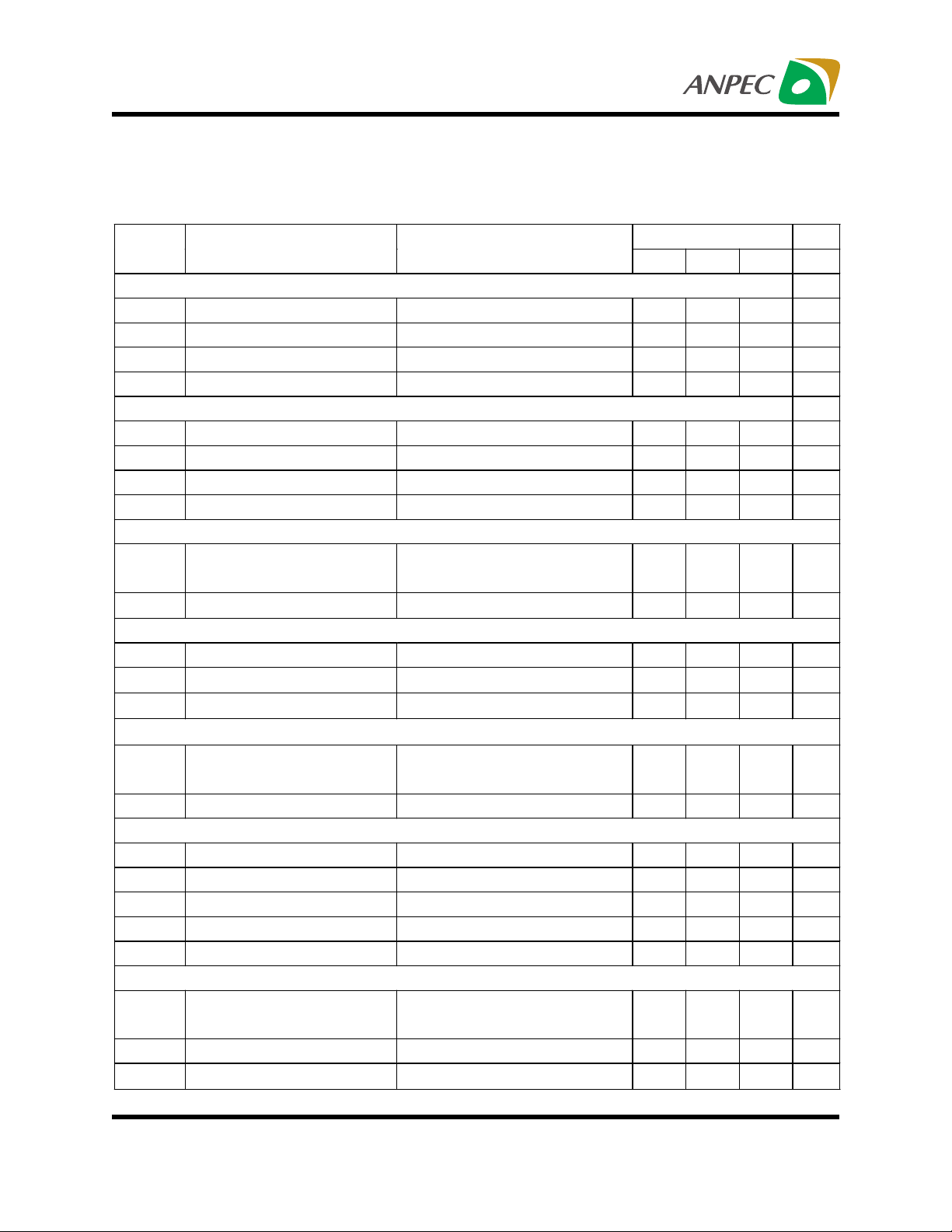

Electrical Characteristics

Unless otherwise specified, these specifications apply over VCC=5V, VC=12V and TA=0 to 70°C. Typical values refer

A=25°C.

to T

APW7037/A Unit

Symbol Parameter Test Conditions

SUPPLY CURRENT

I

I

CCQ

I

VCC Dynamic Supply Current F

CC

I

VC Dynamic Supply Current F

C

VCC Static Supply Current

VC Static Supply Current SS=GND 0.2 0.4 1 mA

CQ

=200KHz, CL=1500pF 2 3 5 mA

OSC

=200KHz, CL=1500pF 2 5.5 8 mA

OSC

SS=GND

POWER-ON RESET

Rising VCC Threshold 4.0 4.2 4.4 V

VCC POR Hysteresis 0.25 V

Rising VC Threshold 3.1 3.3 3.5 V

VC POR Hysteresis 0.2 V

OSCILLATOR

F

V

∆

Free Running Frequency

OSC

Ramp Amplitude

OSC

1.10 V

APW7037

APW7037A

ERROR AMPLIFIER

I

I

FB Pin Input Bias Current SS=3V, VFB=1V

FB1

FB Pin Input Bias Current

FB2

SS=0V, V

FB

=1V

GM Transconductance 450 600 750

REFERENCE VOLTAGE

V

FB Pin Regulation Voltage

FB

APW7037

APW7037A

LREG VFB Line Regulation VCC = 5~12V 0.2 0.35 %

GATE DRIVERS

HDRV Rising Time CL = 1500pF 20 50 nS

HDRV Falling Time CL = 1500pF 15 50 nS

LDRV Rising Time CL = 1500pF 25 50 nS

LDRV Falling Time CL = 1500pF 25 50 nS

Dead Band Time 50 150 250

PROTECTION

V

FB Under-Voltage Threshold VFB Falling APW7037

FBUV

APW7037A

V

Shutdown Threshold Voltage Pull the voltage of SS pin 0.5 V

SD

Soft-Start Current SS=0 10 20 30

I

SS

Min. Typ. Max.

0.5 1.5 3 mA

180

360

200

400

220

440

1nA

-64

µ

1.225

0.784

0.4

0.3

1.250

0.800

0.6

0.4

1.275

0.816

0.8

0.5

KHz

A

µ

mho

V

nS

V

A

µ

Copyright ANPEC Electronics Corp.

Rev. A.4 - May, 2003

www.anpec.com.tw3

APW7037/A

Functional Pin Description

FB (Pin 1)

Connect this pin to the output (VOUT) of the PWM con-

verter via an external resistor divider to provide a volt-

age feedback path for the converter. The output volt-

age set by the resistor divider is determined using the

following formula :

OUT

R

()

VOUT = VREF x

1+

GND

R

where ROUT is the resistor connected from VOUT to FB

, and RGND is the resistor connected from FB to ground.

The voltage at this pin is also monitored for Under-

Voltage protection.

VCC (Pin 2)

Connect this pin to input voltage from 5V to 20V. This

pin provides the bias for the control circuitry and the

low-side power MOSFET driver (LDRV). The voltage

at this pin is monitored for Power-On Reset (POR)

purpose.

HDRV (Pin 5)

Connect this pin to the gate of the high-side power

MOSFET. This pin provides the gate drive for the

MOSFET.

VC (Pin 6)

This pin provides bias voltage to the high-side

MOSFET driver. A bootstrap circuit may be used to

pump a boot voltage for enforcing the driving capabil-

ity of the gate driver and improving the performance of

the MOSFET.

COMP (Pin 7)

This pin is the output of the error amplifier. Add an

external resistor-capacitor network to provide a loop

compensation for the PWM converter.

SS (Pin 8)

LDRV (Pin 3)

Connect this pin to the gate of the low-side power

MOSFET. This pin provides the gate drive for the

MOSFET.

GND (Pin 4)

Signal and power ground for the IC. All voltage levels

are measured with respect to this pin.

Copyright ANPEC Electronics Corp.

Rev. A.4 - May, 2003

Connect a capacitor from this pin to ground.This

capacitor, along with an internal 20uA current source,

sets the soft-start interval of the PWM converter and

prevents the outputs from overshoot as well as limits

the input current. Pull this pin below 0.5V can shut-

down the converter.

www.anpec.com.tw4

Loading...

Loading...