Page 1

Engineer To Engineer Note EE-63

Technical Notes on using Analog Devices’ DSP components and development tools

Phone: (800) ANALOG-D, FAX: (781) 461-3010, EMAIL: dsp.support@analog.com, FTP: ftp.analog.com, WEB: www.analog.com/dsp

Copyright 1999, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers’

products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective

holders. Information furnished by Analog Devices Applications and Development Tools Engineers is believed to be accurate and reliable, however no responsibility is

assumed by Analog Devices regarding the technical accuracy of the content provided in all Analog Devices’ Engineer-to-Engineer Notes.

Considerations for FLASH PROMS

with Timing Requirements

By H.D.

_______________________________________

Question:

I need to know the minimum time between the

rising edge of /RESET and the falling edge of /BMS

when EBOOT is high and LBOOT is low. This

parameter is important since flash PROMS also

have a /RESET input and a minimum timing

requirement between the rising edge of /RESET and

falling edge of /CS and /OE. I may need to

implement an early /RESET for the flash PROM,

but until I know how soon the SHARC asserts

/BMS, I don't know how much earlier the PROM

needs to be reset.

Answer:

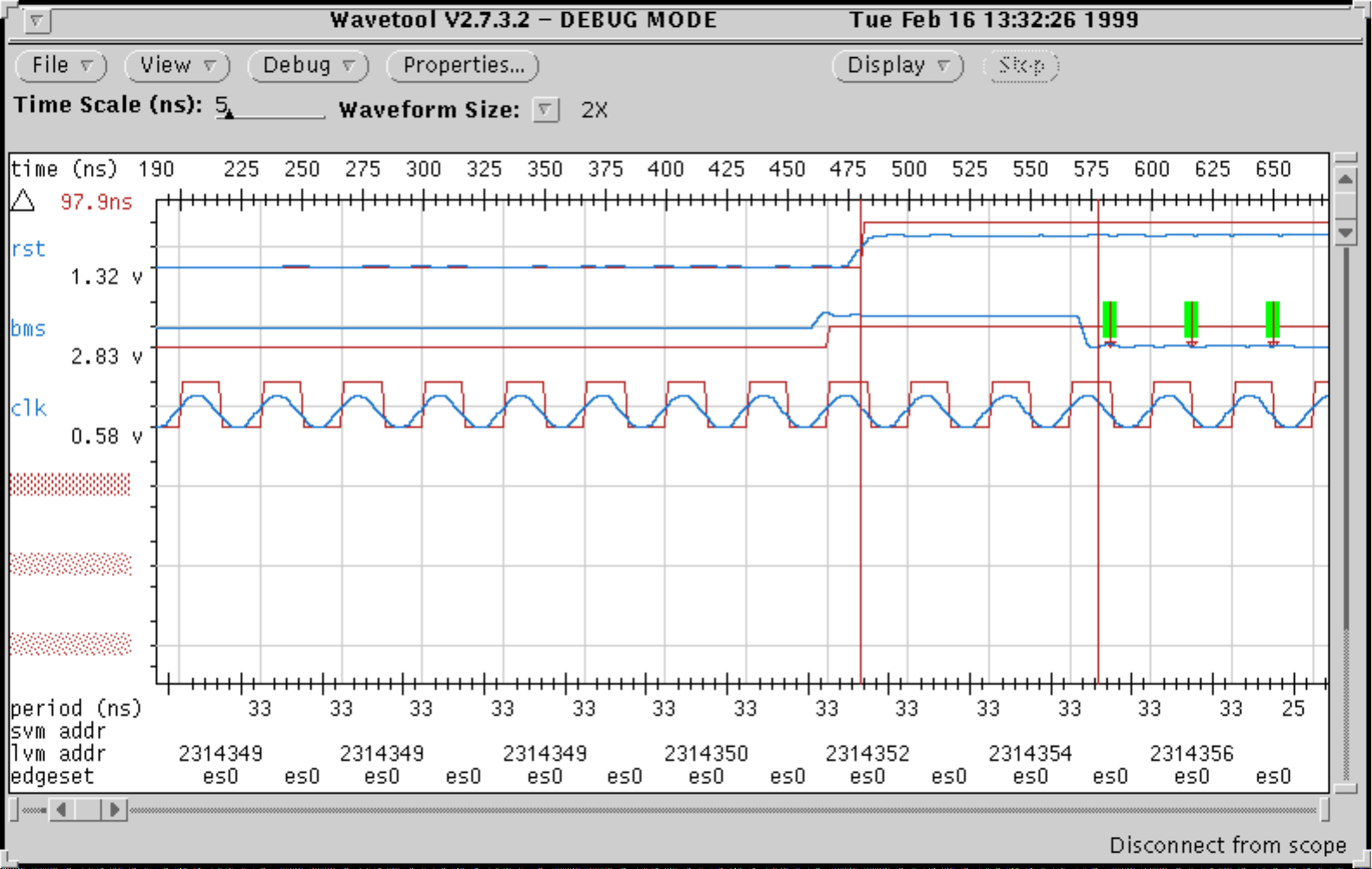

Attached is a waveform for the 21065L from a

digital scope that should help make this clear.

The following applies only to the 21060/60L,

21062/62L and 21061/61L:

If the first cycle that RESET is deasserted (goes

high) is cycle #1, then BMS will be asserted (go

LOW) in cycle #6.

The following applies only to the 21065L:

If the first cycle that RESET is deasserted (goes

high) is cycle #1, then BMS will be asserted (go

LOW) in cycle #4.

Note: A cycle is defined as a CLKIN cycle. ie: if

CLKIN is 30MHz, a cycle is 33.3ns in length.

a

Page 2

Loading...

Loading...