Engineer-to-Engineer Note EE-299

r

Technical notes on using Analog Devices DSPs, processors and development tools

Visit our Web resources http://www.analog.com/ee-notes and http://www.analog.com/processors o

e-mail processor.support@analog.com or processor.tools.support@analog.com for technical support.

Estimating Power Dissipation for ADSP-21368 SHARC® Processors

Contributed by Chris C. and John C. Rev 3 – June 22, 2009

Introduction

This EE-Note discusses power consumption of

ADSP-21367, ADSP-21368, and ADSP-21369

SHARC® processors (hereafter referred to as

ADSP-21368 processors) based on

characterization data measured over power

supply voltage, core frequency (CCLK), and

junction temperature (TJ). The intent of this

document is to assist board designers in

estimating their power budget for power supply

design and thermal relief designs using ADSP21368 processors.

ADSP-21368 processors are members of the

SIMD SHARC family of processors, featuring

Analog Devices Super Harvard Architecture.

Like other SHARC processors, the ADSP-21368

is a 32-bit processor optimized for high-precision

signal processing applications.

drivers (i.e., the I/O). The following sections

detail how to derive both of these components

for estimating total power consumption based on

different dynamic activity levels, I/O activity,

power supply settings, core frequencies, and

environmental conditions.

Estimating Internal Power Consumption

The total power consumption due to internal

circuitry (on the V

static power component and dynamic power

component of the processor’s core logic. The

dynamic portion of the internal power is

dependent on the instruction execution sequence,

the data operands involved, and the instruction

rate. The static portion of the internal power is a

function of temperature and voltage; it is not

related to processor activity.

supply) is the sum of the

DDINT

ADSP-21368 processors are offered in the

commercial and industrial temperature ranges at

core clock frequencies of 266-333 and 400 MHz.

The 266-333 MHz processors operate at a core

voltage of 1.2 V (V

), and the 400 MHz

DDINT

processors operate at a core voltage of 1.3 V

(V

operates at 3.3 V (V

). The I/O of all ADSP-21368 processors

DDINT

).

DDEXT

Analog Devices provides current consumption

figures and scaling factors for discrete dynamic

activity levels. System application code can be

mapped to these discrete numbers to estimate the

dynamic portion of the internal power

consumption for an ADSP-21368 processor in a

given application.

The total power consumption of the ADSP21368 processor is the sum of the power

consumed for each of the power supply domains

(V

DDINT, VDDEXT,

and A

). The total power

VDD

consumption has two components: one due to

internal circuitry (i.e., the core and the PLL), and

the other due to the switching of external output

Copyright 2006-2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of

customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property

of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however

no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Engineer-to-Engineer Notes.

Internal Power Vector Definitions and Activity Levels

The following power vector definitions define

the dynamic activity levels that apply to the

internal power vectors shown in Table 1.

I

DD-IDLE VDDINT

supply current for idle

activity. Idle activity is the core executing the

IDLE instruction only, with no core memory

accesses, no DMA, and no interrupts.

I

DD-INLOW VDDINT

supply current for low

activity. Low activity is the core executing a

single-function instruction fetched from

internal memory, with no core memory

accesses, no DMA, and no activity on the

external port.

I

DD-INMED VDDINT

supply current for medium

activity. Medium activity is the core

executing a multi-function instruction fetched

from internal memory and a NOP, with 8 core

memory accesses per CLKIN cycle (DMx64),

DMA through three SPORTs running at

3.47 MHz, and no SDRAM or AMI activity

on the external port. The DMA is chained to

itself (running continuously) and does not use

interrupts. The bit pattern for each core

memory access and DMA is random.

I

DD-INHIGH VDDINT

supply current for high

activity. High activity is the core executing a

multi-function instruction fetched from

internal memory, with 16 core memory

accesses per

CLKIN cycle (DMx64) and DMA

through three SPORTs running at 3.47 MHz,

and no SDRAM or AMI activity on the

external port. The DMA is chained to itself

(running continuously) and does not use

interrupts. The bit pattern for each core

memory access and DMA is random.

multi-function instruction fetched from

internal memory and/or cache, with 32 core

memory accesses per CLKIN cycle (DMx64,

PMx64), DMA through six SPORTs running

at 41.67 MHz, and no SDRAM or AMI

activity on the external port. The DMA is

chained to itself (running continuously) and

does not use interrupts. The bit pattern for

each core memory access and DMA is

random.

The test code used to measure I

represents worst-case

INPEAK

DD-

processor operation. This activity

level is not sustainable under

normal application conditions.

I

DD-INPEAK-TYP VDDINT

supply current for

typical peak activity. Typical peak activity is

the core executing a multi-function

instruction fetched from internal memory

and/or cache, with 32 core memory accesses

per CLKIN cycle (DMx64, PMx64), DMA

through six SPORTs running at 41.67 MHz,

DMA through one SPI running at 833 KHz,

and SDRAM accesses through the external

port running at 166 MHz. The DMA is

chained to itself (running continuously) and

does not use interrupts. The bit pattern for

each core memory access, DMA and

SDRAM access is random. The SDRAM

accesses are split between 60% reads and

40% writes.

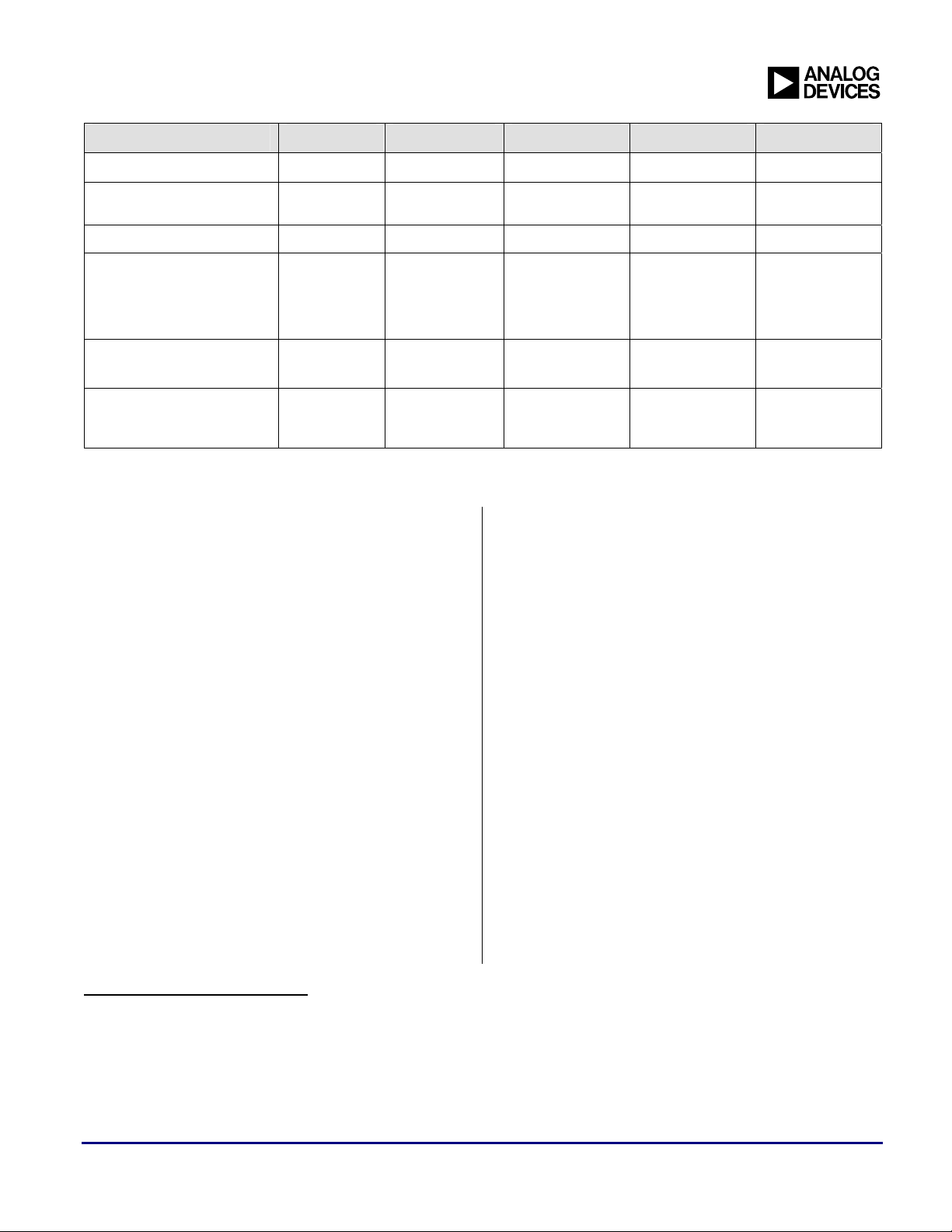

Table 1 summarizes the low, medium, high,

peak, and typical peak dynamic activity levels

corresponding to the internal power vectors

listed above and in Table 2.

I

DD-INPEAK VDDINT

supply current for peak

activity. Peak activity is the core executing a

Estimating Power Dissipation for ADSP-21368 SHARC® Processors (EE-299) Page 2 of 12

Operation Low Medium High Peak Peak (Typical)

Instruction Type Single-function Multi-function Multi-function Multi-function Multi-function

Instruction Fetch Int Memory Int Memory,

NOP

Core Memory Access 1 None 8 per tCK cycle 2 16 per tCK cycle 2 32 per tCK cycle 3 32 per tCK cycle 3

DMA Transmit Int to Ext

Ext Port SDRAM

SPORTs

SPI

Data Bit Pattern for Core

Memory Access and DMA

Ratio – Continuous Instruction

Loop to SDRAM Control Code

Table 1. Dynamic activity level definitions

SDCLK only

N/A

N/A

N/A Random Random Random Random

100% Instruct

Loop

SDCLK only

3 @ 1/96*CCLK

N/A

100% Instruction

Loop

Int Memory Int Memory,

Cache

SDCLK only

3 @ 1/96*CCLK

N/A

100% Instruction

Loop

SDCLK only

6 @ 1/8*CCLK

N/A

100% Instruction

Loop

Int Memory,

Cache

60/40 RD/WR

6 @ 1/8*CCLK

N/A

50::50

60::40

70::30

Estimating I

Dynamic Current, I

DDINT

DD-DYN

Two steps are involved in estimating the

dynamic power consumption due to the internal

circuitry (i.e., on the V

supply). The first

DDINT

step is to determine the dynamic baseline current,

and the second step is to determine the

percentage of activity for each discrete power

vector with respect to the entire application.

IDD Baseline Dynamic Current, I

The ADSP-21368 I

DD_BASELINE_DYN

DD-BASELINE-DYN

current graph

is shown in Appendix A. Note that the

I

DD_BASELINE_DYN

I

DD-INHIGH

dynamic activity level vs. core

current is derived using the

frequency. Each curve in the graph represents a

baseline I

dynamic current for a specified

DDINT

power supply setting. Using the curve specific to

the application, the baseline dynamic current

(I

DD_BASELINE_DYN

) for the V

power supply

DDINT

example, with the core operating at 1.2 V

(V

) and a frequency of 333 MHz, the

DDINT

corresponding baseline dynamic current

(I

DD_BASELINE_DYN

) for the V

power supply

DDINT

domain would be approximately 0.76 A.

IDD Dynamic Current Running Your Application

Table 2 lists the scaling factor for each activity

level, used to estimate the dynamic current for

each specific application. With knowledge of the

program flow and an estimate of the percentage

of time spent at each activity level, the system

developer can use the baseline dynamic current

(I

DD_BASELINE_DYN

) shown in Figure 4 and the

corresponding activity scaling factor from

Table 2 to determine the dynamic portion of the

internal current (I

) for each ADSP-21368

DD-DYN

processor in a system.

domain can be estimated at the operating

frequency of the processor in the application. For

1

tCK = CLKIN; Core clock ratio 16:1

2

DMx64 accesses

3

DMx64, PMx64 accesses

Estimating Power Dissipation for ADSP-21368 SHARC® Processors (EE-299) Page 3 of 12

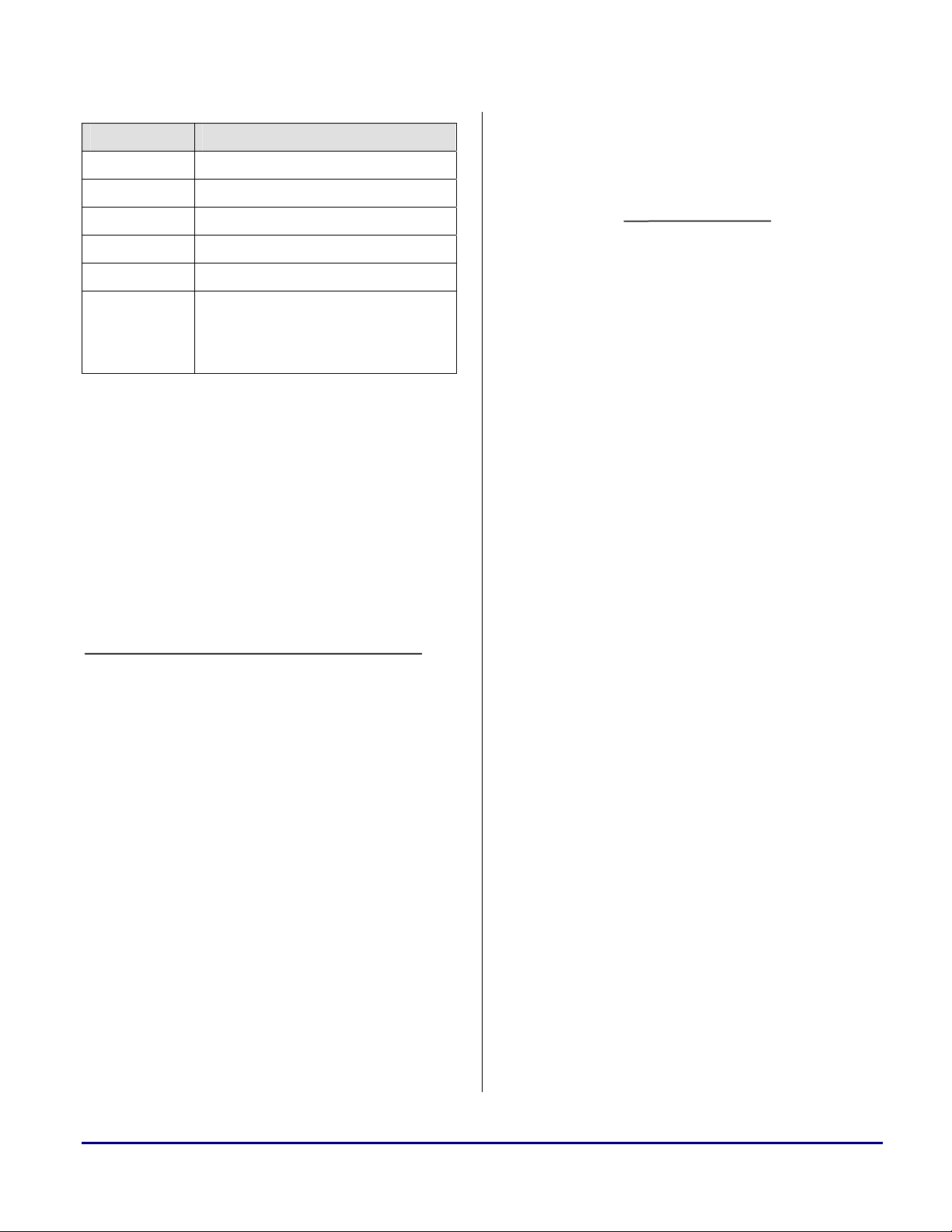

Power Vector Activity Scaling Factor (ASF)

I

0.21

DD-IDLE

I

DD-INLOW

I

DD-INMED

I

DD-INHIGH

I

DD-INPEAK

I

DD-INPEAK-TYP

50 :: 50

60 :: 40

70 :: 30

Table 2. Internal power vectors and dynamic scaling

factors

0.40

0.85

1.00

1.13

0.65

0.71

0.75

The dynamic current consumption for an ADSP21368 processor in a specific application is

calculated according to the following formula,

where “%” is the percentage of the overall time

that the application spends in that state:

( % Peak activity level x I

( % High activity level x I

( % High activity level x I

( % Low activity level x I

+( % Idle activity level x I

DD-INPEAK

DD-INHIGH

DD-INMED

DD-INLOW

DD-IDLE

= Total Dynamic Current for V

Equation 1. Internal dynamic current (I

ASF x I

ASF x I

ASF x I

ASF x I

ASF x I

DDINT (IDD-DYN)

DD_BASELINE_DYN

DD_BASELINE_DYN

DD_BASELINE_DYN

DD_BASELINE_DYN

DD_BASELINE_DYN

DD-DYN

)

)

)

)

)

)

For example, after profiling the application code

for a particular system, activity is determined to

be proportioned as follows.

(10% x 1.13 x 0.76)

(30% x 1.00 x 0.76)

(50% x 0.85 x 0.76)

(10% x 0.40 x 0.76)

+ (0% x 0.21 x 0.76)

= 0.67A

I

DD-DYN

Figure 2. Internal dynamic current estimation

a

Therefore, the total estimated dynamic current on

the V

power supply in this example is

DDINT

0.67 A.

Estimating I

The ADSP-21368 I

Static Current, I

DDINT

DD-STATIC

DD-STATIC

current graphs for

the MQFP and LQFP 266 MHz and 333 MHz

processor speed grade models are shown in

Appendix B, and the Super BGA 333 MHz and

400 MHz processor speed grade models are

shown in Appendix C. The static current on the

V

power supply domain is a function of

DDINT

temperature and voltage but is not a function of

frequency or activity level. Therefore, unlike the

dynamic portion of the internal current, the static

current does not need to be calculated for each

discrete activity level or power vector. Using the

static current curve corresponding to the

application (i.e., at the specific V

baseline static current (I

DD-STATIC

estimated vs. junction temperature (T

DDINT

) can be

) of the for

J

estimating TJ).

), the

(10% Peak Activity Level)

(30% High Activity Level)

(50% Med. Activity Level)

(10% Low Activity Level)

(0% Idle Activity Level)

Figure 1. Internal system activity levels

Using the activity scaling factor (ASF) provided

for each activity level in Table 2 (and the core

operating at 1.2 V (V

) and 333 MHz), a

DDINT

value for the dynamic portion of the internal

current consumption of a single processor can be

estimated as follows.

Estimating Power Dissipation for ADSP-21368 SHARC® Processors (EE-299) Page 4 of 12

For example, in an application with the core

operating at 1.2V (V

processor at a junction temperature (T

) and the ADSP-21368

DDINT

) of

J

+100oC, the corresponding baseline static current

(I

DD-STATIC

) for the V

power supply domain

DDINT

would be approximately 0.56 A.

The ADSP-21368 static power is constant for a

given voltage and temperature. Therefore, it is

simply added to the total estimated dynamic

current when calculating the total power

consumption due to the internal circuitry of the

ADSP-21368 processor. Note that the I

DD-STATIC

current shown in Figure 5 represents the worst-

Loading...

Loading...