Page 1

Engineer To Engineer Note EE-187

Technical Notes on using Analog Devices' DSP components and development tools

a

Using the PCI Interface On The ADSP-BF535 Blackfin® Processor in Host

Mode

Contributed by Jorge Manguane April 17, 2003

Contact our technical support by phone: (800) ANALOG-D or e-mail: dsp.support@analog.com

Or vi sit ou r on-l ine re sourc es ht tp:// www.analog.com/dsp and http://www.analog.com/dsp/EZAnswer

s

Introduction

Configuration entails allocating resources

(memory ranges, interrupt lines) to the various

The purpose of this document is to familiarize

the user with the workings of the PCI interface

on the ADSP-BF535 Blackfin® Processor.

The ADSP-BF535 Processor includes a Revision

2.2, 3.3V-compliant, 33 MHz/32-bit Peripheral

Component Interconnect (PCI) bus interface.

The interface can act as either a Host or a

Device. In Host mode, an external arbiter is

devices. Once configured, devices will respond

to transactions that fall within their allocated

memory ranges.

Note: PCI bus arbitration is not built into the

ADSP-BF535 PCI peripheral. An external PCI

bus arbiter is required (See Momentum Data

Systems Eagle-35 User Manual, Appendix B for

example PLD equations).

required. The ADSP-BF535 Processor can

master the PCI bus in both Host and Device

modes. In addition, a dedicated bus is available

on chip to allow an external bus master to

transfer data directly to internal (L2 memory) or

external memory spaces of the ADSP-BF535.

This document describes how to program the PCI

interface to function in Host mode.

Configuration Accesses

Before it can configure other devices, the PCI

core must initialize its PCI space registers

appropriately for host operation. At a minimum,

it must do the following:

1. Set bit 0 of the PCI Control Register

(PCI_CTL) register to enable host mode

Host mode

In host mode, the ADSP-BF535 PCI peripheral

acts as a system controller of the PCI bus and, as

such, it is responsible for configuring PCI

devices attached to the bus as well as arbitrating

mastership of the bus. Most PCI agents (host

2. Write to the PCI Configuration Command

Register (PCI_CFG_CMD) to enable

response to memory accesses, bus mastership

3. Write to the PCI Host Memory Control

Register(PCI_HMCTL) to tell PCI agents

what ADSP-BF535 resources can be accessed

and/or devices) can master the PCI bus; a device

can initiate a PCI transaction in the same way

that a host can, which allows for peer to peer

communications between different PCI agents.

Essentially, what differentiates a device from a

4. Set bit 1 of the PCI_CTL register to enable

PCI

To perform configuration accesses, the ADSPBF535 PCI interface uses two resources:

host in a system is who performs the

configuration of the various PCI agents.

Copyright 2003, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of

customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property

of their respective holders. Information furnished by Analog Devices Applications and Development Tools Engineers is believed to be accurate and reliable, however

no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices’ Engineer-to-Engineer Notes.

Page 2

a

0

0

1. Configuration Base Address Pointer

Register (PCI_CBAP ) is used to address the

configuration space of the devices. The

structure of the contents of this register

depends on whether a Type 0 or Type 1

configuration access is being performed. If

the device to be configured sits behind a

PCI-to-PCI Bridge, Type 1 configuration

accesses will be performed, otherwise, Type

0 accesses will be performed.

2. Configuration Data Port is a memory

location (0xEEFF FFFC) that holds the data

to be written to devices or returns data read

from devices during configuration accesses.

When performing configuration cycles, the Host

accesses a register set predefined by the PCI

specification. The specification currently defines

three Header formats:

Header Type Two: defined for PCI-to-

CardBus bridges

Header Type One: defined for PCI-to-PCI

bridges

Header Type Zero: defined for all other

devices.

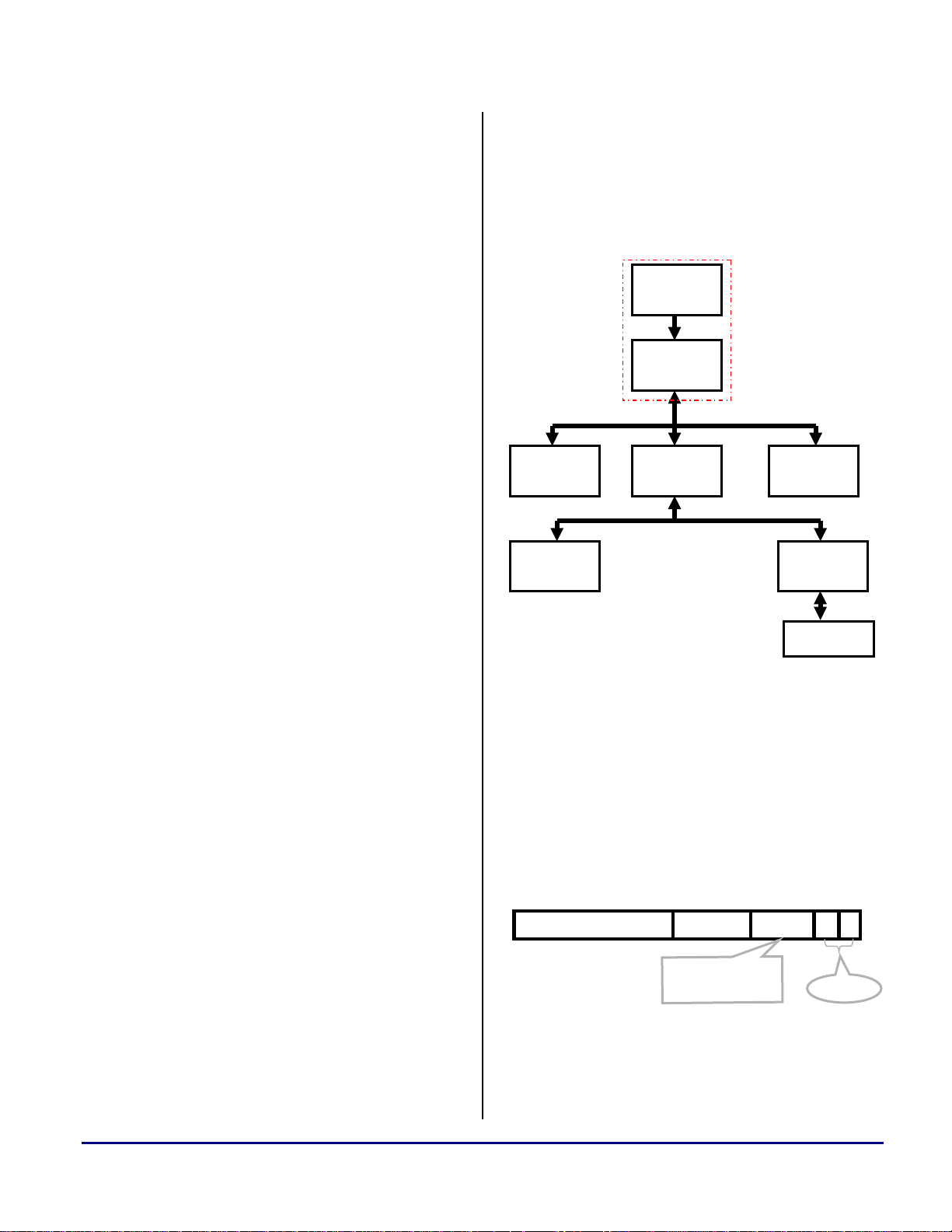

bridges themselves may be on the same

“primary” bus.

Alternatively, the primary bus of the second

bridge may be the secondary bus of the first

bridge, as shown in the figure below.

ADSP-

BF535DSP

CORE

Host-to-PCI

Bridge

PCI Bus 0

PCI Device

PCI-to-PCI

Bridge

PCI Device

PCI Bus 1

PCI-to-PCI

PCI Device

Bridge

PCI Bus 2

PCI Device

Figure 1

The host must traverse some or all of the

registers defined in the headers above. In this

application note, we’ll only touch on the last two

header types (header type 0, and header type 1)

since we are only concerned with configuring

PCI devices that sit directly on the PCI bus

(primary bus: Type 0 configuration) or devices

that sit behind a PCI-to-PCI bridge (secondary

bus: Type 1 configuration). Note when more

than one PCI-to-PCI bridge is present on the

system, the “secondary” bus can be anywhere

from bus #1 to bus #255 in the bus hierarchy.

Each PCI-to-PCI bridge adds a bus number to the

system. For example, if there’s only one bridge,

devices on the other side of the bridge will reside

on secondary bus #1, if there are two bridges,

devices on the other side of the second bridge

will reside on secondary bus #2, and so on. The

Using the PCI Interface On The ADSP-BF535 Blackfin

Type 0 Configuration Accesses

These accesses are directed to all PCI agents that

reside on the primary bus, including devices and

PCI-to-PCI bridges. The format of the data must

be programmed into the PCI_CBAP register

(Configuration Base Address Pointer register) as

shown below.

31 11 10 8 7 2 1 0

Function

RESERVED

Figure 2

rom the above figure,

F

Number

Target configuration

doubleword number

AD[1:0] = 00 to indicate a type zero access

indicate the target word to be accessed AD[7:2]

® Processor in Host Mode (EE-187) Page 2 of 6

DoubleWord

Number

Type 0

access

Page 3

AD[10:8] indicate the function number to be

accessed within the targeted device.

AD[31:11] are reserved and can be used to

implement IDSELs. IDSEL lines are used to

select each of the various devices that may reside

on the bus for configuration acce

sses. As an

example, IDSEL of device 0 may be connected

to AD11, IDSEL of device 1 may be connected

to AD12, and so on. IDSELs are only

meaningful during configuration. After

configuration, during normal operation, devices

decode and respond to PCI transactions that fall

within their memory and I/O ranges as

determined by what’s in their respective Base

Address Registers (BARs). In the case of the

ADSP-BF535, these are PCI_CFG_MBAR and

PCI_CFG_IBAR for memory and I/O

respectively.

Here’s an example that shows how to retrieve the

device’s Device and Vendor ID information:

P5.H = (PCI_CBAP >> 16);

P5.L = (PCI_CBAP & 0xFFFF);

R0.H = PCI_SLOT ; R0.L=FUNCTION_NUMBER| 0x00;

[P5] = r0; //load in PCI_CBAP the address of the 1

//the configuration

ssync;

P3.H = (PCI_CONFIG_SPACE_PORT >> 16);

P3.L = (PCI_CONFIG_SPACE_PORT & 0xFFFF);

R0 = [P3]; // read Vendor ID and Device ID (1

ssync;

space

st

st

Dword)

Dwo

rd of

a

R0.H = PCI_SLOT;

R0.L = FUNCTION_NUMBER| 0x10;

[P5] = r0; // access BA

ssync;

r4 = 0xFFFFFFFF;

[P3] = R4; //write all F’s to the Memory BAR register

SSYNC;

[P5] = r0;

SSYNC;

R4 = [P3]; // read back the unmasked (enabled) bits

ssync;

R4 = ~R4; // memory size requested by device [in bytes]

Now that we know the memory size this device

requires, we can assign it its base address in the

PCI Memory Space.

P0.H = PCI_Memory_Window >> 16;

P0.L = PCI_Memory_Window & 0xFFFF;

[P3] = P0; // assign Device the base of PCI MEM space

ssync;

In this case, the label PCI_Memory_Window

corresponds to address 0xE000 0000, the base

address of the PCI Memory Space. As can be

seen from the PCI Memory Map in Figure 3, the

PCI Memory Space is 128 Mbytes, and it can be

partitioned among the various devices on the bus

so that each device has its own unique PCI

memory region.

R0 – Memory BAR in the BF535

To access the next word (32 bits), increment the

address in PCI_CBAP by 4 bytes.

To find out how much memory and/or I/O a

particular device requires, the host writes

0xFFFFFFFF to the device’s BARx register and

then reads this register back. Only

the bits that

the device unmasked will be written to. All

others will return a value of zero when read back.

The one’s complement of the result read back

will give the size in bytes of the given resource

(memory or I/O).

Using the PCI Interface On The ADSP-BF535 Blackfin® Processor in Host Mode (EE-187) Page 3 of 6

Page 4

PCI Mem y Map:

0xEEFF FFFF

0xEEFF FFFC

0xEEFF FF00

0xEEFE F

0xEEFE 0000

0xE7FF FFFF

0xE000 0000

Figure 3

FFF

PCI Config Space Port (4 bytes)

PCI Config Registers ( 64 KB)

RESERVED

PCI IO SPACE (64KB)

RESERVED

PCI Memory Space

For the next device, we will have to assign it a

memory base address offset by the memory size

memory base address offset by the memory size

requested by the first device, and so on.

requested by the first device, and so on.

Type 1 Configuration accesses

Type 1 Configuration accesses

If a device resides on a secondary bus (for

If a device resides on a secondary bus (for

example, behind a PCI-to-PCI bridge) Type 1

example, behind a PCI-to-PCI bridge) Type 1

equired to configure the device.

accesses will be r

accesses will be r

In general, when a Type 1 transaction is seen on

In general, when a Type 1 transaction is seen on

the bus, only PCI-to-PCI bridges claim the

the bus, only PCI-to-PCI bridges claim the

transaction, which then convert it to a Type 0

transaction, which then convert it to a Type 0

transaction and pass it on to devices that reside

transaction and pass it on to devices that reside

on their secondary buses. It is, of course,

on their secondary buses. It is, of course,

understood that only one bridge will claim a

understood that only one bridge will claim a

transaction at a given time, depending on

transaction at a given time, depending on

whether the targeted device resides on its

whether the targeted device resides on its

secondary bus (i.e., there is a Bus Number

secondary bus (i.e., there is a Bus Number

match). Before we get into more detail, let’s

match). Before we get into more detail, let’s

review the data format of a Type 1 address:

review the data format of a Type 1 address:

equired to configure the device.

or

(128 MB)

will have to assign it a

a

31 23 15 10 7 1 0

reserved

Figure 4

Figure 4

Lets focus on the case where the Bus Number

Lets focus on the case where the Bus Number

does not correspond to the bridge’s secondary

does not correspond to the bridge’s secondary

b t is between the secondary bus

b t is between the secondary bus

us number buus number bu

number and the su r (the

number and the su r (the

very last bus number on the system). In this case,

very last bus number on the system). In this case,

the bridge still claims the transaction and passes

the bridge still claims the transaction and passes

it on as a Type 1 transaction to be claimed by

it on as a Type 1 transaction to be claimed by

other bridges.

other bridges.

Before the devices behind a bridge are

Before the devices behind a bridge are

configured, the bridg nfigured

configured, the bridg nfigured

with the Primary, Secondary and Subordinate bus

with the Primary, Secondary and Subordinate bus

n ation, as well with the base

n ation, as well with the base

umber informumber inform

address and ranges of the memory and I/O

address and ranges of the memory and I/O

spaces. spaces.

Type 0 accesses.

Type 0 accesses.

As an example of how to configure a bridge,

As an example of how to configure a bridge,

refer to Intel Corp’s 21152 PCI-to-PCI

refer to Intel Corp’s 21152 PCI-to-PCI

Configuration Application Note (

Configuration Application Note (

278068-001). 278068-001).

Having crossed this bridge (configuring the PCI-

Having crossed this bridge (configuring the PCIto-PCI bridge), devices can be configured in

to-PCI bridge), devices can be configured in

much the same way as that discussed for Type 0

much the same way as that discussed for Type 0

transactions, except that now the programmer

transactions, except that now the programmer

must include the Bus Number and Device

must include the Bus Number and Device

Number, as well as add a 1 to bit 0 of the address

Number, as well as add a 1 to bit 0 of the address

presented on the bus.

presented on the bus.

// Device ID | Vendor ID

// Device ID | Vendor ID

R0.H = BUS_NUMBER;

R0.H = BUS_NUMBER;

R0.L = DEVICE_NUMBER | FUNCTION_NUMBER| 0x01;

R0.L = DEVICE_NUMBER | FUNCTION_NUMBER| 0x01;

[P5] = r0;

[P5] = r0;

ssync;

ssync;

P3.H = (PCI_CONFIG_SPACE_PORT >> 16);

P3.H = (PCI_CONFIG_SPACE_PORT >> 16);

P3.L = (PCI_CONFIG_SPACE_PORT & 0xFFFF);

P3.L = (PCI_CONFIG_SPACE_PORT & 0xFFFF);

R0 = [P3];

R0 = [P3];

ssync;

ssync;

Bus

Number

Bridges themselves are configured using

Bridges themselves are configured using

Device

Number

Function

Number

bordinate bus numbebordinate bus numbe

e itself must be coe itself must be co

rd

doubleWo

Number

Order Number:

Order Number:

0 1

Type 1

Bridge

Bridge

Using the PCI Interface On The ADSP-BF535 Blackfin® Processor in Host Mode (EE-187) Page 4 of 6

Page 5

a

Now that the devices are configured, the host can

access the devices by initiating transactions in

the PCI memory or I/O regions that correspond

to those regions that were assigned to the

devices’ BARs. To that end, the host use I

Outboun

d Memory Base Address Register

s PC

(PCI_MBAP) for memory accesses and the PCI

Outbound I/0 Base Address Register (PCI_IBAP)

for I/O accesses.

Memory Accesses

To initiate a memory access, the host writes to

the PCI_MBAP register the uppermost 5 bits

(31:27) of th

These 5 bits will be prefixed to the 27-bit offset

of the actual address in the PCI memory space.

Example:

P4.H = (PCI_MBAP >> 16);

P4.L = (PCI_MBAP & 0xFFFF);

R0.H = 0xE000;

R0.L = 0x0000;

[P4] = R0;

ssync;

Now an access in the PCI memory space will

initiate a PCI transaction:

P2.H = 0xEF00;

P2.L = 0x1234;

R0 = [P2];

ssync;

The upper 5 bits of the

The lower 27 bits of the address in P2 are:

111 0000 0000 0001 0010 0011 0100

The actua

will be

:

1110 0111 0000 0000 0001 0010 0011

which corresponds to: 0xE700 1234

This is not the intended address. To access

0xEF0

0 0000, PCI_MBAP should have been

e intended destination address.

PCI_MBAP are: 11100

l address that will be output on the bus

0100

programmed with 0xE800 0000, which would

produce the following upper 5 bits:

11101

Prefixing the above upper 5 bits to the lower 27

bits of the address in P2 would produce:

1110 1111 0000 0000 0001 0010 0011 0100

the intended 0xEF

00 1234 address.

This address may correspond to different

addresses within different

devices. Each device

has its own internal memory/(I/O) space

mapping to the PCI space. As an example, the

ADSP-BF535 acting as a device uses the Target

Inbound Memory Base Address Register

(PCI_TMBAP) to map the P CI memory spa ce to

its internal/external memory space.

If PCI_TM

address would corres

which falls within Rese

Note that the

BAP = 0xF000 0000, the above

pond to 0xFF00 1234,

rved memory space.

above example is for illustration

purposes only.

I/O ACCESSES

The mechanism to perform I/O accesses is

similar to that described

except that now PCI_IBAP register is used. This

register prefix

will go on the

OUND TRANSACTIONS

INB

es 16 bits to the actual address that

bus.

We just described transactions that are initiate

by the host. As stated earlier, any PCI age

the bus can be the bus master and the h

the target, making it a slave for that

transaction. In this case, the particular

transacti

on is referred to as an inbound

transaction.

To participate in inbound transa

ADSP-BF535 as a host needs to enable accesses

to its various resources, i.e., L2 memory, system

MMR space, SDRAM space, and Asynchronous

Memory space.

for memory accesses

d

nt on

ost can be

particular

ctions, the

Using the PCI Interface On The ADSP-BF535 Blackfin® Processor in Host Mode (EE-187) Page 5 of 6

Page 6

a

Note, however, that in host mode the

ADSP-BF535 PCI core interface does

espond to I/O accesses, it only

not r

s memory transactions.

claim

Therefore, the host’s MMR space

should be accessed as a

prefetchable memory region. Wh

PCI-to-PCI bridges are used, be sure

to program their Non-P

Memory Base and Limit registers with

a base address that corresponds to the

ADSP-BF535’s system MMR space.

non-

en

refetchable

References

ADSP-BF535 Blackfin Processor Hardware Refere

PCI SYSTEM A

RCHITECTURE, 4

th

Edition, MindShare

To enable the various resources, the host uses the

PCI Host Memory Control Register

(PCI_HMCTL). Refer to the ADSP-BF535

Blackfin Processor Hardware Reference Manual

for bit definition

HMCTL:

P4.H = PCI_HMCTL >> 16; P4.L = PCI_HMCTL & 0XFFFF;

R0.H = 0X0

[P4] = R0;

SSYNC;

Now, the

the host’

spaces as

nce , Rev. 1.0, November 2002, Analog Devices, Inc.

, Inc.

; R0.L = 0X3;

// allow access to L2 and system MMR spaces

host can claim transactions that have

s L2 memory and/or System MMR

the target addresses.

s.

21152 PCI-to-PCI Bridge Configuration Application No

Document History

Version Description

April 17, 2003 by J. Manguane Initial Release

te, INTEL

Using the PCI Interface On The ADSP-BF535 Blackfin® Processor in Host Mode (EE-187) Page 6 of 6

Loading...

Loading...