Page 1

Engineer-to-Engineer Note EE-179

Technical notes on using Analog Devices DSPs, processors and development tools

a

Contact our technical support at dsp.support@analog.com and at dsptools.support@analog.com

Or vi sit our o n-li ne r esou rces htt p:/ /www.analog.com/ee-notes and http://www.analog.com/processors

ADSP-TS20xS TigerSHARC® System Design Guidelines

Contributed by Greg F., John A., & Phil G. Rev 4 – January 15, 2005

Introduction

This EE-Note discusses specific hardware issues when

implementing a system design, which incorporates any of

the ADSP-TS20xS TigerSHARC® processors. This

document is provided as an aid to hardware engineers for

designing systems using processors with silicon revisions

of 1.0 and higher.

All of the guidelines provided in this EE-Note apply to

ADSP-TS201S, ADSP-TS202S, and ADSP-TS203S

TigerSHARC embedded processors.

Power Supplies

The ADSP-TS20xS processor has four power supply

domains V

(External I/O) and a V

(Internal), V

DD

DD_DRAM

supply is a filtered version of the V

Refer to the ADSP-TS20xS TigerSHARC Embedded

Processor Data Sheet [1] for more specific details.

• V

Power Supply

DD

The V

power supply pins are used to power all

DD

internal logic except for the internal DRAM, I/O’s and

PLL.

(Analog PLL), V

DD_A

(DRAM) domain. The V

supply.

DD

DD_IO

DD_A

• V

DD_DRAM

The V

internal embedded DRAM logic.

Ground (VSS) Supply

The ADSP-TS20xS processor contains a single ground

supply V

V

, V

DD_A

Power Supply Current

The VDD, V

can be calculated with the formulas specified in the

application note Estimating Power For The ADSP-TS201S

(EE-170) [5].

Power Supply Sequencing

There are no power sequencing requirements other than

the V

DD_DRAM

ADSP-TS201S TigerSHARC Embedded Processor Data

Sheet [1] for more information.

Supply Bypass Capacitors

Power Supply

DD_DRAM

. The V

SS

DD_DRAM

DD_A, VDD_DRAM

power supply pins provide power to the

pins are ground returns for the VDD,

SS

and V

supply pins.

DD_IO

and V

power supply currents

DD_IO

voltage must occur last. Refer to the

• V

Power Supply

DD_A

The two V

power supply pins are used to directly

DD_A

power the PLL. These pins are isolated from the

internal V

supply pins so additional decoupling and

DD

filtering circuits can be added to reduce noise.

For multiprocessor designs ADI recommends keeping

the V

to the V

supplies separate for each processor. Refer

DD_A

supply decoupling section for further

DD_A

details.

• V

Power Supply

DD_IO

The V

DD_IO

power supply pins provide power to all the

I/O’s including all the link port LVDS pins.

The ADSP-TS20xS processor requires bypass capacitors

on each supply. In many cases it is difficult to place lots of

supply bypass capacitors close to the package pins,

especially on the bottom side of the PCB. ADI

recommends that PCB designers prioritize decoupling

capacitor placement in the following order:

1. V

2. V

3. V

4. V

to VSS bypass capacitors

DD_A

to V

DD

DD_DRAM

DD_IO

bypass capacitors

SS

to V

bypass capacitors

SS

to V

bypass capacitors

SS

Low-ESR/low-ESL 0.1 µF capacitors are recommended

for proper bypassing. For higher-frequency filtering,

0.01 µF and 0.001 µF capacitors can also be used (in

Copyright 2005, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of

customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property

of their respective holders. Information furnished by Analog Devices Applications and Development Tools Engineers is believed to be accurate and reliable, however

no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices’ Engineer-to-Engineer Notes.

Page 2

addition to the 0.1 µF capacitors), provided their

inductance is small enough. In some cases, performing

SPICE analyses of the power supply filtering

characteristics may be necessary.

Enough “bulk” capacitors must be used to prevent power

supply ripple that exceeds max/min power supply

tolerances (refer to the data sheet for the appropriate

supply tolerances) caused by current transients in the

system. Several parallel electrolytic and/or tantalum

capacitors are preferred in order to minimize ESR and to

provide sufficient capacitance.

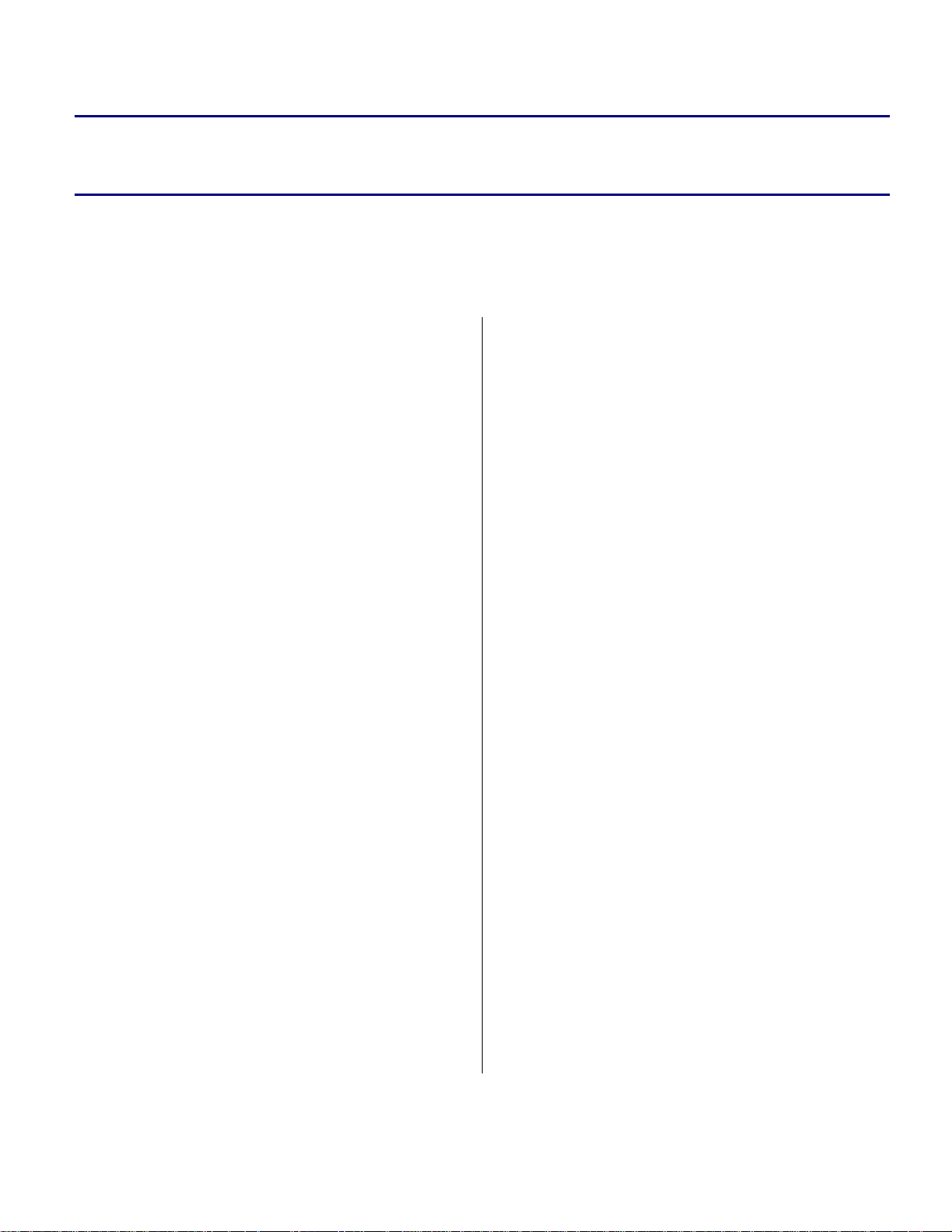

V

The two analog (V

generator PLLs. To produce a good stable clock, systems

must provide a “clean” power supply to the V

Therefore, the system designer must pay critical attention

to bypassing and filtering of the V

decoupling capacitor placement for V

first priority over the other supplies. Figure-1 shows the

recommended design of the V

components used in this circuit should be placed as close

as possible to the V

stray capacitance.

V

V

It is recommended that the V

duplicated for each processor in multiprocessor systems.

V

Below are the minimal recommended bypass capacitor

requirements for a single processor’s V

capacitors should be duplicated for each processor in the

system.

Supply Decoupling

DD_A

) supply pins power the clock

DD_A

domain.

DD_A

supply. The

DD_A

should be given

DD_A

filtering circuit. The

DD_A

pins to minimize inductance and

DD_A

DD

SS

10uH

1uF

Place as close to

pins as possible

TS20xS #1

V

1nF

HF

SMD

DD_A

V

DD_A

V

SS

Figure-1: V

10uH

V

DD

V

SS

Supply Decoupling

DD_A

DD_A

Place as close to

pins as possible

TS20xS #N

V

1nF

HF

1uF

V

SMD

V

decoupling circuit be

• Place 10 µH inductor and 1 µF capacitor together

with good connections to V

DD, VSS,

and V

DD_A

• Place one (minimum) or two 1 nF HF SMD

capacitors as close to the V

SS

and V

DD_A

package

pins as possible.

• Make sure that the V

PCB trace isn’t close to

DD_A

any noise-generating signals.

DD_DRAM

Supply Decoupling

DD_DRAM

supply. All

DD_A

DD_A

SS

.

a

1. Minimum of six 1 nF high frequency bypass

capacitors located as close to the package pins as

possible.

2. At least two 10 nF bypass capacitor located as

close to the package pins as possible.

3. At least four 0.1 µF bypass capacitors located as

close to the package pins as possible.

4. A minimum of 47 µF of “bulk” low ESR (less

then 100mΩ) capacitors for each processor

connected to the V

DD_DRAM

recommended. These capacitors are used to

reduce power supply ripple during high peak

transient currents.

• Single Electrolytic: Panasonic FK Series or

Sanyo OS-CON series

• Single tantalum: AVX TPS III series

• Multiple ganged MLC capacitors: AVX Y5V

series

V

Supply Decoupling

DD

High frequency noise on internal supplies can adversely

affect the speed of any device. It is always important to

provide robust supply bypassing for internal supplies

especially for products whose internal voltages are less

than 1.5 V. It is recommended that as many highfrequency capacitors as possible be connected to the V

supplies as close to the package pins as possible.

A minimum of 470 µF of “bulk” low ESR (less than 25

mΩ) capacitors for each processor connected to the V

supply is recommended. These capacitors are used to

reduce power supply ripple during high peak transient

currents.

1. Minimum of six 1 nF high frequency bypass

capacitors located as close to the package pins as

possible.

2. At least two 10 nF bypass capacitor located as

close to the package pins as possible.

3. At least four 0.1 µF bypass capacitors located as

close to the package pins as possible.

4. A minimum of 470 µF of “bulk” low ESR (less

than 25 mΩ) capacitors for each processor

connected to the V

supply is recommended.

DD

These capacitors are used to reduce power supply

ripple during high peak transient currents.

supply is

DD

DD

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 2 of 14

Page 3

• Single Electrolytic: Panasonic FK Series or

Sanyo OS-CON series

• Single tantalum: AVX TPS III series

• Multiple ganged MLC capacitors: AVX Y5V

series

Proper VDD supply design is critical to ensure

L

operation within the data sheet specifications

under all operating conditions. Adhering to the

data sheet V

and IDD specifications will ensure

DD

that no run time system errors will occur due to

specification violations.

V

DD_IO

It is important to provide proper decoupling on the V

supply. Although not as important as the V

V

DD_DRAM

Supply Decoupling

DD_IO

, VDD, and

DD_A

supplies, careful capacitor placement and supply

ripple analysis is required to ensure adequate decoupling.

1. Minimum of six 1 nF high frequency bypass

capacitors located as close to the package pins as

possible.

2. At least two 10 nF bypass capacitor located as

close to the package pins as possible.

3. At least four 0.1 µF bypass capacitors located as

close to the package pins as possible.

4. A minimum of 100 µF of “bulk” low ESR (less

than 100 mΩ) capacitors for each processor

connected to the V

supply is recommended.

DD_IO

These capacitors are used to reduce power supply

ripple during high peak transient currents.

a

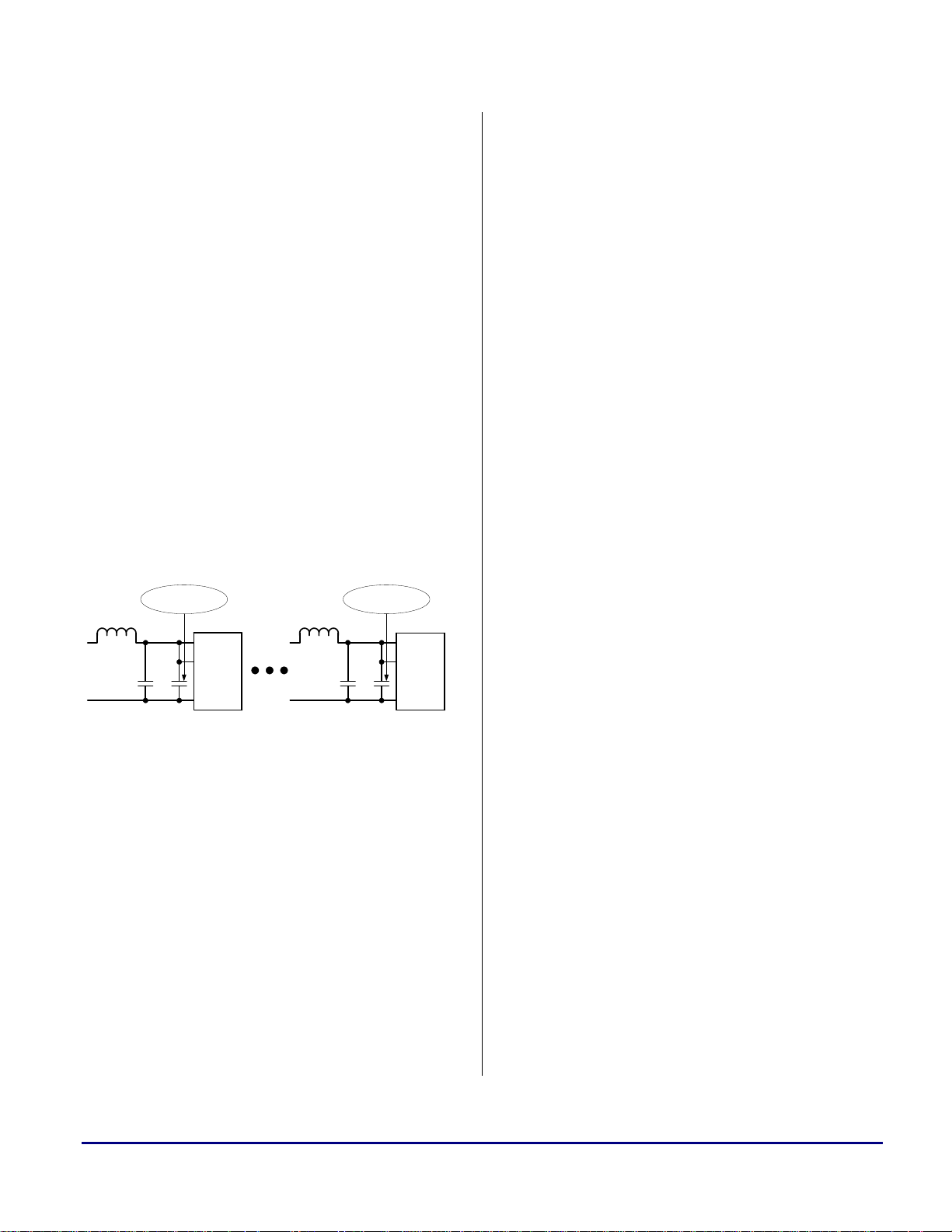

Figure-2: Recommended V

In multiprocessor (cluster bus) designs V

shared between all DSPs. It is important to make sure that

each processor has at least one (preferably more) 1 nF high

speed decoupling capacitor located close to the V

is also important to keep noise sources from coupling into

REF

signal.

REF

Pin

the V

SCLK_V

The ADSP-TS20xS contains a single SCLK_V

reference pin. This pin sets the input reference voltage for

the SCLK input pin.

The SCLK_V

voltage should be set to the value

REF

specified in the data sheet with the recommended circuit in

Figure-3. All resistor tolerances must be 1%. (For values

of R1 and R2, refer to Figure 7 of the ADSP-TS201S

TigerSHARC Embedded Processor Data Sheet [1].)

REF

circuit

REF

should be

pin. It

REF

voltage

REF

• Single Electrolytic: Panasonic FK Series or

Sanyo OS-CON series

• Single tantalum: AVX TPS III series

• Multiple MLC capacitors: AVX Y5V series

V

Pin

REF

The ADSP-TS20xS contains a single V

REF

voltage

reference pin. This pin sets the input reference voltage for

certain input pins. For the exact list of pins whose

threshold is set by V

refer to the ADSP-TS201S

REF

TigerSHARC Embedded Processor Data Sheet [1].

The V

voltage should be set to the value specified in the

REF

data sheet with recommended circuit in Figure-2 below.

Figure-3: Recommended SCLK_V

REF

In multiprocessor (cluster bus) designs, SCLK_V

should be shared between all DSPs. It is important to make

sure that each processor has at least one (preferably more)

1 nF high speed decoupling capacitor located close to the

SCLK_V

source from coupling into the SCLK_V

pin. It is also important to keep any noise

REF

REF

circuit

REF

signal.

All resistor tolerances must be 1%. (For values of R1 and

R2, refer to Figure 6 of the ADSP-TS201S TigerSHARC

Embedded Processor Data Sheet [1].)

No-Connect (NC) Pins

The ADSP-TS20xS contains several No-Connect (NC)

pins. These pins must not connect to any supply or ground

(V

DD

, V

, VDD_A, VDD_

DD_IO

, or VSS) and they must not

DRAM

connect to any other NC pin. All NC pins must be left

totally unconnected.

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 3 of 14

Page 4

Configuration Pins

The ADSP-TS20xS configuration pins SCLKRAT2-0,

ID2-0, CONTROLIMP1-0 and DS2-0 are used to select

various chip functions such as PLL clock ratio, chip-ID

and output impedance. These pins typically have either an

internal pull-up or pull-down resistor. All configuration

pins must have a constant value while the ADSP-TS20xS

is powered.

When using the default configuration, no external

connection is needed; the pin should be treated as a NC

(No Connect). For all other configurations (non default),

the pin must be connected to V

through a sufficiently strong resistor.

In multi-processor designs where configuration pins are

likely to be wired together (SCLKRAT2-0 connected to

several processor’s) make sure that a proper value of

resistor is used to override the default pull-down/up. Note

that the total resistor value is divided by the number of

processors.

For initial or prototype designs it is

L

• CONTROLIMP1-0 Configuration Pins

advantageous to have pads on the PCB for

populating strap resistors to change the default

setting for all the SCLKRAT2-0,

CONTROLIMP1-0 and DS2-0 pins.

Configuration pins, which have default pull-ups,

should have resistor pads between the pin and

and default pull-downs should have resistor

V

SS

pads between the pin and V

The CONTROLIMP0 pin has an internal pull-down

resistor and CONTROLIMP1 has an internal pull-up

resistor. These pins control output driver impedance.

Refer to Table 12 of the ADSP-TS201S TigerSHARC

Embedded Processor Data Sheet [1] for more

information on the CONTROLIMP1-0 pin values.

For all designs it is recommended to set the

L

CONTROLIMP1-0 pins to a value of “00”

(Normal), since this is the only mode

supported by IBIS model simulation.

DD_IO

DD_IO

or V

SS

.

directly or

a

• SCLKRAT2-0 Configuration Pins

The SCLKRAT2-0 pins contain an internal pull-down

resistor. These pins set the PLL multiplier, which

generates the core clock from the SCLK input.

For more information on the maximum SCLK duty

cycle specifications, and max/min SCLK frequency

specifications, refer to the ADSP-TS201S

TigerSHARC Embedded Processor Data Sheet [1].

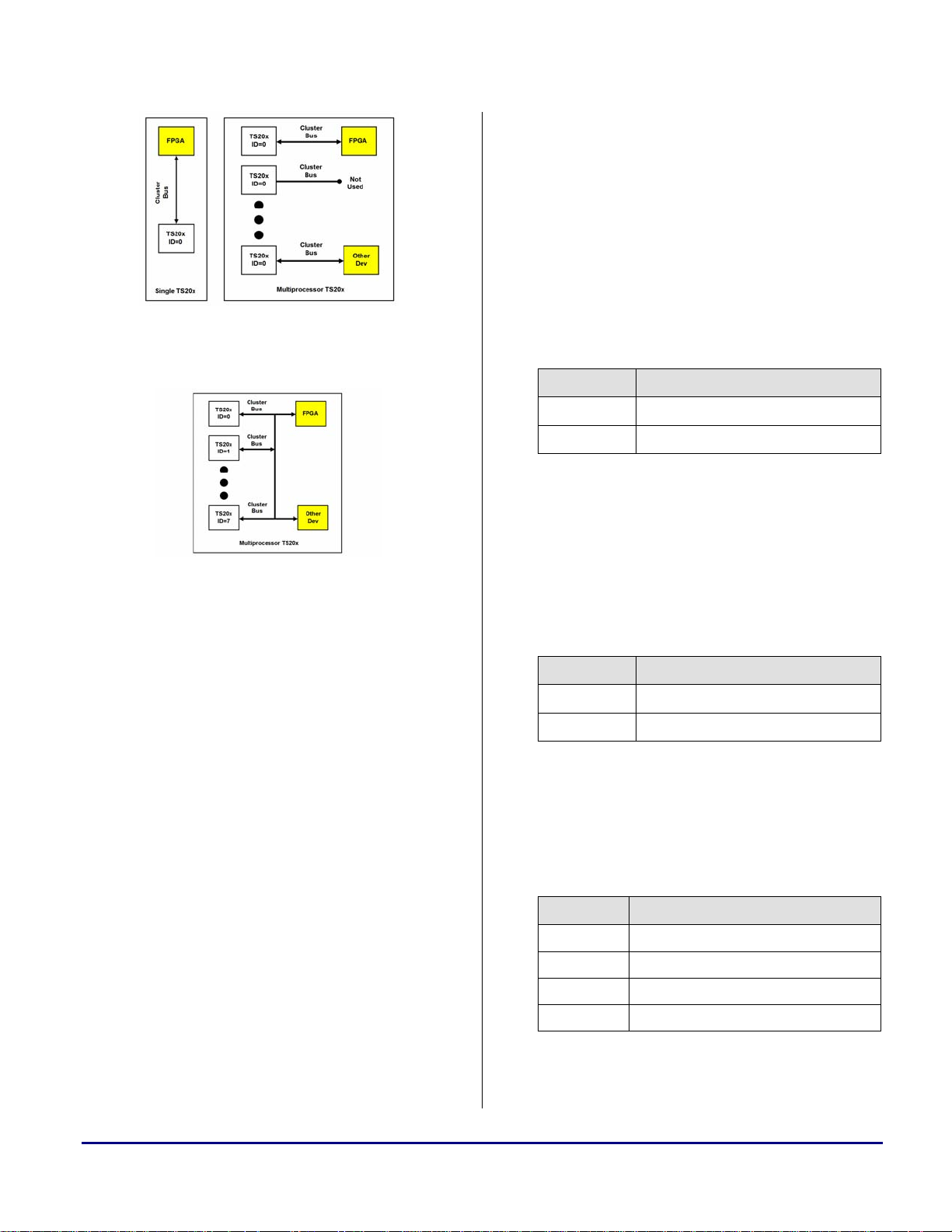

• ID2-0 Configuration Pins

The ID2-0 pins have an internal pull-down resistor. In

single processor systems and in multiprocessor

designs where the cluster bus is not connected to any

other TS20xS device, the ID pins should be set to the

default value (000). This is because internal pullup/pull-downs on certain pins, like memory interface

and bus arbitration are enabled only when the ID2-0 =

(000). Setting the processor ID2-0 pins to (000)

eliminates the need for external resistors. Refer to

ADSP-TS201S TigerSHARC Embedded Processor

Data Sheet [1] for more details.

Note that ID2-0=[000] is the only processor which can

enable SDRAM and start the MRS sequence.

In multiprocessor designs where the cluster bus is

shared between TS20xS devices, each processor must

be programmed to a unique device ID starting with

ID2-0 = (000) and incrementing upwards. The table

and figures below describe the various configurations

and ID2-0 assignments.

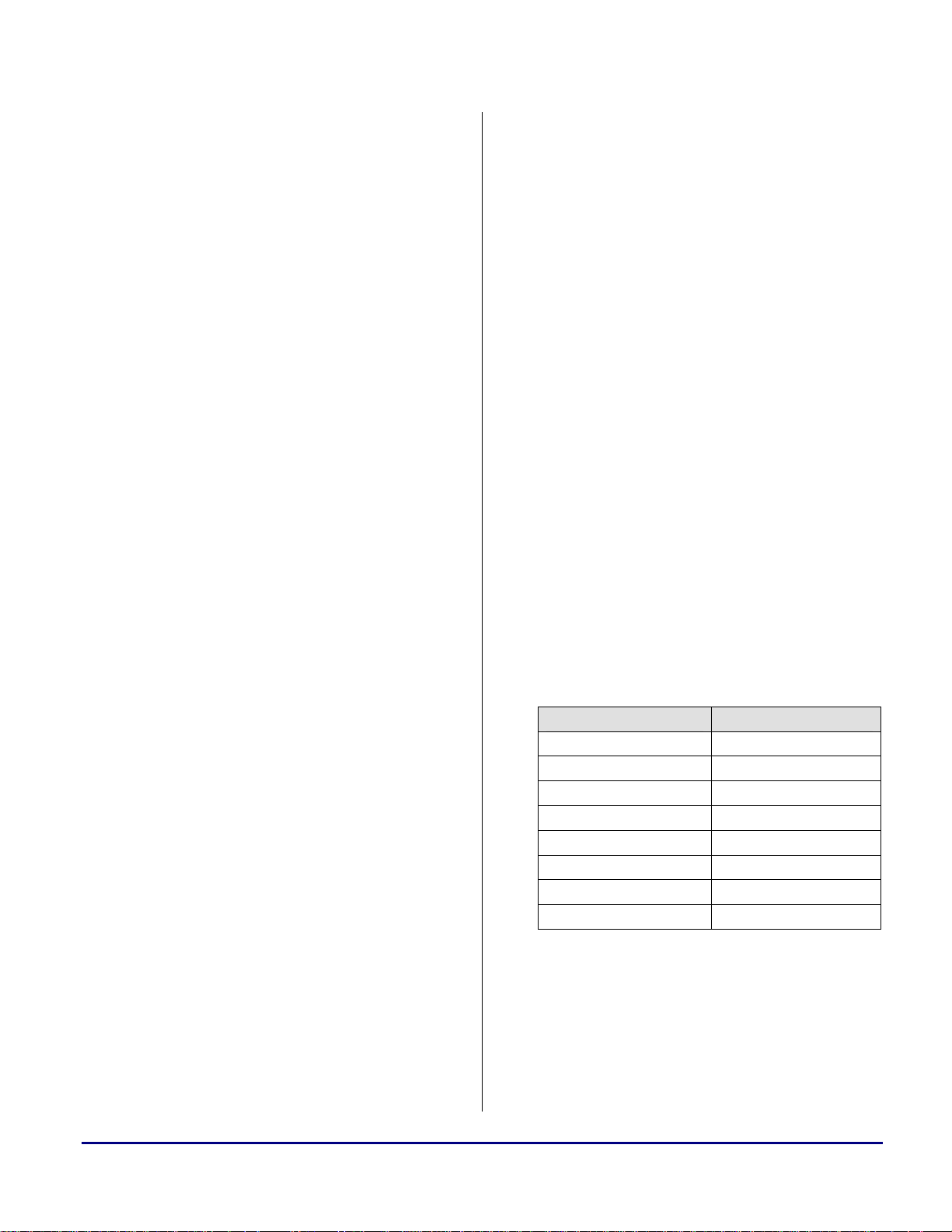

ID2-0 Multiprocessor ID

000 (default) 0

001 1

010 2

011 3

100 4

101 5

110 6

111 7

• DS2-0 Configuration Pins

The DS2 and DS0 pins contain an internal pull-up

resistor. DS1 contains an internal pull-down resistor.

These pins control the drive strength of the ADSPTS20xS output drivers. For further information refer

to the ADSP-TS201S TigerSHARC Embedded

Processor Data Sheet [1] and the application note

User Guide to ADSP-TS201S TigerSHARC processor

IBIS files (EE-198) [7].

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 4 of 14

Table-1: ID2-0 Configuration options

Page 5

a

• /BMS Strap Pin (EBOOT)

The /BMS strap pin sets EEPROM (default) or

External boot mode.

During reset, /RST_IN (low), a 5 kΩ pull-down

resistor is enabled on /BMS if the chip’s ID2-0 pins

are programmed to (000). All remaining DSPs ID2-0

programmed to (1 to 7), in the system, will not have

any pull-downs or pull-ups active on /BMS.

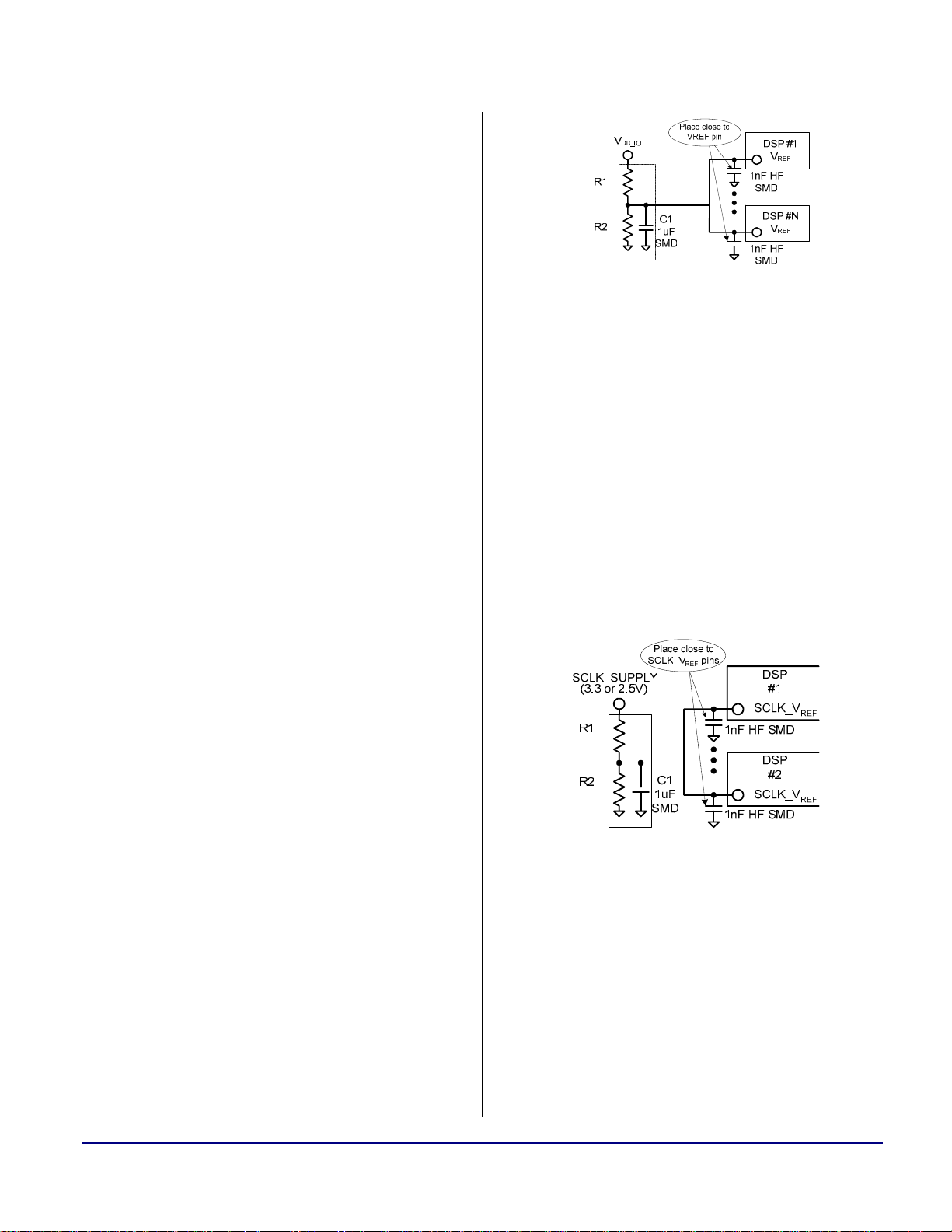

Figure-4: No cluster bus connection between TS20x

processors. (All processor ID’s must be 0)

Figure-5: Cluster bus connection between TS20x

processors. (All processor ID’s must be

unique)

Strap Pins: /BMS,/BM,TMR0E,/BUSLOCK

The ADSP-TS20xS processor contains four dual-purpose

strap pins /BMS, /BM, TMR0E and /BUSLOCK. These

strap pins select the boot-mode, SYSCON/SDRCON write

enable, link port width and interrupt (edge/level). These

strap pins also have additional functionality after reset.

When the default configuration is used, no external resistor

is needed. For all other configurations, a sufficiently strong

resistor (typically 500 Ω) connected to V

Do not strap these pins directly to any supply or any other

pin.

For designs which are driving strap pins directly from an

FPGA, ASIC or other device, refer to the data sheet for

timing details on when the strap pins are sampled and

when the FPGA, ASIC or device should stop driving strap

pin data value.

The four strap pins have an internal pull-down resistor,

pull-up resistor or no-resistor (three-state) on each pin. The

resistor type, which is connected to the I/O pad, depends

on whether /RST_IN is active (low) or if /RST_IN is deasserted (high). Refer to Table 17 (“Strap Pin Internal

Resistors”) of the ADSP-TS201S TigerSHARC Embedded

Processor Data Sheet [1] for more information.

is required.

DD_IO

To over-ride the default setting, place a sufficiently

strong resistor (typically 500 Ω) between /BMS and

.

V

DD_IO

/BMS Boot Mode

0 (default) EPROM Boot

1 External or Link port Boot

Table-2: /BMS strap options

• /BM Strap Pin (IRQEN)

The /BM strap pin sets Interrupt disable (default) or

Interrupt enable for /IRQ3-0. During reset, /RST_IN

(low), an internal pull-down resistor is enabled.

To override the default setting, place a sufficiently

strong resistor (typically 500 Ω) between /BM and

.

V

DD_IO

/BM Interrupt Enable, (IRQ3-0) Type

0 (default) Disable interrupts, level-sensitive

1 Enable interrupts, edge-sensitive

Table-3: /BM strap options

If the /BM and /BMS strap pins are high, at the deassertion of /RST_IN, the processor starts running

from the memory address selected by one of the

/IRQ3-0 signals (one /IRQ signals should be asserted).

The table below shows the starting memory address.

Interrupt Address

/IRQ0 0x3000 0000 (External Memory, /MS0)

/IRQ1 0x3800 0000 (External Memory, /MS1)

/IRQ2 0x8000 0000 (External Memory, /MSH)

/IRQ3 0x0000 0000 (Internal Memory)

Table-4: No Boot, Run From Memory Address

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 5 of 14

Page 6

• TMR0E Strap Pin (LINK_DWIDTH)

The TMR0E strap pin sets the Link Port Data Width,

1-bit (default) or 4-bit, for all Link Ports. During reset,

/RST_IN (low), an internal pull-down resistor is

enabled on the TMR0E pin.

To override the default setting, place a sufficiently

strong resistor (typically 500 Ω) between TMR0E and

.

V

DD_IO

TMR0E Link Port Input Data Width

0 (default) 1-Bit

1 4-bit

Table-5: TMR0E strap options

• /BUSLOCK Strap Pin (/SYS_REG_WE)

The /BUSLOCK strap pin sets the write enable to

always writable or one-time writable (default) for the

SYSCON and SDRCON registers.

During reset, /RST_IN (low), an internal pull-down

resistor is enabled on the /BUSLOCK pin if the chip’s

processor ID is programmed to “0”. All remaining

processor ID’s (1-7), in the system, will not have any

pull-downs or pull-ups active on /BUSLOCK.

To over-ride the default, place a sufficiently strong

resistor (typically 500 Ω) between /BUSLOCK and

.

V

DD_IO

/BUSLOCK SYSCON/SDRCON write enable

0 (default) One-time writable after reset

1 Always writable

Table-6: /BUSLOCK strap options

a

/RST_IN is asserted (low). If the FPGA or ASIC has a

pull-up this is ok.

Note, only link ports 1, 2, and 3 have special test mode

straps. If only one link port requires connection to an

FPGA or ASIC, use link port “0” since this Link Port

Block Completion signal doesn’t have any test mode straps

associated with it.

For designs which are driving Test Mode strap pins

directly from an FPGA, ASIC or other device, refer to the

data sheet for timing details on when the Test Mode strap

pins are sampled and when the FPGA, ASIC or device

should stop driving strap pin data value.

Note: If under any circumstances, at the rising edge of

reset (de-assertion edge), if any of the 3 test mode Block

Completion signals has a value other than a logic-1 a

processor test mode will be enabled.

To assist in debugging it is recommend that

L

Test Mode Description Strap Pin

TM1 /L1BCMPO

TM2 /L2BCMPO

TM3

• CCLK/4 on pin /L0BCMPO

• SOCCLK/2 on pin /L1BCMPO

• SCLK on pin /L2BCMPO

designers include an option for placing three

optional pull-down resistors (typically 500 Ω)

between the Test Mode Strap pins and V

also recommended that designers include an

option for placing three optional pull-up

resistors (typically 500 Ω) between the Test

Mode Strap pins and V

be added or removed to enable and disable each

specific test modes.

. These resistors can

DD_IO

. It is

SS

/L3BCMPO

Test Mode Strap Pins (Link Port)

There are three special test strap pins /L1BCMPO,

/L2BCMPO and /L3BCMPO, which enable test mode

functions. These pins are the Link Port 1, 2, and 3’s Block

Completion signals. They are normally outputs, however,

when /RST_IN is active (low) these pins are three-stated

and an internal pull-up resistor enabled.

All FPGAs and some ASICs three-state their pins before

they are programmed. During this time, some FPGAs

and/or ASICs typically turn on an internal pull-up or pulldown resistor. These resistors are used to keep signals

from floating to mid-scale before programming. It is

important to make sure that the FPGA or ASIC which

connects to Link Port 1, 2, or 3’s Block Completion pins

don’t have any internal pull-down resistor active while

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 6 of 14

Table-7: Link Port test mode strap options TS201/TS202

Test Mode Description Strap Pin

TM1 /L1BCMPO

TM2 TM2

TM3

• CCLK/4 on pin /L0BCMPO

• SOCCLK/2 on pin /L1BCMPO

• SCLK on pin TM2

Table-8: Link Port test mode strap options TS203

TM3

Page 7

SCLK Pin

After power-up the SCLK signal should not stop running

unless the reset signal (/RST_IN) is asserted. If SCLK

needs to stop following the power-up sequence, /RST_IN

must also get asserted. When re-starting the SCLK from

this condition, follow the same guidelines as the pow er-up

sequence.

SCLK Distribution

In single and multiprocessor designs careful clock design

and distribution is required to ensure proper and full-speed

internal and external operation.

Listed below are some guidelines for clock distribution.

• PCB connections should be point-to-point from the

clock buffer output to all clock inputs. Trace lengths

should be matched (+/- 125 mils) to minimize skew.

• Capacitance on all clock signals should be matched

within 5%.

a

Two or more

CLOCK

SOURCE

CLOCK BUFFERS

Figure-7: Not Recommended Clock Distribution Method

SCLK Design Considerations

Careful analysis is required when choosing components for

generating, buffering and distributing the SCLK signals on

a PCB. Refer to the ADSP-TS20xS data sheet specification

for SCLK input jitter requirements.

Single-stage or dual-stage clock tree designs are typically

used to create a clock distribution network. Figure-8 shows

a couple of examples of these types of designs.

Matched PCB Length

CLK#0

TigerSHARC ID=0

CLK#5

TigerSHARC ID=5

CLK#6

CLK#8

TigerSHARC ID=6

Other Devices

(Memory, Host)

CLUSTER BUS

• Minimize the number of PCB vias.

• Maintain same number of vias on each clock signal.

• Do not run clock signals close to other signals on

same layer. Keep at least 4x minimum spacing to other

signals.

• Do not run any signals directly above or below the

clock signals.

• Use a high quality low-jitter clock source for

generating the clock reference.

• Use a low-jitter clock buffer driver.

• Use a low output-to-output skew clock buffer driver.

• All clock signals from the clock buffer outputs to the

SCLK inputs should be carefully reviewed.

• A single, multiple-output clock buffer should be used

to drive the clock signals to all devices including

DSPs, FPGAs, ASICs and Memories. Using multiple

clock buffer chips increases the clock-to-clock skew

between clock signals and is not recommended.

CLOCK

SOURCE

Single

CLOCK BUFFER

Matched PCB Length

CLK#0

CLK#1

CLK#7

CLK#8

TigerSHARC ID=0

TigerSHARC ID=1

TigerSHARC ID=7

Other Devices

(Memory, Host)

CLUSTER BUS

Figure-6: Recommended Clock Distribution Method

Dual-Stage

CLK1

OSC BUF

CLKn

Single-Stage

CLKGEN

& BUF

CLK1

CLKn

Figure-8: Clock Generation Examples

In most instances single stage clock designs provide lower

jitter specifications and tighter duty-cycle control than dual

or multi-stage clock designs. It is very important to

simulate all designs, however dual and multi-stage designs

require special attention when analyzing total jitter (OSC

jitter & BUF jitter) and duty cycle impact. In some cases

jitter is additive, therefore a 100 ps OSC jitter + 150 ps

BUF jitter could result in a 250 ps total peak-to-peak jitter.

In some BUF products, however, some input jitter is

filtered out resulting in only a fraction of the input jitter

being added to the inherent BUF jitter. Designers should

review manufacturer data sheets and application notes

before choosing Oscillators, Crystals and clock driver

components to ensure they meet the jitter, rise/fall time,

and duty cycle requirements for the SCLK of the ADSPTS20xS.

L

It is important to ensure that the SCLK_V

reference voltage complies with the data sheet

specification. It is important to note that the duty

REF

cycle of SCLK is dependent upon the

SCLK_V

voltage setting.

REF

Other factors to consider: When selecting components, the

output-to-output skew between various clock buffer

outputs should be as small as possible to ensure high speed

operation of the external bus interface. Make sure the

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 7 of 14

Page 8

output rise and fall times of clock drivers are symmetrical.

Review power supply grid and supply decoupling for all

clock generation components. Signal integrity analysis

should be run on all clock signals to ensure no external

coupling and they meet or exceed the SCLK specifications.

Reset Pins

There are four external pins /RST_IN, /RST_OUT,

/POR_IN and /TRST associated with the reset circuitry of

the ADSP-TS20xS. Three of the pins /RST_IN,

/RST_OUT and /POR_IN are associated with resetting the

core and internal DRAM. These pins must be configured

as shown in Figure-11 below. The /TRST pin is the JTAG

and Emulator reset pin.

ADI recommends designers place a 0 Ω resistor

L

/RST_IN is the chip hardware reset pin, /RST_OUT is a

delayed and synchronized internal version of /RST_IN and

/POR_IN is used to reset the internal DRAM.

In multiprocessor designs, the /RST_IN signal must be

connected to all devices to provide a common reset

sequence. Each processor should connect its /RST_OUT

pin to its /POR_IN pin.

It is required that the circuit supplying /RST_IN should

hold the signal asserted (low) when the power supply is

ramping up to its stable value.

The TS20xS has four types of resets; Power-Up Reset,

Normal Reset, Core Reset and JTAG/Emulator Reset.

•

between /RST_OUT and /POR_IN. This

provides a useful place for connecting a trigger

to a logic-analyzer or oscilloscope for

debugging potential system problems.

RESET

CIRCUIT

“0” O hm

Figure-9: Hardware Reset Pin Connections

/RST_IN

/RST_OUT

/POR_IN

DSP #1

/RST_IN

/RST_OUT

/POR_IN

DSP #N

Power-Up Reset:

Refer to the “Power-Up Reset Timing” and “Normal

Reset Timing” sections of the ADSP-TS201S

TigerSHARC Embedded Processor Data Sheet [1] for

specific timing on the /RST_IN and SCLK pins.

All strap and test mode pins are sampled 14 SCLK

cycles after /RST_IN is de-asserted. Refer to the

ADSP-TS201S TigerSHARC Embedded Processor

a

Data Sheet [1] for exact timing when theses pins are

latched.

• Normal Reset

Normal Reset is defined as any chip reset (assertion of

/RST_IN) following the initial Power-Up Reset. The

supplies, SCLK and other signals must be stable.

• Core Reset:

When setting the SWRST bit in the register

EMUCTL, the processor core is reset, but not the

external ports or I/O. This is sometimes referred to as

a software reset.

• /TRST Boundary Scan and Emulator Reset:

The /TRST reset pin not only resets the IEEE 1149.1

Boundary Scan port but it also provides the reset

signal for the Emulator interface. This signal requires

special considerations if the Emulator or Boundary

Scan port is being used.

Refer to EE-68 “Analog Devices JTAG Emulation

Technical Reference” [4] for more information.

Boundary Scan and Emulator Pins

The ADSP-TS20xS has six pins associated with the

Boundary Scan and Emulator interface. The pins, /EMU,

TCK, TDI, TDO, TMS and /TRST should be connected to

a Boundary Scan pod connector if the ADSP-TS20xS

emulator is used. To get detailed and updated information

on this subject, please refer to engineering note Analog

Devices JTAG Emulation Technical Reference (EE-68) [4].

Cluster Bus Pins

In a single processor system, the ID2-0 pins of the single

processor must be set to “000”. In a multiprocessor system,

the processor IDs must be uniquely assigned starting from

“000” up to “111”; a single TigerSHARC cluster can

gluelessly support up to 8 DSPs. For both single and

multiple processor topologies, it is imperative to include

processor ID2-0 = “000” in the system, since this

processor supports the following features upon reset:

• Has active internal pull-ups or pull-downs on

certain external signals when ID2-0=”000”

(processor ID 0). See ADSP-TS201S TigerSHARC

Embedded Processor Data Sheet [1] for details.

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 8 of 14

Page 9

• Is the default bus master, and can therefore

provide active bus arbitration signals to an

external host processor.

• Has an on-chip SDRAM controller, which

provides an MRS sequence to any external

SDRAM present in the system.

If there is an external host on the cluster bus and common

data are shared between the host and the TigerSHARC

processor(s), the endianess on both sides must be matched

to each other. Note, the TigerSHARC processor is only

little endian and does not support big endian.

The TigerSHARC processor’s addressing is word-oriented

(32-bit). Some host processors’ addressing is byteoriented. Therefore, for connecting to these processors the

least-significant bit of the TigerSHARC processor’s

address bus should be connected to the third

least-significant bit of the host processor’s address bus,

regardless if a 32-bit or 64-bit bus width is specified.

The address and data busses may float for several cycles

during bus-mastership transitions between a TigerSHARC

processor and a host. Floating in this case means that these

inputs are not driven by any source. The ADSP-TS20xS

contains internal pull-up resistors to ensure busses don’t

float under these conditions.

a

100 Ω termination resistors. This will also allow the use of

revision 1.2 silicon on the same PCB, by simply removing

this resistor. Systems that will be populated with only

revision 1.2 silicon (and newer), do not need to be

designed for the external resistors.

Transmit Link Port Connections

Transmit link port connections should follow guidelines in

the tables below. Note that the /LxBCMPO pins for

transmit link ports 1, 2 and 3 can be used for test mode

straps. Refer to the test mode strap section for details. In

cases where only one data transmit signal pair is used, the

remaining 3 transmit pairs should be left unconnected or

terminated with 100Ω resistors as shown in Table-10.

Pin Name Pin Connection

LxDATAO3-0P/N Link Partner

LxCLKOUTP/N Link Partner

LxACKI Link Partner

/LxBCMPO Link Partner

Table-9: 4-bit Transmit Link Port

*

If either the host or external memory bus widths are

configured as 64-bits, then the multiprocessing memory

space must be configured as 64-bits as well. If external

wait-state mode is used, please ensure that no contention

on the ACK signal occurs.

Link Ports Pins

The ADSP-TS201S and ADSP-TS202S contain four

full-duplex Link Ports, whereas the ADSP-TS203S

contains only two full-duplex Link Ports. Each link port’s

receive and transmit sections operate independently and

may or may not be used or connected to other link

partners. If link ports are used then all link port pins must

be connected between link partners. The only exception is

for 1-bit data mode operation. Refer to the following

sections for connecting or terminating the transmit and

receive link port.

The Link Ports on revision 1.2 silicon have a

L

Systems that will be populated with revision 1.0 or 1.1 of

ADSP-TS20x silicon, must be designed to use external

100 Ω terminating resistor across the LVDS P/N

clock and data pin pairs, on the link port input

pins (i.e. the receiver pin pairs), incorporated

on-chip. Therefore, an external 100Ω

terminating resistor is no longer required on the

PCB.

Pin Name Pin Connection

LxDATAO3-1P/N NC

LxDATAO0P/N Link Partner

LxCLKOUTP/N Link Partner

LxACKI Link Partner

/LxBCMPO Link Partner*

Table-10: 1-bit Transmit Link Port

Pin Name Pin Connection

LxDATAO3-0P/N NC

LxCLKOUTP/N NC

LxACKI NC

/LxBCMPO NC*

Table-11: Unused Transmit Link Port

*

: Refer to Test Mode strap section for information on

providing PCB pads for optional resistor placement for

system debug.

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 9 of 14

Page 10

• Receive Link Port Connections

Receive link port connections should follow guidelines in

the tables below. If a receive link port is used, all pins

must be connected with the exception of the 3 data pins

when using a 1-bit wide data port.

For silicon revisions 1.0 and 1.1, each LVDS receive pair

that is connected to a link partner requires an external

100 Ω 1% terminating resistor. These resistors must be

placed as close to the receiving link port pins as possible.

a

Pin Name Pin

Connection

LxDATAI3-1P/N V

No

DD_IO

LxDATAI0P/N Link Partner Yes*

LxCLKINP/N Link Partner Yes*

LxACKO Link Partner N/A

/LxBCMPI Link Partner N/A

Termination

Resistor

100 Ohm 1% External

LVDS Terminating

Resistor

LVDS

Link Transmitter

PP

Tx

NN

PCB

Routing

LVDS

Rx

Link Receiver

Figure-10: LVDS Receive Termination (for silicon

revisions 1.0 and 1.1)

For silicon revisions 1.2 and newer, the external 100Ω 1%

terminating resistor is not required.

Figure-11: LVDS Receive Termination (for silicon

revisions 1.2 and newer)

Pin Name Pin

Connection

Termination

Resistor

LxDATAI3-0P/N Link Partner Yes*

LxCLKINP/N Link Partner Yes*

LxACKO Link Partner N/A

/LxBCMPI Link Partner N/A

Table-12: 4-bit Receive Link Port

Table-13: 1-bit Receive Link Port

Pin Name Pin

Connection

LxDATAI3-0P/N V

LxCLKINP/N V

DD_IO

DD_IO

No

No

Termination

Resistor

LxACKO NC N/A

/LxBCMPI NC or VSS N/A

Table-14: Unused Receive Link Port

*

The receive link ports on revision 1.2 silicon does not

require any external terminating resistors.

• Using Connectors for Link Port Communication

Some applications may require either daughter-cards

or cable connectors for communications between link

ports on separate systems. This requires special

considerations for inputs when the cable or perhaps

daughter-board is not used or plugged in.

The following guidelines should be followed when

using connectors:

• LxDATAO3-0P/N, LxCLKOUTP/N, LxBCMPO

and LxACKO; these outputs should be connected

to the connector or left unconnected if not used

(for example using only 1-bit data).

• LxDATAI3:0P/N and LxCLKINP/N; these

differential inputs require an input termination

resistor located close to the receiver pins if they

are used. (For silicon revision 1.2 and newer, this

external input termination resistor is not

required.)

• LxACKI; this signal has an internal pull-down

resistor. No special requirements needed.

• /LxBCMPI; this signal has an internal pull-up

resistor. No special requirements needed.

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 10 of 14

Page 11

a

Link Port LVDS PCB Guidelines

• PCB traces should be optimized for 100 Ω differential

impedance.

• Connections should be point-to-point from the Link

Port source to the Link Port destinations. Trace

lengths should be matched to minimize skew. All trace

lengths should be +/- 250 mils. This limits PCB trace

delays to +/- 50 ps.

• For high-speed 4-bit Link Port operation, place the

Link Port clock signals between the four sets of LVDS

data signals

VDD or VSS Plane

2-P

TA

A

AT

D

D

Supply/Gnd plane

A2-N

ATA3-P

D

3-N

DATA

DATA

0-P

DATA0-N

DATA

1-P

D

TA1-N

A

-P

LK

C

CLK-N

Figure-12: 4-Bit Link Port Clock placement

• Minimize the number of PCB vias. Vias reduce signal

integrity. Additional stub length can cause unwanted

reflections.

• No signals or vias between LVDS pairs.

Supply/Gnd plane

W

W

S

S

W

90 degrees not

recommended

LVDS PAIR

recommended

S

W

45 degrees

W

Figure-15: No 90-Deg Angles for LVDS signals

• Do not run any signals under or above LVDS pairs.

"

P

"

S

D

V

L

LVDS PAIR SIGNAL

Not Recommended

A

N

G

I

S

Not Recommended

"

N

"

S

D

V

L

SIGNAL

LVDS PAIR SIGNAL

Not Recommended

L

L

A

N

G

I

S

SIGNALLVDS PAIR

LVDS PAIR SIGNAL

"

P

"

S

D

V

L

Not Recommended

"

N

"

S

D

V

L

Figure-16: No Signals above/below LVDS signals

LVDS PAIR

Not Recommended

SIGNAL

LVDS PAIR

Not Recommended

VIA

Figure-13: No Signals Between LVDS signal

• Do not place any closely spaced signals or vias

between adjacent LVDS pairs unless careful analysis

is done.

VDD or VSS Plane

• Place LVDS differential signals on the top or bottom

layer of the PCB if possible. A solid supply or ground

plane directly underneath the LVDS signals is also

required. This configuration is typically referred to as

“MicroStrip”.

Supply/Gnd Plane

"

"P

DS

V

L

LVDS PAIR

N"

"

DS

V

L

"MicroStrip"

LVDS PAIR

SIGNAL

Not Recommended

or VIA

LVDS PAIR

Figure-14: No Signals Between LVDS pairs

• No 90 degrees angles for LVDS routing. Use 45-

degree bends and maintain constant width and space

Figure-17: MicroStrip Example

• If placement of LVDS signals is not possible on the

top or bottom layers of the PCB, it is acceptable to

sandwich the LVDS layers in between supply and/or

ground planes. This configuration is referred to as

“StripLine”.

between all LVDS pairs and spacing between adjacent

LVDS pairs.

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 11 of 14

Page 12

a

VDD or VSS Plane

"StripLine"

Sup

AC ground

d

n

ly/G

p

Planes

D'

D'

Sign

l

a

LVDS PAIR

Figure-18: StripLine Example

Although the StripLine topology significantly reduces

EMI, it does have some drawbacks.

1. Difficulty maintaining constant impedance

2. Higher propagation delay (~1 ½ times)

3. May require additional vias and layers

• It is recommended that the supply and/or ground plane

extend past the edges of all LVDS signals.

Supply/Gnd

Plane

D'

VDS "N"

L

D'

LVDS "P"

LVDS PAIR

Figure-19: Supply Plane overlap of LVDS signal

• If a Non-LVDS (single ended) signal must run on the

same plane as LVDS signals, a ground or supply trace

should be inserted between the LVDS signal and the

Non-LVDS signal.

Supply/Gnd Plane

"

LVDS

LVDS PAIR

"

P

"

VD

L

D'

N

"

S

LVDS Pair

W S

P N

Microstrip (Supply / Ground Plane)

W W S

D

LVDS Pair

P N

H

W

D'D'

Figure-21: MicroStrip PCB guidelines

(Supply / Ground Plane)

W S

P N

Stripline (Supply / Ground Plane)

W W S

D

P N

H

W

D'D'

Figure-22: StripLine PCB guidelines

W = Width of PCB trace

S = Space between LVDS pair.

D = Distance between LVDS pairs

D’ = Space to ground or supply plane edge

D’ = Distance to neighboring supply trace

H = Height between signal and next layer

Note: The following PCB (S, D and H) Ratios are also

required. Optimize the differential impedance of

100 Ω.

S < 2W

D, D’ >= 2S

H > S

Figure-20: Non LVDS signal to LVDS distance

• Below are some industry standard guidelines for

LVDS signal routing.

Booting

To understand the booting process for each of the boot

modes in further detail, please refer to TigerSHARC

processor engineering note ADSP-TS20x TigerSHARC

Processor Boot Loader Kernels Operation (EE-200) [8].

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 12 of 14

Page 13

After reset, the ADSP-TS20xS has four boot options for

beginning operation: EPROM Boot, Host Boot, Link Port

Boot, and No Boot.

EPROM Boot:

•

Master Boot Mode, TigerSHARC processor starts

actively fetching externally.

The ADSP-TS20xS processor defaults to EPROM

booting depending on the value of the /BMS strap pin.

When the processor is configured to boot from

EPROM, /BMS is active during the boot sequence and

should be connected to the chip select signal of the

EPROM. For additional information refer to the /BMS

strap pin section.

• Host Boot:

Slave Boot Mode: TigerSHARC processor expects

code to be placed internally.

The ADSP-TS20xS processor supports booting from

an external master (host or another ADSP-TS20xS).

Any master on the cluster bus can boot the ADSPTS20xS through writes to its internal memory or

through auto DMA.

For host boot, place a sufficiently strong resistor

(typically 500 Ω) between /BMS and V

DD_IO

.

a

internal memory addresses 0 through 255, and to issue

an interrupt at the end of the block (similar to an

external port DMA). The corresponding DMA

interrupts are set to address zero. For additional

information refer to the /BMS and TMR0E strap pin

sections.

For Link Port boot place a sufficiently strong resistor

(typically 500 Ω) between /BMS and V

• No Boot:

Master mode: TigerSHARC processor will start from

IRQ vector (externally or internally) fetching data.

The ADSP-TS20xS processor will begin execution

from the memory address selected with one of the

/IRQ3-0 interrupt signals. Using the ‘no boot’ option,

the ADSP-TS20xS will start running from memory

when one of the interrupts is asserted. For additional

information refer to the /BMS and /BM strap pin

sections.

For No boot (boot from memory address) place a

sufficiently strong resistor (typically 500 Ω) between

/BM to V

(typically 500 Ω) between /BMS to V

and place a sufficiently strong resistor

DD_IO

Miscellaneous Items

DD_IO

DD_IO

.

.

• Link Port Boot:

Slave Boot Mode: TigerSHARC processor expects

code to be placed internally.

All four receive link port DMA channels are

initialized after reset to transfer a 256-word block to

It is important to run PCB signal integrity an alysis for

all signals in a single or multiprocessor ADSPTS20xS based systems.

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 13 of 14

Page 14

a

References

[1] ADSP-TS201S TigerSHARC Embedded Processor Data Sheet, Analog Devices, Inc.

ADSP-TS202S TigerSHARC Embedded Processor Data Sheet, Analog Devices, Inc.

ADSP-TS203S TigerSHARC Embedded Processor Data Sheet, Analog Devices, Inc.

[2] ADSP-TS201S TigerSHARC Processor Hardware Reference, Analog Devices, Inc.

[3] ADSP-TS201S TigerSHARC Processor Programming Reference, Analog Devices, Inc.

[4] Analog Devices JTAG Emulation Technical Reference (EE-68). Analog Devices, Inc.

[5] Estimating Power For The ADSP-TS201S (EE-170), Analog Devices, Inc.

[6] Thermal Relief Design for the ADSP-TS20xS TigerSHARC Processor (EE-182), Analog Devices, Inc.

[7] User Guide to ADSP-TS201S TigerSHARC processor IBIS files (EE-198)

[8] ADSP-TS20x TigerSHARC Processor Boot Loader Kernels Operation (EE-200), Analog Devices, Inc.

[9] Considerations for Porting Code from the ADSP-TS101S TigerSHARC Processor to the ADSP-TS201S TigerSHARC

Processor (EE-205), Analog Devices, Inc.

Document History

Version Description

Rev 4 – January 15, 2005

by Greg F.

Rev 3 – May 19, 2003

by John A. & Phil G.

Rev 0.6 – October 23, 2003

by Phil G.

Rev 0.5 – October 22, 2003

by Greg F., John A. & Phil G.

Modified for production silicon.

Updated link port section for rev 1.2 silicon.

Updated SCLK_Vref information per data sheet spec

Discussing Rev 1.0 silicon

Revised title from

ADSP-TS201S TigerSHARC System Design Guidelines

to ADSP-TS20xS TigerSHARC System Design Guidelines

First released version

ADSP-TS20xS TigerSHARC® System Design Guidelines (EE-179) Page 14 of 14

Loading...

Loading...