Page 1

Engineer To Engineer Note EE-169

Technical Notes on using Analog Devices' DSP components and development tools

a

Estimating Power For The ADSP-TS101S

Contributed by Greg F. February 24, 2003

Contact our technical support by phone: (800) ANALOG-D or e-mail: dsp.support@analog.com

Or visit our on-line resources http://www.analog.com/dsp and http://www.analog.com/dsp/EZAnswers

Introduction

This EE note will discuss power consumption

estimation based on characterized measurements

for the ADSP-TS101S digital signal processor.

The motivation for this document is to assist

board designers by providing data as well as

recommendations that will allow the designer to

estimate their power budget for their power

supply and thermal relief designs.

The ADSP-TS101S is an ultra-high-performance,

static superscalar, 32-bit processor from the

TigerSHARC DSP family of Analog Devices.

The DSP operates at a core clock frequency of

300 MHz with the core operating at 1.2V (V

and the I/O operating at 3.3V (V

). The data

DD_IO

DD

)

presented in this EE note is actual measured

power consumption for silicon revision 0.2 of the

ADSP-TS101S.

Power Consumption

Total power consumption has two components,

one due to internal circuitry and one due to the

switching of external output drivers. The

following sections will show how to derive both

of these power numbers.

Devices provides current consumption numbers

for discrete activity levels. System application

code can be mapped to these discrete numbers to

estimate internal power consumption for an

ADSP-TS101S processor for a given application.

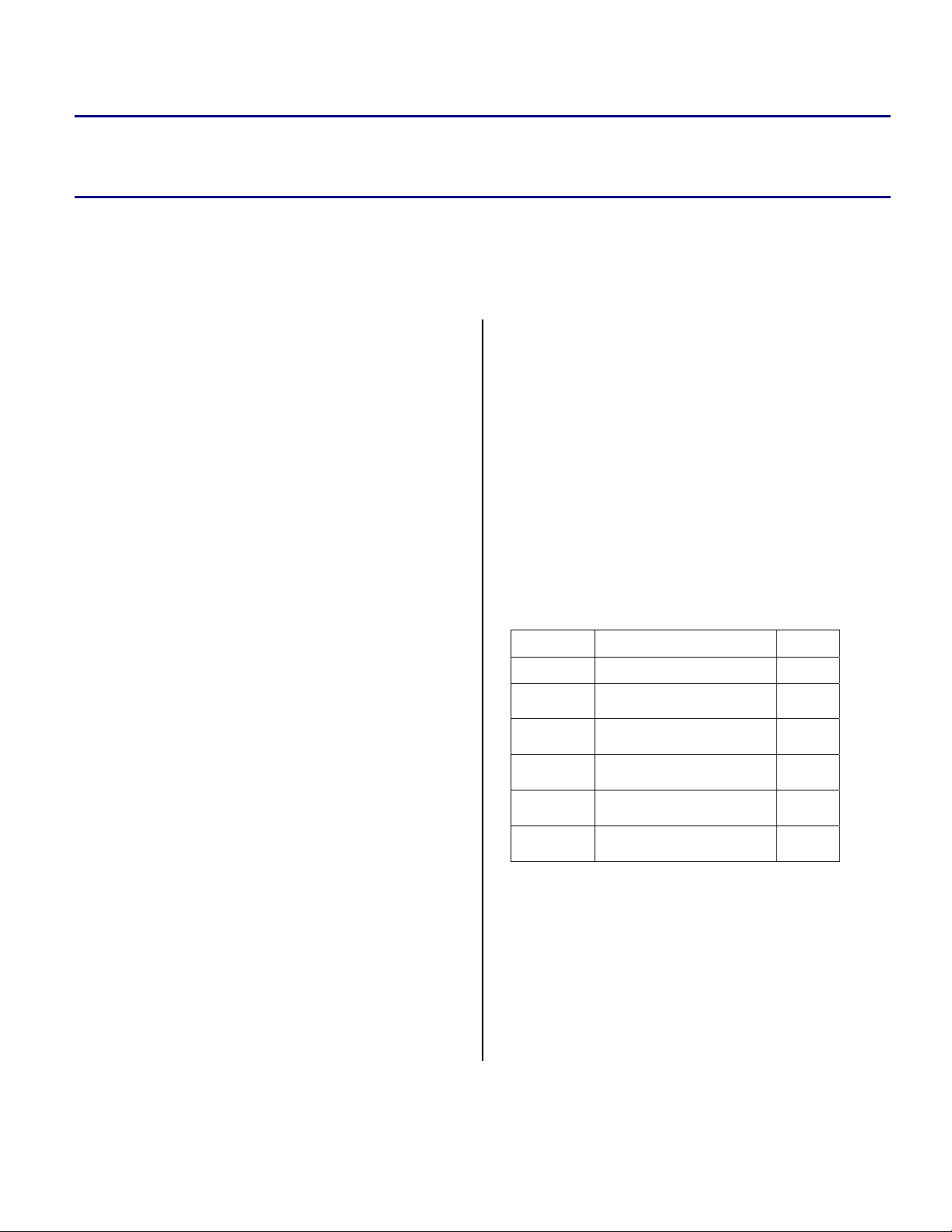

Table 1 below shows the current consumption for

the DSP at different levels of activity. From these

internal activity levels (and from an

understanding of the program flow using

profiling or some other means), you can calculate

a weighted-average of power consumption for

each ADSP-TS101S processor in a system.

Parameter Test Conditions IDD (A)

T

=25C, VDD=1.20V, @ 300

I

DDMAX

I

DDTYP

I

DDCTRL

I

DDDMA

I

DDIDLE

I

DDIDLELP

Table 1: Internal Power Vectors

CASE

MHz

T

=25C, VDD=1.20V, @ 300

CASE

MHz

T

=25C, VDD=1.20V, @ 300

CASE

MHz

T

=25C, VDD=1.20V, @ 300

CASE

MHz

T

=25C, VDD=1.20V, @ 300

CASE

MHz

T

=25C, VDD=1.20V, @ 300

CASE

MHz

1.5460

1.5130

0.8380

0.6835

0.6650

0.1723

Internal Power Vector Definitions

Internal Power Consumption Estimation

The internal power consumption (on the VDD

supply) is dependent on the instruction execution

sequence and the data operands involved. Analog

Copyright 2003, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of

customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property

of their respective holders. Information furnished by Analog Devices Applications and Development Tools Engineers is believed to be accurate and reliable,

however no responsibility is assumed by Analog Devices regarding the technical accuracy and topicality of the content provided in all Analog Devices’ Engineer-toEngineer Notes.

The following power vector definitions apply to

the internal average power vectors shown above

in Table 1:

• I

Maximum activity is a SIMD quad 16-bit fixed-point

DDMAX

--- V

supply current for maximum activity.

DD

Page 2

a

multiply and an add in parallel with two quad-word data

fetches. The data fetched and operated on are random. This

vector includes DMA activity as described below in the

I

definition.

DDDMA

• I

activity is a SIMD quad 16-bit fixed-point compute

operation in parallel with two quad-word data fetches. The

data fetched and operated on are random. This vector

includes DMA activity as described below in the I

definition.

•

I

Control activity is continuous decision-making and

predicted branches. The branch prediction is deliberately

set to be incorrect 50% of the time for equal distribution.

This vector includes DMA activity as described below in

the I

• I

activity is a single external port DMA from external to

internal memory, quad-word transfers of 32 words total.

The DMA is chained to itself (in order to run continuously),

and the DMA does not use interrupts. After setup, the core

is not involved, executing the IDLE instruction only.

•

I

activity is the core executing the IDLE instruction only

with no DMA or interrupts.

•

I

Low Power activity is the core executing the IDLE(LP)

instruction only with no DMA or interrupts.

--- V

DDTYP

DDCTRL

DDDMA

DDIDLE

DDIDLELP

--- V

DDDMA

--- V

--- V

supply current for typical activity. Typical

DD

supply current for control activity.

DD

definition.

supply current for DMA activity. DMA

DD

supply current for idle activity. Idle

DD

--- V

supply current for idle low power. Idle

DD

DDDMA

The average current consumption for an ADSPTS101S for a specific application is calculated

according to the following formula, where “%” is

the percentage of the overall time that the

application spends in that state:

(% Maximum Activity Level x I

(% Typical Activity Level x I

(% Control Activity Level x I

(% DMA Activity Level x I

(% Idle Activity Level x I

+ (% Idle Low Power Activity Level x I

= Total Current for V

= I

DD

Equation 1: Internal Current (IDD) Calculation

DD

DDTYP

DDCTRL

DDDMA

DDIDLE

DDMAX

)

)

)

)

)

DDIDLELP

)

Therefore, the estimated average internal power

consumption (PDD) can be calculated as follows:

P

= IDD x V

DD

DD

Equation 2: Internal Power (PDD) Estimation Calculation

For example, after profiling the application code

the entire system activity is determined as

follows:

- 30% Maximum Activity Level

- 30% Typical Activity Level

- 20% DMA Activity Level

- 20% Idle Activity Level

Example 1: Internal System Activity Level Example

From the percentages of this example, one can

estimate a value for the current consumption of a

single processor as follows:

(30% x 1.5460A)

(30% x 1.5130A)

(20% x 0.6835A)

+ (20% x 0.6650A)

= 1.1874A

= I

Example 2: Internal Current Estimation Example

DD

Therefore, the average internal power estimation

for the processor can be calculated from example

2 above as follows:

P

= 1.1874A x 1.20V

= 1.43W

Example 3: Internal Power Estimation Example

DD

External Power Consumption Estimation

The external power consumption (on V

consumed by the switching of the output pins

and is system dependent. For each unique group

of pins, the magnitude of power consumed

depends on the following:

• The number of output pins that switch

during each cycle, O

• The load capacitance of the output pins, C

• Their voltage swing, V

DD_IO

• The maximum frequency at which the pins

can switch, f

DD_IO

) is

Estimating Power For The ADSP-TS101S (EE-169) Page 2 of 5

Page 3

a

The load capacitance should include the input

capacitance of each connected device as well as

the DSP's own input capacitance (C

). For

IN

additional accuracy, trace capacitance should be

included if possible. The switching frequency

includes driving the load high and then back low.

Address and data pins can drive high and low at

a maximum frequency of ½ SCLK (50MHz).

Equation 3 below shows how to calculate the

average external current (I

) given the above

DD_IO

parameters:

I

= O x C x V

DD_IO

DD_IO

x f

Equation 3: External Current (I

) Calculation

DD_IO

Therefore, the estimated average external power

consumption (P

) can be calculated as

DD_IO

follows:

P

DD_IO

= I

DD_IO

x V

DD_IO

Equation 4: External Power (P

) Calculation

DD_IO

For example, estimate P

for the external

DD_IO

port pins with the following assumptions:

• The example system consists of four ADSPTS101S processors with one bank of shared

external memory (64-bit), where C

= 5pF

IN

per TigerSHARC DSP.

• Two 1M × 32 SDRAM chips are used, each

with a load of 5 pF per pin (trace

capacitance is neglected for this example).

• Continuous burst of quad-word (128-bit)

writes occur every cycle at a rate of SCLK,

with 50% of the data pins switching (this

represents random data).

• The external address increments sequentially

on a transaction boundary (every quadword). For sequential addressing, the

number of address bits switching per cycle

approaches 2-bits.

• The control pins switch for refresh cycles

and page boundary crossings.

• SCLK = 100Mhz (bus cycle time).

The I

equation is calculated for each class of

DD_IO

pins that can drive as shown in Table 2.

Pin

# of

Type

Pins % Switching

Data 64 50 5pF

Addr 32 6.25 10pF

Ctrl 8 50 10pF

Table 2: External Current (I

x C x V

+ 4 x C

+ 4 x C

+ 4 x C

DD_IO

3.3V 50

IN

3.3V 25

IN

3.3V 250

IN

) Calculation Example

x f = I

DD_IO

MHz

MHz

KHz

DD_IO

0.1320A

0.0049A

0.0001A

From the data tabulated in Table 2 above, the

external average current consumed by the DSP

can be calculated by summing all of the data

from the right-most column:

I

= 0.1320A + 0.0049A + 0.0001A

DD_IO

Example 4: Total Average Estimated Current Calculation

Using the result from Example 4, the estimated

average external power can be calculated as

follows:

P

= 0.1370A x 3.3V

DD_IO

Example 5: Total Average Estimated Power Calculation

Therefore, from this example system an

estimated total of 0.4521W has been calculated

as the average external power consumption for

our system.

Power Supply Design

From the previous two sections we have shown

how to estimate the average current and power

consumption values for the internal and external

power domains for a given system.

When designing a power supply, the designer

must ensure that the power supply is capable of

handling worst-case sustainable power

consumption. Therefore, guard-banded values for

the maximum internal (P

(P

) power requirements should be used.

DD_IO

) and external

DD

Estimating Power For The ADSP-TS101S (EE-169) Page 3 of 5

Page 4

a

This will ensure that the power supply design

will provide sufficient voltage at a relatively high

efficiency (typically greater than 90%) to each of

the two voltage domains (V

and V

DD

DD_IO

) during

sustained periods of maximum activity. This is

due to the fact that the power required during a

sustained maximum operating condition may be

greater than what can be supplied by bypass

and/or bulk capacitance.

For the core voltage (V

), the power supply

DD

design must be capable of supplying the

maximum sustainable power consumption under

worst-case conditions. This specific value is

I

(from Table 1), VDD = 1.26V, 85°C, and

DDMAX

300 MHz (from the data sheet). For the I/O

domain (V

), the power supply design must

DD_IO

be capable of supplying a guard-banded

conservative power consumption estimate for I/O

activity (V

= 3.45V, from the data sheet).

DD_IO

This is to ensure sufficient overhead in the power

supply design during sustained periods of high

activity on the I/O domain.

Another critical specification when selecting a

power supply (that can properly supply your

system within normal operating specifications

and at maximum efficiency) is the maximum

dI/dt required by the processor. This number is

simply the worst-case change in current required

by the processor over a short time interval. This

specification corresponds with the response time

of your power supply.

We can calculate the value for dI/dt max as

follows:

dI/dt

= (I

= (1.5460A – 0.6650A) / (8 x 3.3ns)

= 33.371 A/µs

MAX

DDMAX

– I

DDIDLE

) / (8 x t

CCLK

)

Example 6: Maximum dI/dt Calculation

Where “t

” represents the core clock period

CCLK

of the DSP while operating at a frequency of 300

MHz, and the value “8” represents the minimum

number of cycles to exit an “idle” instruction via

an external interrupt, due to the length of the

processor’s instruction pipeline.

Thermal Relief Design

The overall system power estimation can also be

used to estimate the requirements for a thermal

relief design. Equation 5 below gives a value for

the total average estimated power. Note that this

equation yields total estimated average power

consumption for a single ADSP-TS101S in a

given system. Guard-banding this value is

recommended for a thermal relief design that will

allow the system to operate within specified

thermal parameters.

P

= VDD x IDD + V

TOTAL

Equation 5: Total Estimated Average Power

Note that guard-banded values taken at worstcase conditions (V

= 1.26V, f = 300 MHz,

DD

temp = 85°C), are used when considering a

design for thermal relief.

Therefore, for the complete system example,

(which is comprised of a cluster of four ADSPTS101S processors and a shared bank of external

memory comprised of two 1M x 32 SDRAM

chips), we can estimate the total system power

budget as follows:

P

= PDD (average) + P

TOTAL

Equation 6: Total System Power Calculation

DD_IO

DD_IO

x I

DD_IO

(average)

Estimating Power For The ADSP-TS101S (EE-169) Page 4 of 5

Page 5

a

Compensation Curves

The following section of this EE note shows

I

and maximum allowable values for processor

core voltage, operating frequency, and operating

temperature. These curves can be used to

extrapolate data (from Table 1) to estimate more

precise values for a system, depending upon the

specific operational parameters of the system.

Figure 1 shows a graph for the maximum internal

current (I

tolerances. The data for this graph was obtained

while operating the processor at its maximum

operating frequency and at nominal operating

temperature, 300 MHz and 25°C, respectively.

Figure 1: I

Figure 2 shows a graph for the maximum internal

current (I

operating range. The data for this graph was

obtained while operating the processor at its

maximum operating frequency and at nominal

V

compensation curves versus the minimum

DDMAX

) versus VDD operating range

DDMAX

Iddmax Current vs. Voltage

(@ 25C, 300MHz)

1.7

1.65

1.6

1.55

1.5

Idd (A)

1.45

1.4

1.35

1.3

, 300 MHz and 1.20V, respectively.

DD

1.14 1.2

Current vs. Voltage

DDMAX

) versus the specified temperature

DDMAX

Voltage (V)

1.26

Iddmax Current vs. Temperature

(@ 1.20V, 300MHz)

2

1.8

1.6

1.4

1.2

1

0.8

Idd (A)

0.6

0.4

0.2

0

-40 25 85

Temp (C)

Figure 2: I

Current vs. Temperature

DDMAX

Figure 3 shows a graph for the maximum internal

current (I

) versus the specified operating

DDMAX

frequency range. The data for this graph was

obtained while operating the processor at its

nominal temperature and voltage, 25°C and

1.20V, respectively.

Iddmax Current vs. Frequency

(@25C, 1.20V Vdd)

1.8

1.6

1.4

1.2

1

0.8

0.6

0.4

Frequency (MHz)

0.2

0

100 150 200 250 300

Idd (A)

Figure 3: I

Current vs. Frequency

DDMAX

Document History

Version Description

Feb 24, 2003 by Greg F. Updated Data For 300MHz Upgrade

Sep 23, 2002 by Greg F. Initial Release

Estimating Power For The ADSP-TS101S (EE-169) Page 5 of 5

Loading...

Loading...