www.BDTIC.com/IC

HDMI/DVI TMDS Equalizer

FEATURES

One input, one output HDMI/DVI high speed signal

equalizer/driver

Enables HDMI 1.3 receive-compliant input

Four TMDS channels per input/output

Supports 250 Mbps to 2.25 Gbps data rates

Supports 25 MHz to 225 MHz pixel clocks

Fully buffered unidirectional inputs/outputs

Equalized inputs for operation with long HDMI cables

(20 meters at 2.25 Gbps)

Pre-emphasized outputs

Matched 50 Ω input and output on-chip terminations

Low added jitter

Transmitter disable feature

Reduces power dissipation

Disables input terminations

Single-supply operation (3.3 V)

Standards compliant: HDMI receiver, DVI

40-lead, 6 mm × 6 mm, RoHS-compliant LFCSP

APPLICATIONS

Multiple input displays

Advanced television set (HDTV) front panel connectors

HDMI/DVI cable extenders

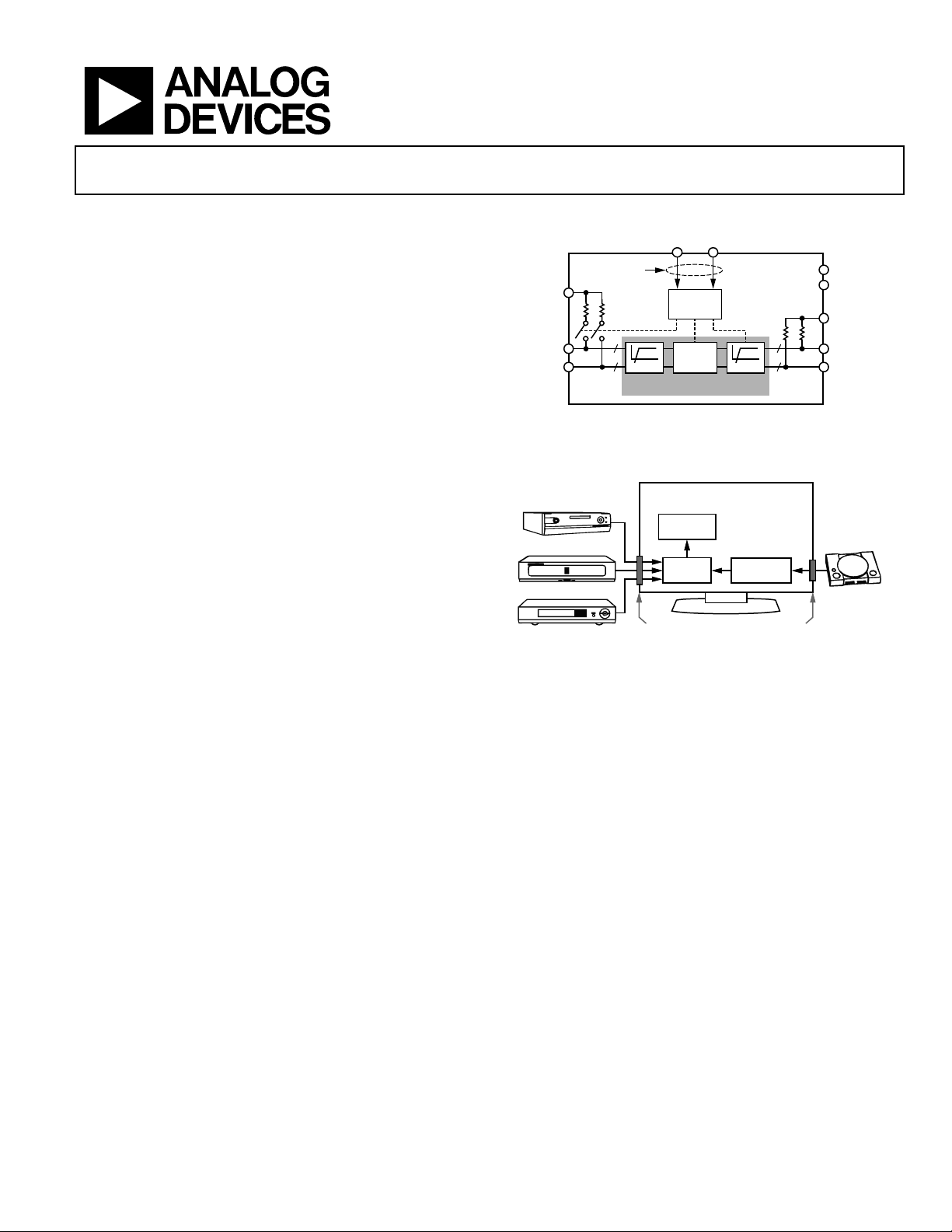

VTTI

IP[3:0]

IN[3:0]

MEDIA CENTER

SET-TOP BOX

DVD PLAYER

ADV3003

FUNCTIONAL BLOCK DIAGRAM

PE_EN TX_EN

PARALLEL

CONTROL

CONTROL

LOGIC

+

4

4

–

BUFFER

EQ

HIGH SPEED BUFFERED

Figure 1.

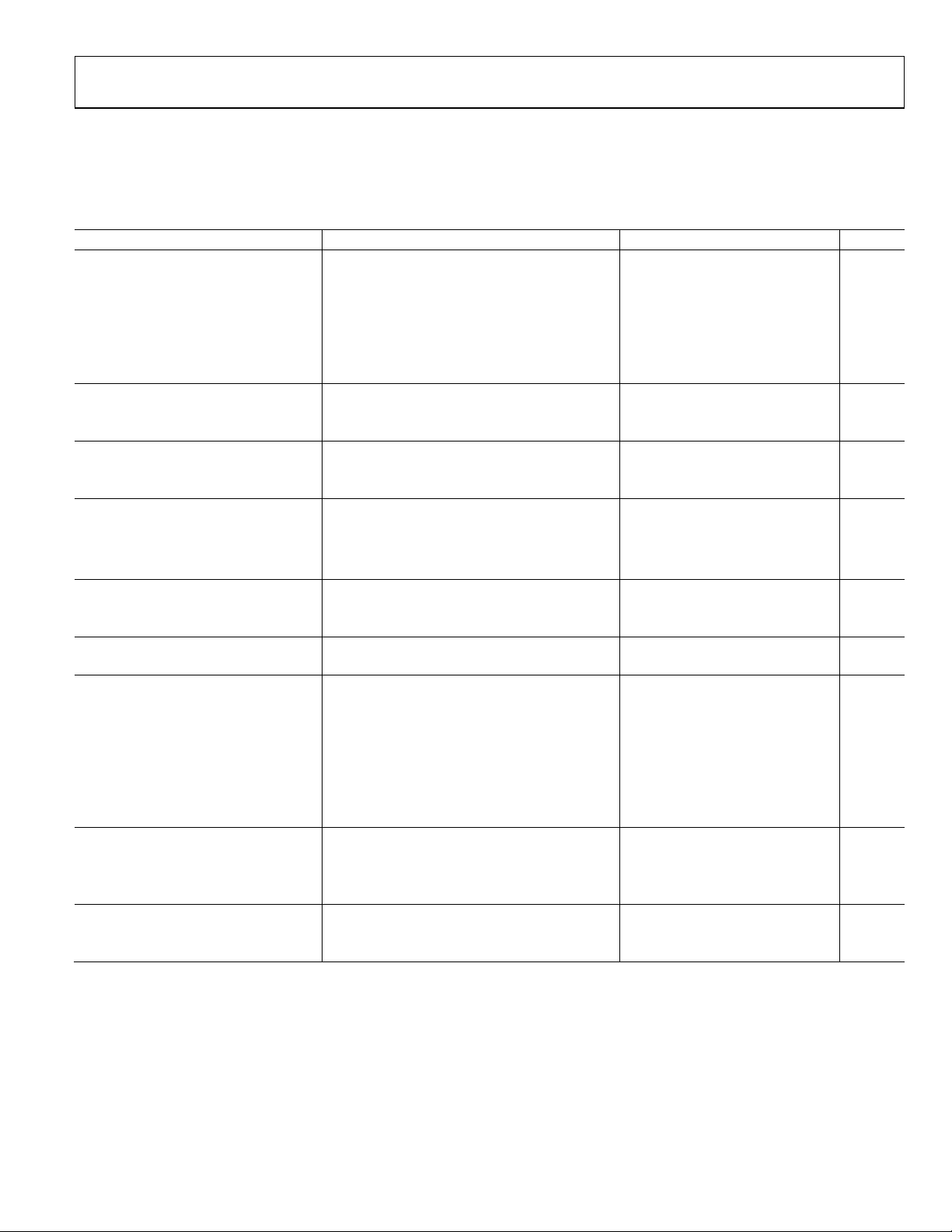

TYPICAL APPLICATION DIAGRAM

HDMI

RECEIVER

4:1 HDMI

SWITCH

BACK PANEL

CONNECTORS

Figure 2.

ADV3003

4

4

PE

HDTV SET

ADV3003

FRONT PANEL

CONNECT OR

+

–

AVCC

AVEE

VTTO

OP[3:0]

ON[3:0]

GAME

CONSOLE

7212-001

07212-002

GENERAL DESCRIPTION

The ADV3003 is a 4-channel transition minimized differential

signaling (TMDS) buffer featuring equalized inputs and

pre-emphasized outputs. The ADV3003 features 50 Ω input

and output terminations, providing full-swing output signal

recovery and minimizing reflections for improved system

signal integrity. The ADV3003 is targeted at HDMI™/DVI

applications and is ideal for use in systems with long cable

runs, long PCB traces, and designs with interior cabling.

The ADV3003 is provided in a 40-lead, LFCSP, surface-mount,

RoHS-compliant, plastic package and is specified to operate

over the −40°C to +85°C temperature range.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

PRODUCT HIGHLIGHTS

1. Supports data rates up to 2.25 Gbps, enabling 1080p deep

color (12-bit color) HDMI formats and greater than UXGA

(1600 × 1200) DVI resolutions.

2. The 12 dB input cable equalizer enables the use of long

cables at the input. For a typical 24 AWG cable, the

ADV3003 compensates for more than 20 meters at data

rates up to 2.25 Gbps.

3. The selectable 6 dB of output pre-emphasis allows the

ADV3003 to drive high loss output cables or long PCB traces.

4. Matched 50 Ω on-chip input and output terminations

improve system signal integrity.

5. An external control pin, PE_EN, sets the output

pre-emphasis to either 0 dB or 6 dB.

6. An external control pin, TX_EN, simultaneously disables

both the transmitter and the on-chip input terminations.

This feature reduces the power dissipation of the ADV3003

and indicates to a connected source when the ADV3003 is

disabled.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

ADV3003

www.BDTIC.com/IC

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

Typical Application Diagram .......................................................... 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 4

Thermal Resistance ...................................................................... 4

Maximum Power Dissipation ..................................................... 4

ESD Caution .................................................................................. 4

Pin Configuration and Function Descriptions ............................. 5

REVISION HISTORY

2/08—Revision 0: Initial Version

Typical Performance Characteristics ..............................................6

Theory of Operation ...................................................................... 10

Introduction ................................................................................ 10

Input Channels ........................................................................... 10

Output Channels ........................................................................ 10

Application Notes ........................................................................... 12

Pinout ........................................................................................... 12

Cable Lengths and Equalization ............................................... 12

Pre-Emphasis .............................................................................. 12

PCB Layout Guidelines .............................................................. 12

Outline Dimensions ....................................................................... 15

Ordering Guide .......................................................................... 15

Rev. 0 | Page 2 of 16

ADV3003

www.BDTIC.com/IC

SPECIFICATIONS

TA = 27°C, AVCC = 3.3 V, VTTI = 3.3 V, VTTO = 3.3 V, AVEE = 0 V, differential input swing = 1000 mV, pattern = PRBS 27 − 1,

data rate = 2.25 Gbps, TMDS outputs terminated with external 50 Ω resistors to 3.3 V, unless otherwise noted.

Table 1.

Parameter Conditions/Comments Min Typ Max Unit

DYNAMIC PERFORMANCE

Maximum Data Rate (DR) per Channel NRZ 2.25 Gbps

Bit Error Rate (BER) PRBS 223 − 1 10−9

Added Deterministic Jitter DR ≤ 2.25 Gbps, PRBS 27 − 1 25 ps (p-p)

Added Random Jitter 1 ps (rms)

Differential Intrapair Skew At output 1 ps

Differential Interpair Skew

EQUALIZATION PERFORMANCE

Receiver (Fixed Setting)

Transmitter (Pre-Emphasis On)

INPUT CHARACTERISTICS

Input Voltage Swing Differential 150 1200 mV

Input Common-Mode Voltage (V

OUTPUT CHARACTERISTICS

High Voltage Level Single-ended high speed channel AVCC − 200 AVCC + 10 mV

Low Voltage Level Single-ended high speed channel AVCC − 600 AVCC − 400 mV

Rise/Fall Time (20% to 80%) 75 178 ps

TERMINATION

Input Termination Resistance Single-ended 50 Ω

Output Termination Resistance Single-ended 50 Ω

POWER SUPPLY

AVCC Operating range (3.3 V ± 10%) 3 3.3 3.6 V

QUIESCENT CURRENT

AVCC Output disabled 20 40 mA

Output enabled, pre-emphasis off 32 50 mA

Output enabled, pre-emphasis on 66 80 mA

VTTI Input termination on

VTTO Output termination on, pre-emphasis off 40 50 mA

Output termination on, pre-emphasis on 80 100 mA

Output disabled 0 1 mA

POWER DISSIPATION

6

Output disabled 66 148 mW

Output enabled, pre-emphasis off 370 553 mW

Output enabled, pre-emphasis on 686 937 mW

PARALLEL CONTROL INTERFACE TX_EN, PE_EN

Input High Voltage, VIH 2 V

Input Low Voltage, VIL 0.8 V

1

Differential interpair skew is measured between the TMDS pairs of the HDMI/DVI link.

2

ADV3003 output meets the transmitter eye diagram mask as defined in the HDMI Standard Version 1.3a and the DVI Standard Version 1.0.

3

Cable output meets the receiver eye diagram mask as defined in the HDMI Standard Version 1.3a and the DVI Standard Version 1.0.

4

PE = 0 dB.

5

Typical value assumes the HDMI/DVI link is active with nominal signal swings. Minimum and maximum limits are measured at the extremes of input termination

resistance and input voltage swing, respectively .

6

The total power dissipation excludes power dissipated in the 50 Ω off-chip loads.

1

At output 50 ps

2

Boost frequency = 1.125 GHz 12 dB

3

Boost frequency = 1.125 GHz 6 dB

) AVCC − 800 AVCC mV

ICM

4

5

40 54 mA

Rev. 0 | Page 3 of 16

ADV3003

www.BDTIC.com/IC

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

AVCC to AVEE 3.7 V

VTTI AVCC + 0.6 V

VTTO AVCC + 0.6 V

Internal Power Dissipation 2.0 W

High Speed Input Voltage

High Speed Differential Input Voltage 2.0 V

Parallel Interface (TX_EN, PE_EN)

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +85°C

Junction Temperature 150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

AVC C − 1.4 V < V

AVCC + 0.6 V

AVEE − 0.3 V < V

AVCC + 0.6 V

<

IN

<

IN

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a 4-layer JEDEC circuit board for surface-mount

packages.

circuit board with no airflow.

Table 3.

Package Type θJA θ

40-Lead LFCSP 31.9 2.6 °C/W

is specified for the exposed pad soldered to the

JC

Unit

JC

MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the ADV3003

is limited by the associated rise in junction temperature. The

maximum safe junction temperature for plastic encapsulated

devices is determined by the glass transition temperature of the

plastic, approximately 150°C. Temporarily exceeding this limit

may cause a shift in parametric performance due to a change

in the stresses exerted on the die by the package. Exceeding a

junction temperature of 175°C for an extended period can result

in device failure. To ensure proper operation, it is necessary to

observe the maximum power derating as determined by the

thermal resistance coefficients.

ESD CAUTION

Rev. 0 | Page 4 of 16

ADV3003

www.BDTIC.com/IC

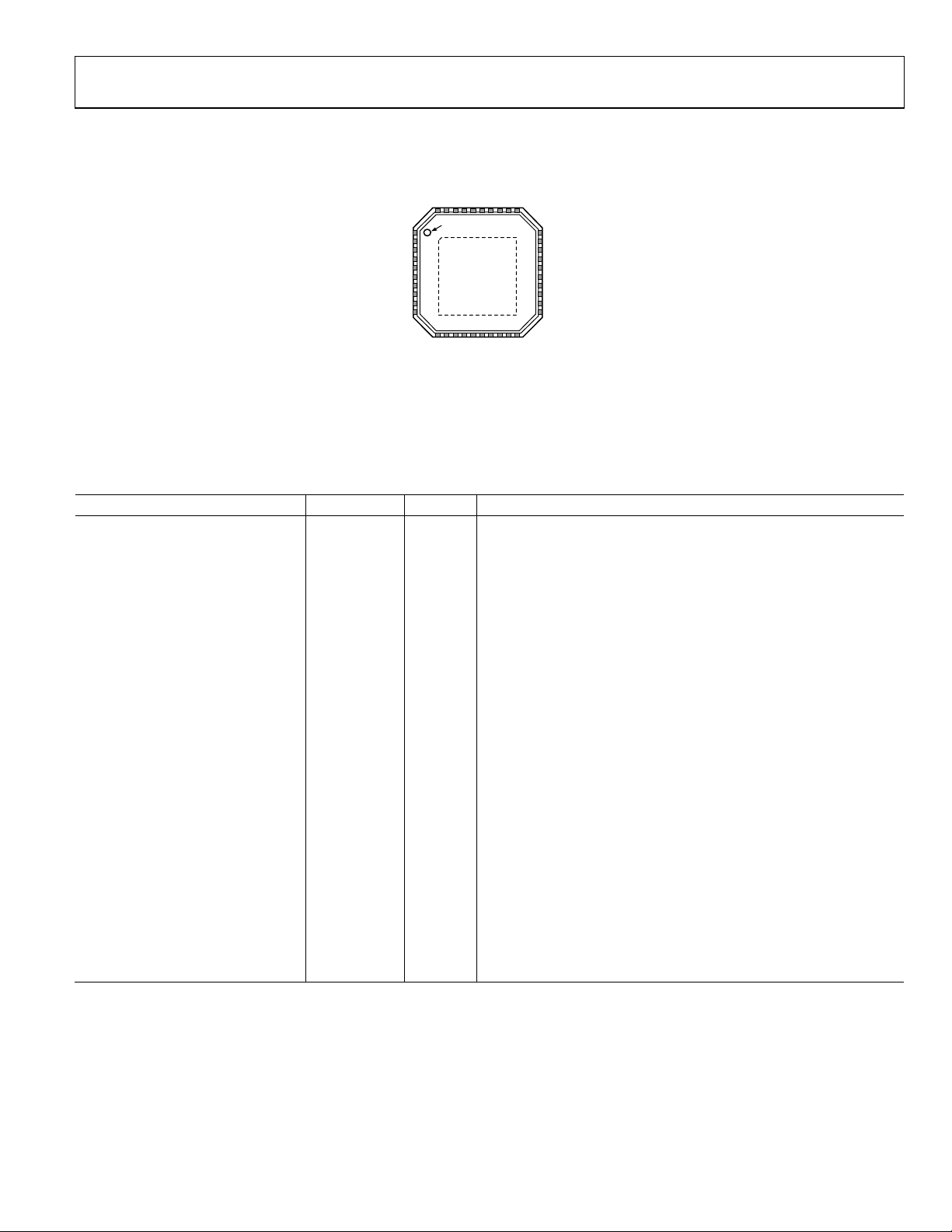

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NC

NC

NC

NC

AVEE

NC

NC

NC

38

39

40

PIN 1

INDICATO R

1IN0

2IP0

3IN1

4IP1

5VTTI

6IN2

7IP2

8IN3

9IP3

10AV CC

NOTES

1. NC = NO CO NNECT.

2. THE ADV 3003 LFCSP HAS AN EX POSED PADDLE (ePAD) ON THE UNDERSIDE

OF THE PACKAG E, WHICH AI DS IN HEAT DISSIPATIO N. THE ePAD MUST BE

ELECTRICALLY CONNECTED TO THE AVEE SUPPLY PLANE TO MEET

ELECTRICAL AND THERMAL SPECIFICATI ONS.

ADV3003

TOP VIEW

(Not to Scale)

11

12

13

OP0

ON0

VTTO

Figure 3. Pin Configuration

AVCC

NC

32

31

33

34

35

36

37

30 AVCC

29 PE_EN

28 TX_EN

27 AVEE

26 AVCC

25 AVCC

24 AVEE

23 AVCC

22 AVCC

21 NC

15

17

16

18

19

14

N1

O

20

OP1

OP2

OP3

ON2

ON3

AVCC

07212-003

Table 4. Pin Function Descriptions

Pin No. Mnemonic Type

1

Description

1 IN0 HS, I High Speed Input Complement.

2 IP0 HS, I High Speed Input.

3 IN1 HS, I High Speed Input Complement.

4 IP1 HS, I High Speed Input.

5 VTTI Power Input Termination Supply. Nominally connected to AVCC.

6 IN2 HS, I High Speed Input Complement.

7 IP2 HS, I High Speed Input.

8 IN3 HS, I High Speed Input Complement.

9 IP3 HS, I High Speed Input.

10, 16, 22, 23, 25, 26, 30, 32 AVCC Power Positive Analog Supply. 3.3 V nominal.

11 ON0 HS, O High Speed Output Complement.

12 OP0 HS, O High Speed Output.

13 VTTO Power Output Termination Supply. Nominally connected to AVCC.

14 ON1 HS, O High Speed Output Complement.

15 OP1 HS, O High Speed Output.

17 ON2 HS, O High Speed Output Complement.

18 OP2 HS, O High Speed Output.

19 ON3 HS, O High Speed Output Complement.

20 OP3 HS, O High Speed Output.

24, 27, 37, ePAD AVEE Power Negative Analog Supply. 0 V nominal.

28 TX_EN Control High Speed Output Enable Parallel Interface.

29 PE_EN Control High Speed Pre-Emphasis Enable Parallel Interface.

21, 31, 33, 34, 35, 36, 38, 39, 40 NC NC No Connect.

1

HS = high speed, I = input, O = output.

Rev. 0 | Page 5 of 16

Loading...

Loading...