JPEG2000 Video Codec

FEATURES

Complete single-chip JPEG2000 compression and

decompression solution for video and still images

Patented SURF™ (spatial ultraefficient recursive filtering)

technology enables low power and low cost waveletbased compression

Supports both 9/7 and 5/3 wavelet transforms with up to

6 levels of transform

Programmable tile/image size with widths up to 2048 pixels

in 3-component 4:2:2 interleaved mode, and up to

4096 pixels in single-component mode

Maximum tile/image height: 4096 pixels

Video interface directly supporting ITU.R-BT656,

SMPTE125M PAL/ NTSC, SMPTE274M, SMPTE293M (525p),

ITU.R-BT1358 (625p) or any video format with a maximum

input rate of 65 MSPS for irreversible mode or 40 MSPS for

reversible mode

Two or more ADV202s can be combined to support full-

frame SMPTE274M HDTV (1080i) or SMPTE296M (720p)

Interlaces temporally coherent frame-based SD video

sources for improved performance

Flexible asynchronous SRAM-style host interface allows

glueless connection to most 16-/32-bit microcontrollers

and ASICs

2.5 V to 3.3 V I/O and 1.5 V core supply

12 mm × 12 mm 121-lead CSPBGA, speed grade 115 MHz, or

13 mm × 13 mm 144-lead CSPBGA, speed grade 135 MHz, or

13 mm × 13 mm 144-lead CSPBGA, speed grade 150 MHz

ADV202

APPLICATIONS

Networked video and image distribution systems

Wireless video and image distribution

Image archival/retrieval

Digital CCTV and surveillance systems

Digital cinema systems

Professional video editing and recording

Digital still cameras

Digital camcorders

GENERAL DESCRIPTION

The ADV202 is a single-chip JPEG2000 codec targeted for

video and high bandwidth image compression applications that

can benefit from the enhanced quality and feature set provided

by the JPEG2000 (J2K)—ISO/IEC15444-1 image compression

standard. The part implements the computationally intensive

operations of the JPEG2000 image compression standard as

well as providing fully compliant code-stream generation for

most applications.

The ADV202’s dedicated video port provides glueless

connection to common digital video standards such as ITU.RBT656, SMPTE125M, SMPTE293M (525p), ITU.R-BT1358

(625p), SMPTE274M(1080i), or SMPTE296M(720p). A variety

of other high speed synchronous pixel and video formats can

also be supported using the programmable framing and

validation signals.

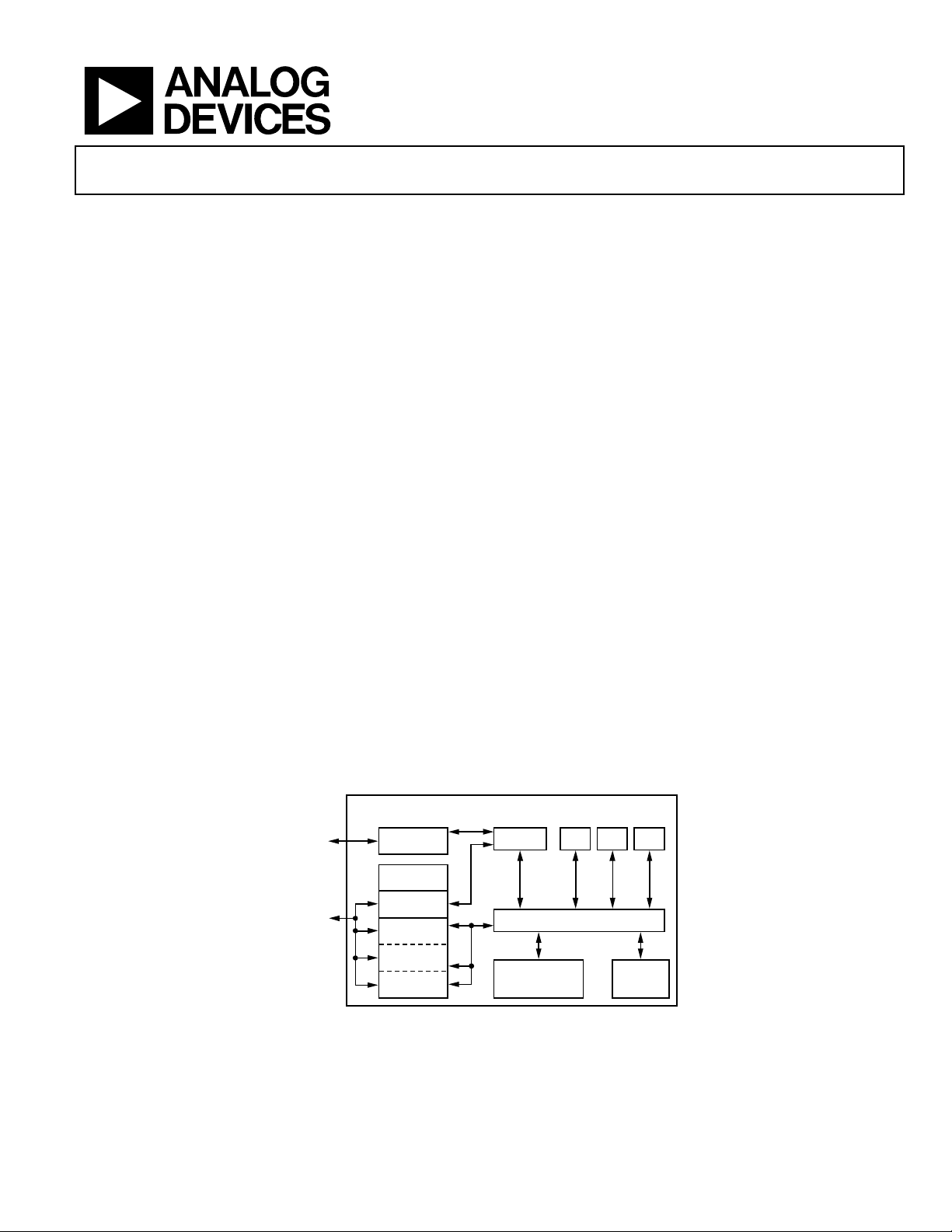

FUNCTIONAL BLOCK DIAGRAM

ADV202

PIXEL I/F

HOST I/F

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

PIXEL I/F

EXTERNAL

DMA CTRL

PIXEL

FIFO

CODE

FIFO

ATTRIBUTE

FIFO

ANCILLARY

FIFO

WAVELET

ENGINE

INTERNAL BUS AND DMA ENGINE

EMBEDDED RISC

PROCESSOR

SYSTEM

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

EC1 EC2 EC3

(continued on Page 3)

MEMORY

SYSTEM

04723-001

www.analog.com

ADV202

TABLE OF CONTENTS

General Description......................................................................... 3

Video Interface (VDATA Bus) .................................................. 26

JPEG2000 Feature Support.......................................................... 3

Specificatons...................................................................................... 4

Supply Voltages and Current....................................................... 4

Input/Output Specifications........................................................ 4

Clock and

RESET

Specifications ................................................ 5

Normal Host Mode—Read Operation ...................................... 6

Normal Host Mode—Write Operation..................................... 7

DREQ/DACK

DREQ/DACK

DMA Mode—Single FIFO Write Operation .. 8

DMA Mode—Single FIFO Read Operation.10

External DMA Mode—FIFO Write, Burst Mode................... 12

External DMA Mode—FIFO Read, Burst Mode.................... 13

Streaming Mode (JDATA)—FIFO Read/Write ......................15

VDATA Mode Timing............................................................... 15

Raw Pixel Mode Timing ............................................................ 17

SPI Port Timing.......................................................................... 18

Pin BGA Assignments and Function Descriptions.................... 19

Pin BGA Assignments ............................................................... 19

Pin Function Descriptions ........................................................ 22

Theory of Operation ...................................................................... 25

Wave l et En g in e ........................................................................... 25

Entropy Codecs........................................................................... 25

Embedded Processor System .................................................... 25

Memory System ..........................................................................25

Internal DMA Engine ................................................................25

Host Interface (HDATA Bus) ................................................... 26

Direct and Indirect Registers.................................................... 26

Control Access Registers ........................................................... 27

Pin Configuration and Bus Sizes/Modes ................................ 27

Stage Register.............................................................................. 27

JDATA Mode............................................................................... 27

External DMA Engine............................................................... 27

SPI Port ........................................................................................ 27

Internal Registers ............................................................................ 28

Direct Registers........................................................................... 28

Indirect Registers........................................................................ 29

PLL ............................................................................................... 30

Hardware Boot............................................................................ 31

Video Input Formats ...................................................................... 32

Applications..................................................................................... 34

Encode—Multichip Mode......................................................... 34

Decode—Multichip Master/Slave............................................ 35

Digital Still Camera/Camcorder .............................................. 35

Encode/Decode SDTV Video Application.............................. 36

ASIC Application (32-Bit Host/32-Bit ASIC)......................... 37

HIPI (Host Interface—Pixel Interface) ................................... 38

JDATA Interface ......................................................................... 38

Outline Dimensions....................................................................... 39

Ordering Guide .......................................................................... 40

ADV202 Interface........................................................................... 26

REVISION HISTORY

1/05—Rev. A to Rev. B

Updated Outline Dimensions....................................................... 39

Rev. B | Page 2 of 40

12/04—Rev. 0 to Rev. A

Changes to Features ..........................................................................1

Changes to Table 2.............................................................................4

Changes to Table 16 ....................................................................... 24

Changes to Table 23 ....................................................................... 32

7/04—Revision 0: Initial Version

ADV202

GENERAL DESCRIPTION

(continued from Page 1)

The ADV202 can process images at a rate of 40 MSPS in

reversible mode and at higher rates when used in irreversible

mode. The ADV202 contains a dedicated wavelet transform

engine, three entropy codecs, an on-board memory system, and

an embedded RISC processor that can provide a complete

JPEG2000 compression/decompression solution.

The wavelet processor supports the 9/7 irreversible wavelet

transform and the 5/3 wavelet transform in reversible and

irreversible modes. The entropy codecs support all features in

the JPEG2000 Part 1 specification, except Maxshift ROI.

The ADV202 operates on a rectangular array of pixel samples

called a tile. A tile can contain a complete image, up to the

maximum supported size, or some portion of an image. The

maximum horizontal tile size supported depends on the wavelet

transform selected and the number of samples in the tile.

Images larger than the ADV202’s maximum tile size can be

broken into individual tiles and then sent sequentially to the

chip while still maintaining a single, fully compliant JPEG2000

code stream for the entire image.

JPEG2000 FEATURE SUPPORT

The ADV202 supports a broad set of features that are included

in Part 1 of the JPEG2000 standard (ISO/IEC 15444). See

Getting Started with ADV202 for information on the JPEG2000

features that the ADV202 currently supports.

Depending on the particular application requirements, the

ADV202 can provide varying levels of JPEG2000 compression

support. It can provide raw code-block and attribute data

output, which allows the host software to have complete control

over the generation of the JPEG2000 code stream and other

aspects of the compression process such as bit-rate control.

Otherwise, the ADV202 can create a complete, fully compliant

JPEG2000 code stream (.j2c) and enhanced file formats such as

.jp2, .jpx, and .mj2 (Motion JPEG2000). See Getting Started with

ADV202 for information on the formats that the ADV202

currently supports.

Rev. B | Page 3 of 40

ADV202

SPECIFICATONS

SUPPLY VOLTAGES AND CURRENT

Table 1.

Parameter Description Min Typ Max Unit

VDD DC Supply Voltage, Core 1.425 1.5 1.575 V

IOVDD DC Supply Voltage, I/O 2.375 3.3 3.63 V

PLLVDD DC Supply Voltage, PLL 1.425 1.5 1.575 V

V

Input Range −0.3 V

Input

Temp Operating Ambient Temperature Range in Free Air −40 +25 +85 °C

IDD Static Current1 300 mA

Dynamic Current, Core (JCLK Frequency = 150 MHz)

2

570 mA

Dynamic Current, Core (JCLK Frequency = 108 MHz) 420 mA

Dynamic Current, Core (JCLK Frequency = 81 MHz) 325 mA

Dynamic Current, I/O 20 mA

Dynamic Current, PLL 2.6 mA

1

No clock or I/O activity.

2

ADV202-150 only.

INPUT/OUTPUT SPECIFICATIONS

Table 2.

Parameter Description Test Conditions Min Typ Max Unit

V

High Level Input Voltage VDD = max 2.2 V

IH (3.3 V)

V

IH (2.5 V)

V

IL (3.3 V, 2.5 V)

V

OH (3.3 V)

V

High Level Output Voltage VDD = min, IOH = −0.5 mA 2.0 V

OH (2.5 V)

V

OL (3.3 V, 2.5 V)

IIH High Level Input Current VDD = max, VIN = VDD 1.0 µA

IIL Low Level Input Current VDD = max, VIN = 0V 1 µA

I

High Level Three-State Leakage Current VDD = max, VIN = VDD 1.0 µA

OZH

I

Low Level Three-State Leakage Current VDD = max, VIN = 0

OZL

CI Input Pin Capacitance 8 pF

CO Output Pin Capacitance 8 pF

High Level Input Voltage VDD = max 1.9 V

Low Level Input Voltage VDD = min 0.6 V

High-Level Output Voltage VDD = min, IOH = −0.5 mA 2.4 V

Low Level Output Voltage VDD = min, IOL = 2 mA 0.4 V

V

1.0 µA

+ 0.3 V

DDI/O

Rev. B | Page 4 of 40

ADV202

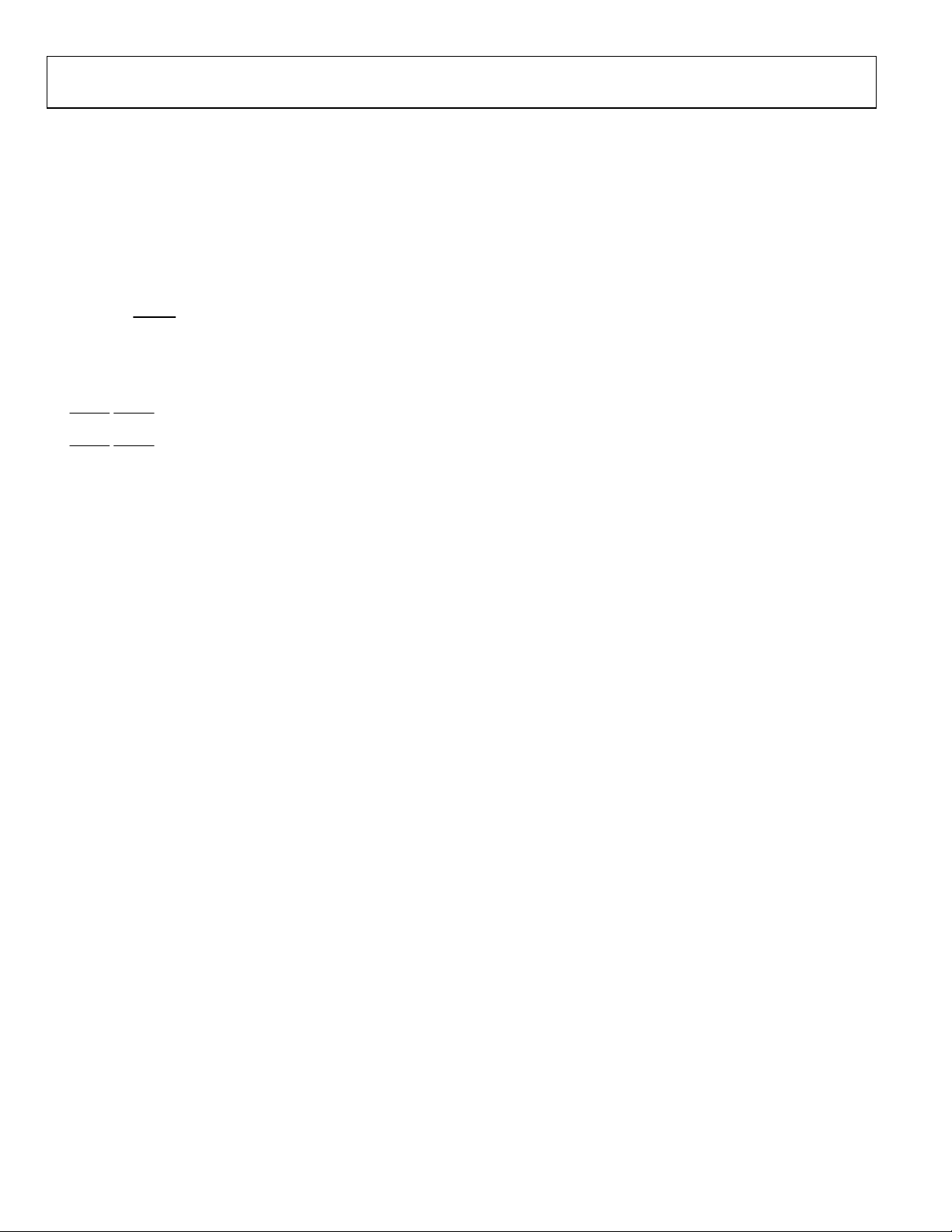

CLOCK AND RESET SPECIFICATIONS

Table 3.

Parameter Description Min Typ Max Unit

t

MCLK

t

MCLK Width Low 6 ns

MCLKL

t

MCLK Width High 6 ns

MCLKH

t

VCLK

t

VCLKL

t

VCLKH

t

RST

1

For a definition of MCLK, see the section. PLL

MCLK Period 13.3 100 ns

VCLK Period 13.4 50 ns

VCLK Width Low 5 ns

VCLK Width High 5 ns

RESET Width Low

MCLK

t

MCLKL

t

VCLKL

t

MCLK

t

VCLK

t

MCLKH

t

VCLKH

5 MCLK cycles

1

VCLK

Figure 2. Input C lock

04723-010

Rev. B | Page 5 of 40

ADV202

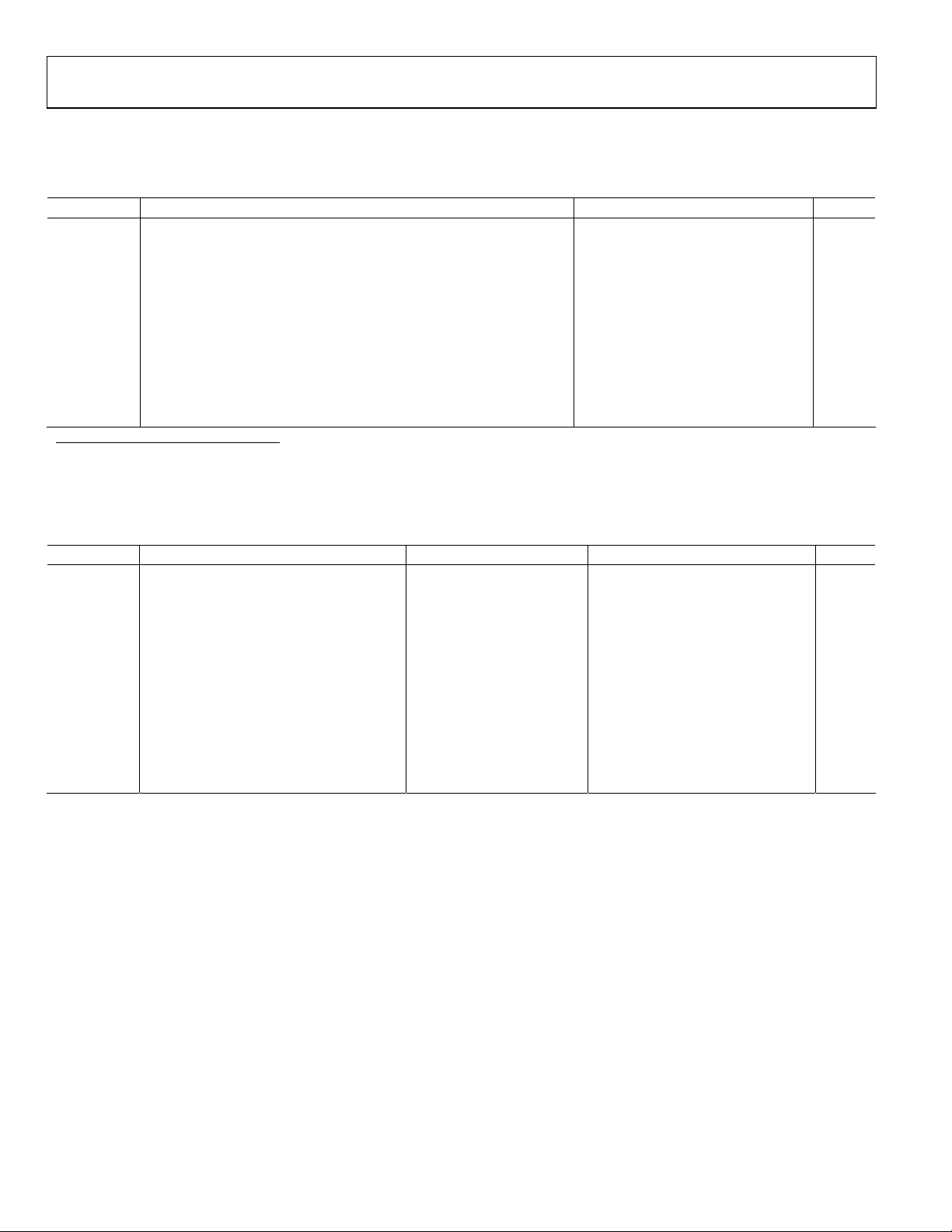

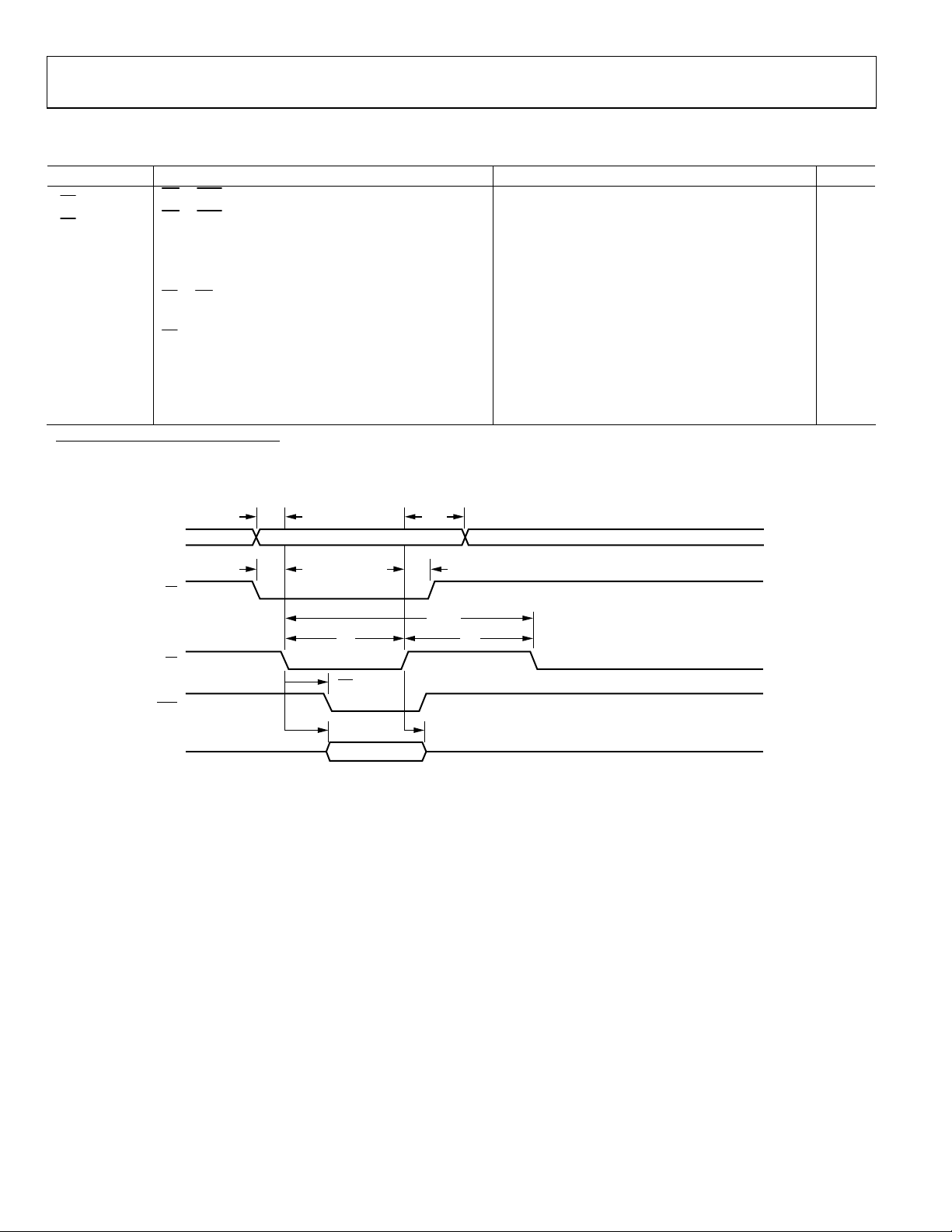

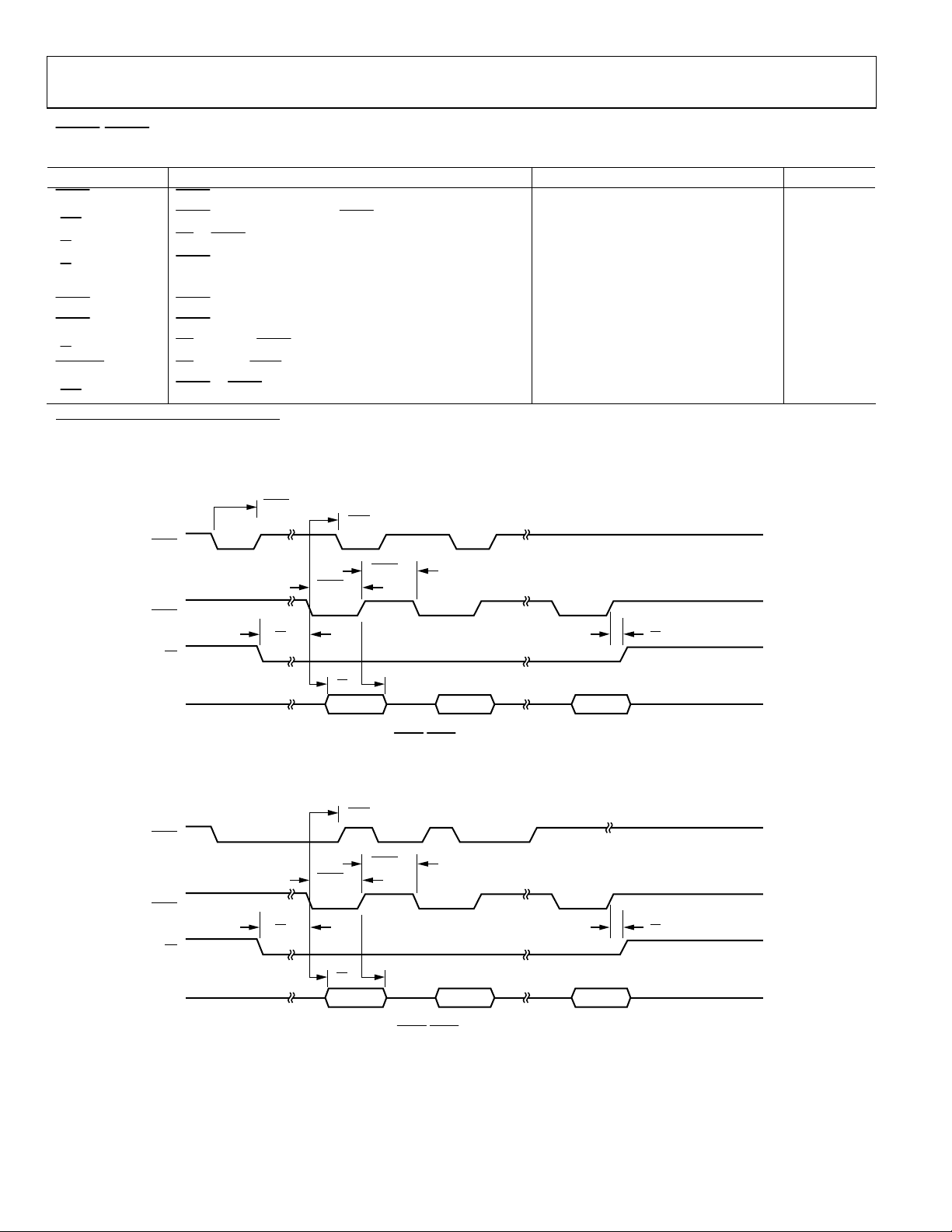

A

NORMAL HOST MODE—READ OPERATION

Table 4.

Parameter Description Min Typ Max Unit

t

[dir]

ACK

t

[indir]

ACK

t

[dir] Read Access Time, Direct Registers 5 ns 1.5 × JCLK + 7.0 ns

DRD

t

[indir] Read Access Time, Indirect Registers 10.5 × JCLK 15.5 × JCLK + 7.0 ns

DRD

t

HZRD

t

SC

RD to ACK, Direct Registers and FIFO Accesses

RD to ACK, Indirect Registers

Data Hold 2 8.5 ns

CS to RD Setup

tSA Address Setup 2 ns

tHC

t

HA

CS Hold

Address Hold 2 ns

tRH Read Inactive Pulse Width 2.5 JCLK

tRL Read Active Pulse Width 2.5 JCLK

t

Read Cycle Time, Direct Registers 5.0 JCLK

RCYC

1

For a definition of JCLK, see the section. PLL

5 ns 1.5 × JCLK + 7.0 ns

10.5 × JCLK 15.5 × JCLK + 7.0 ns

0 ns

0 ns

1

ADDR

ACK

HDAT

CS

RD

t

SA

t

SC

t

RL

t

ACK

t

DRD

VALID

t

HA

t

HC

t

RCYC

t

RH

t

HZRD

04723-011

Figure 3. Normal Host Mode—Read Operation

Rev. B | Page 6 of 40

ADV202

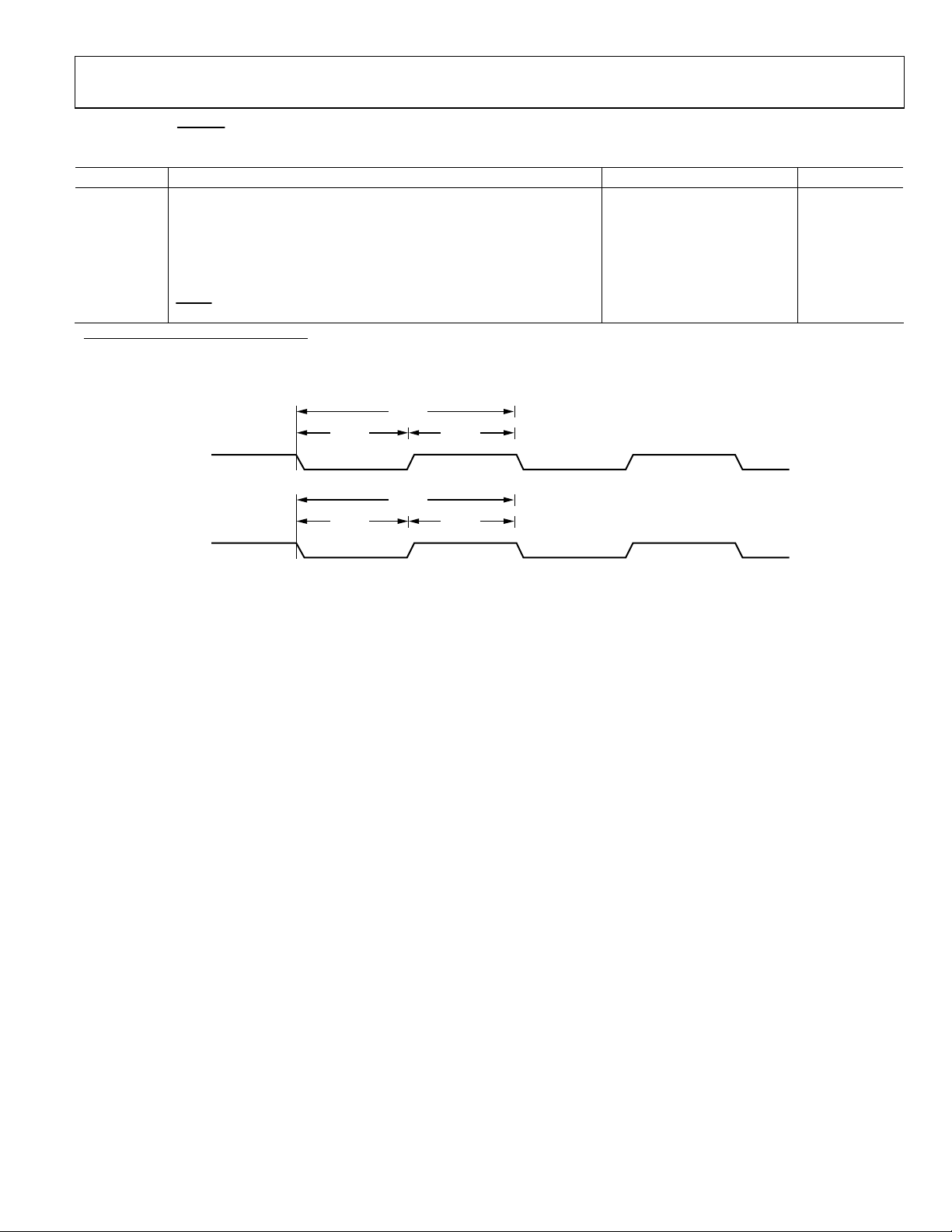

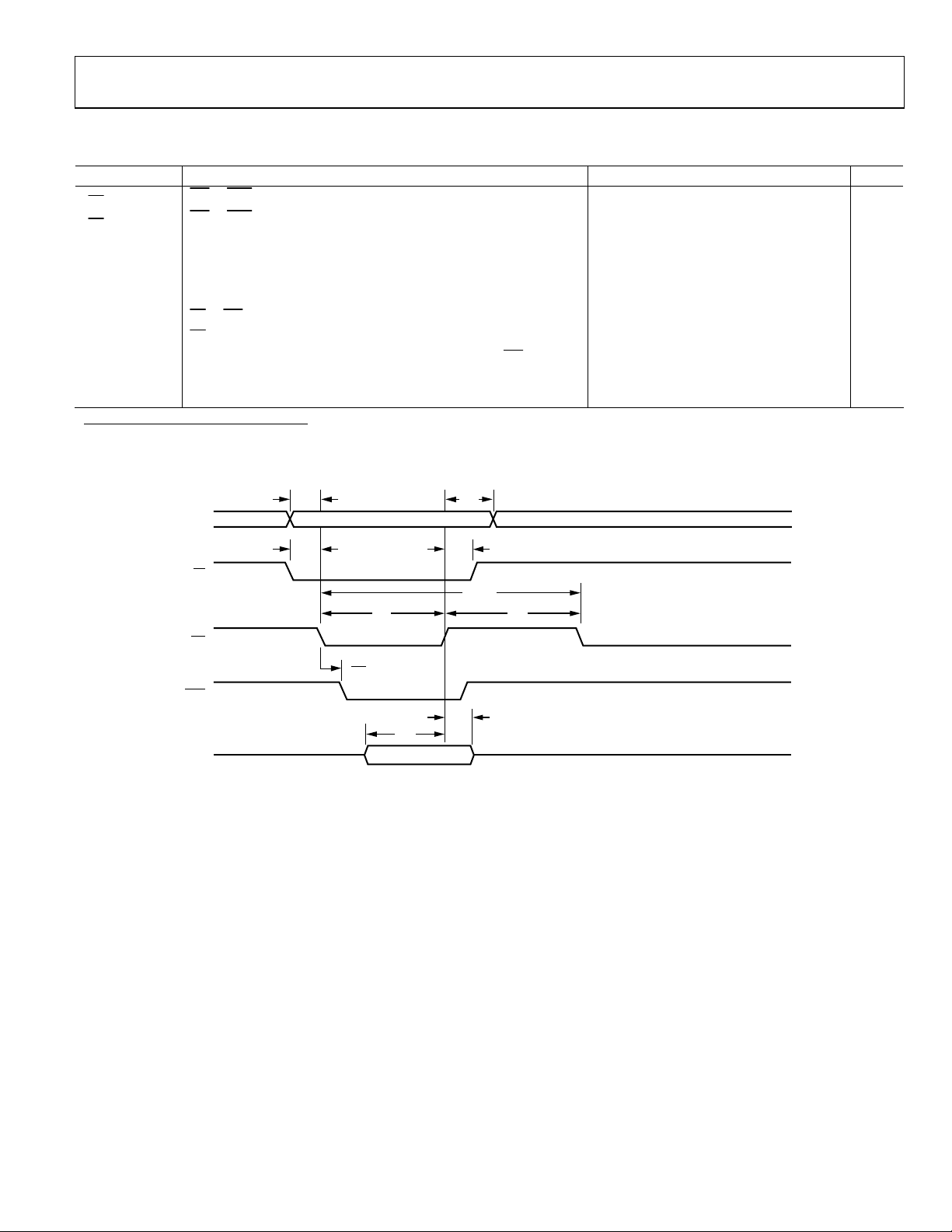

A

NORMAL HOST MODE—WRITE OPERATION

Table 5.

Parameter Description Min Typ Max Unit

t

(Direct)

ACK

t

(Indirect)

ACK

WE to ACK, Direct Registers and FIFO Accesses

WE to ACK, Indirect Registers

tSD Data Setup 3.0 ns

tHD Data Hold 1.5 ns

tSA Address Setup 2 ns

t

HA

tSC

tHC

t

WH

Address Hold 2 ns

CS to WE Setup

CS Hold

Write Inactive Pulse Width (Minimum Time until Next WE Pulse)

tWL Write Active Pulse Width 2.5 JCLK

t

WCYC

Write Cycle Time 5 JCLK

1

For a definition of JCLK, see the section. PLL

5 1.5 × JCLK + 7.0 ns ns

5 2.5 × JCLK + 7.0 ns ns

0 ns

0 ns

2.5 JCLK

1

ADDR

ACK

HDAT

CS

WE

t

SA

t

SC

t

WL

t

ACK

t

SD

VALID

t

HA

t

HC

t

WCYC

t

WH

t

HD

04723-012

Figure 4. Normal Host Mode—Write Operation

Rev. B | Page 7 of 40

ADV202

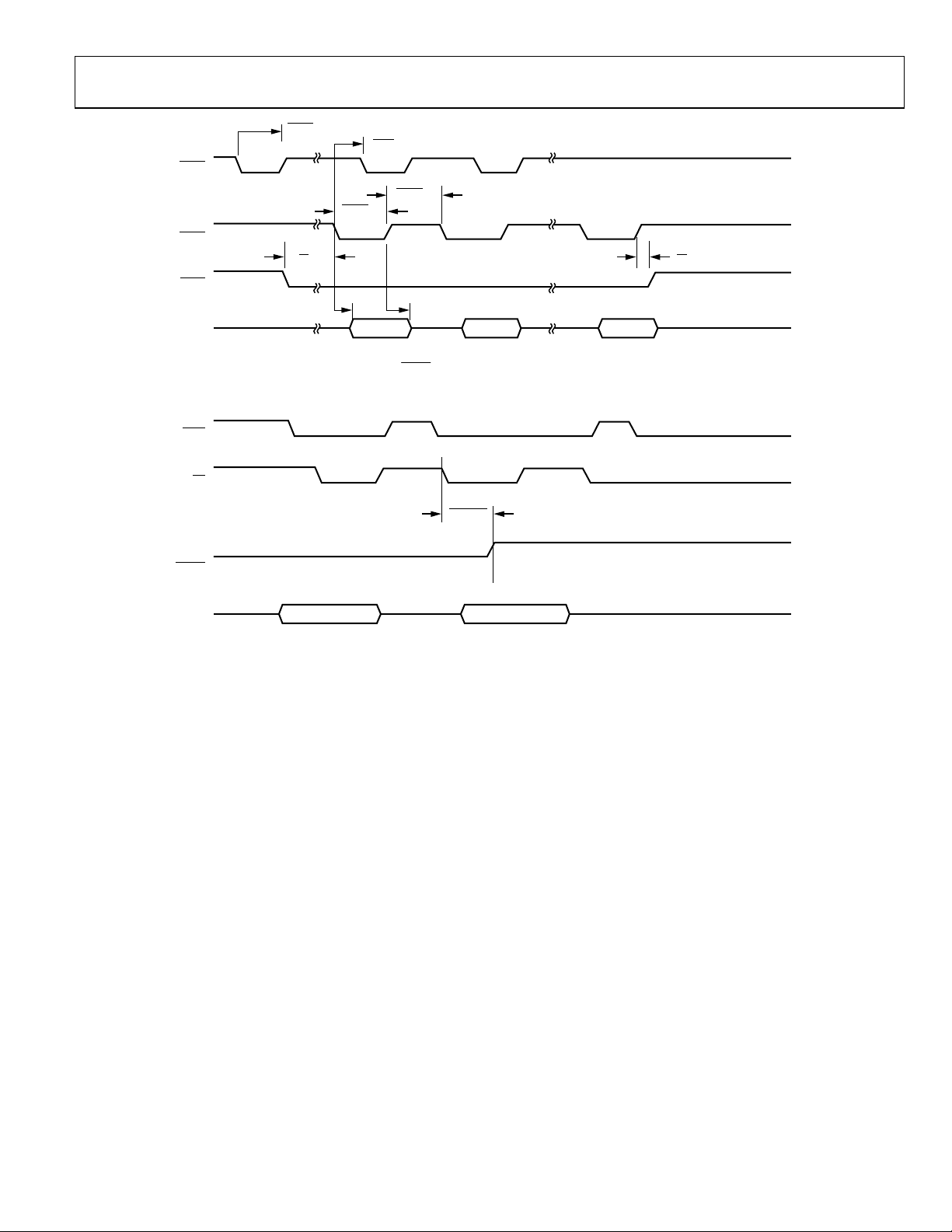

A

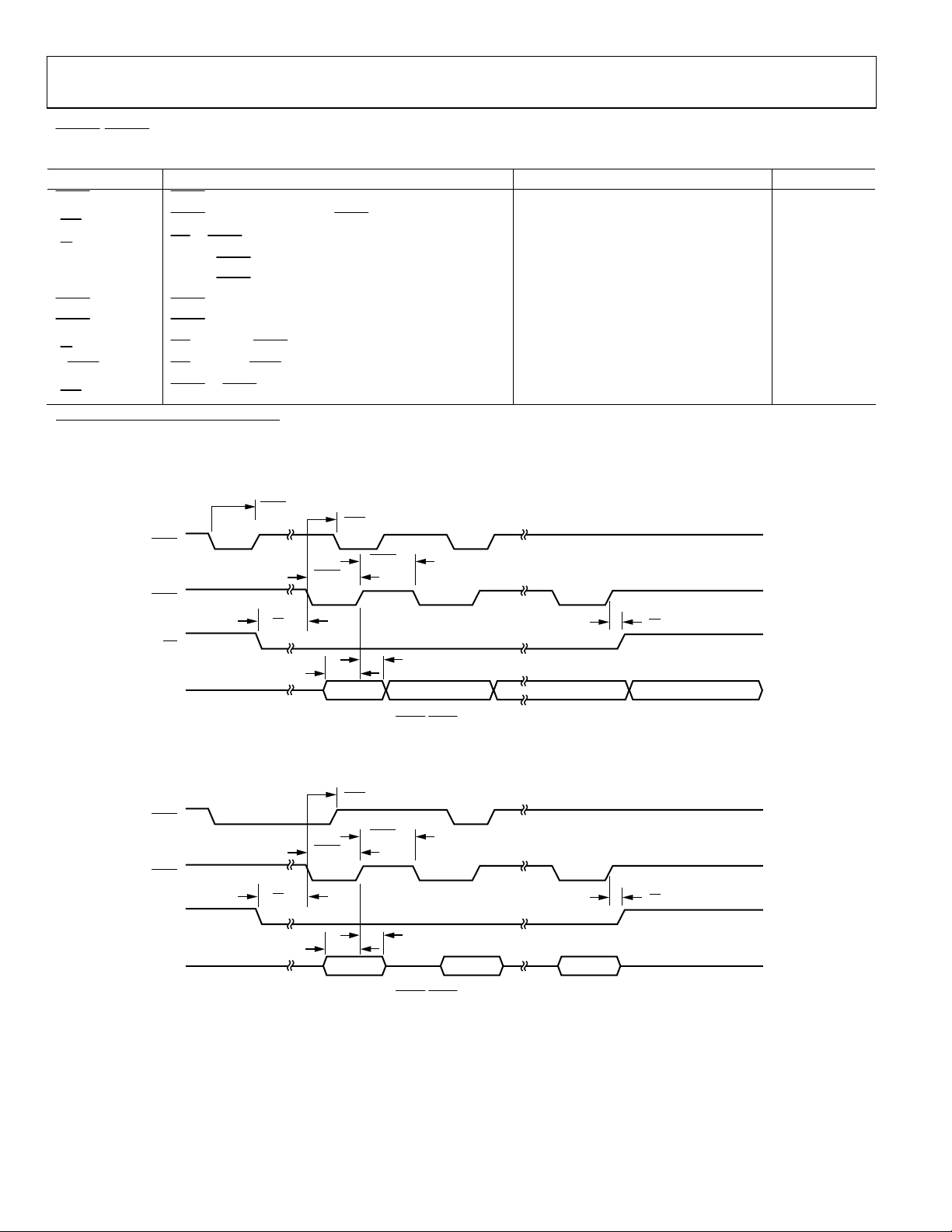

A

/

DREQ

Table 6.

Parameter Description Min Typ Max Unit

DREQ

PULSE1

t

DREQ

t

SU

WE

t

SU

tHD

DACK

LO

DACK

HI

t

HD

WE

WFSRQ WE Assert to FSRQ Deassert (FIFO Full)

t

RTN

DREQ

1

Applies to assigned DMA channel, if EDMOD0 or EDMOD1 <14:11> is programmed to a value that is not 0. Pulse width depends on the value programmed.

2

For a definition of JCLK, see the PLL section.

DMA MODE—SINGLE FIFO WRITE OPERATION

DACK

DREQ Pulse Width

DACK Assert to Subsequent DREQ Delay

WE to DACK Setup

Data to DACK Deassert Setup

Data to

DACK Deassert Hold

DACK Assert Pulse Width

DACK Deassert Pulse Width

WE Hold after DACK Deassert

DACK to DREQ Deassert (DR × PULS = 0)

DREQ

DREQ

DACK

HDAT

WE

PULSE

t

WESU

Figure 5. Single Write for

t

DREQ

DACK

DACK

LO

t

SU

HI

t

HD

DREQ/DACK

(EDMOD0/EDMOD1 <14:11> NOT Programmed to a Value of 0000)

1 15 JCLK cycles

2.5 3.5 × JCLK + 7.5 ns JCLK cycles

0 ns

2 ns

2 ns

2 JCLK cycles

2 JCLK cycles

0 ns

1.5 2.5 × JCLK + 7.5 ns JCLK cycles

2.5 3.5 × JCLK + 7.5 ns JCLK cycles

DMA Mode for Assigned DMA Channel

t

WEHD

3210

04723-013

2

t

DREQRTN

DREQ

DACK

HI

t

HD

0 1 2

DREQ/DACK

DMA Mode for Assigned DMA Channel

t

WEHD

04723-014

DACK

HDAT

WE

DACK

LO

t

WESU

t

SU

Figure 6. Single Write for

(EDMOD0/EDMOD1 <14:11> Programmed to a Value of 0000)

Rev. B | Page 8 of 40

ADV202

A

DREQ

DREQ

DACK

WEFB

HDAT

PULSE

t

WESU

Figure 7. Fly-By DMA Mode —Single Write Cycle (

t

DREQ

DACK

DACK

LO

t

SU

HI

t

HD

0 1 2

DREQ

t

WEHD

Pulse Width Is Programmable)

04723-015

FSC0

WE

WFSRQ

FSRQ0

HDATA

FIFO NOT FULL

0 1 2

Figure 8. DCS DMA Mode—Single Write Access (Rev. 0.1 and Higher)

FIFO FULL

NOT WRITTEN TO FIFO

04723-016

Rev. B | Page 9 of 40

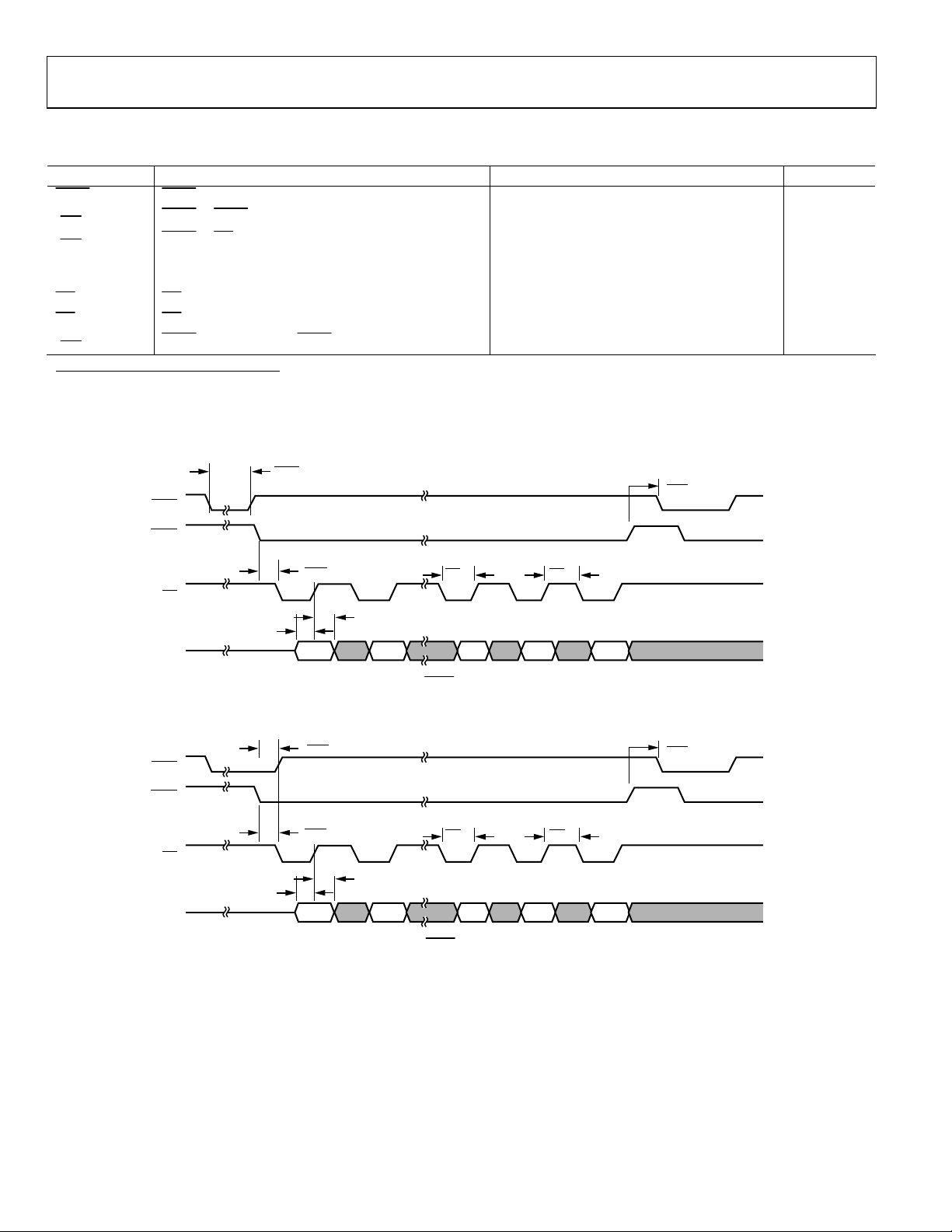

ADV202

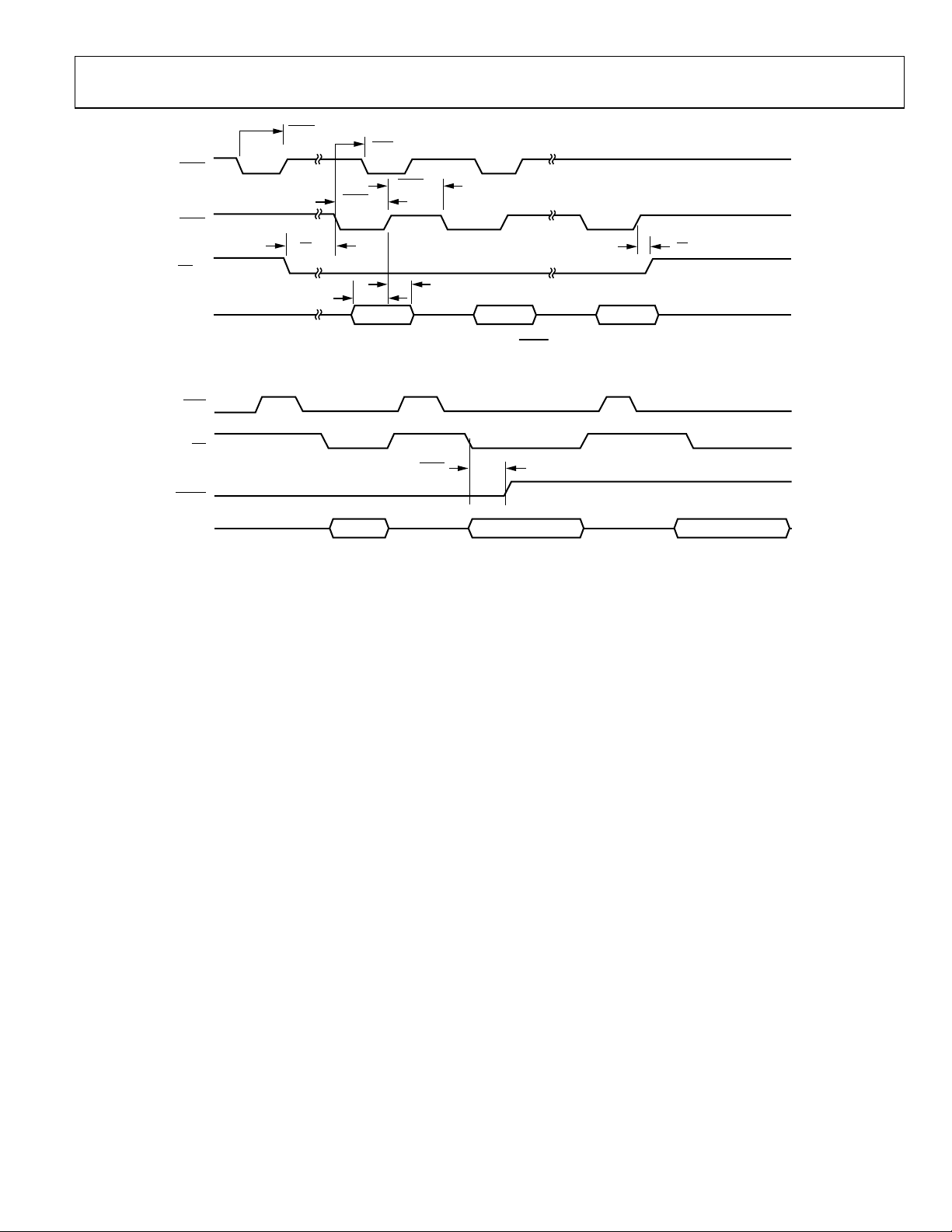

A

A

DREQ/DACK DMA MODE—SINGLE FIFO READ OPERATION

Table 7.

Parameter Description Min Typ Max Unit

DREQ

t

DREQ

t

RD

tRD

DREQ Pulse Width

PULSE

DACK Assert to Subsequent DREQ Delay

SU

RD to DACK Setup

DACK to Data Valid

tHD Data Hold 1.5 ns

DACK

DACK

t

HD

RD

LO

HI

DACK Assert Pulse Width

DACK Deassert Pulse Width

RD Hold after DACK Deassert

RDFSRQ RD Assert to FSRQ Deassert (FIFO Empty)

t

DREQ

RTN

DACK to DREQ Deassert (DR × PULS = 0)

1

Applies to assigned DMA channel, if EDMOD0 or EDMOD1 <14:11> is programmed to a nonzero value.

2

For a definition of JCLK, see the section. PLL

DREQ

DREQ

1

PULSE

DACK

t

DREQ

LO

DACK

1 15 JCLK cycles

2.5 3.5 × JCLK + 7.5 ns JCLK cycles

0 ns

2.5 11 ns

2 JCLK cycles

2 JCLK cycles

0 ns

1.5

2.5

HI

2.5 × JCLK + 7.5 ns

3.5 × JCLK + 7.5 ns

JCLK cycles

JCLK cycles

2

DACK

t

RDHD

04723-018

HDAT

RD

t

RDSU

t

RD

0 1 2

Figure 9. Single Read for

t

HD

DREQ/DACK

DMA Mode for Assigned DMA Channel

(EDMOD0/EDMOD1 <14:11> NOT Programmed to a Value of 0000)

t

DREQRTN

DREQ

DACK

HI

t

HD

0 1 2

DREQ/DACK

DMA Mode for Assigned DMA Channel

t

RDHD

04723-019

DACK

HDAT

RD

DACK

LO

t

RDSU

t

RD

Figure 10. Single Read for

(EDMOD0/EDMOD1 <14:11> Programmed to a Value of 0000)

Rev. B | Page 10 of 40

ADV202

A

A

DREQ

DACK

RDFB

HDAT

DREQ

t

RDSU

PULSE

t

DREQ

DACK

DACK

LO

t

RD

HI

t

HD

0 1 2

t

RDHD

04723-020

Figure 11. Fly-By DMA Mode—Single Read Cycle

DREQ

Pulse Width Is Programmable)

(

FCS0

RD

RDFSRQ

FIFO NOT EMPTY

FSRQ0

FIFO EMPTY

HDAT

0 1

04723-021

Figure 12. DCS DMA Mode—Single Read Access (Rev. 0.1 and Higher)

Rev. B | Page 11 of 40

ADV202

A

A

EXTERNAL DMA MODE—FIFO WRITE, BURST MODE

Table 8.

Parameter Desription Min Typ Max Unit

DREQ

t

DREQ

t

DACK

DREQ Pulse Width

PULSE

RTN

SU

DACK to DREQ Deassert (DR × Pulse = 0)

DACK to WE Setup

tSU Data Setup 2.5 ns

tHD Data Hold 2 ns

WE

WE

t

DREQ

LO

HI

WAIT

WE Assert Pulse Width

WE Deassert Pulse Width

DACK Deassert to Next DREQ

1

Applies to assigned DMA channel, if EDMOD0 or EDMOD1 <14:11> is programmed to a value that is not 0. Pulse width depends on the value programmed.

2

For a definition of JCLK, see the section. PLL

3

If sufficient space is available in FIFO.

DREQ

DACK

1

DREQ

PULSE

1 15 JCLK cycles

2.5 3.5 × JCLK + 7.5 ns JCLK cycles

0 ns

1.5 JCLK cycles

1.5 JCLK cycles

2.5 4.5 × JCLK + 7.5 ns

t

DREQWAIT

3

JCLK cycles

2

HDAT

DREQ

DACK

HDAT

WE

WE

t

DACKSU

t

HD

t

SU

0 1 13 14 15

Figure 13. Burst Write Cycle for

WE

LO

DREQ

/DMA Mode for Assigned DMA Channel

WE

HI

(EDMOD0/EDMOD1 <14:11> NOT Programmed to a Value of 0000)

t

DREQRTN

t

DACKSU

t

HD

t

SU

0 1 13 14 15

Figure 14. Burst Write Cycle for

WE

LO

DREQ

/DMA Mode for Assigned DMA Channel

WE

HI

(EDMOD0/EDMOD1 <14:11> Programmed to a Value of 0000)

t

DREQWAIT

04723-022

04723-023

Rev. B | Page 12 of 40

Loading...

Loading...