Analog Devices ADuM6132 Datasheet

Isolated Half-Bridge Driver

with Integrated Isolated High-Side Supply

PRELIMINARY TECHNICAL DATA

FEATURES

Integrated Isolated High Side Supply

250mW Isolated DC/DC converter

200mA Output Sink Current, 200mA Output Source Current

High common-mode transient immunity: > 25 kV/μs

High temperature operation: 105°C

Wide body SOIC 16-lead package

Safety and regulatory approvals (pending)

UL recognition

3750 V rms for 1 minute per UL 1577

CSA component acceptance notice #5A

CSA/IEC 60950-1, 400 V

VDE certificate of conformity

DIN V VDE 0884-10 (VDE V 0884-10):2006-12

= 560 V peak

V

IORM

APPLICATIONS

MOSFET/IGBT Gate Drive

Motor Drives

Solar Panel Inverters

Power Supplies

RMS

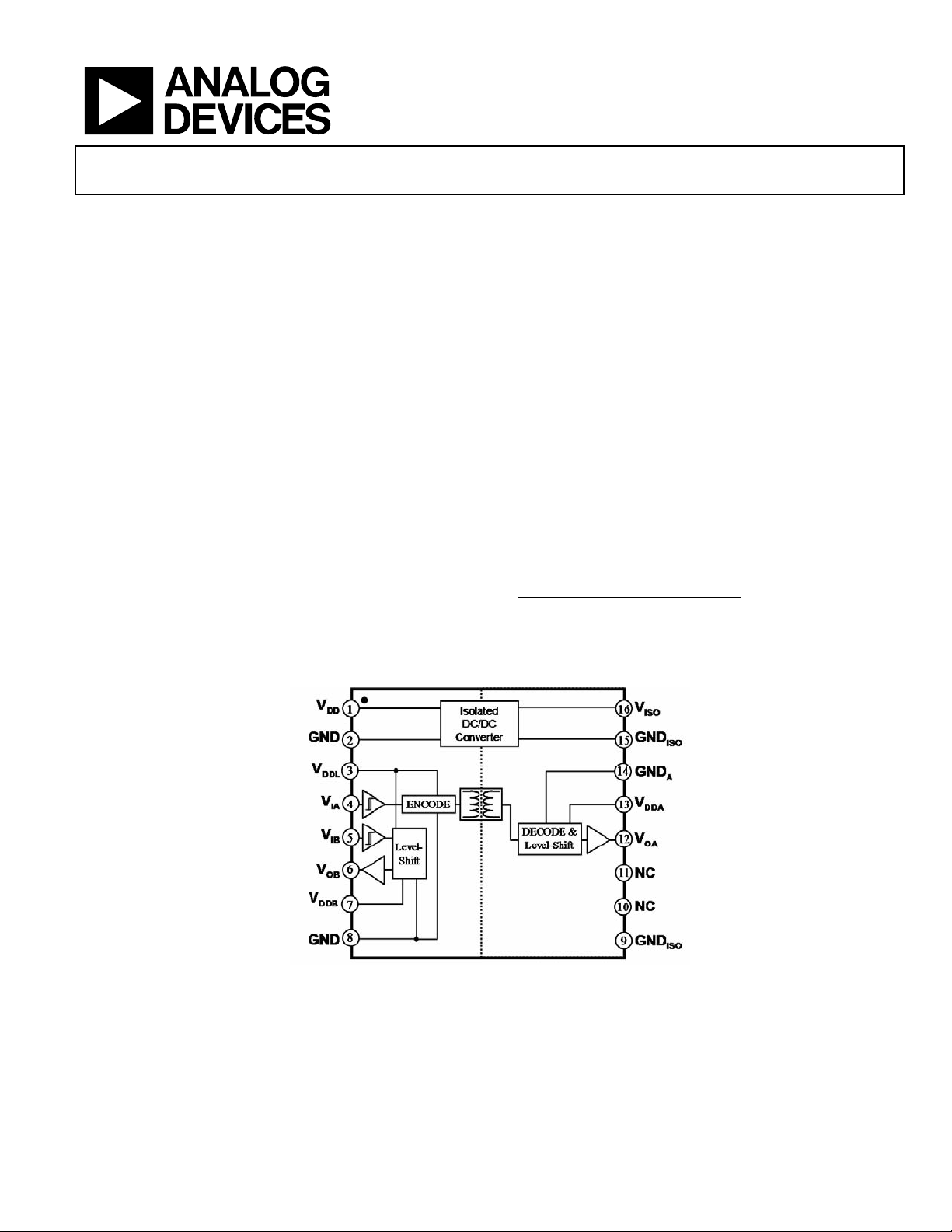

FUNCTIONAL BLOCK DIAGRAM

ADuM6132

GENERAL DESCRIPTION

The ADuM61321 is an isolated half-bridge gate driver that employs

Analog Devices’ iCoupler® technology to provide an isolated highside driver with an integrated 300 mW high-side supply. This

supply, provided by an internal isolated DC/DC converter powers

not only the ADuM6132’s high-side output but also any external

buffer circuitry that would commonly be used with the

ADuM6132.

difficulties associated with external supply configurations such

as a bootstrap circuitry.

channel and high side power from the control and low side

interface circuitry. Care has been taken to ensure close matching

between the high and low side driver timing characteristics,

reduces the need for dead time margin.

In comparison to gate drivers employing high voltage level

translation methodologies, the ADuM6132 offers the benefit of

true, galvanic isolation. The differential voltage between high and

low side channels can be as high as 1131V in some configurations

(see Table 7).

1

Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075 329. Other patents

pending.

This eliminates the cost, space, and performance

The architecture isolates the high side

Figure 1. ADuM6132 Functional Block Diagram

Rev. PrG March 19, 2008

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Anal og Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2008 Analog Devices, Inc. All rights reserved.

ADuM6132 PRELIMINARY TECHNICAL DATA

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

All voltages are relative to their respective ground. 4.5 ≤ VDD = V

apply over the entire recommended operating range, unless otherwise noted. All typical specifications are at T

5.0V, V

= 15 V, V

DDB

DDA

= V

ISO

.

Table 1.

Parameter Symbol Min Typ Max Unit Test Conditions

DC SPECIFICATIONS

Isolated Power Supply

Input Current, Quiescent

I

DD

(Q)

Input Current, Loaded IDD 350 mA I

Maximum Output Current1 I

Output Voltage V

22 mA 12.5 < V

ISO(max)

12.5 15 17 V 0 < I

ISO

Logic Supply

Input Current I

1.8 3.0 mA

DDL

Output Supplies, Channel A or Channel B2

Supply Current, Quiescent

Supply Current, fIN=20kHz

Supply Current, fIN=100kHz

Supply Current, fIN=1000kHz

I

DDA

(Q)

I

DDA(20)

I

DDA(100)

I

DDA(1000)

, I

,

DDB

I

DDB(20)

I

DDB(100)

,

I

DDB(1000)

,

(Q)

Logic Inputs, Channel A or Channel B

Input Current IIA, I

Logic High Input Voltage V

Logic Low Input Voltage V

IB

, V

0.7 xV

IAH

IBH

, V

IAL

IBL

Outputs, Channel A or Channel B

Channel A High Level Output Voltage V

Channel B High Level Output Voltage V

Low Level Output Voltages V

High Level Output Current, Peak3 I

Low Level Output Current, Peak3 I

Undervoltage Lockout, V

DDA

or V

Supply

DDB

Positive going threshold V

Negative going threshold V

Hysteresis V

Undervoltage Lockout, V

Supply

DDL

Positive going threshold V

Negative going threshold V

Hysteresis V

V

OAH

V

OBH

0.1 V I

OAL,VOBL

, I

200 mA

OAH

OBH

, I

200 mA

OAL

OBL

DDAUV+, VDDBUV+

DDAUV-, VDDBUV-

, V

DDBUVH

DDBUVH

DDLUV+

DDLUV-

DDLUVH

SWITCHING SPECIFICATIONS

Minimum Pulse Width4 PW 50 ns CL = 200 pF

Maximum Switching Frequency5 f

Propagation Delay

6

1000 KHz CL = 200 pF

IN

t

, t

40 60 100 ns CL = 200 pF

PHL

PLH

Change versus temperature 100

Pulse-Width Distortion, |t

Channel-to-Channel Matching, Rising or

Falling Matching Edge Polarity

Channel-to-Channel Matching, Rising vs.

Falling Opposite Edge Polarity

| PWD 10 ns CL = 200 pF

PLH−tPHL

t

20 ns CL = 200 pF

7

8

M2

20 ns CL = 200 pF

t

M1

Part-to-Part Matching9 60 ns CL = 200 pF

Output Rise Time (10%−90%) tR 15 ns CL = 200 pF

Output Fall Time (10%−90%) tF 15 ns CL = 200 pF

≤ 5.5 V, 12.5 ≤ V

DDL

≤ 17.0 V, V

DDB

250 mA I

DDA

= V

. All min/max specifications

ISO

= 25°C, VDD = V

A

=0, DC signal inputs

ISO

= I

ISO

ISO(max,)

ISO

< 22

ISO

DDL

< 17.0

1.0 2 mA

1.1 2.1 mA CL = 200 pF

1.3 2.3 mA CL = 200 pF

4.5 5.5 mA CL = 200 pF

−10 0.01 10 μA 0 ≤ VIA, VIB ≤ 5.5V

DDL

–0.1

DDA

–0.1 V I

DDB

0.3 x V

V I

V

V

DDL

= -1 mA

OAH

= -1 mA

OBH

, I

OAL

= +1 mA

OBL

11.0 11.7 12.3 V

10.0 10.7 11.2 V

0.8 1.0 1.2 V

3.5 4.2 V

3.0 3.7 V

0.3 V

ps/°

C

=

Rev. PrG| Page 2 of 12

PRELIMINARY TECHNICAL DATA

ADuM6132

1

The maximum output current is the maximum isolated supply current that the ADuM6132 can provide. This current supports external loads as well as the needs of

the ADuM6132 Channel A output circuitry. This is achieved via external connection of V

external loads is the ADuM6132 output current I

2

I

is supplied by the output of the integrated isolated dc/dc power as described in Footnote 1 above. I

DDA

Figure 3.

3

Duration less than 1 second. Average output current must conform to the limit shown under the Absolute Maximum Ratings.

4

The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed. Operation below the minimum pulse width is not

recommended.

5

The maximum switching frequency is the maximum signal frequency at which the specified timing parameters are guaranteed. Operation beyond the maximum

frequency is not recommended since high switching rates can cause droop in the output supply voltage.

6

t

propagation delay is measured from the 50% level of the falling edge of the VIx signal to the 50% level of the falling edge of the VOx signal. t

PHL

measured from the 50% level of the rising edge of the VIx signal to the 50% level of the rising edge of the VOx signal.

7

“Channel-to-channel matching, rising or falling matching edge polarity” is the magnitude of the propagation delay difference between two channels of the same part

when both inputs are either both rising or falling edges. The loads on each channel are equal.

8

“Channel-to-channel matching, rising vs. falling opposite edge polarity” is the magnitude of the propagation delay difference between two channels of the same part

when one input is a rising edge and one input is a falling edge. The loads on each channel are equal.

9

Part-to-part matching is the magnitude of the propagation delay difference between the same channels of two different parts. This includes rising vs. rising, falling vs.

falling, or rising vs. falling edges. The supply voltages, temperatures, and loads of each part are equal.

less the Channel A supply current I

ISO

DDA

to V

and GND

ISO

DDA

.

to GNDA (Figure 3). The net current available to power

ISO

is supplied by external power connection to V

DDB

propagation delay is

PLH

pin. See

DDB

Rev. PrG| Page 3 of 12

ADuM6132 PRELIMINARY TECHNICAL DATA

PACKAGE CHARACTERISTICS

Table 2.

Parameter Symbol Min Typ Max Unit Test Conditions

Resistance (Input Side- High Side Output)1 R

Capacitance (Input to High Side Output)1 C

Input Capacitance CI 4.0 pF

IC Junction-to-Ambient Thermal Resistance θJA 45 °C/W 4-layer PC board

1

The device is considered a two-terminal device: Pins 1-8 are shorted together, and Pins 9-16 are shorted together.

REGULATORY INFORMATION

The ADuM6132 will be approved by the organizations listed in Table 3.

Table 3.

UL (pending) CSA (Pending) VDE (Pending)

Recognized under 1577

component recognition program

Double/reinforced insulation,

3750 V rms isolation voltage

Approved under CSA Component

1

Acceptance Notice #5A

Basic insulation per CSA 60950-1-03 and IEC

60950-1, 800 V rms (1131 V peak) maximum

working voltage

Reinforced insulation per CSA 60950-1-03 and

IEC 60950-1, 400 V rms maximum working voltage

File E214100 File 205078 File 2471900-4880-0001

1

In accordance with UL1577, each ADuM6132 is proof tested by applying an insulation test voltage ≥ 4500 V rms for 1 second (current leakage detection limit = 10 μA).

2

In accordance with DIN V VDE V 0884-10, each ADuM6132 is proof tested by applying an insulation test voltage ≥1050 V peak for 1 sec (partial discharge detection

limit = 5 pC). The * marking branded on the component designates DIN V VDE V 0884-10 approval.

INSULATION AND SAFETY-RELATED SPECIFICATIONS

Table 4.

Parameter Symbol Value Unit Conditions

Rated Dielectric Insulation Voltage 3750 V rms 1 minute duration

Minimum External Air Gap (Clearance) L(I01) 8.0 min mm Measured from input terminals to output terminals, shortest

Minimum External Tracking (Creepage) L(I02) 8.0 min mm

Minimum Internal Gap (Internal

Clearance)

Tracking Resistance (Comparative

Tracking Index)

Isolation Group IIIa Material Group (DIN VDE 0110, 1/89, Table 1)

0.017 min mm Insulation distance through insulation

CTI >175 V DIN IEC 112/VDE 0303 Part 1

1012 Ω

I-O

2.0 pF

I-O

Certified according to DIN V VDE V 0884-10

(VDE V 0884-10):2006-122

Reinforced insulation, 560 V peak

Complies with DIN EN 60747-5-2 (VDE 0884

Part 2): 2003-01, DIN EN 60950 (VDE 0805):

2001-12; EN 60950: 2000, DIN V VDE 0884-10

(VDE V 0884-10):2006-12

distance through air

Measured from input terminals to output terminals, shortest

distance path along body

Rev. PrG| Page 4 of 12

Loading...

Loading...