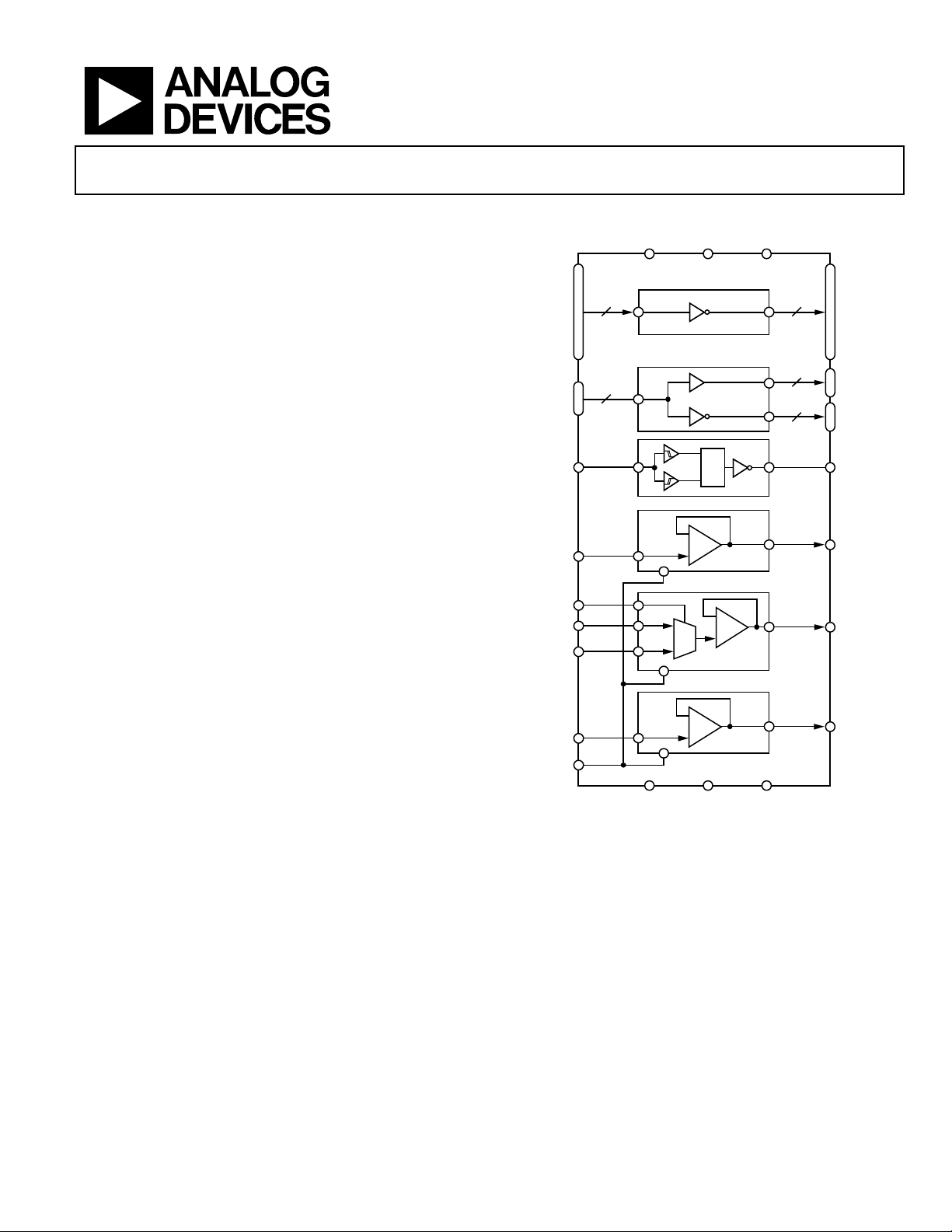

LCD Level Shifters with VCOM,

NRS Buffers, and High Voltage Edge Detector

FEATURES

Complete suite of level shifters

Eight inverting and three complementary level shifters for

LCD timing

High voltage edge detector

Integrated low offset buffer for VCOM drives high capacitive

loads

MUXed input, low offset buffer for 2-level precharge drives

high capacitive loads

High current buffer for precharge provides high current

drive into large capacitive loads

Low power dissipation: 576 mW

Available in 48-lead 7 mm × 7 mm LFCSP E-pad

PRODUCT DESCRIPTION

The ADSY8401 provides fast, 3 V to 15 V level shifters for LCD

panel timing signals. An integrated low offset analog buffer is

capable of driving the high capacitive loads. A 2:1 MUX input,

low offset buffer simplifies application of 2-level precharge

signals. A high current buffer provides high slew rates for large

capacitive loads.

The ADSY8401 is fabricated on ADI’s fast, 26 V XFHV process,

providing fast input logic, high voltage level shifters, and

precision drive amplifiers on the same chip.

DI1

DI2

DI3

DI4

DI5

DI6

DI7

DI8

DI9

DI10

DI11

DTCTI

AMPI

SEL

MUXA

MUXB

ADSY8401

FUNCTIONAL BLOCK DIAGRAM

DVCC AVCCL AVCC

ADSY8401

8

3

R

S

+1

+1

8

3

3

DO1

DO2

DO3

DO4

DO5

DO6

DO7

DO8

DO9T

DO10T

DO11T

DO9C

DO10C

DO11C

DTCTO

AMPO

MUXO

The ADSY8401 dissipates 576 mW nominal static power.

The ADSY8401 is offered in a 48-lead 7 mm × 7 mm LFCSP

E-pad package and operates over the commercial temperature

range of 0°C to 85°C.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Anal og Devices. Trademarks and

registered trademarks are the property of their respective owners.

BFRI

GSW

DGND AGNDL AGND

+1

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

BFRO

04758-0-001

ADSY8401

TABLE OF CONTENTS

Specifications..................................................................................... 3

Applications..................................................................................... 11

Absolute Maximum Ratings............................................................ 6

Maximum Power Dissipation ..................................................... 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Amplifier Applications..................................................................... 8

Amp Section as VCOM Buffer ................................................... 8

MUX and BFR Sections as NRS Buffer ..................................... 8

MUX Section as VCOM Buffer .................................................. 8

Level Shifter Characteristics............................................................ 9

Level Shifter Timing Characteristics ......................................... 9

Inverting and Complementary Level Shifter Timing.............. 9

Level Shifting Edge Detector Timing Characteristics ........... 10

Level Shifting Edge Detector Timing ...................................... 10

REVISION HISTORY

AMP Channel ............................................................................. 11

MUX Channel............................................................................. 11

Driving NRS................................................................................ 11

BFR Channel ............................................................................... 11

Grounded Output Mode ........................................................... 11

Driving VCOM........................................................................... 11

PCB Design for Optimized Thermal Performance ............... 13

Power Supply Sequencing ......................................................... 14

Layout Considerations............................................................... 14

Tot a l Po w er D is s ip a ti o n ............................................................. 14

Outline Dimensions....................................................................... 15

Ordering Guide .......................................................................... 15

7/04—Revision 0: Initial Version

Rev. 0 | Page 2 of 16

ADSY8401

SPECIFICATIONS

At 25°C, AVCC = AVCCL = 15.5 V, DVCC = 3.3 V, TA min = 0°C, TA max = 85°C, unless otherwise noted.

Table 1.

Parameter Conditions Min Typ Max Unit

Amp Section

INPUT/OUTPUT CHARACTERISTICS

Voltage Range

V

H

V

L

Output Voltage Grounded Mode GSW = LOW 45 mV

Input Current 100 nA

Output Current 20 mA

Output Offset Voltage VAMPI = 6 V, TA = 25°C 1.5 8 mV

Output Offset Voltage VAMPI = 6 V, TA min to TA max 11 mV

PSRR AVCC ± 10%, TA min to TA max 0.1 mV/V

Gain Error

OUTPUT DYNAMIC PERFORMANCE

−3 dB Bandwidth (Small Signal) VO = 0.25 V p-p 5.2 MHz

Slew Rate 13 V/µs

Settling Time to 0.5% TA min to TA max 0.5 1 µs

Overshoot 0.05 %

MUX Section

INPUT/OUTPUT CHARACTERISTICS

Voltage Range

V

H

V

L

Output Voltage Grounded Mode GSW = LOW 45 mV

Input Current

II MUXA, MUXB 100 nA

Output Current 20 mA

Output Offset Voltage VMUXA, B = 7.5 V, TA = 25°C 1.5 8 mV

Output Offset Voltage VMUXA, B = 7.5 V, TA min to TA max 11 mV

PSRR AVCC ± 10%, TA min to TA max 0.1 mV/V

Gain Error

SEL INPUT CHARACTERISTICS

IIH SEL 0.05 µA

IIL SEL −0.7 µA

VTH SEL 1.65 V

VIH SEL 2 V

VIL SEL 0.8 V

OUTPUT DYNAMIC PERFORMANCE VO = 5 V step, CL = 1 nF

−3 dB Bandwidth (Small Signal) VO = 0.25 V p-p 5.2 MHz

Slew Rate 13 V/µs

Settling Time to 0.5% TA min to TA max 0.5 1 µs

Overshoot 0.05 %

OUTPUT DYNAMIC PERFORMANCE VO = 5 V step, CL = 15 pF

−3 dB Bandwidth (Small Signal) VO = 0.25 V p-p 27 MHz

Slew Rate 13 V/µs

Settling Time to 0.5% TA min to TA max 0.4 0.7 µs

Overshoot

AVCC − V

H

1.5 2.5 V

VL − AGND 1.1 1.5 V

VAMPI = 3 V to 10 V, TA min to TA max

TA min to TA max, VO = 5 V step, CL = 1 nF

0.07 0.12 %

AVCC − V

H

1.5 2.5 V

VL − AGND 1.1 1.5 V

VMUXA, B 1.5 V to 12 V, TA min to TA max

0.07 0.12 %

0.1

%

Rev. 0 | Page 3 of 16

ADSY8401

Parameter Conditions Min Typ Max Unit

BFR Section

INPUT/OUTPUT CHARACTERISTICS

Voltage Range

V

H

V

L

Output Voltage Grounded Mode GSW = LOW 90 mV

Input Current 0.3 µA

Output Current 100 mA

Output Offset Voltage BFRI = 7.5 V, TA = 25°C 6 20 mV

Output Offset Voltage BFRI = 7.5 V, TA min to TA max 30 mV

PSRR, TA min to TA max AVCC ± 10% 1 mV/V

Gain Error, TA min to TA max BFRI = 1.5 V to 12 V 0.5 0.65 %

OUTPUT DYNAMIC PERFORMANCE VO = 6 V step, CL = 10 nF

−3 dB Bandwidth (Small Signal) VO = 0.25 V p-p 1.3 MHz

Slew Rate 12 V/µs

Settling Time to 0.5% TA min to TA max 0.7 1 µs

Overshoot 0.3 %

MUX and BFR Sections as NRS Buffer

Settling Time to 0.5% CL = 10 nF 0.9 1.5 µs

Level Shifter Section

LEVEL SHIFTER LOGIC INPUTS

C

IN

I

IH

I

IL

V

IH

V

IL

V

TH

LEVEL SHIFTER OUTPUTS

V

OH

V

OL

LEVEL SHIFTER DYNAMIC PERFORMANCE TA min to TA max

Output Rise, Fall Times, tr, tf 10% to 90%

DO1–DO8, DO9T–DO11T, DO9C–DO11C CL = 40 pF 20 30 ns

DO1–DO8 CL = 300 pF 130 150 ns

Propagation Delay times, t11, t12, t13, t

14

DO1–DO8, DO9T–DO11T, DO9C–DO11C CL = 40 pF 23 50 ns

DO1–DO8 CL = 300 pF 60 80 ns

Propagation Delay Skew, t15, t

16

DO1–DO8 2 ns

Propagation Delay Skew, t15, t16, t17, t

18

DO1–DO8, DO9T–DO11T, DO9C–DO11C 4 ns

AVCC − VH 1.5 2.5 V

VL − AGND 1.1 1.5 V

See Figure 4

3 pF

0.05 µA

−0.6 µA

2 V

0.8 V

1.65 V

AVCCL − 0.5 AVCCL − 0.25

V

0.25 0.5 V

CL = 40 pF

CL = 40 pF

Rev. 0 | Page 4 of 16

ADSY8401

Parameter Conditions Min Typ Max Unit

= 10 pF

Level Shifting Edge Detector Section

Input Low Voltage, V

Input High Voltage, V

IL

IH

Input Rising Edge Threshold Voltage, VTH LH AGND + 3 V

Input Falling Edge Threshold Voltage, VTH HL AVCC − 3 V

Output High Voltage, V

Output Low Voltage, V

Input Current High State, I

Input Current, I

IL

OH

OL

IH

Input Rising Edge Propagation Delay Time, t

Input Falling Edge Propagation Delay Time, t20 16.5 ns

t20 Variation with Temperature, ∆t20

Output Rise, Fall Time, t

r

Grounded-Mode Switch

GSW INPUT CHARACTERISTICS

C

IN

R

IN

I

IH

I

IL

V

IH

V

IL

V

TH

Power Supplies

Operating Range, DVCC 3 3.3 3.6 V

Quiescent Current, DVCC 20 25 mA

Operating Range, AVCC, AVCCL1, 2, 3 18 V

Quiescent Current, AVCCL1 12.5 15.5 mA

Quiescent Current, AVCCL2

Quiescent Current, AVCCL3

Quiescent Current, AVCCL2

Quiescent Current, AVCCL3

Quiescent Current, AVCC 10 12.8 mA

Operating Temperature

Ambient Temperature Range, T

A

C

L

AVCC − 1.5

V

DVCC − 0.5 DVCC − 0.25

AGND + 1.5

V

V

0.25 0.5 V

1.2 2.5 µA

15.5 ns

19

T

= 25°C to 85°C 2 ns

A

−

2.5

−

1.2 µA

10% to 90% 6 ns

3 pF

50 kΩ

0.6 µA

−70 µA

2 V

0.8 V

1.65 V

DI1 − DI11 ≤ V

DI1 − DI11 ≤ V

DI1 − DI11 ≥ V

DI1 − DI11 ≥ V

IL

IL

IH

IH

5.2 6.6 mA

5.2 6.6 mA

11.5 14.3 mA

11.5 14.3 mA

In still air 0 85 °C

Rev. 0 | Page 5 of 16

Loading...

Loading...