SHARC® Mel-100

SUMMARY

High performance 32-bit audio processor

Super Harvard Architecture Computer (SHARC)

4 independent buses for dual data, instruction, and

nonintrusive, zero-overhead I/O fetch on a single cycle

Code compatible with all other SHARC family DSPs

Single-instruction-multiple-data (SIMD) computational

architecture—two 32-bit IEEE floating-point computation units, each with a multiplier, ALU, shifter, and

register file

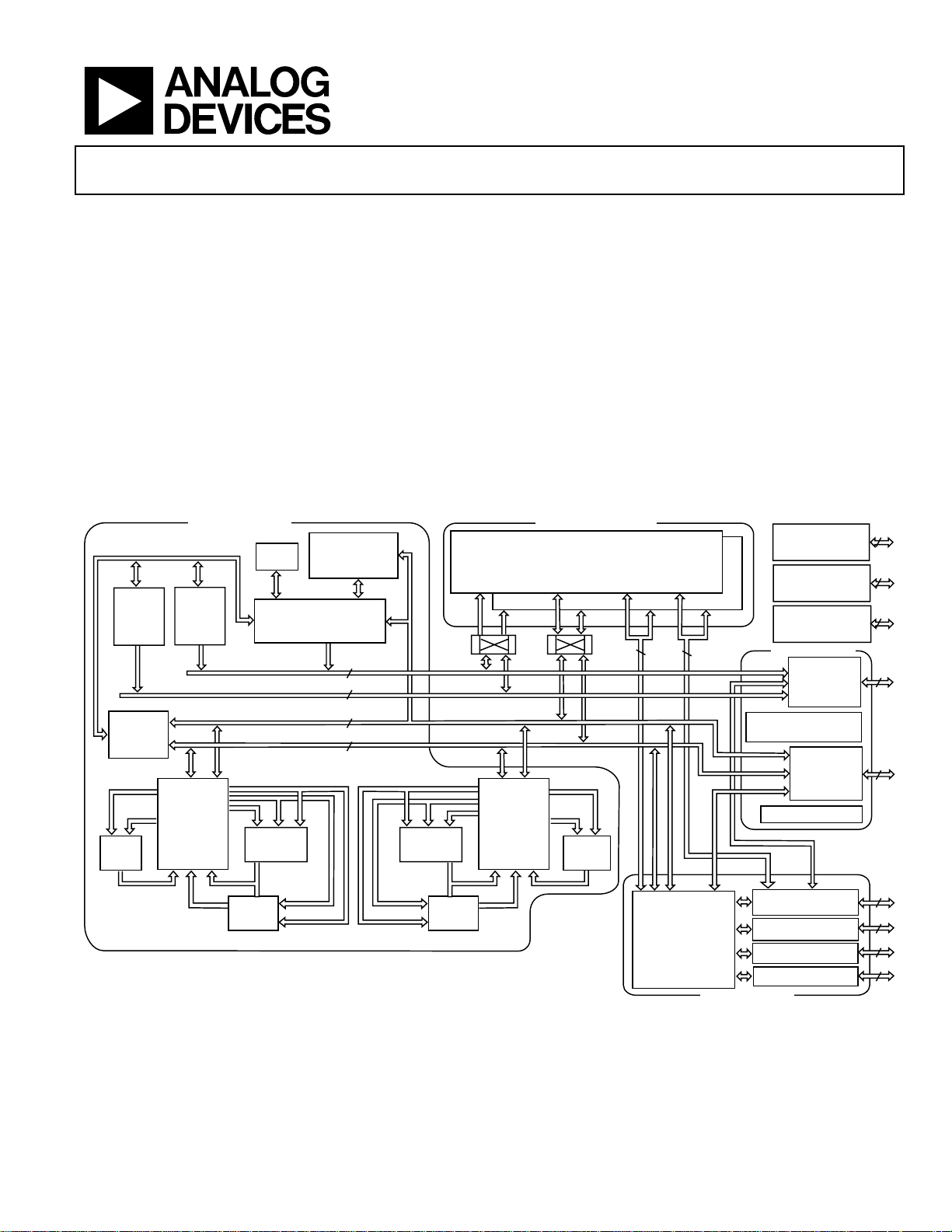

CORE PROCESSOR

INSTRUCTION

CACHE

32 × 48-BIT

PROGRAM

SEQUENCER

32

32

64

64

BARREL

SHIFTER

DAG1

8 × 4 × 32

BUS

CONNECT

(PX)

MULT

DAG2

8 × 4 × 32

DATA

REGISTER

FILE

(PEX)

16 × 40-BIT

TIMER

PM ADDRESS BUS

DM ADDRESS BUS

PM DATA BUS

DM DATA BUS

BARREL

SHIFTER

ADSST-SHARC-Mel-100

2

Serial ports offer I

simultaneous receive or transmit pins, which support up

to 16 transmit or 16 receive channels of audio

Integrated peripherals—integrated I/O processor,

0.5 Mbit on-chip SRAM, SDRAM controller, glueless

multiprocessing features, and I/O ports (serial, link,

external bus, SPI®, and JTAG)

SHARC Mel-100 supports 32-bit fixed-point, 32-bit

floating-point, and 40-bit floating-point formats

DUAL-PORTED SRAM

TWO INDEPENDENT

DUAL-PORTED BLOCKS

PROCESSOR PORT

ADDR DATA ADDR

ADDR DATA

DATA

REGISTER

FILE

(PEY)

16 × 40-BIT

MULT

S support via 8 programmable and

I/O PORT

DATA

DATA

IOD

64

Audio Processor

6

12

8

24

32

ADDR

IOA

18

BLOCK 0

BLOCK 1

JTAG

TEST & EMULATION

GPIO

FLAGS

SDRAM

CONTROLLER

EXTERNAL PORT

ADDR BUS

MUX

MULTIPROCESSOR

INTERFACE

DATA BUS

MUX

HOST PORT

ALU

ALU

Figure 1. Functional Block Diagram

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

IOP

REGISTERS

(MEMORY MAPPED)

CONTROL,

STATUS, AND

DATA BUFFERS

I/O PROCESSOR

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2003 Analog Devices, Inc. All rights reserved.

www.analog.com

DMA

CONTROLLER

SERIAL PORTS (4)

LINK PORTS (2)

SPI PORTS (1)

5

16

20

4

ADSST-SHARC-Mel-100

TABLE OF CONTENTS

Key Features ...................................................................................... 3

Absolute Maximum Ratings ......................................................... 20

General Description......................................................................... 4

Hardware Architecture ................................................................ 4

Software Architecture .................................................................. 5

SHARC Mel-100 Family Core Architecture.............................. 6

SHARC Mel-100 Memory and I/O Interface Features............ 9

Pin Function Descriptions ............................................................ 12

Boot Modes .................................................................................17

Specifications................................................................................... 18

Recommended Operating Conditions .................................... 18

Electrical Characteristics........................................................... 19

REVISION HISTORY

Revision 0: Initial Version

Timing Specifications ................................................................ 20

Power Dissipation ...................................................................... 21

Output Drive Currents .............................................................. 21

Test Conditions........................................................................... 21

Environmental Conditions ....................................................... 23

Pin Configuration........................................................................... 24

Pin Layout Summary ................................................................. 25

Outline Dimensions....................................................................... 26

Ordering Guide .......................................................................... 26

Rev. 0 | Page 2 of 28

ADSST-SHARC-Mel-100

KEY FEATURES

100 MHz (10 ns) core instruction rate

Single-cycle instruction execution, including SIMD

operations in both computational units

600 Mflops peak and 400 Mflops sustained performance

225-ball 17 mm × 17 mm MBGA package

Decodes industry-standard formats, using a 32-bit floatingpoint implementation

Decoders:

Dolby® Digital, Dolby Pro Logic® II, DTS-ES® Extended

Surround (including DTS-ES Discrete and DTS-ES

Matrix), DTS-96/24, DTS Neo:6®

PCM

Delay management

Bass management

MPEG-2 AAC

Wavesurround® virtual headphone and virtual

loudspeaker

Downsampling 96 kHz to 48 kHz (2-channel)

Single-chip DSP based implementation of digital audio

algorithms

SHARC Mel-100 processor features 100 MIPS

2

S compatible serial ports

I

Interface to external SDRAM

Easy interfaces to audio codecs

192 kHz processing

Supports customer specific postprocessing

Automatic stream detection

Automatic code loading

Easy to use software architecture

Optimized library of routines

Host communication using SPI port

Supports IEC 60958 for bit streams

8-channel output

Rev. 0 | Page 3 of 28

ADSST-SHARC-Mel-100

GENERAL DESCRIPTION

The SHARC Mel-100 family of powerful 32-bit audio

processors from Analog Devices enables flexible designs and

delivers a host of features across high-end and high fidelity

audio systems to the AV receiver and DVD markets. It includes

multichannel audio decoders, encoders, and postprocessors for

digital audio designs using DSPs in home theater systems and

automotive audio receivers.

With 32-bit audio quality, the SHARC Mel-100 audio processor

autodetects and decodes audio formats in real time, enabling

end users to enjoy a theater-quality audio experience in their

homes and automobiles.

The designs can be customized to meet the exact requirements

of the application. This audio DSP system enables designers to

make value additions to product features working off the highend base functionality with which they are provided.

Evaluation boards, sample applications, and all necessary

software support (e.g., drivers) are available. The evaluation

board enables OEMs to offer comprehensive and single-chip

implementations of advanced features for end-user products.

SHARC Mel-100 audio processors enable OEMs to produce

high quality, low cost designs featuring decoder algorithms and

postprocessors for DTS-ES Extended Surround (including both

DTS Discrete 6.1 and DTS Matrix 6.1), DTS Neo:6, Dolby

Digital, Dolby Pro Logic II, AAC, and WaveSurround.

The cost of development is reduced, enabling common

solutions across product lines. Field and remotely upgradeable

products with programmable DSPs and an optimized library of

routines, along with the best development tools in the industry,

reduce the time to market.

HARDWARE ARCHITECTURE

Hardware architecture includes the interface between the DSP

and the host microcontroller, command processing, data

transfer in serial and parallel form, data buffer management,

algorithm combinations, MIPS, and memory requirements that

are provided.

The multichannel algorithms are implemented on a SHARC

Mel-100 AVR evaluation board. The board is standalone and

accepts a compressed digital bit stream as serial input from

LD/DVD/CD players or stream generators, decodes the bit

stream, and generates a PCM stream in real time in

2-channel or multichannel mode. It has a microcontroller to

handle commands and option selections from a small keypad

and an LCD display for status display.

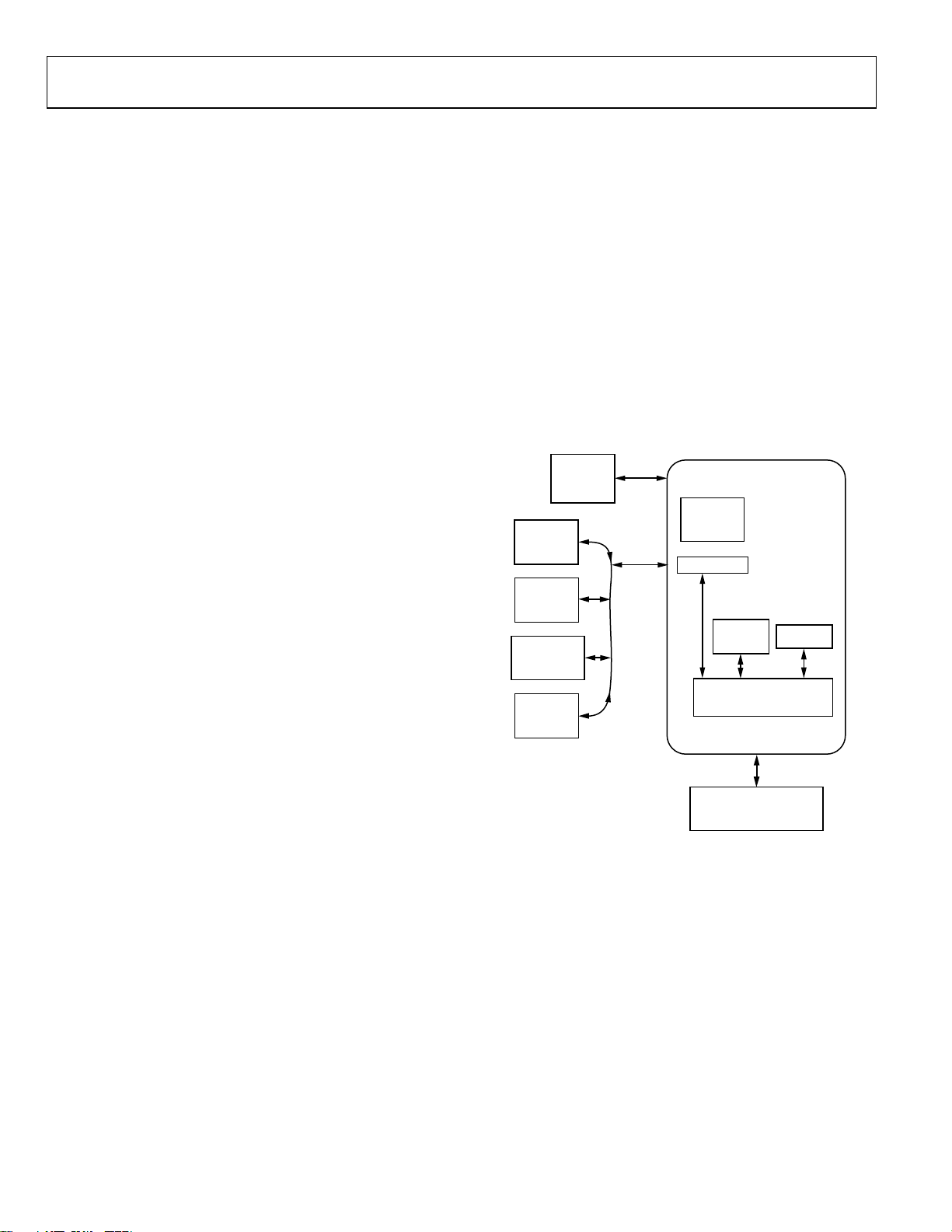

SDRAM

128k × 32,

BOOT ROM

1M × 8

IRQ

GPIO

ADC

SERIAL PORT

DAC

S/PDIF

TRANSMITTER

S/PDIF

RECEIVER

MULTI-

CHANNEL

CODEC

COMMAND

KERNEL

SHARC Mel-100 is the comprehensive answer to the needs of

the high-end, high quality digital audio market. It delivers a

realistic high fidelity audio experience along with the maximum

number of features in the product, across price points in the

high-end home theater and DVD markets.

Rev. 0 | Page 4 of 28

HOST MICRO

03373-0-002

Figure 2. Simplified Block Diagram

To understand the SHARC Mel-100 family hardware

architecture, one should examine its four major blocks:

• The Core Processor

• Dual-Ported SRAM

• External Port

• Input/Output Processor

The hardware architecture of the SHARC Mel-100 is complex. It

has four independent buses for dual data, one for instructions,

and one for I/O fetch. Since the four buses are independent,

multiple transactions take place within a single clock cycle. It

has two external ports, DMA channels, and eight serial ports. It

is a 0.35 ns technology IC operating at 3.3 V.

ADSST-SHARC-Mel-100

The SHARC Mel-100 processor can be interfaced to external

peripherals with relative ease. The communication between the

SHARC Mel-100 processor and a host microcontroller utilizes

the SPI bus. The host microcontroller can be the master and the

SHARC Mel-100 processor can act as a slave. The peripherals

can be controlled by the host microcontroller using the SPI bus.

The communication is based on commands and parameters.

Status information regarding the SHARC Mel-100 decoding is

periodically updated and made available to the host

microcontroller.

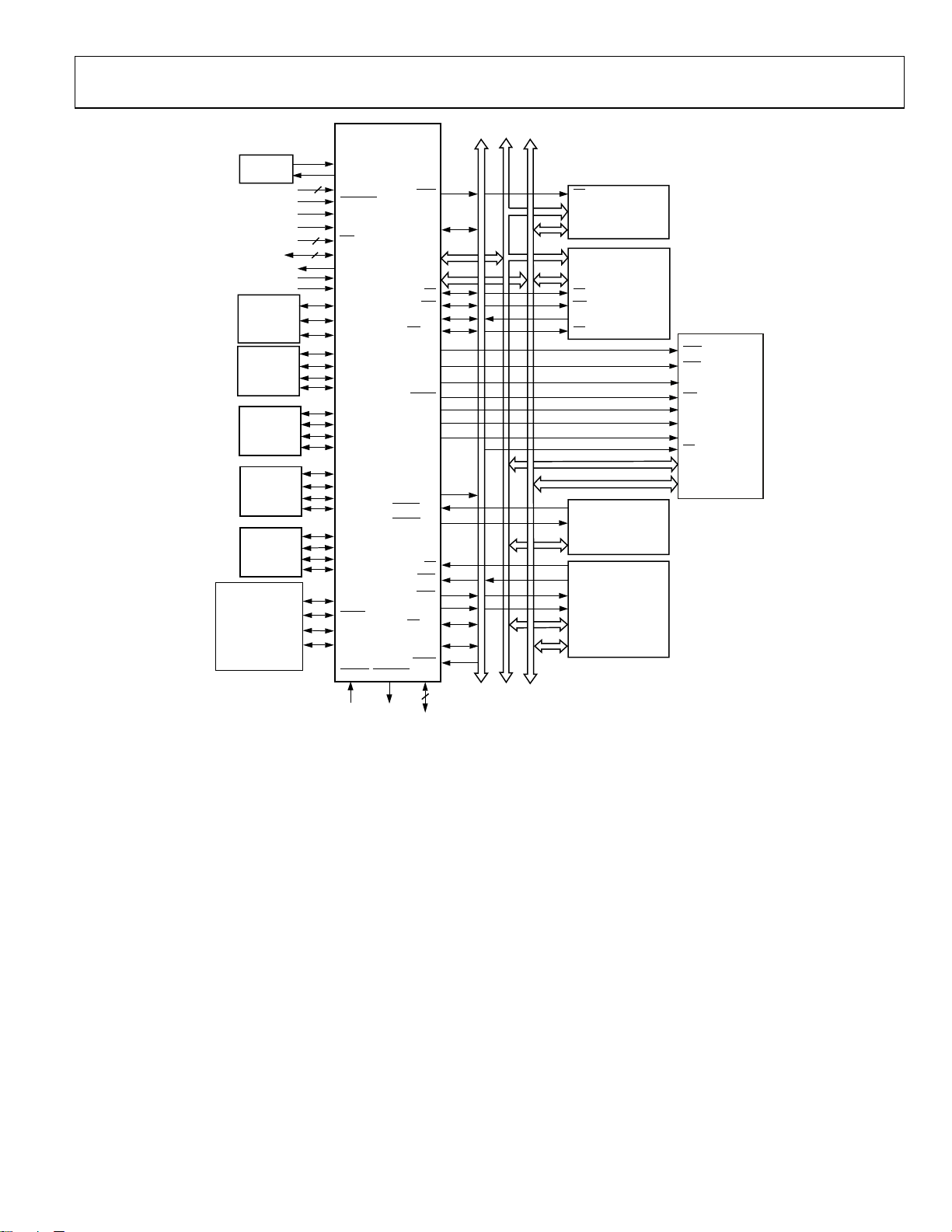

The block diagram of the SHARC Mel-100 (see Figure 1)

illustrates the following architectural features:

• Computation units (ALU, multiplier, and shifter) with a

shared data register file

• Data address generators (DAG1, DAG2)

• Program sequencer with instruction cache

• Timers with event capture modes

• On-chip, dual-ported SRAM

• External port for interfacing to off-chip memory and

peripherals

• Host port and SDRAM interface

• DMA controller

• Enhanced serial ports

• JTAG test access port

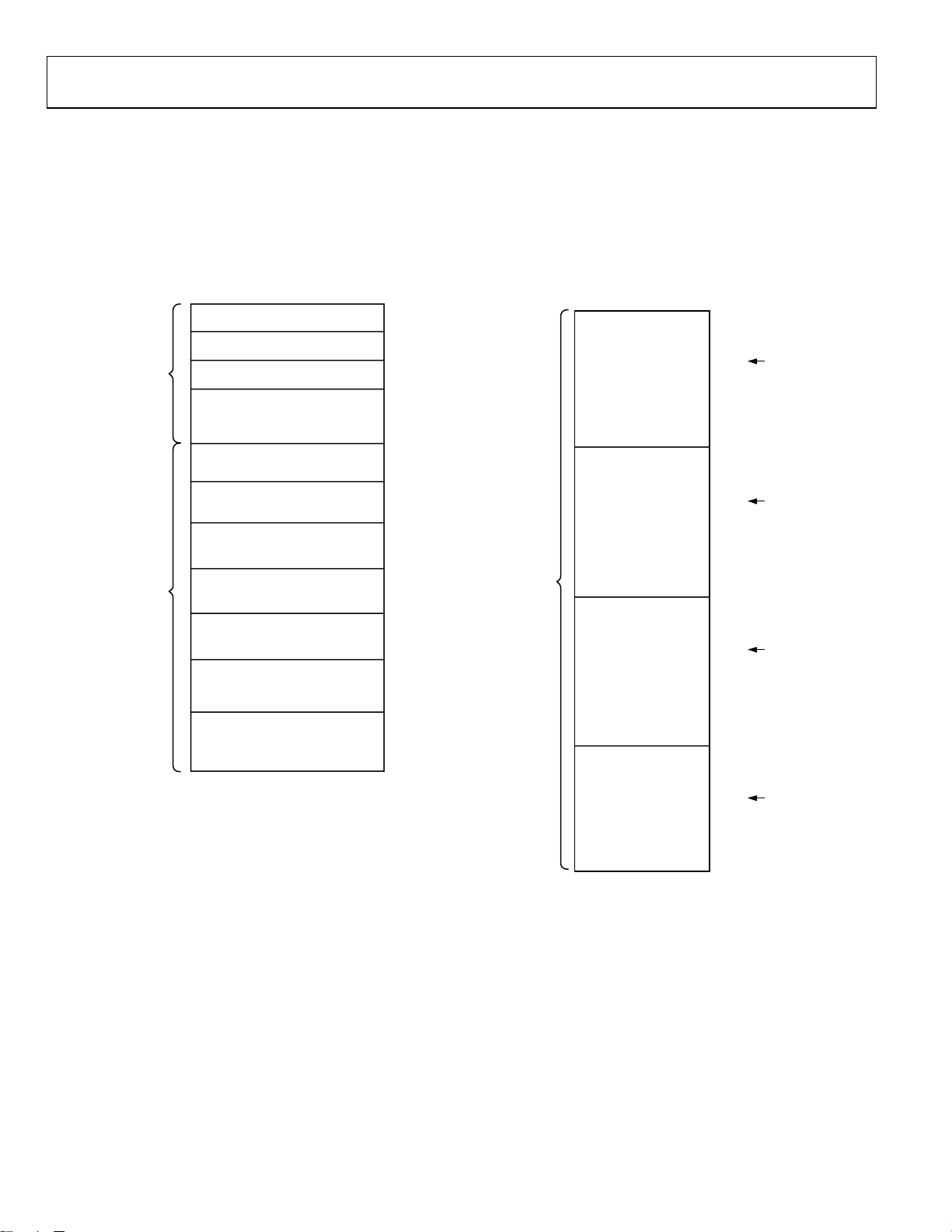

We will use Figure 2 as our reference. The SHARC Mel-100

communicates with the host microcontroller using SPI. The

SHARC Mel-100 has an on-chip memory buffer that is used for

storing commands/parameters sent by the host to the SHARC

Mel-100 and also status information from the SHARC Mel-100.

There is a defined protocol for passing commands and

obtaining status information. Once the SHARC Mel-100

receives a command from the host micro, it will process the

command and inform the host micro about the status. These

commands initiate actions such as encoding and decoding.

Encoding and decoding will result in data processing and the

processed data may be delivered over the serial port. For

example, while encoding, the MP3 data is accepted through the

serial port from peripherals like an ADC or S/PDIF receiver.

The MP3 data is then encoded and stored in an on-chip

compressed data buffer. The SHARC Mel-100 will prepare the

compressed frames in IEC 958 format so that they can be sent

out using the serial port or S/PDIF transmitter. Using the serial

port, compressed frames can be downloaded to the SHARC

Mel-100, where they can be decoded, and the resulting MP3

data can be sent on the serial port transmitter. While commands

and data are transferred between the host microcontroller and

the SHARC Mel-100 over the SPI, reliable communication

needs the help of interrupts and a few general-purpose

input/output lines.

SOFTWARE ARCHITECTURE

The audio processors from Analog Devices enable designers to

make value additions to product features working off the highend base functionality. The SHARC Mel-100 software has the

following parts:

• Executive kernel

• Algorithm as library module

The executive kernel has the following functions:

• Power-up hardware initialization

• Serial port management

• Automatic stream detect

• Automatic code load

• Command processing

• Interrupt handling

• Data buffer management

• Calling library module

• Status report

The executive kernel gets executed as soon as booting takes

place. The hardware resources are initialized in the beginning.

The command buffer and general-purpose programmable flag

pins are initialized. Various data buffers and memory variables

are initialized. Interrupts are programmed and enabled. Then,

definite signatures are written “Command buffer” to inform the

host that the SHARC Mel-100 is ready to receive the

commands. Once commands are issued by the host

microcontroller, they are executed and appropriate actions take

place. Decoding is handled by issuing appropriate commands

from the host microcontroller.

The kernel communicates with the library module for a

particular algorithm in a defined way. The details are found in

the specific implementation documents. As the kernel is

modular, it is easy to customize to different hardware platforms.

Most of the time, users need to change the initialization code to

suit the particular codec chosen.

INPUT STREAM

DECODING

LIBRARY

EXECUTIVE KERNEL

Figure 3. Software

The SHARC Mel-100 includes a 100 MHz core, dual-ported onchip SRAM, an integrated I/O processor with multiprocessing

support, and multiple internal buses to eliminate I/O

bottlenecks. The SHARC Mel-100 offers a Single-InstructionMultiple-Data (SIMD) architecture, using two computational

units. Fabricated in a state-of-the-art, high speed, low power

CMOS process, the SHARC Mel-100 has a 10 ns instruction

cycle time.

OUTPUT STREAM

Rev. 0 | Page 5 of 28

ADSST-SHARC-Mel-100

With its SIM

the SHARC Mel-100 can perform 600 million math operations

per second. Table 1 shows performance benchmarks for the

SHARC Mel-100.

The SHARC Mel-1

standards of integration for DSPs, combining a high

performance 32-bit DSP core with integrated, on-chip system

features. These features include a 1-Mbit dual-ported SRAM

memory, a host processor interface, an I/O processor that

supports 14 DMA channels, four serial ports, two link ports, a

SDRAM controller, an SPI interface, an external parallel bus,

and glueless multiprocessing.

Figure 2 illustrates the followin

• Two processing elements, each made up of an AL

• Data address generators (DAG1, DAG2)

• Program sequencer with instruction cach

• PM and DM buses capable of supporting fo

•

• On-chip SRAM

• SDRAM controller for gluel

• External port that supports

• D

• Four serial ports

• Two link p o r ts

• SPI compatible

• JTAG test access port

• 12 general-purpose I/O

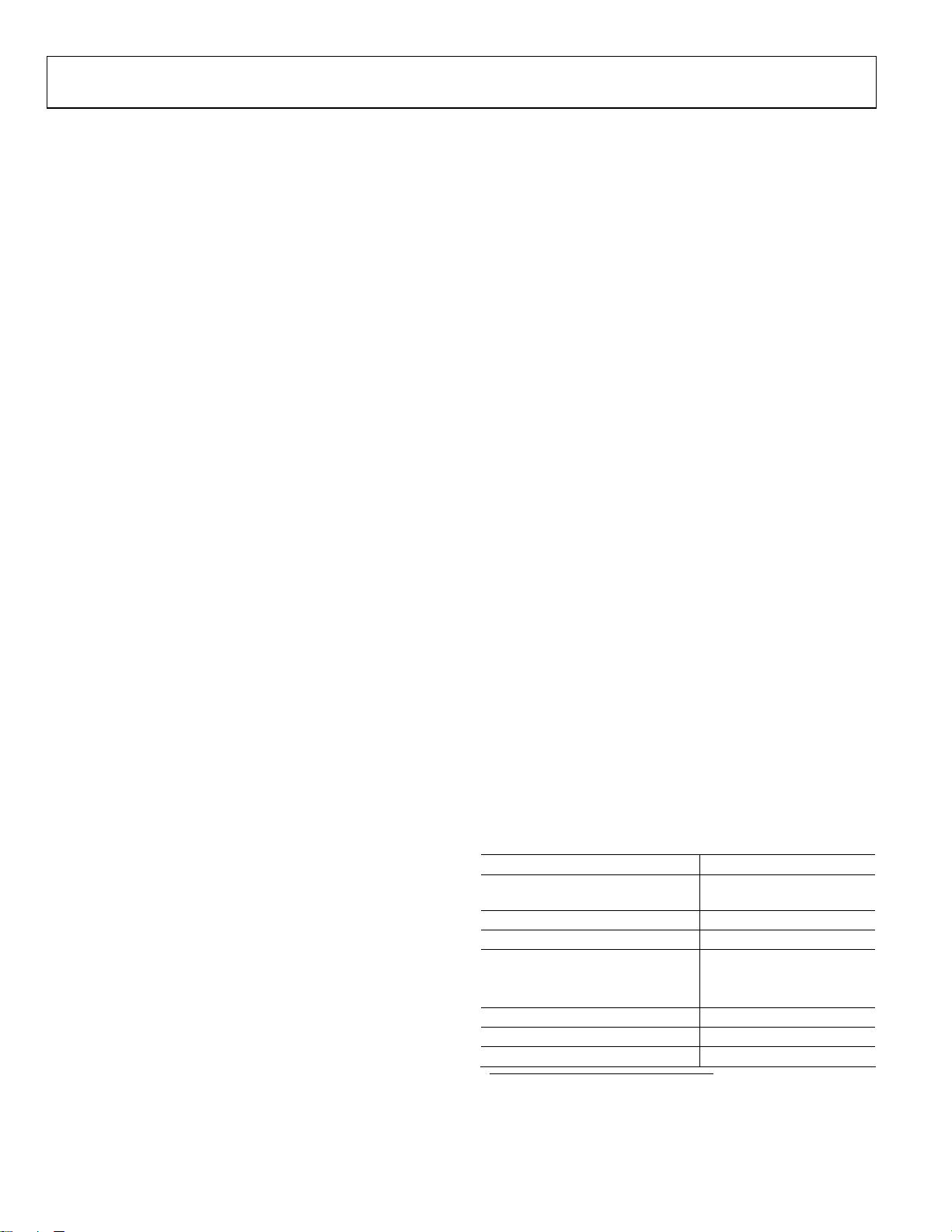

Figure 4 shows a typical single-p

multiprocessing system appears in Figure 8.

D computational hardware running at 100 MHz,

00 continues the SHARC’s industry-leading

g architectural features:

U,

multiplier, shifter, and data register file

e

ur 32-bit

data transfers between memory and the core every co

processor cycle

Interval timer

(0.5 Mbit)

ess interface to SDRAMs

• Interfacing to off-chip me

mory peripherals

• Glueless multiprocessing for six SHARC Mel-1

processors

• Host port read/write of IOP registers

MA controller

interface

pins

rocessor system. A

re

00

SHARC MEL-100 FAMILY CORE ARCHITECTURE

The SHARC Mel-100 includes the following architectural

features of the ADSP-2116x family core:

SIMD Computational Engine

The SHARC Mel-100 contains two computational processing

elements that operate as a Single Instruction Multiple Data

(SIMD) engine. The processing elements are referred to as PEX

and PEY, and each contains an ALU, multiplier, shifter, and

n

register file. PEX is always active, and PEY may be enabled by

setting the PEYEN mode bit in the MODE1 register. When this

mode is enabled, the same instruction is executed in both

processing elements, but each processing element operates on

different data. This architecture is efficient at executing mathintensive DSP algorithms.

Entering SIMD mode also has an effect on the way data is

transferred between memory and the processing elements.

When in SIMD mode, twice the data bandwidth is required to

sustain computational operation in the processing elements.

Because of this requirement, entering SIMD mode also doubles

the bandwidth between memory and the processing elements.

When using the DAGs to transfer data in SIMD mode, two data

values are transferred with each access of memory or the

register file.

Independent, Parallel Computation Units

Within each processing element is a set of computational units.

The computational units consist of an arithmetic/logic unit

(ALU), multiplier, and shifter. These units perform single-cycle

instructions. The three units within each processing element are

arranged in parallel, maximizing computational throughput.

Single multifunction instructions execute parallel ALU and

multiplier operations. In SIMD mode, the parallel ALU and

multiplier operations occur in both processing elements. These

computation units support IEEE 32-bit single-precision

floating-point, 40-bit extended precision floating-point, and

32-bit fixed-point data formats.

Table 1. Benchmarks (at 100 MHz)

Benchmark Algorithm Speed (at 100 MHz)

1024 Point Complex FFT

(Radix 4, with Reversal)

FIR Filter (per Tap)1 5 ns

IIR Filter (per Biquad)1 40 ns

Matrix Multiply (Pipelined)

[3 × 3] • [3 × 1] 30 ns

[4 × 4] • [4 × 1] 37 ns

Divide (y/x) 60 ns

Inverse Square Root 40 ns

DMA Transfers 800 Mbytes/s

1

Assumes two filters in multichannel SIMD mode

1

171 µs

Rev. 0 | Page 6 of 28

ADSST-SHARC-Mel-100

ADSST SHARC

MEL-100

3

12

2

CLKIN

XTAL

CLK_CFG1–0

CLKDBL

EBOOT

LBOOT

IRQ2-0

FLAG11–0

TIMEXP

RPBA

ID2-0

LXCLK

LXACK

LXDAT7–0

SCLK0

FS0

D0A

D0B

SCLK1

FS1

D1A

D1B

SCLK2

FS2

D2A

D2B

SCLK3

FS3

D3A

D3B

SPICLK

SPIDS

MOSI

MISO

RESET

RSTOUT

BMS

BRST

ADDR23–0

DATA47–16

WR

ACK

MS3–0

RAS

CAS

DQM

SDWE

SDCLK1–0

SDCKE

SDA10

CLKOUT

DMAR1–2

DMAG1–2

HBR

HBG

REDY

BR1–6

SBTS

JTAG

RD

CS

PA

7

CONTROL

Figure 4. System Block Diagram

ADDRESS

DATA

CS

ADDR

DATA

ADDR

DATA

OE

WE

ACK

CS

DATA

ADDR

DATA

BOOT

EPROM

(OPTIONAL)

MEMORY

AND

PERIPHERALS

(OPTIONAL)

DMA DEVICE

(OPTIONAL)

HOST

PROCESSOR

INTERFACE

(OPTIONAL)

03681-0-001

RAS

CAS

DQM

WE

CLK

CKE

A10

CS

ADDR

DATA

SDRAM

(OPTIONAL)

Instruction Cache

The SHARC Mel-100 includes an on-chip instruction cache that

enables 3-bus operation for fetching an instruction and four

data values. The cache is selective—only the instructions whose

fetches conflict with PM bus data accesses are cached. This

cache enables full speed execution of core, looped operations

such as digital filter multiply-accumulates and FFT butterfly

processing.

Data Address Generators with Hardware Circular Buffers

The SHARC Mel-100 processor’s two data address generators

(DAGs) are used for indirect addressing and implementing

circular data buffers in hardware. Circular buffers enable

efficient programming of delay lines and other data structures

required in digital signal processing, and are commonly used in

digital filters and Fourier transforms. The two DAGs of the

SHARC Mel-100 contain sufficient registers to enable the

creation of up to 32 circular buffers (16 primary register sets,

16 secondary). The DAGs automatically handle address pointer

CLOCK

LINK

DEVICES

(2 MAX)

(OPTIONAL)

SERIAL

DEVICE

(OPTIONAL)

SERIAL

DEVICE

(OPTIONAL)

SERIAL

DEVICE

(OPTIONAL)

SERIAL

DEVICE

(OPTIONAL)

SPI

COMPATIBLE

DEVICE

(HOST OR SLAVE)

(OPTIONAL)

Data Register File

A general-purpose data register file is contained in each

processing element. The register files transfer data between the

computation units and the data buses, and store intermediate

results. These 10-port, 32-register (16 primary, 16 secondary)

register files, combined with the SHARC Mel-100’s enhanced

Harvard architecture, enable unconstrained data flow between

computation units and internal memory. The registers in PEX

are referred to as R0–R15, and in PEY as S0–S15.

Single-Cycle Fetch of Instruction and Four Operands

The SHARC Mel-100 features an enhanced Harvard

architecture in which the data memory (DM) bus transfers data

and the program memory (PM) bus transfers both instructions

and data (see Figure 4). With the SHARC Mel-100’s separate

program and data memory buses and on-chip instruction cache,

the processor can simultaneously fetch four operands (two over

each data bus) and an instruction (from the cache), all within a

single cycle.

Rev. 0 | Page 7 of 28

ADSST-SHARC-Mel-100

Y

L

Y

wraparound, reduce overhead, increase performance, and

simplify implementation. Circular buffers can start and end at

any memory location.

Flexible Instruction Set

The 48-bit instruction word accommodates a variety of parallel

operations for concise programming. For example, the SHARC

Mel-100 can conditionally execute a multiply, an add, and a

ADDRESS

subtract in both processing elements, while branching, all

within a single instruction.

ADDRESS

INTERNA

MEMOR

SPACE

MULTIPROCESSOR

MEMOR

SPACE

IOP REGISTERS

LONG WORD ADDRESSING

NORMAL WORD ADDRESSING

SHORT WORD ADDRESSING

IOP REGISTERS OF

ADSST-SHARC-MEL-100

WITH ID = 001

IOP REGISTERS OF

ADSST-SHARC-MEL-100

WITH ID = 010

IOP REGISTERS OF

ADSST-SHARC-MEL-100

WITH ID = 011

IOP REGISTERS OF

ADSST-SHARC-MEL-100

WITH ID = 100

IOP REGISTERS OF

ADSST-SHARC-MEL-100

WITH ID = 101

IOP REGISTERS OF

ADSST-SHARC-MEL-100

WITH ID = 110

RESERVED

0x0000 0000–0x0001 FFFF

0x0002 0000–0x0002 1FFF (BLK 0)

0x0002 8000–0x0002 9FFF (BLK 1)

0x0004 0000–0x0004 3FFF (BLK 0)

0x0005 0000–0x0005 3FFF (BLK 1)

0x0008 0000–0x0008 7FFF (BLK 0)

0x000A 0000–0x000A 7FFF (BLK 1)

0x0010 0000–0x0011 FFFF

0x0012 0000–0x0013 FFFF

0x0014 0000–0x0015 FFFF

0x0016 0000–0x0017 FFFF

0x0018 0000–0x0019 FFFF

0x001A 0000–0x001B FFFF

0x001C FFFF

0x001F FFFF

0x0020 0000

MS0

BANK 0

0x00FF FFFF (NON-SDRAM)

0x03FF FFFF (SDRAM)

0x0400 0000

MS1

BANK 1

0x04FF FFFF (NON-SDRAM)

0x07FF FFFF (SDRAM)

0x0800 0000

MS2

BANK 2

0x08FF FFFF (NON-SDRAM)

0x0BFF FFFF (SDRAM)

0x0C00 0000

EXTERNAL MEMORY SPACE

BANK 3

0x0CFF FFFF (NON-SDRAM)

0x0FFF FFFF (SDRAM)

NOTE: BANK SIZES ARE FIXED

MS3

Figure 5. Memory Map Block Diagram

Rev. 0 | Page 8 of 28

ADSST-SHARC-Mel-100

SHARC MEL-100 MEMORY AND I/O INTERFACE FEATURES

The SHARC Mel-100 adds the following architectural features

to the ADSP-2116x family core:

On-Chip Memory

The SHARC Mel-100 contains 0.5 Mbit of on-chip SRAM.

Off-Chip Memory and Peripherals Interface

The SHARC Mel-100’s external port provides the processor’s

interface to off-chip memory and peripherals. The 62.7 Mword

off-chip address space (254 Mword if all SDRAM) is included in

the SHARC Mel-100 processor’s unified address space. The

separate on-chip buses—for PM addresses, PM data, DM

addresses, DM data, I/O addresses, and I/O data—are

multiplexed at the external port to create an external system bus

with a single 24-bit address bus and a single 32-bit data bus.

Every access to external memory is based on an address that

fetches a 32-bit word. When fetching an instruction from

external memory, two 32-bit data locations are being accessed

for packed instructions. Unused link port lines can also be used

as additional data lines DATA[0]–DATA[15], enabling singlecycle execution of instructions from external memory at up to

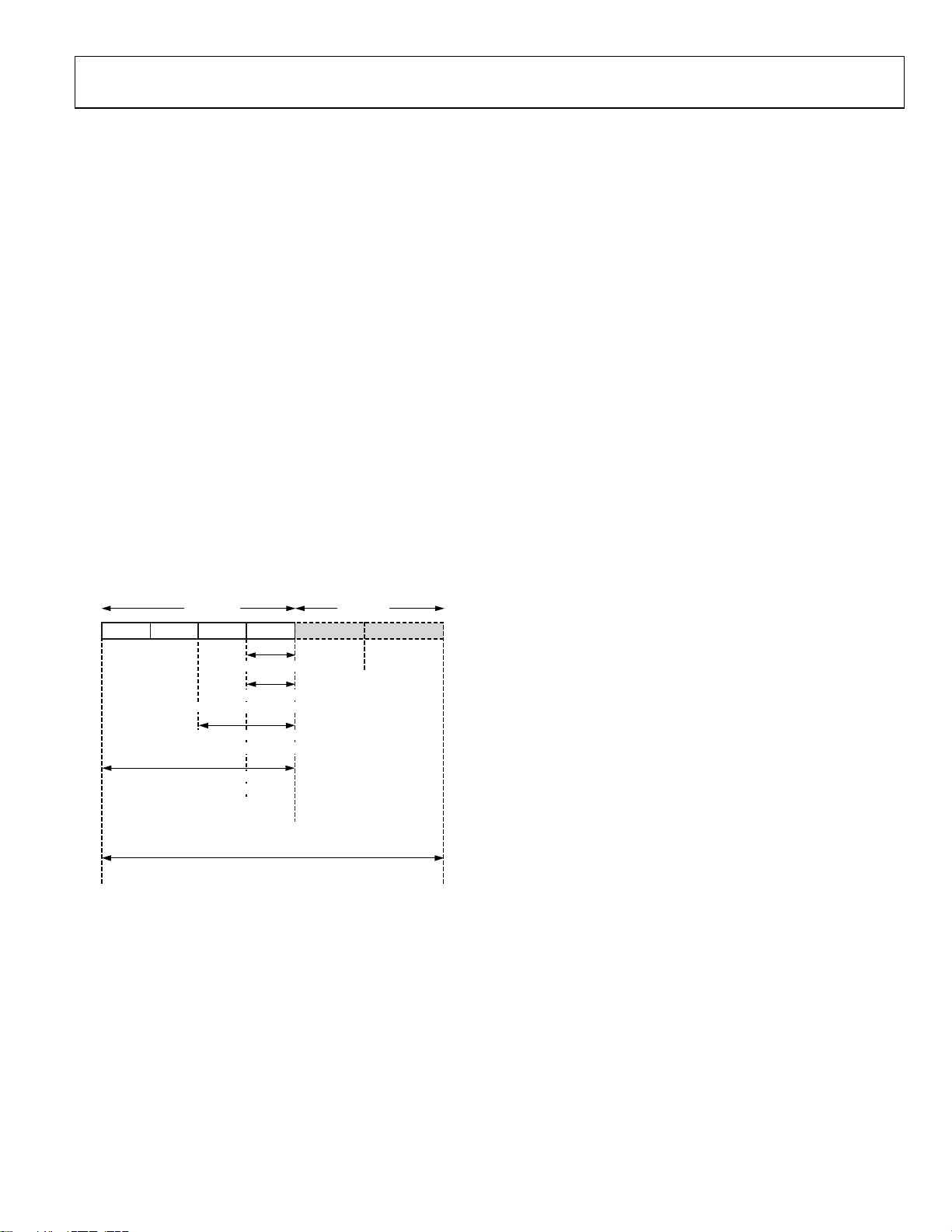

100 MHz. Figure 6 shows the alignment of various accesses to

external memory.

DATA 47

–

16 DATA 15–0

47 40 39 32 31 24 23 16 15 8 7

PROM BOOT

8-BIT PACKED DMA DATA

8-BIT PACKED INSTRUCTION EXECUTION

16-BIT PACKED DMA DATA

16-BIT PACKED INSTRUCTION EXECUTION

FLOAT OR FIXED, D31–D0, 32-BIT PACKED

32-BIT PACKED INSTRUCTION

48-BIT INSTRUCTION FETCH

(NO PACKING)

Figure 6. External Data Alignment Options

L1DATA[7:0]

DATA 15

EXTRA DATA LINES DATA[15–0]

ARE ONLY ACCESSIBLE IF

LINK PORTS ARE DISABLED.

ENABLE THESE ADDITIONAL

DATA LINES BY SELECTING

IPACK[1:0] = 01 IN SYSCON

–

8

L0DATA[7:0]

DATA7–0

The external port supports asynchronous, synchronous, and

synchronous burst access. Synchronous burst SRAM can be

interfaced gluelessly. The SHARC Mel-100 can also interface

gluelessly to SDRAM. Addressing of an external memory device

is facilitated by on-chip decoding of high-order address lines to

generate memory bank select signals. The SHARC Mel-100

provides programmable memory wait states and external

memory acknowledge controls to enable interfacing to memory

and peripherals with variable access, hold, and disable time

requirements.

0

SDRAM Interface

The SDRAM interface enables the SHARC Mel-100 to transfer

data to and from synchronous DRAM (SDRAM) at the core

clock frequency or one-half the core clock frequency. The

synchronous approach, coupled with the core clock frequency,

supports data transfer at a high throughput—up to

400 Mbytes/s for 32-bit transfers and 600 Mbytes/s for 48-bit

transfers. The SDRAM interface provides a glueless interface

with standard SDRAMs (16 Mbit, 64 Mbit, 128 Mbit, and

256 Mbit) and includes options to support additional buffers

between the SHARC Mel-100 and SDRAM. The SDRAM

interface is extremely flexible and provides capability for

connecting SDRAMs to any one of the SHARC Mel-100

processor’s four external memory banks, with up to all four

banks mapped to SDRAM. Systems with several SDRAM

devices connected in parallel may require buffering to meet

overall system timing requirements. The SHARC Mel-100

supports pipelining of the address and control signals to enable

such buffering between itself and multiple SDRAM devices.

Target Board JTAG Emulator Connector

Analog Devices’ DSP Tools product line of JTAG emulators uses

the IEEE 1149.1 JTAG test access port of the SHARC Mel-100

processor to monitor and control the target board processor

during emulation. Analog Devices’ DSP Tools product line of

JTAG emulators provides emulation at full processor speed,

enabling inspection and modification of memory, registers, and

processor stacks. The processor’s JTAG interface ensures that

the emulator will not affect target system loading or timing. For

complete information on Analog Devices’ DSP Tools product

line of JTAG emulator operation, see the appropriate Emulator

Hardware User's Guide. For detailed information on the

interfacing of Analog Devices’ JTAG emulators with Analog

Devices’ DSP products with JTAG emulation ports, please refer

to the Engineer-to-Engineer Note EE-68, Analog Devices JTAG

Emulation Technical Reference. Both of these documents can be

found on the Analog Devices website at:

http://www.analog.com/dsp/tech_docs.html

DMA Controller

The SHARC Mel-100 processor’s on-chip DMA controller

enables zero-overhead data transfers without processor

intervention. The DMA controller operates independently and

invisibly to the processor core, enabling DMA operations to

occur while the core is simultaneously executing its program

instructions. DMA transfers can occur between the SHARC

Mel-100 processor’s internal memory and external memory,

external peripherals, or a host processor. DMA transfers can

also occur between the SHARC Mel-100 processor’s internal

memory and its serial ports, link ports, or the SPI (serial

peripheral interface) compatible port. External bus packing and

unpacking of 16-, 32-, 48-, or 64-bit words in internal memory

is performed during DMA transfers from either 8-, 16-, or 32bit wide external memory. Fourteen channels of DMA are

Rev. 0 | Page 9 of 28

Loading...

Loading...