Analog Devices ADSST-EM-3035 Datasheet

SALEM® Three-Phase

a

FEATURES

IEC 687, Class 0.5 and Class 0.2 Accuracy

ANSI C12.1

IEC 1268, Requirements for Reactive Power

Configurable as Import/Export or Import Only

Simultaneous Measurement of:

Active Power and Energy—Import and Export

Reactive Power and Energy

Apparent Power

Power Factor for Individual Phases and Total Frequency

RMS Voltage for All Phases

RMS Current for All Phases

Harmonic Analysis for Voltage and Current

All Odd Harmonics up to 21st Order

Interface with a General Purpose Microcontroller

User-Friendly Calibration of Gain Offset and Phase and

Nonlinearity Compensation on CTs (Patent Pending)

Two Programmable Output E-Pulses

Programmable E-Pulse Constant from 1,000 Pulses/kWh

to 20,000 Pulses/kWh

15 kHz Sampling Frequency

Tamper-Proof Metering

Single 5 V Supply

SMPS

RESISTOR

BLOCK

CT

CT

CT

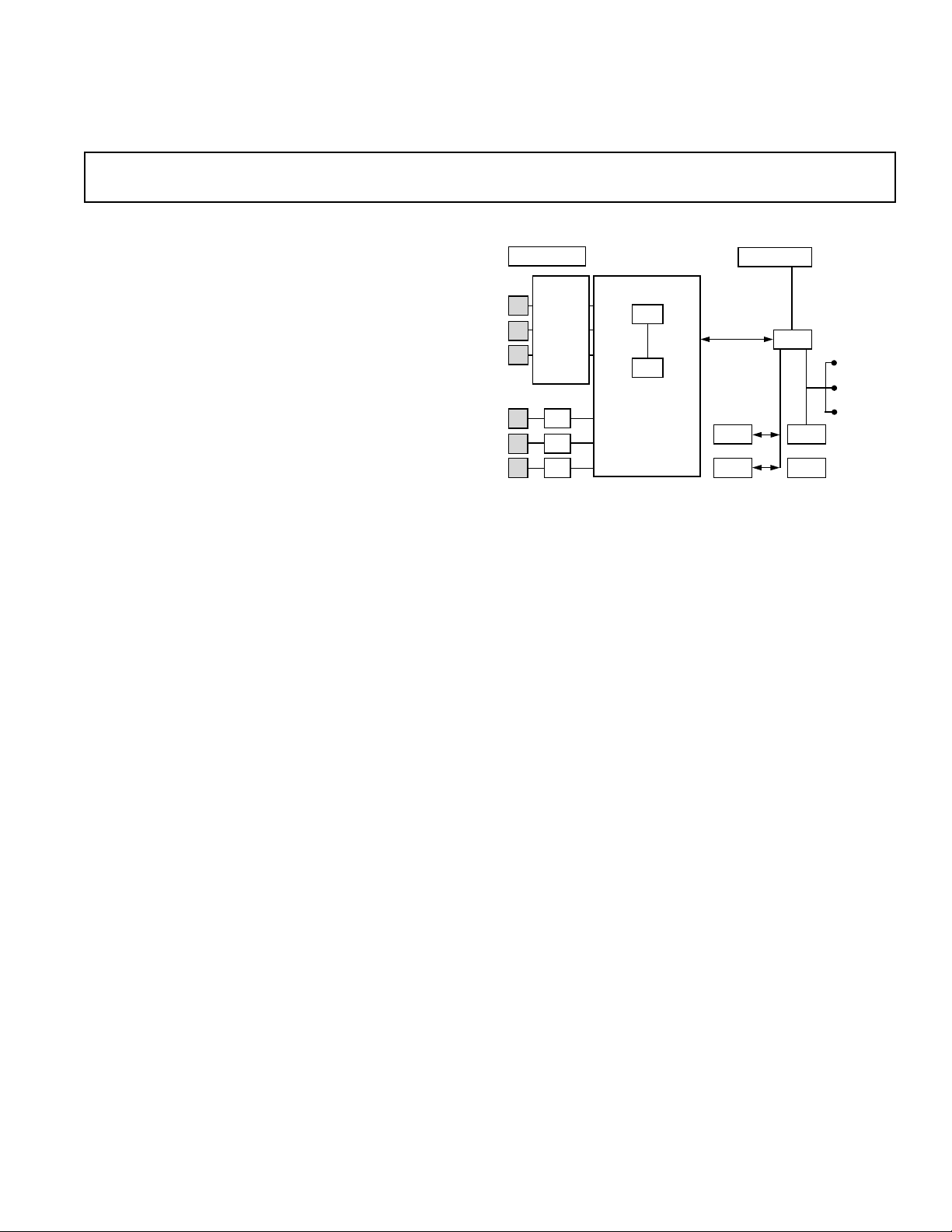

Electronic Energy Meter

ADSST-EM-3035

FUNCTIONAL BLOCK DIAGRAM

LCD DISPLAY

DSP

ADC

ADSST-EM-3035

CHIPSET

SPI BUS

FLASH

RTC

C

BUTTONS

OPTO

RS-232

GENERAL DESCRIPTION

The ADSST-EM-3035 Chipset consists of a fast and accurate

6 channel, 16-bit sigma-delta analog-to-digital converter

ADSST-73360AR (ADC), an efficient digital signal processor

ADSST-2185KST-133 (DSP), and Metering Software. The

ADC and DSP are interfaced together to simultaneously acquire

voltage and current samples on all the three phases and perform

mathematically intensive computations to accurately

calculate

the Powers, Energies, Instantaneous Quantities, and Harmonics.

The chipset could be interfaced to any general-purpose microprocessor to develop state of the art polyphase or Tri-vector energy

metering solution in accordance with IEC 1036, IEC 687, or

ANSI C12.1.

All calibrations are done in digital domain and no trimming

potentiometers are required.

SALEM is a registered trademark of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

ADSST-EM-3035

ADSST-2185KST-133 (DSP) SPECIFICATION

FEATURES

30 ns Instruction Cycle 33 MIPS Sustained Performance

Single-Cycle Instruction Execution

Single-Cycle Context Switch

Three-Bus Architecture Allows Dual Operand Fetches

in Every Instruction Cycle

Multifunction Instructions

Power-Down Mode Featuring Low CMOS Standby Power

Dissipation with 100 Cycle Recovery from Power-Down

Condition

Low Power Dissipation in Idle Mode

ADSP-2100 Family Code Compatible, with Instruction

Set Extensions

40 kBytes of On-Chip RAM, Configured as

8 KWords On-Chip Program Memory RAM and

8 KWords On-Chip Data Memory RAM

Dual Purpose Program Memory for Both Instruction

and Data Storage

Independent ALU, Multiplier/Accumulator, and Barrel

Shifter Computational Units

Two Independent Data Address Generators

Powerful Program Sequencer Provides Zero Overhead

Looping Conditional Instruction Execution

Programmable 16-Bit Interval Timer with Prescaler

100-Lead TQFP

16-Bit Internal DMA Port for High Speed Access to On-

Chip Memory (Mode Selectable)

4 MBytes Byte Memory Interface for Storage of Data

Tables and Program Overlays

8-Bit DMA to Byte Memory for Transparent Program and

Data Memory Transfers (Mode Selectable)

I/O Memory Interface with 2048 Locations Supports

Parallel Peripherals (Mode Selectable)

Programmable Memory Strobe and Separate I/O

Memory Space Permits Glueless System Design

(Mode Selectable)

Programmable Wait State Generation

Two Double-Buffered Serial Ports with Companding

GENERAL DESCRIPTION

The ADSST-2185KST-133 is a single-chip microcomputer

optimized for digital signal processing (DSP) and other high

speed numeric processing applications.

The ADSST-2185KST-133 combines the ADSP-2100 family

base architecture (three computational units, data address

generators, and a program sequencer) with two serial ports, a

16-bit internal DMA port, a byte DMA port, a programmable

timer, Flag I/O, extensive interrupt capabilities, and on-chip

program and data memory.

The ADSST-2185KST-133 integrates 40 kBytes of on-chip

memory configured as 8 Kwords (24-bit) of program RAM and

8 Kwords (16-bit) of data RAM. Power-down circuitry is also

provided to meet the low power needs of battery operated portable

equipment. The ADSST-2185KST-133 is available in a 100-lead

TQFP package.

In addition, the ADSST-2185KST-133 supports instructions

that include bit manipulations, bit set, bit clear, bit toggle, bit

test new ALU constants, new multiplication instruction (x squared),

biased rounding, result free ALU operations, I/O memory transfers, and global interrupt masking for increased flexibility.

Fabricated in a high speed, double metal, low power, CMOS

process, the ADSST-2185KST-133 operates with a 25 ns

instruction cycle time. Every instruction can execute in a single

processor cycle.

The ADSST-2185KST-133’s flexible architecture and comprehensive instruction set allow the processor to perform

multiple operations in parallel. In one processor cycle, the

ADSST-2185KST-133 can:

•

•

•

•

•

•

Hardware and Automatic Data Buffering

Automatic Booting of On-Chip Program Memory from

Byte-Wide External Memory, e.g., EPROM, or through

Internal DMA Port

Six External Interrupts

13 Programmable Flag Pins Provide Flexible System Signaling

UART Emulation through Software SPORT Reconfiguration

ICE-Port Emulator Interface Supports Debugging in Final Systems

Generate the next program address

Fetch the next instruction

Perform one or two data moves

Update one or two data address pointers

Perform a computational operation

This takes place while the processor continues to:

Receive and transmit data through the two serial ports

Receive and/or transmit data through the internal DMA port

Receive and/or transmit data through the byte DMA port

Decrement timer

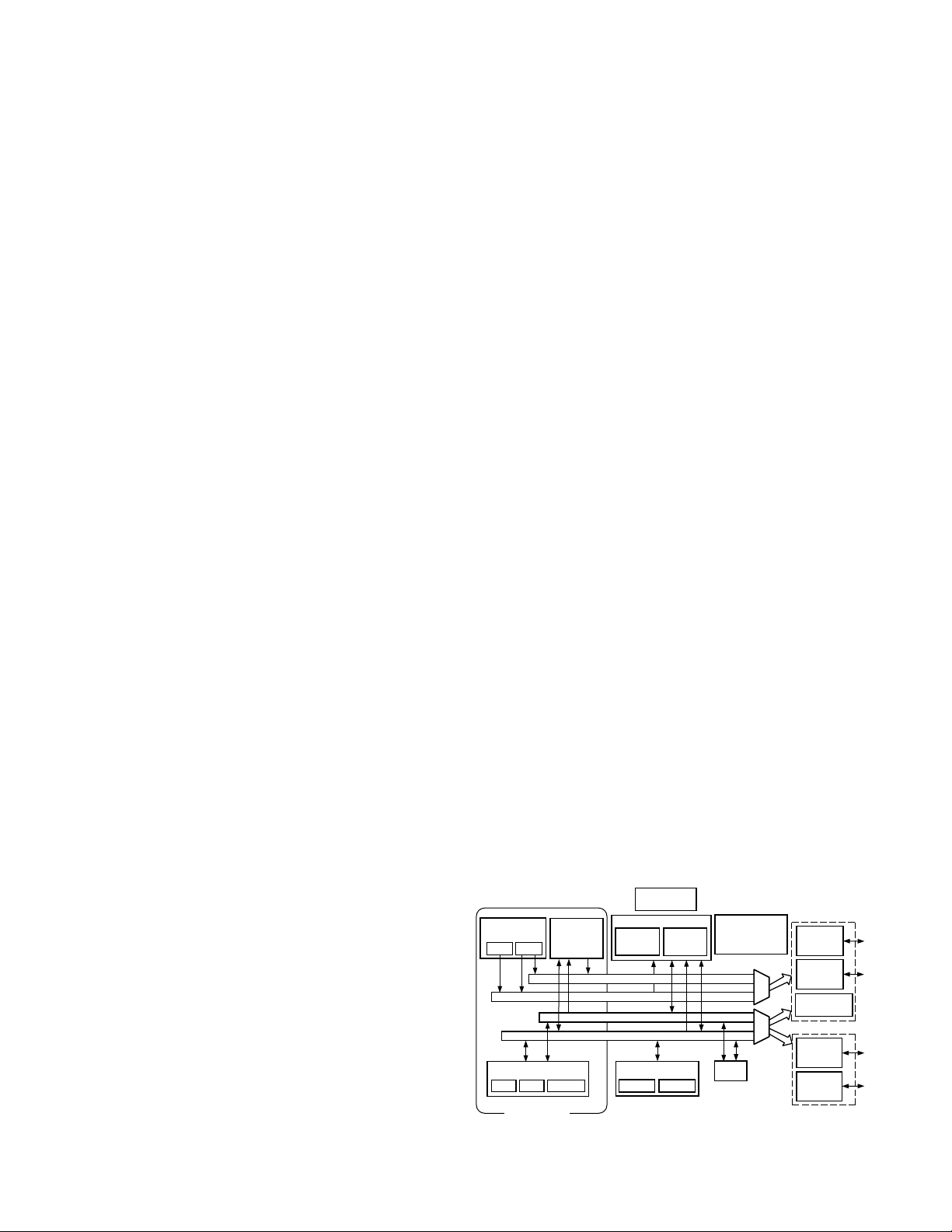

POWER-DOWN

DATA ADDRESS

GENERATORS

DAG 2

DAG 1

ARITHMETIC UNITS

ALU

MAC

ADSP-2100 BASE

ARCHITECTURE

PROGRAM

SEQUENCER

PROGRAM MEMORY ADDRESS

DATA MEMORY ADDRESS

PROGRAM MEMORY DATA

DATA MEMORY DATA

SHIFTER

CONTROL

MEMORY

16K 24

PROGRAM

MEMORY

SERIAL PORTS

16K 16

DATA

MEMORY

SPORT 1SPORT 0

PROGRAMMABLE

I/O

AND

FLAGS

TIMER

FULL MEMORY

MODE

EXTERNAL

ADDRESS

BUS

EXTERNAL

DATA

BUS

BYTE DMA

CONTROLLER

OR

EXTERNAL

DATA

BUS

INTERNAL

DMA

PORT

HOST MODE

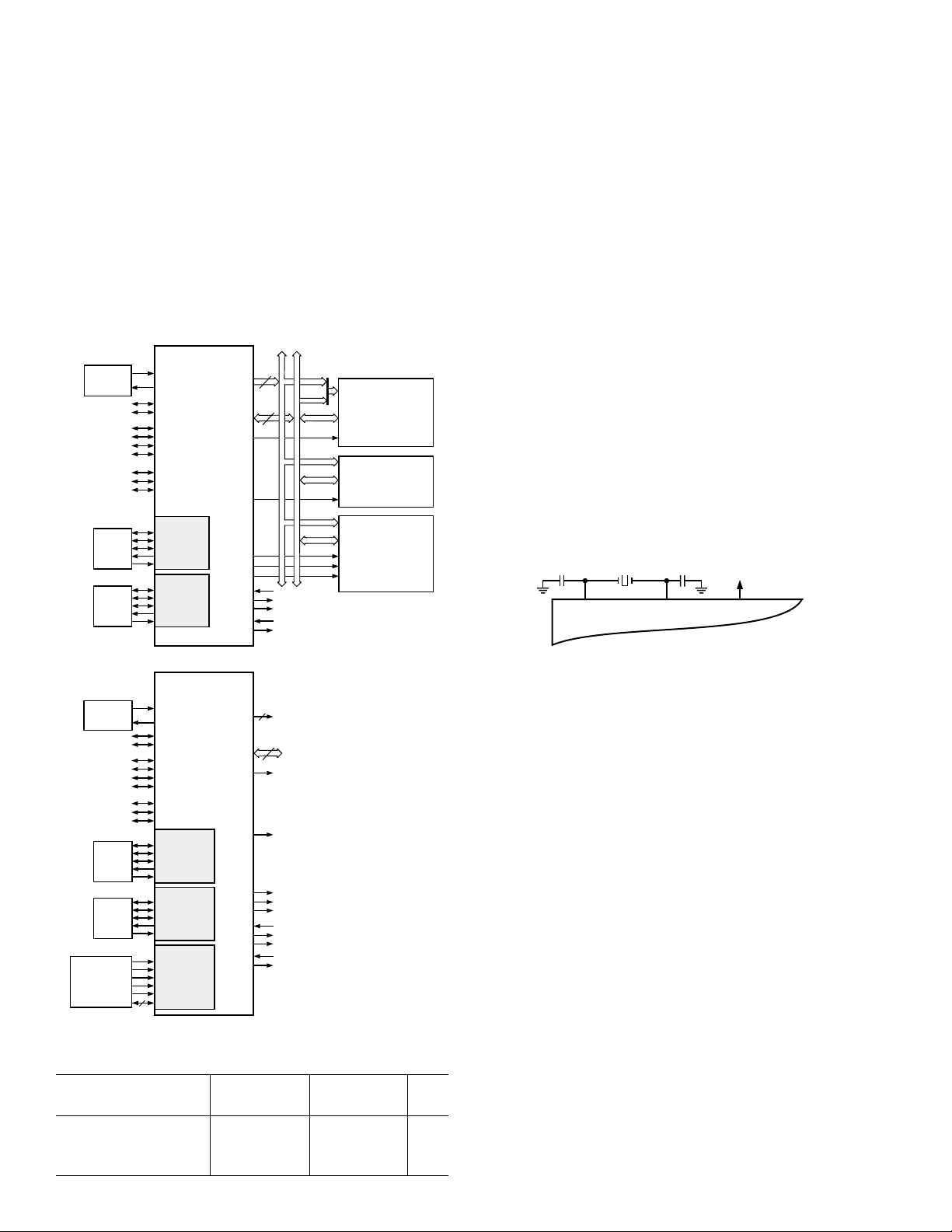

Figure 1. Functional Block Diagram

–2–

REV. 0

ADSST-EM-3035

ARCHITECTURE OVERVIEW

The ADSST-2185KST-133 instruction set provides flexible

data moves and multifunction (one or two data moves with a

computation) instructions. Every instruction can be executed in

a single processor cycle. The ADSST-2185KST-133 assembly

language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports

program development.

Figure 1 is an overall block diagram of the ADSST-2185KST-133.

The processor contains three independent computational units:

the ALU, the multiplier/accumulator (MAC), and the shifter.

The computational units process 16-bit data directly and have

provisions

performs a standard set of arithmetic and logic operations; division

primitives are also supported. The MAC performs single-cycle

multiply, multiply/add and multiply/subtract operations with 40

bits of accumulation. The shifter performs logical and arithmetic

shifts, normalization, denormalization and derive exponent

operations.

The shifter can be used to efficiently implement numeric format

control including multiword and block floating-point representations.

The internal result (R) bus connects the computational units

so the output of any unit may be the input of any unit on the

next cycle.

A powerful program sequencer and two dedicated data address

generators ensure efficient delivery of operands to these computational units. The sequencer supports conditional jumps,

subroutine calls, and returns in a single cycle. With internal loop

counters and loop stacks, the ADSST-2185KST-133 executes

looped code with zero overhead. No explicit jump instructions

are required to maintain loops.

Two data address generators (DAGs) provide addresses for simultaneous dual operand fetches from data memory and program memory.

Each DAG maintains and updates four address pointers. Whenever

the pointer is used to access data (indirect addressing),

modified by the value of one of four possible modify registers. A

length value may be associated with each pointer to implement

automatic modulo addressing for circular buffers.

Efficient data transfer is achieved with the use of five internal buses:

•

•

•

•

•

The two address buses (PMA and DMA) share a single external

address bus, allowing memory to be expanded off-chip, and the two

data buses (PMD and DMD) share a single external data bus.

memory space and I/O memory space also share the external buses.

Program memory can store both instructions and data, permitting

the ADSST-2185KST-133 to fetch two operands in a single cycle,

one from program memory and one from data memory. The

ADSST-2185KST-133 can fetch an operand from program

memory and the next instruction in the same cycle.

When configured in host mode, the ADSST-2185KST-133 has

a 16-bit Internal DMA port (IDMA port) for connection to

external systems. The IDMA port is made up of 16 data/address

pins and five control pins. The IDMA port provides transparent,

direct access to the DSP’s on-chip program and data RAM.

REV. 0

to support multiprecision computations. The ALU

it is post-

Program Memory Address (PMA) Bus

Program Memory Data (PMD) Bus

Data Memory Address (DMA) Bus

Data Memory Data (DMD) Bus

Result (R) Bus

Byte

An interface to low cost byte-wide memory is provided by the

Byte DMA port (BDMA port). The BDMA port is bidirectional

and can directly address up to four megabytes of external RAM

or ROM for off-chip storage of program overlays or data tables.

The byte memory and I/O memory space interface supports slow

memories and I/O memory-mapped peripherals with programmable

wait state generation. External devices can gain control of external

buses with bus request/grant signals (BR, BGH, and BG). One

execution mode (Go Mode) allows the ADSST-2185KST-133

to continue running from on-chip memory. Normal execution

mode requires the processor to halt while buses are granted.

The ADSST-2185KST-133 can respond to 11 interrupts.

There are up to six external interrupts (one edge-sensitive, two

level-sensitive, and three configurable) and seven internal interrupts generated by the timer, the serial ports (SPORTs), the

Byte DMA port, and the power-down circuitry. There is also a

master RESET signal. The two serial ports provide a complete

synchronous serial interface with optional companding in hardware and a wide variety of framed or frameless data transmit

and receive modes of operation.

Each port can generate an internal programmable serial clock or

accept an external serial clock.

The ADSST-2185KST-133 provides up to 13 general purpose

flag pins. The data input and output pins on SPORT1 can be

alternatively configured as an input flag and an output flag. In

addition, eight flags are programmable as inputs or outputs, and

three flags are always outputs.

A programmable interval timer generates periodic interrupts. A

16-bit count register (TCOUNT) decrements every n processor

cycle, where n is a scaling value stored in an 8-bit register (TSCALE).

When the value of the count register reaches zero, an interrupt is

generated and the count register is reloaded from a 16-bit period

register (TPERIOD).

Serial Ports

The ADSST-2185KST-133 incorporates two complete synchronous

serial ports (SPORT0 and SPORT1) for serial communications

and multiprocessor communication.

Here is a brief list of the capabilities of the ADSST-2185KST-133

SPORTs. For additional information on Serial Ports, refer to

the ADSP-2100 Family User’s Manual, Third Edition.

•

SPORTs are bidirectional and have a separate, double-buffered

transmit and receive section.

•

SPORTs can use an external serial clock or generate their own

serial clock internally.

•

SPORTs have independent framing for the receive and transmit

sections. Sections run in a frameless mode or with frame synchronization signals internally or externally generated. Frame

sync signals are active high or inverted, with either of two

pulsewidths and timings.

•

SPORTs support serial data word lengths from 3 to 16 bits and

provide optional A-law and M-law companding according to

CCITT recommendation G.711.

•

SPORT receive and transmit sections can generate unique

interrupts on completing a data-word transfer.

•

SPORTs can receive and transmit an entire circular buffer of

data with only one overhead cycle per data-word. An interrupt

is generated after a data buffer transfer.

–3–

ADSST-EM-3035

•

SPORT0 has a multichannel interface to selectively receive and

transmit a 24- or 32-word, time-division multiplexed, serial

bitstream.

•

SPORT1 can be configured to have two external interrupts

(IRQ0 and IRQ1) and the Flag In and Flag Out signals. The

internally generated serial clock may still be used in this

configuration.

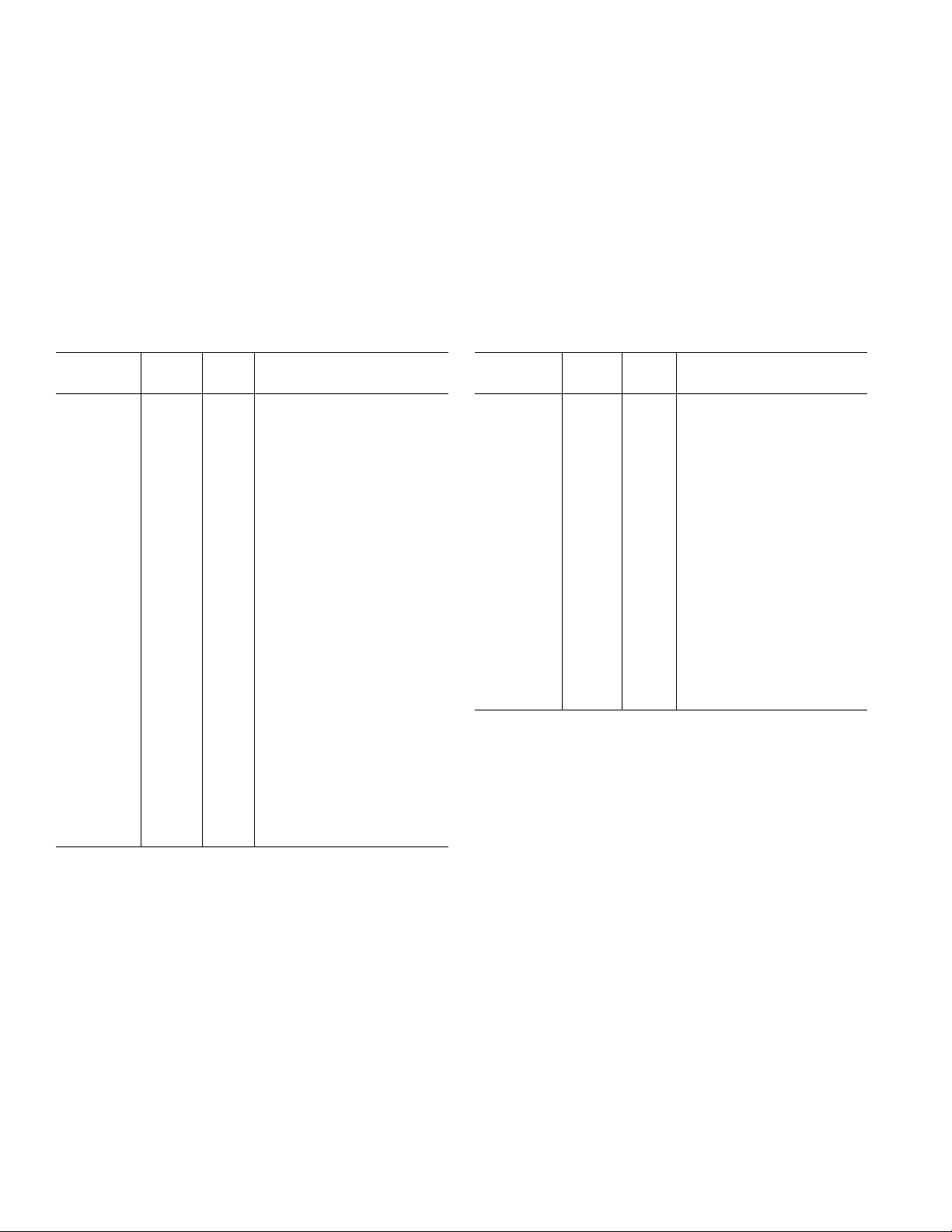

Table I. Common-Mode Pins

Pin Descriptions

The ADSST-2185KST-133 is available in a 100-lead TQFP

package. To maintain maximum functionality and reduce package size and pin count, some serial ports, programmable flags,

interrupt and external bus pins have dual, multiplexed functionality. The external bus pins are configured during RESET only,

while serial port pins are software configurable during program

execution. Flag and interrupt functionality is retained concurrently on multiplexed pins. In cases where pin functionality is

reconfigurable, the default state is shown in plain text; alternate

functionality is shown in italics.

Pin Number Input/

Name(s) of Pins Output Function

RESET 1IProcessor Reset Input

BR 1IBus Request Input

BG 1OBus Grant Output

BGH 1OBus Grant Hung Output

DMS 1OData Memory Select Output

PMS 1O

Program Memory Select Output

IOMS 1OMemory Select Output

BMS 1OByte Memory Select Output

CMS 1OCombined Memory

Select Output

RD 1OMemory Read Enable Output

WR 1OMemory Read Enable Output

IRQ2+PF7

IRQL0+PF5 1 I Level-Sensitive

IRQL1+PF6

IRQE+PF4

1IEdge- or Level-Sensitive

Interrupt Request

Interrupt Requests

1ILevel-Sensitive

Interrupt

Requests

1IEdge-Sensitive

Interrupt Requests

1

1

1

1

PF3 1 I/O Programmable I/O Pin

PF2 (Mode C)

1IProgrammable I/O Pin Mode

Select Input-Checked only

During RESET

PF1 (Mode B)

1IMode Select Input-Checked

only During RESET

Pin Number Input/

Name(s) of Pins Output Function

PF0 (Mode A) 1 I Mode Select Input-Checked

only During RESET

CLKIN, 2 I Clock or Quartz Crystal Input

XTAL

CLKOUT 1 O Processor Clock Output

SPORT0 5 I/O Serial Port I/O Pins

SPORT1 5 I/O Serial Port I/O Pins

IRQ1:0 Edge- or Level-Sensitive

Interrupts

F1, F0 Flag In, Flag Out

2

PWD 1IPower-Down Control Input

PWDACK 1 O Power-Down Control Output

FL0, FL1, 3 O Output Flags

FL2

VDD 16 I VDD and GND

AND

GND

EX-Port 9 I/O For Emulation Use

NOTES

1

Interrupt/Flag pins retain both functions concurrently. If IMASK is set to enable

the corresponding interrupts, the DSP will vector to the appropriate interrupt

vector address when the pin is asserted, either by external devices or set as a

programmable flag.

2

SPORT configuration determined by the DSP System Control Register. Software

configurable.

–4–

REV. 0

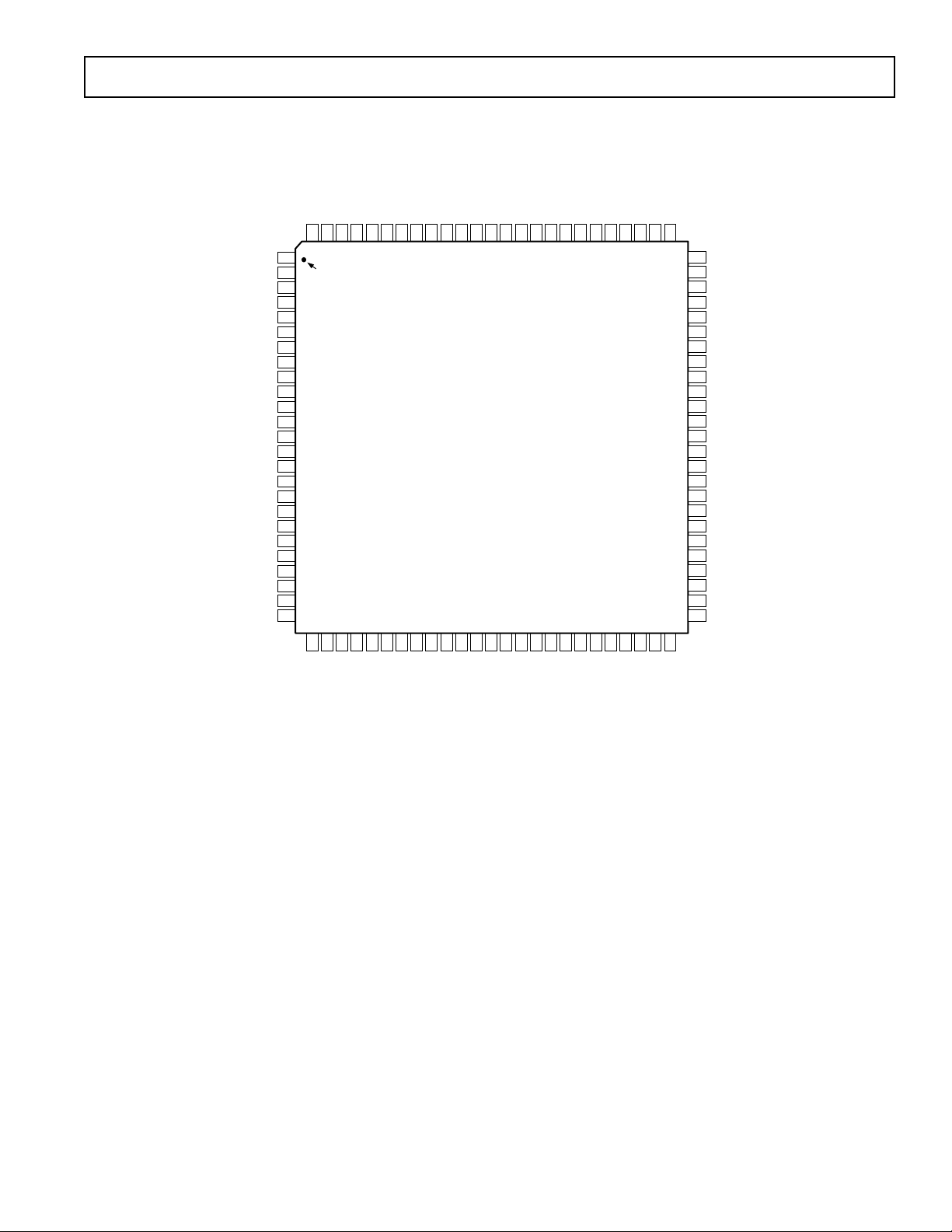

100-Lead TQFP Package Pinout

ADSST-EM-3035

A4/IAD3

A5/IAD4

GND

A6/IAD5

A7/IAD6

A8/IAD7

A9/IAD8

A10/IAD9

A11/IAD10

A12/IAD11

A13/IAD12

GND

CLKIN

XTAL

VDD

CLKOUT

GND

VDD

WR

RD

BMS

DMS

PMS

IOMS

CMS

A0

A3/IAD2

A2/IAD1

A1/IAD0

PWDACK

BGH

9998979695949392919089888786858483828180797877

100

1

PIN 1

2

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

2728293031323334353637383940414243444546474849

26

DT0

GND

IRQL0+PF5

IRQL1+PF6

IRQ2+PF7

IRQE+PF4

PWD

GND

PF1 [MODE B]

PF0 [MODE A]

PF2 [MODE C]

VDD

ADSST-2185KST-133

TOP VIEW

(Not to Scale)

DR0

RFS0

VDD

SCLK0

DT1/FO

TFS0

PF3

TFS1/IRQ1

FL0

RFS1/IRQ0

FL1

FL2

GND

DR1/FI

D23

D22

SCLK1

ERESET

D20

D21

EMS

RESET

GND

EE

D19

ECLK

D18

D17

ELIN

ELOUT

D16

76

50

EINT

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

D15

D14

D13

D12

GND

D11

D10

D9

VDD

GND

D8

D7/IWR

D6/IRD

D5/IAL

D4/IS

GND

VDD

D3/IACK

D2/IAD15

D1/IAD14

D0/IAD13

BG

EBG

BR

EBR

REV. 0

–5–

ADSST-EM-3035

System Interface

Figure 2 shows typical basic system configurations with the

ADSST-2185KST-133, two serial devices, a byte-wide EPROM

and optional external program and data overlay memories (mode

selectable). Programmable wait state generation allows the processor to connect easily to slow peripheral devices. The ADSST2185KST-133 also provides four external interrupts and two serial

ports, or six external interrupts and one serial port. Host Memory

Mode allows access to the full external data bus, but limits addressing to a single address bit (A0). Additional system peripherals can

be added in this mode through the use of external hardware to

generate and latch address signals.

FULL MEMORY MODE

ADSST-2185

1/2x CLOCK

OR

CRYSTAL

SERIAL

DEVICE

SERIAL

DEVICE

KST-133

CLKIN

XTAL

FL0–2

PF3

IRQ2/PF7

IRQE/PF4

IRQL0/PF5

IRQL1/PF6

MODE C/PF2

MODE B/PF1

MODE A/PF0

SPORT1

SCLK1

RFS1 OR IRQ0

TFS1 OR IRQ1

DT1 OR FO

DR1 OR FI

SPORT0

SCLK0

RFS0

TFS0

DT0

DR0

ADDR13–0

DATA23–0

BMS

IOMS

PMS

DMS

CMS

BGH

PWD

PWDACK

BR

BG

A

14

13–0

A0–A21

D

23–16

D

24

15–8

A

10–0

D

23–8

A

13–0

D

23–0

DATA

CS

ADDR

DATA

(PERIPHERALS)

2048 LOCATIONS

CS

ADDR

OVERLAY

MEMORY

DATA

PM SEGMENTS

DM SEGMENTS

BYTE

MEMORY

I/O SPACE

TWO 8K

TWO 8K

Clock Signals

Either a crystal or a TTL-compatible clock signal can clock the

ADSST-2185KST-133.

The CLKIN input cannot be halted, changed during operation,

or operated below the specified frequency during normal

operation. The only exception is while the processor is in the

power-down state. For additional information, refer to Chapter 9,

ADSP-2100 Family User’s Manual, Third Edition, for detailed

information on this power-down feature.

If an external clock is used, it should be a TTL-compatible signal

running at half the instruction rate. The signal is connected to the

processor's CLKIN input. When an external clock is used, the

XTAL input must be left unconnected.

The ADSST-2185KST-133 uses an input clock with a frequency

equal to half the instruction rate; a 20.00 MHz input clock

yields a 25 ns processor cycle (which is equivalent to 40 MHz).

Normally, instructions are executed in a single processor cycle.

All device timing is relative to the internal instruction clock rate,

which is indicated by the CLKOUT signal when enabled.

Because the ADSST-2185KST-133 includes an on-chip oscillator

circuit, an external crystal may be used. The crystal should be

connected across the CLKIN and XTAL pins, with two capacitors

connected as shown in Figure 3. Capacitor values are dependent

on crystal type and should be specified by the crystal manufacturer.

A parallel-resonant, fundamental frequency,

microprocessor-

grade crystal should be used.

CLKIN XTAL CLKOUT

DSP

HOST MEMORY MODE

ADSST-2185

1/2x CLOCK

OR

CRYSTAL

SERIAL

DEVICE

SERIAL

DEVICE

SYSTEM

INTERFACE

OR

CONTROLLER

CLKIN

XTAL

FL0–2

PF3

IRQ2/PF7

IRQE/PF4

IRQL0/PF5

IRQL1/PF6

MODE C/PF2

MODE B/PF1

MODE A/PF0

SCLK1

RFS1 OR IRQ0

TFS1 OR IRQ1

DT1 OR FO

DR1 OR FI

SCLK0

RFS0

TFS0

DT0

DR0

IRD/D6

IWR/D7

IS/D4

IAL/D5

IACK/D3

IAD15–0

16

KST-133

SPORT1

SPORT0

IDMA PORT

ADDR0

DATA23–8

BMS

IOMS

PMS

DMS

CMS

BGH

PWD

PWDACK

1

16

BR

BG

Figure 2. Basic System Interface

Recommended Operating Conditions

A Grade B Grade

Parameters Min Max Min Max Unit

Supply Voltage 4.5 5.5 4.5 5.5 V

V

DD

T

Ambient 0 +70 –40 +85 °C

AMB

Operating Temperature

Figure 3. External Crystal Connections

A clock output (CLKOUT) signal is generated by the processor

at the processor’s cycle rate. This can be enabled and disabled by

the CLKODIS bit in the SPORT0 Autobuffer Control Register.

Reset

The RESET signal initiates a master reset of the ADSST2185KST-133. The RESET signal must be asserted during the

power-up sequence to assure proper initialization. RESET dur-

ing initial power-up must be held long enough to allow the

internal clock to stabilize. If RESET is activated any time after

power-up, the clock continues to run and does not require stabilization time.

The power-up sequence is defined as the total time required for

the crystal oscillator circuit to stabilize after a valid VDD is

applied to the processor, and for the internal phase-locked loop

(PLL) to lock onto the specific crystal frequency. A minimum of

2000 CLKIN cycles ensures that the PLL has locked, but does

not include the crystal oscillator start-up time. During this powerup sequence, the RESET signal should be held low. On any

subsequent resets, the RESET signal must meet the minimum

pulsewidth specification, t

RSP

.

The RESET input contains some hysteresis; however, if you use

an RC circuit to generate your RESET signal, the use of an

external Schmidt trigger is recommended. The master reset sets

all internal stack pointers to the empty stack condition, masks

all interrupts and clears the MSTAT register. When RESET is

released, if there is no pending bus request and the chip is configured for booting, the boot-loading sequence is performed.

The first instruction is fetched from on-chip program memory

location 0x0000 once boot loading completes.

–6–

REV. 0

Loading...

Loading...