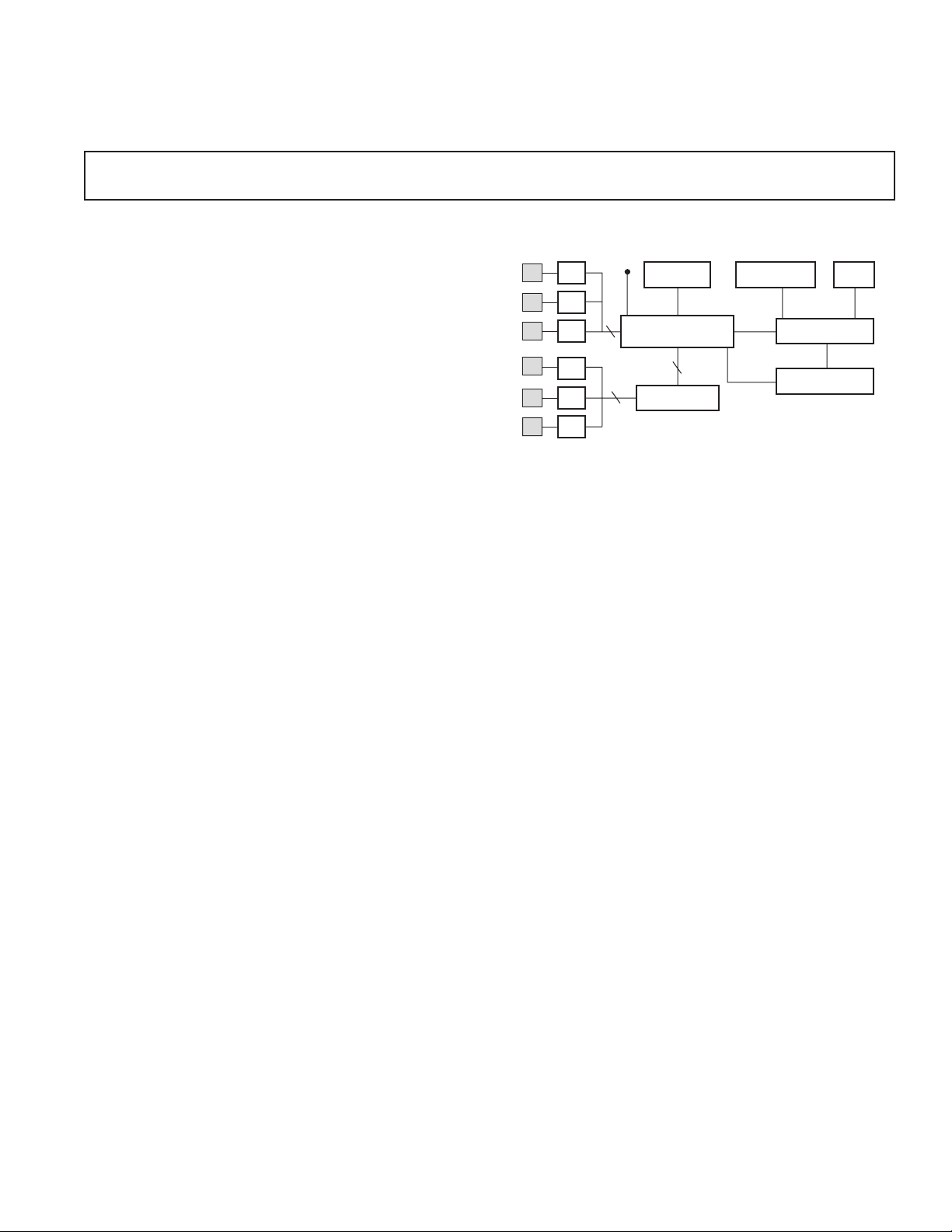

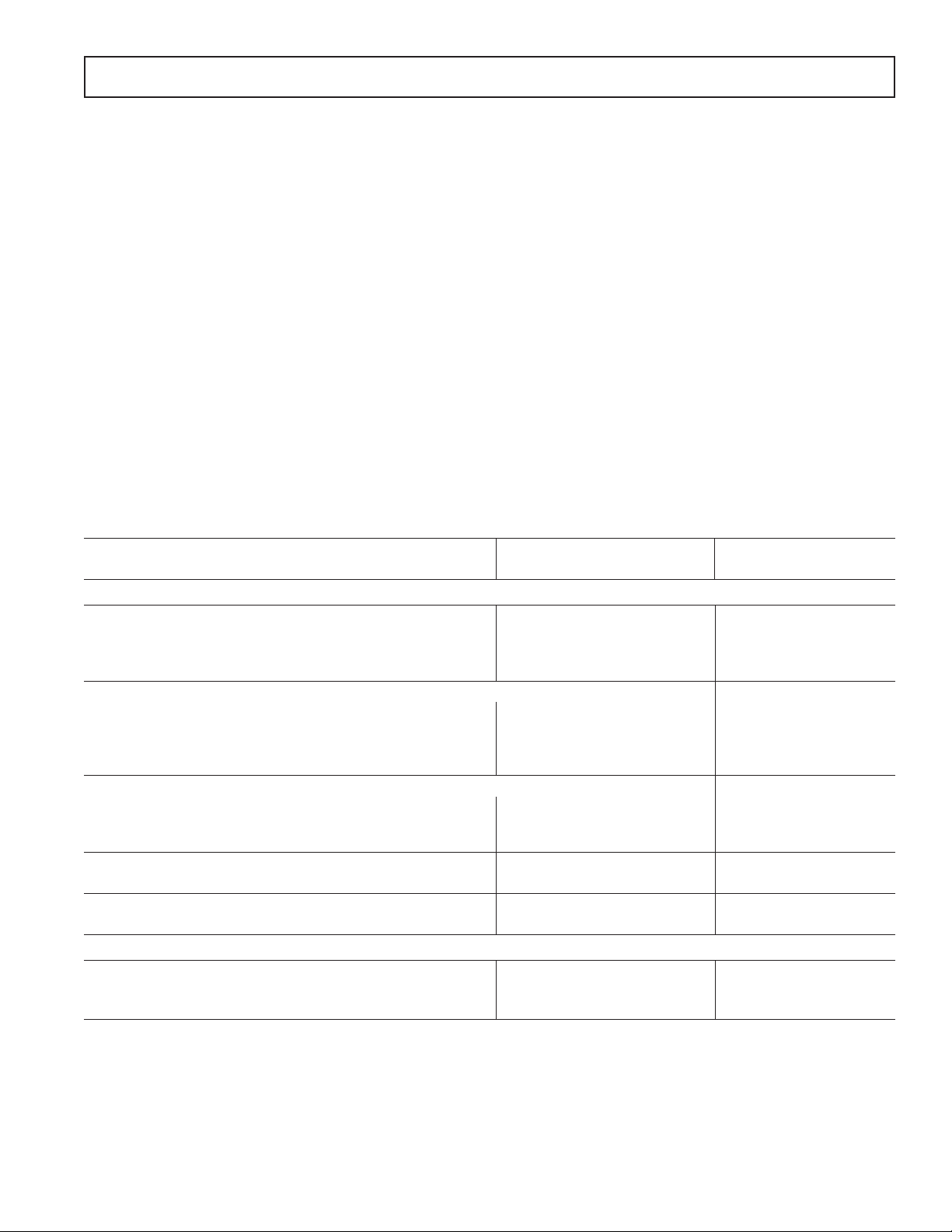

Three-Phase Energy

E-PULSE

ADSST-EM-2030

µCONTROLLER

OPTICAL PORT

OP AMP + MUX

COUNTER LCD DISPLAY RTC

PT

PT

PT

CT

CT

CT

POLY PHASE ENERGY METER USING THE ADSST-EM-2030

a

FEATURES

3-Phase, 4-Wire Metering IC

High Accuracy Support for 50 Hz/60 Hz, IEC1036

Design Accuracy:

0.5% over 5% of Ib to 6% of Ib

0.65% over 2% of Ib to 5% of Ib

Measures:

kWh

kW

rms Voltage of Each Phase

rms Current of Each Phase

Phase and Nonlinearity Compensation for CTs

Potentiometer-Free Design

SPI Communication for:

Data to Microcontroller

Calibration

Programmable E-Pulse

Drive for:

Electromechanical Counter

2-Phase Stepper Motor Counter

Low Power (50 mW Typ)

Meter Chipset

ADSST-EM-2030

FUNCTIONAL BLOCK DIAGRAM

*

GENERAL DESCRIPTION

ADSST-EM-2030 is a highly accurate and low cost phase

energy measurement IC intended to be used in 3-phase, 4-wire

systems. When used with an op amp and a multiplexer, the

ADSST-EM-2030 surpasses the accuracy requirement of the

IEC1036 standard.

ADSST-EM-2030 is a MicroConverter

troller, 6-channel, 12-bit ADC, SPI port, program memory and

Flash for storage of constants. The only analog circuitry used in

ADSST-EM-2030 is the ADC. All other signal processing is carried

out in digital domain. This provides superior accuracy over extreme

environmental conditions and time.

ADSST-EM-2030 can drive an electromechanical counter or a

2-phase stepper motor counter, or can be interfaced to a

microcontroller to build a feature-rich meter with LCD, maximum

demand, time of use, and communication.

*Protected by U.S.Patent No. 5,969,657; other patents pending.

MicroConverter is a registered trademark of Analog Devices.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

®

consisting of a microcon-

Ratio, phase, and nonlinearity errors of the CTs are compensated

for by using software. This reduces the cost of CTs and reduces

calibration time caused by unreliable potentiometers.

Because the ADSST-EM-2030 is a low power device, it can be

powered by a simple R-C power supply, reducing the cost of

operation.

ADSST-EM-2030 supplies average real power information on

the low frequency outputs F1 and F2. These logic outputs can

be used to drive an electromechanical counter. The CF logic pin

gives the instantaneous real power information. This output is

intended to be used for calibration.

ADSST-EM-2030 is available in a 28-lead SSOP package.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

ADSST-EM-2030

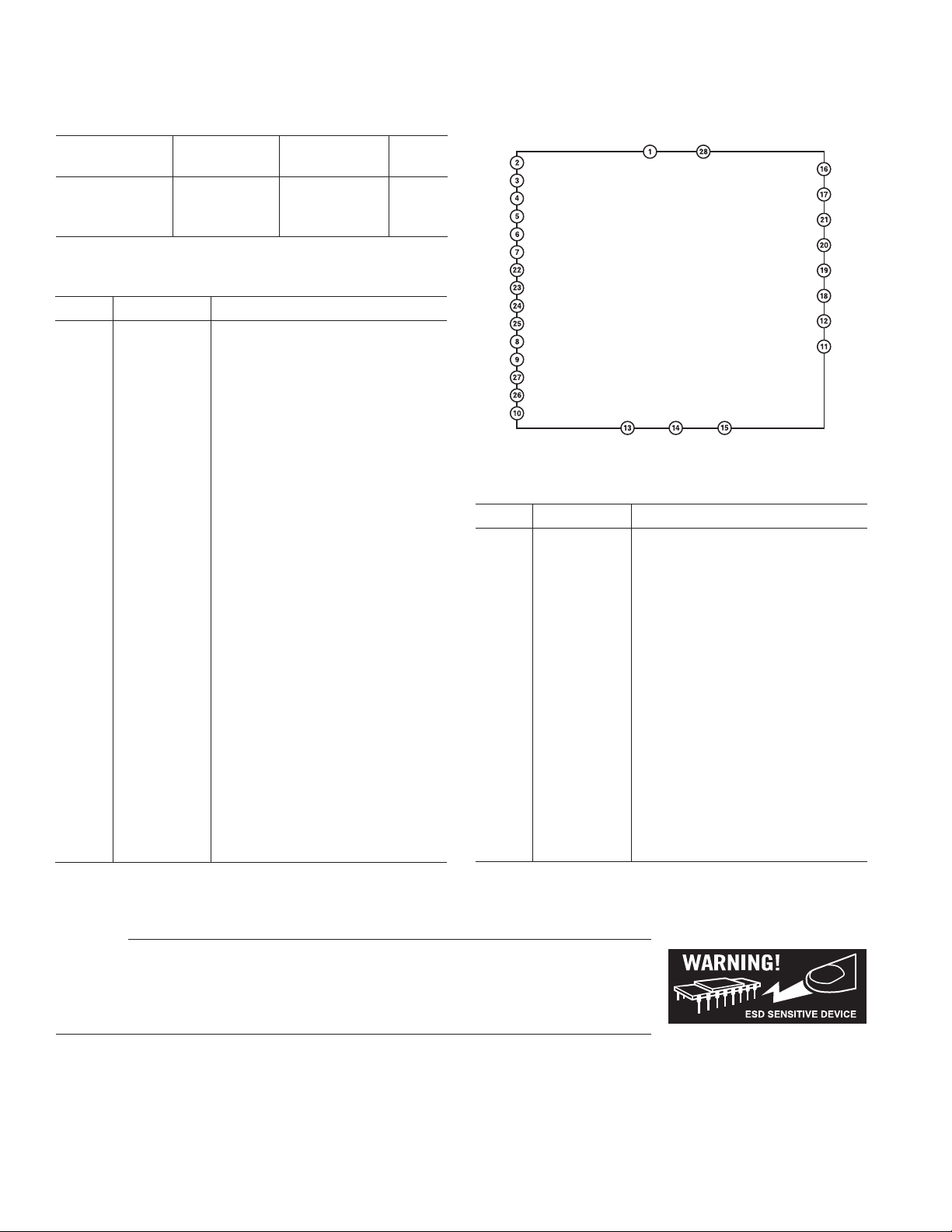

ORDERING GUIDE

Model Temperature Package Package

Range Description Option

ADSST-EM-2030 –40°C to +85°C Tiny Shrink RU–28

Small Outline

Package

PIN FUNCTION DESCRIPTION

Pin No. Mnemonic Description

1 DGND Digital Ground

2DLOAD Used to Enable Serial Download of

Program Memory

3GAIN 1 Logic Channels Output for

Multiplexer to Switch Gain for

A-Phase Current

4GAIN 2 Logic Channels Output for

Multiplexer to Switch Gain for

B-Phase Current

5 TAMP Logic Output Indicating that One

More Current Is Reversed

6CFCalibration Frequency Logic Output.

This gives instantaneous real power

information and can be used for

calibration.

7GAIN 3 Logic Channels Output for

Multiplexer to Switch Gain for

C-Phase Current

8, 9 F1, F2 Low Frequency Logic Outputs. F1

and F2 provide average real power

information. The logic outputs can

be used to drive electromechanical

counters and 2-phase stepper motors.

10 RESET System Reset

11 APHV A-Phase Voltage Input

12 APHC A-Phase Current Input

13 AVDD Analog Positive Supply

14 AGND Analog Ground

15 AGND Analog Ground

16 VREF Input for External Voltage Reference

PIN CONFIGURATION

DLOAD

GAIN 1

GAIN 2

TA M P

CF

GAIN 3

SS

MISO

MOSI

SCLK

F1

F2

XTAL2

XTAL1

RESET

DGND DVDD

AV DD

VREF

CREF

CPHC

CPHV

BPHC

BPHV

APHC

APHV

AGND AGND

PIN FUNCTION DESCRIPTION (continued)

Pin No. Mnemonic Description

17 CREF Filter Capacitor for Reference

18 BPHV B-Phase Voltage Input

19 BPHC B-Phase Current Input

20 CPHV C-Phase Voltage Input

21 CPHC C-Phase Current Input

22 SS This Logic Signal conveys to ADSST-

EM-2030 that data transfer on SPI is

requested.

23 MISO Data Output on SPI from

ADSST-EM-2030

24 MOSI

25 SCLK Clock for SPI. This clock is generated

by an external microcontroller when

the data transfer to or from ADSST-

EM-2030 takes place.

26 XTAL1 Crystal Oscillator

27 XTAL2 Crystal Oscillator

28 DVDD Digital Positive Supply

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate

on the human body and test equipment and can discharge without detection. Although the ADSSTEM-2030 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

REV. 0–2–

ADSST-EM-2030

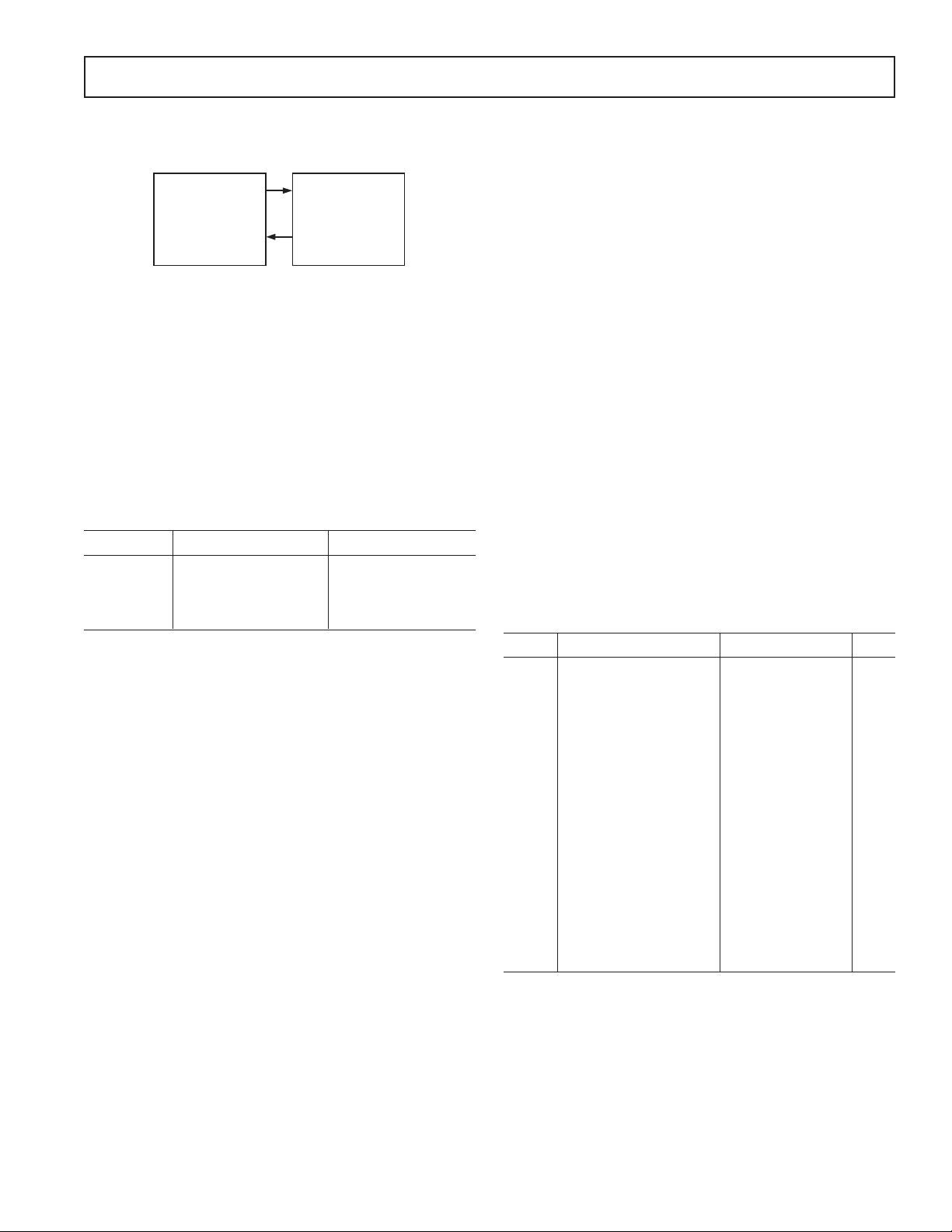

SERIAL PERIPHERAL INTERFACE (SPI)

The SPI bus available on the ADSST-EM-2030 is useful to

communicate to an external microcontroller as shown in Figure 1.

SLAVE

ADSST-EM-2030

MASTER

MICROCONTROLLER

Figure 1. SPI Communication between ADSST-EM-2030

and Microcontroller

Here, the microcontroller functions as master and the ADSSTEM-2030 is a slave for this protocol. Using this communication

port, the microcontroller will be able to read and write to the

ADSST-EM-2030 to perform the following functions:

•

Calibrate the meter

•

Configure the ADSST-EM-2030 chipset

•

Read measured parameters from the ADSST-EM-2030 chipset

Four pins are used on the ADSST-EM-2030 chipset for the

communication, and are shown Table I.

Table I. Pin Description for SPI Communication Port

Pin No. Mnemonic Description

22 SS Select

23 MISO Output

24 MOSI Input

25 SCLK SPI Clock

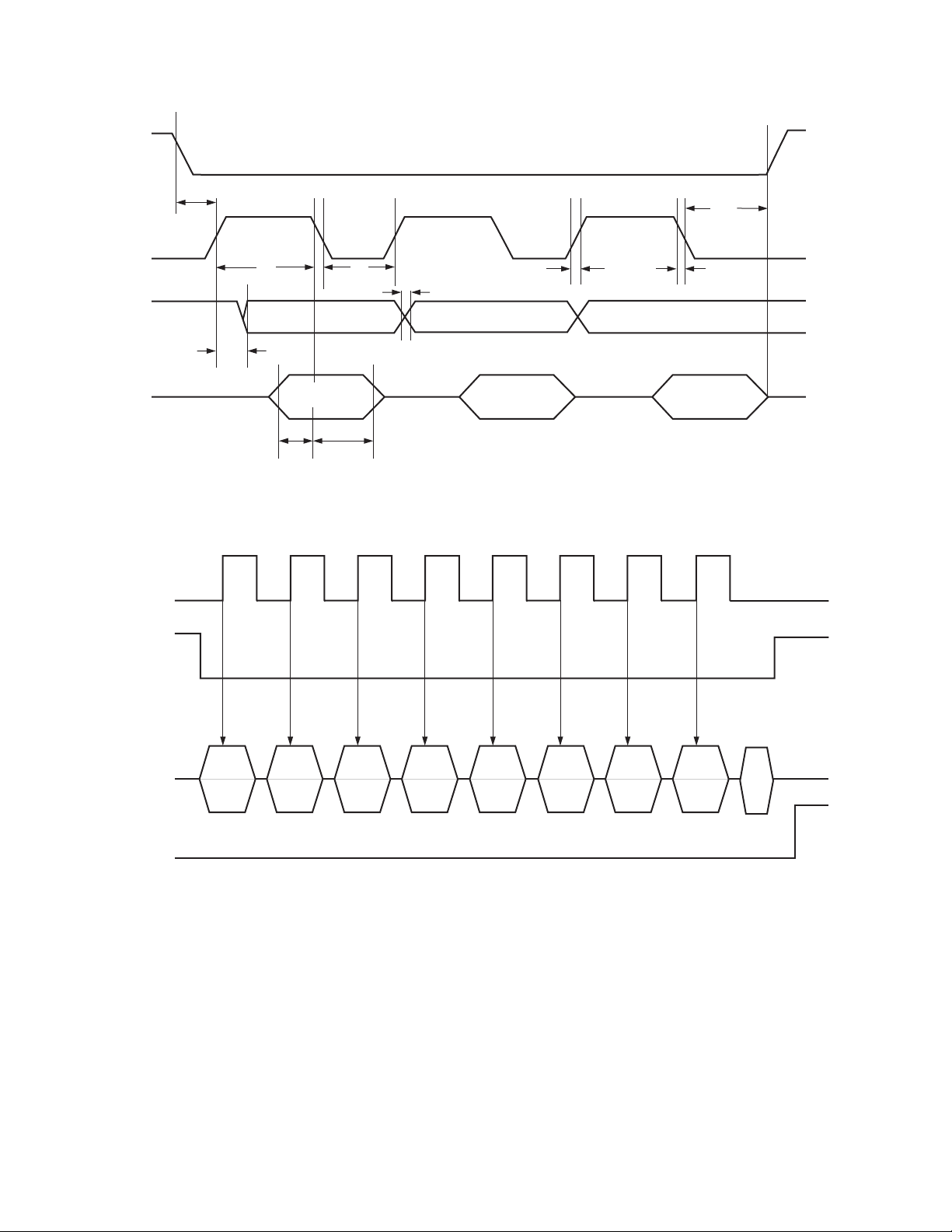

TIMING SPECIFICATIONS

This section contains timing information for the ADSST-EM2030 chipset.

General Notes

Use the exact timing information given. Do not attempt to

derive parameters from the addition or subtraction of others.

While addition or subtraction would yield meaningful results for

an individual device, the values given in this data sheet reflect

statistical variations and worst cases. Consequently, parameters

cannot be added up meaningfully to derive longer times.

Timing Notes

Switching characteristics specify how the processor changes its

signals. Designers have no control on this timing—circuitry external to the processor must be designed for compatibility with these

signal characteristics. These characteristics can be used to ensure

that any timing requirement of a microcontroller connected to

the chipset is satisfied.

Timing requirements apply to signals that are controlled by circuitry

external to the chipset, such as the data input for a read operation.

Timing requirements guarantee that the chipset operates correctly with the external microcontroller.

Data Access

Data can be written or read to the ADSST-EM-2030 chipset only

when the SS pin is low. Since the chipset is a slave, the external

controller must bring the SS pin low, the SCLK clock should be

sent to clock in or clock out the data. For sending the data to the

chipset, data should be sent on MOSI pin; for receiving the data

from the chipset, data should be collected on MISO pin.

With the external microcontroller as the master for the SPI

communication, the microcontroller should send eight successive clocks to the ADSST-EM-2030 every 5 ms. At this instant,

the microcontroller may either send a command or data or may

receive an acknowledgment followed by data from the chipset.

The ADSST-EM-2030 maintains a time gap of 5 ms between

transmission of two successive bytes to or from the microcontroller.

This helps in avoiding clashing o f interrupts while the chipset

and the microcontroller are executing their respective tasks.

Table II. SPI Pin Timings

Timing Parameter Min Typ Max Unit

t

SS

t

SC

SS to SCLOCK Edge 0 ns

SCLOCK Low

Pulsewidth 300 ns

t

SH

SCLOCK High

Pulsewidth 300 ns

t

DAV

Data Output Valid

after SCLOCK Edge 50 ns

t

DSU

Data Input Setup Time

before SCLOCK Edge 100 ns

t

DHD

Data Input Hold Time

before SCLOCK Edge 100 ns

t

t

t

t

t

DF

DR

SR

SF

SFS

Data Output Fall Time 10 25 ns

Data Output Rise Time 10 25 ns

SCLOCK Rise Time 10 25 ns

SCLOCK Fall Time 10 25 ns

SS High after

SCLOCK Edge 0 ns

REV. 0

–3–

ADSST-EM-2030

SS

t

SS

t

DF

SCLK

t

SFS

MISO

MOSI

SCLOCK

SS

t

SH

t

DAV

t

SC

MSB

MSB

t

DSUtDHD

t

DF

t

DR

BITS6–1 LSB

BITS 6–1

Figure 2. SPI Communication Port Timing

t

SR

t

SF

LSB

SAMPLE INPUT

DATA OUTPUT

SPI INTERRUPT

FOR 8712S

MSB BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 LSB ?

Figure 3. SPI Timing for Data Transmission Byte

SPI FUNCTIONS

Three specific functions can be performed on the SPI communication port on the ADSST-EM-2030 chipset:

Data Read—The external microcontroller can read the data

from the ADSST-EM-2030 by sending specific commands; this

includes metering data, constants, and so on.

Data Write—The external microcontroller can send data to the

ADSST-EM-2030 to be stored in its internal nonvolatile memory;

this includes calibration and configuration constants, and so on.

Special Commands—The external microcontroller can send

special commands to the ADSST-EM-2030 for performing specific

functions. These commands do not have any data.

Data Read

The microcontroller being the master for the SPI communication,

has to send the desired commands for getting data from ADSSTEM-2030. For the data transfer to take place, the following

sequence of operations must take place:

1. The microcontroller should send the specific command to

the ADSST-EM-2030 chipset to read the desired data.

2. The ADSST-EM-2030 will first respond with an acknowledgment to the microcontroller within 5 ms that it has

received the command. To send the acknowledgment, the

ADSST-EM-2030 adds 0x30 to the received command,

and which is then sent back to the microcontroller.

REV. 0–4–

ADSST-EM-2030

3. If the microcontroller does not get this acknowledgment from the

ADSST-EM-2030 within 5 ms then the microcontroller may

transmit this command to read the same data again.

4. After being sensed by the microcontroller, the ADSST-EM-2030

sends an acknowledgment to the microcontroller, the chipset

then prepares a packet of 10 bytes of requested data and starts

transmitting the bytes one by one at intervals of 5 ms. This

packet of 10 bytes also includes a header as the first byte of the

packet and checksum as the last byte.

5. The microcontroller can strip the data from this packet, compute

the checksum, and compare it with the last byte in the packet.

If the checksum does not match, the microcontroller should

then send the command again to ADSST-EM-2030 chipset.

The complete process of reading a packet of data should take

60 ms. The next command from the microcontroller to the

ADSST-EM-2030 can be sent immediately after receipt of data

or wait for the desired amount of time. The amount of time the

microcontroller should wait for the next command to be sent to

the ADSST-EM-2030 is purely dependent on the execution

of other functions on the microcontroller. It may be sufficient

for the microcontroller to collect data from the chipset after

Table III. Read Commands to ADSST-EM-2030 on SPI

Function ADSST-EM-2030 from C from ADSST-EM-2030

CONSTANTS

GAIN CALIBRATION CONSTANTS

Read Voltage Gain Constants 0x01 6

Read Low Gain Current Constants 0x02 6

Read High Gain Current Constants 0x03 6

POWER CALIBRATION CONSTANTS AT HIGH CURRENT RANGE

A-Phase Power Constant at High Current

(Including E-Pulse and Counter Pulse Constant) 0x07 4

B-Phase Power Constant at High Current 0x09 2

C-Phase Power Constant at High Current 0x0B 2

POWER CALIBRATION CONSTANTS AT LOW CURRENT RANGE

A-Phase Power Constant at Low Current 0x06 2

B-Phase Power Constant at Low Current 0x08 2

C-Phase Power Constant at Low Current 0x0A 2

PHASE COMPENSATION COEFFICIENTS

Read A-, B-, and C-Phase Coefficients 0x15 6

DC OFFSET CONSTANTS

Read DC Offset Constants 0x0E 6

INSTANTANEOUS PARAMETERS

Read Voltages for Phase A, B, and C 0x0F 6

Read Currents for Phase A, B, and C 0x10 6

Read Energy and Power for Phase A, B, and C 0x11 8

every second. The remaining time may be used by the microcontroller to perform other housekeeping functions.

For example, if the command sent by the microcontroller is 0x01,

the ADSST-EM-2030 adds 0x30 to it, making it 0x31, and sends

this to the microcontroller as an acknowledgment.

The data packet structure created by the ADSST-EM-2030 has

10 bytes. The first byte is a packet start byte (0xEE) and the last

byte is a checksum byte.

< START of Packet (0xEE) >< 8 Bytes of Data>

< CHECKSUM >

The checksum is calculated by adding the first nine bytes, including the packet start byte.

st

CHECKSUM = 1

Table III shows various commands that can be sent to the ADSSTEM-2030 chipset by the microcontroller on the SPI communication

port. The chipset returns a specific number of bytes for each data

parameter specified, in the data column of the table. The data

that can be read from the chipset could be calibration constants

or instantaneous data.

Command to Number of Data Bytes

nd

+ 2

+ ...... ...... + 9th Byte

REV. 0

–5–

ADSST-EM-2030

Data Structure in the Packet

The ADSST-EM-2030 sends out eight bytes of data for every command. The last bytes of a parameter with a 6-byte structure are

kept at zero and should be neglected.

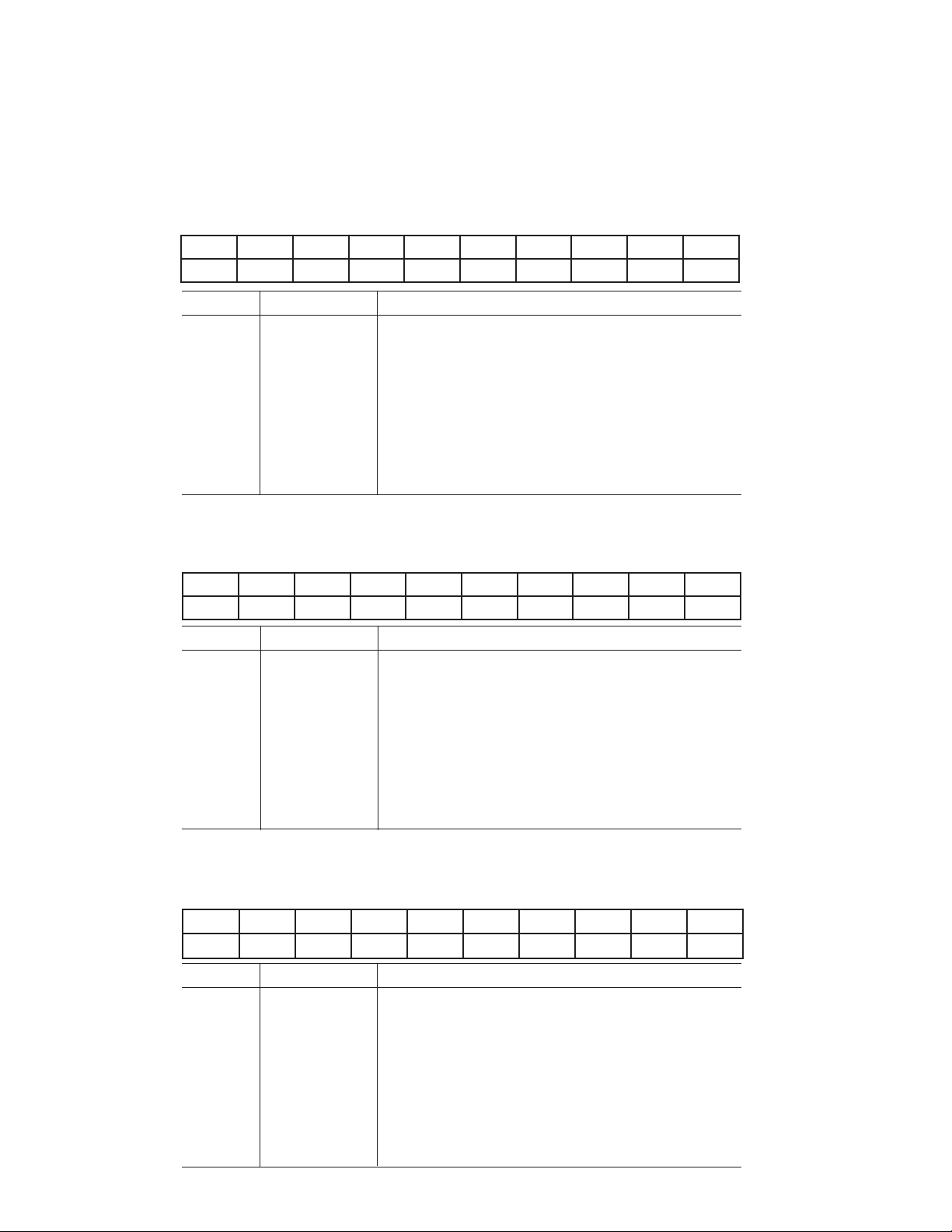

Table IV. Byte Wise Packet Data Structure for Voltage Gain Constants

Command to ADSST-EM-2030: 0x01

Acknowledgment from ADSST-EM-2030: 0x31

123456789 01

BPSSMVASLVASMVBSLVBSMVCSLVCVLNVLNMUSC

Byte No. Name Description

1 SPB Start Packet Byte (0xEE)

2 AVMS Voltage Constant for A-Phase – MSB

3 AVLS Voltage Constant for A-Phase – LSB

4 BVMS Voltage Constant for B-Phase – MSB

5 BVLS Voltage Constant for B-Phase – LSB

6 CVMS Voltage Constant for C-Phase – MSB

7 CVLS Voltage Constant for C-Phase – LSB

8 NLV No Legal Value (0x00)

9 NLV No Legal Value (0x00)

10 CSUM Checksum

Table V. Byte Wise Packet Data Structure for Low Gain Current Constants

Command to ADSST-EM-2030: 0x02

Acknowledgment from ADSST-EM-2030: 0x32

123456789 01

BPSMLIALLIAMLIBLLIBMLICLLICVLNVLNMUSC

Byte No. Name Description

1 SPB Start Packet Byte (0xEE)

2 AILM Current Constant for A-Phase – Low Gain – MSB

3 AILL Current Constant for A-Phase – Low Gain – LSB

4 BILM Current Constant for B-Phase – Low Gain – MSB

5 BILL Current Constant for B-Phase – Low Gain – LSB

6 CILM Current Constant for C-Phase – Low Gain – MSB

7 CILL Current Constant for C-Phase – Low Gain – LSB

8 NLV No Legal Value (0x00)

9 NLV No Legal Value (0x00)

10 CSUM Checksum

Table VI. Byte Wise Packet Data Structure for High Gain Current Constants

Command to ADSST-EM-2030: 0x03

Acknowledgment from ADSST-EM-2030: 0x33

123456789 01

BPSMHIALHIAMHIBLHIBMHICLHICVLNVLNMUSC

Byte No. Name Description

1 SPB Start Packet Byte (0xEE)

2 AIHM Current Constant for A-Phase – High Gain – MSB

3 AIHL Current Constant for A-Phase – High Gain – LSB

4 BIHM Current Constant for B-Phase – High Gain – MSB

5 BIHL Current Constant for B-Phase – High Gain – LSB

6 CIHM Current Constant for C-Phase – High Gain – MSB

7 CIHL Current Constant for C-Phase – High Gain – LSB

8 NLV No Legal Value (0x00)

9 NLV No Legal Value (0x00)

10 CSUM Checksum

REV. 0–6–

Loading...

Loading...