Analog Devices ADSP-21msp58 Datasheet

a

DSP Microcomputers

ADSP-21msp58/59

FEATURES

38 ns Instruction Cycle Time (26 MIPS) from 13.00 MHz

Crystal

ADSP-2100 Family Code and Function Compatible with

New Instruction Set Enhanced for Bit Manipulation

Instructions, Multiplication Instructions, Biased

Rounding, and Global Interrupt Masking

2K 3 24 Words of On-Chip Program Memory RAM

2K 3 16 Words of On-Chip Data Memory RAM

4K 3 24 Words of On-Chip Program Memory ROM

(ADSP-21msp59 Only)

8-Bit Parallel Host Interface Port

Analog Interface Provides:

16-Bit Sigma-Delta ADC and DAC

Programmable Gain Stages

On-Chip Anti-Aliasing & Anti-Imaging Filters

8 kHz Sampling Frequency

65 dB ADC, SNR and THD

72 dB DAC, SNR and THD

425 mW Typical Power Dissipation @ 5.0 V @ 38 ns

<1 mW Powerdown Mode with 100 Cycle Recovery

Dual Purpose Program Memory for Both Instruction

and Data Storage

Independent ALU, Multiplier/Accumulator, and Barrel

Shifter Computational Units

Two Independent Data Address Generators

Powerful Program Sequencer Provides:

Zero Overhead Looping

Conditional Instruction Execution

Two Double-Buffered Serial Ports with Companding

Hardware, One Serial Port (SPORT0) has Automatic

Data Buffering

Programmable 16-Bit Interval Timer with Prescaler

Programmable Wait State Generation

Automatic Booting of Internal Program Memory from

Byte-Wide External Memory, e.g., EPROM, or

Through Host Interface Port

Stand-Alone ROM Execution (ADSP-21msp59 Only)

Single-Cycle Instruction Execution

Single-Cycle Context Switch

Multifunction Instructions

Three Edge- or Level-Sensitive External Interrupts

Low Power Dissipation in Standby Mode

100-Lead TQFP

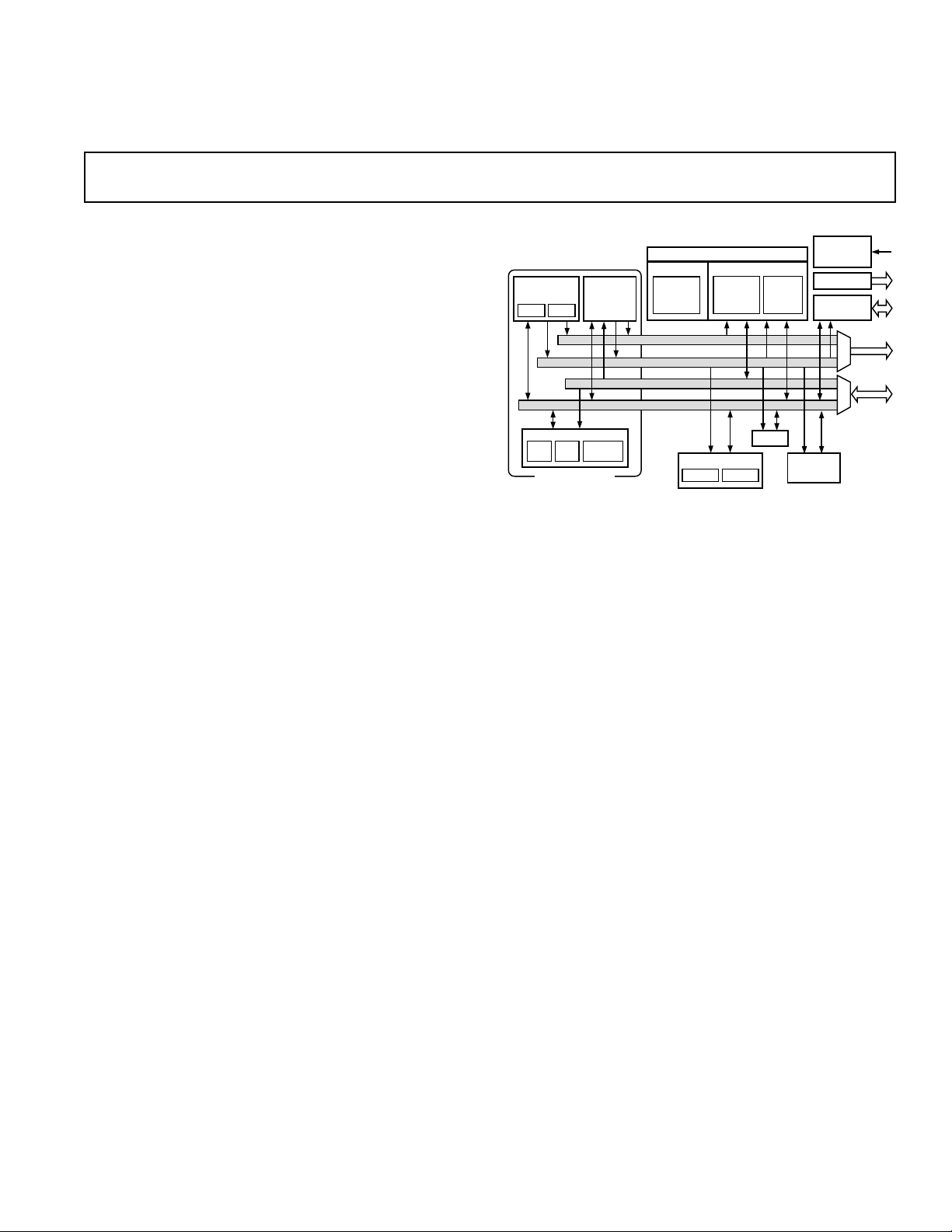

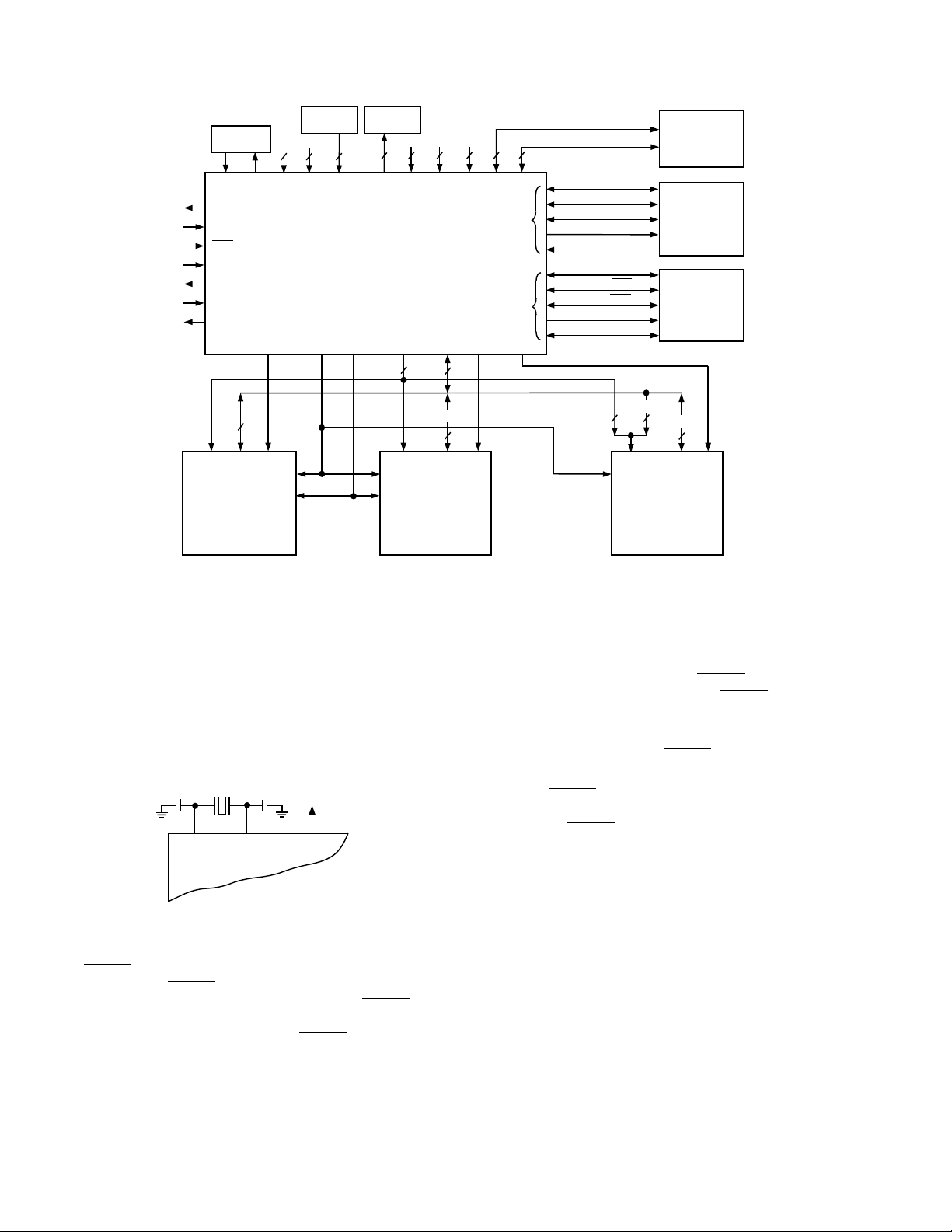

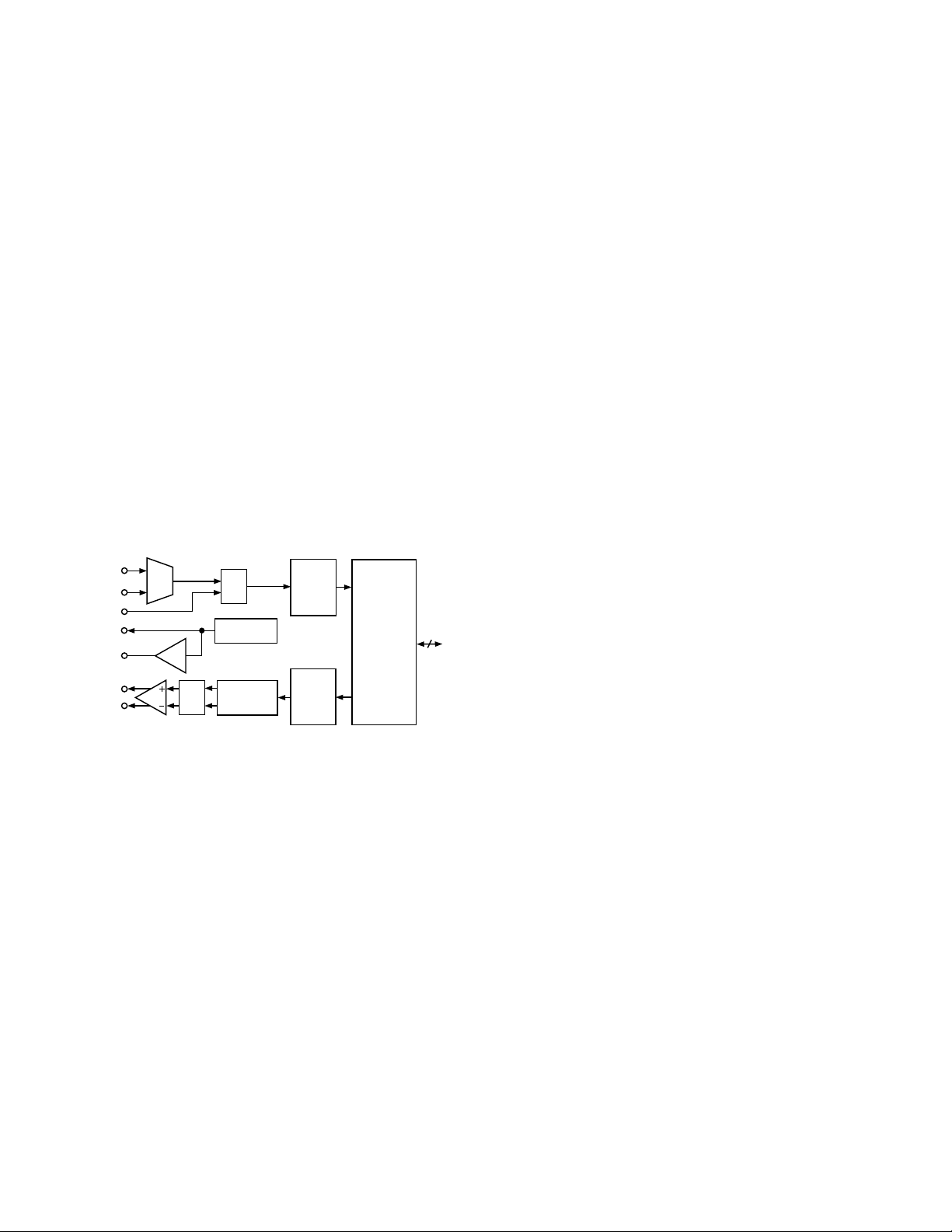

FUNCTIONAL BLOCK DIAGRAM

POWERDOWN

INTERFACE

HOST

INTERFACE

PORT

CONTROL

LOGIC

FLAG

ANALOG

EXTERNAL

ADDRESS

BUS

EXTERNAL

DATA

BUS

DATA

ADDRESS

GENERATORS

DAG 1 DAG 2

ARITHMETIC UNITS

ALU

MAC

ADSP-2100 BASE

ARCHITECTURE

ADSP-21msp59

PROGRAM

SEQUENCER

PROGRAM MEMORY ADDRESS

DATA MEMORY ADDRESS

PROGRAM MEMORY DATA

DATA MEMORY DATA

SHIFTER

PROGRAM

MEMORY

4K x 24

(ROM)

MEMORY

PROGRAM

SERIAL PORTS

SPORT 0

ADSP-21msp58/59

MEMORY

2K x 24

TIMER

SPORT 1

DATA

MEMORY

2K x 16

GENERAL DESCRIPTION

The ADSP-21msp58 and ADSP-21msp59 Mixed-Signal Processors (MSProcessor

®

DSPs) are fully integrated, single-chip

DSPs complete with a high performance analog front end. The

ADSP-21msp58/59 Family is optimized for voice band applications such as Speech Compression, Speech Processing, Speech

Recognition, Text-to Speech, and Speech-to-Text conversion.

The ADSP-21msp58/59 combines the ADSP-2100 base architecture (three computation units, data address generators, and

program sequencer) with two serial ports, a host interface port,

an analog front end, a programmable timer, extensive interrupt

capability, and on-chip program and data memory.

The ADSP-21msp58 provides 2K words (24-bit) of program

RAM and 2K words (16-bit) of data memory. The ADSP21msp59 provides an additional 4K words (24-bit) of program

ROM. The ADSP-21msp58/59 integrates a high performance

analog codec based on a single chip, voice band codec, the

AD28msp02. Powerdown circuitry is also provided to meet the

low power needs of battery operated portable equipment. The

ADSP-21msp58/59 is available in a 100-pin TQFP package

(thin quad flat package).

In addition, the ADSP-21msp58/59 supports new instructions,

which include bit manipulations–bit set, bit clear, bit toggle,

bit test–new ALU constants, new multiplication instruction

(x squared), biased rounding, and global interrupt masking.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

MSProcessor is a registered trademark of Analog Devices, Inc.

© Analog Devices, Inc., 1995

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

ADSP-21msp58/59

DIGITAL ARCHITECTURE OVERVIEW

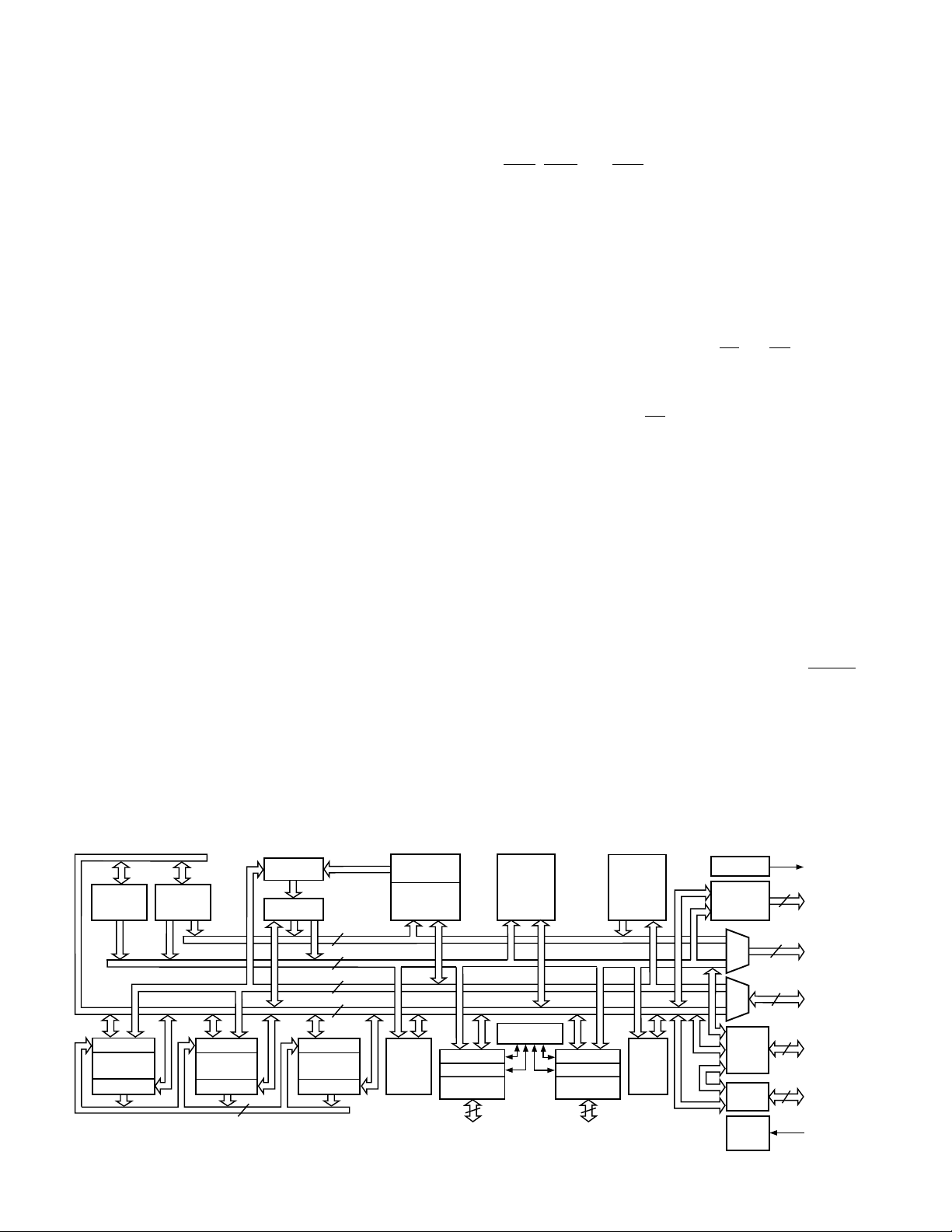

Figure 1 is an overall block diagram of the ADSP-21msp58/59.

The processors contain three independent computational units:

the ALU, the multiplier/accumulator (MAC), and the shifter.

The computational units process 16-bit data directly and have

provisions to support multiprecision computations. The ALU

performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs singlecycle multiply, multiply/add, and multiply/subtract operations.

The shifter performs logical and arithmetic shifts, normalization,

denormalization, and derive exponent operations. The shifter

can be used to efficiently implement numeric format control including multiword floating-point representations.

The internal result (R) bus directly connects the computational

units so that the output of any unit may be the input of any unit

on the next cycle.

A powerful program sequencer and two dedicated data address

generators ensure efficient use of these computational units.

The sequencer supports conditional jumps, subroutine calls,

and returns in a single cycle. With internal loop counters and

loop stacks, the ADSP-21msp58/59 executes looped code with

zero overhead—no explicit jump instructions are required to

maintain the loop.

Two data address generators (DAGs) provide addresses for simultaneous dual operand fetches (from data memory and program memory). Each DAG maintains and updates four address

pointers. Whenever the pointer is used to access data (indirect

addressing), it is post-modified by the value of one of four

modify registers. A length value may be associated with each

pointer to implement automatic modulo addressing for circular

buffers. The circular buffering feature is also used by the serial

ports for automatic data transfers to (and from) on-chip

memory.

Efficient data transfer is achieved with the use of five internal

buses:

• Program Memory Address (PMA) Bus

• Program Memory Data (PMD) Bus

• Data Memory Address (DMA) Bus

• Data Memory Data (DMD) Bus

• Result (R) Bus

The two address buses (PMA, DMA) share a single external address bus, allowing memory to be expanded off chip, and the

two data buses (PMD, DMD) share a single external data bus.

The

BMS, DMS, and PMS signals indicate which memory

space the external buses are being used for.

Program memory can store both instructions and data, permit-

ting the ADSP-21msp58/59 to fetch two operands in a single

cycle, one from program memory and one from data memory.

The ADSP-21msp58/59 can fetch an operand from on-chip

program memory and the next instruction in the same cycle.

The memory interface supports slow memories and memorymapped peripherals with programmable wait state generation.

External devices can gain control of the processors’ buses with

the use of the bus request/grant signals (

BR and BG). Bus grant

has two modes of operation. If GoMode is enabled in the MSTAT

register, instruction execution continues from internal memory.

If GoMode is disabled, the processor stops instruction execution

and waits for deassertion of

BR.

In addition to the address and data bus for external memory

connection, the ADSP-21msp58/59 has a host interface port

(HIP) for easy connection to a host processor. The HIP is made

up of 8 data/address pins and 10 control pins. The HIP is extremely flexible and provides a simple interface to a variety of

host processors. For example, the Motorola 68000 series, the

Intel 80C51 series, and the Analog Devices ADSP-2101 can be

easily connected to the HIP. The host processor can boot the

ADSP-21msp58/59 on-chip memory through the HIP.

The ADSP-21msp58/59 can respond to eleven interrupts. There

can be up to three external interrupts, configured as edge- or

level-sensitive, and seven internal interrupts generated by the

Timer, the Serial Ports (SPORTs), the HIP, the powerdown circuitry, and the analog interface. There is also a master

RESET

signal.

The two serial ports provide a complete synchronous serial in-

terface with optional companding in hardware and a wide variety of framed or frameless data transmit and receive modes of

operation. Each port can generate an internal programmable serial clock or accept an external serial clock.

Booting circuitry provides for loading on-chip program memory

automatically from byte-wide external memory. After reset,

DATA

ADDRESS

GENERATOR

#1

INPUT REGS

ALU

OUTPUT REGS

DATA

ADDRESS

GENERATOR

#2

INPUT REGS

MAC

OUTPUT REGS

16

INSTRUCTION

REGISTER

PROGRAM

SEQUENCER

R BUS

PROGRAM

SRAM

14

14

24

16

INPUT REGS

SHIFTER

OUTPUT REGS

PMA BUS

DMA BUS

PMD BUS

DMD BUS

2K x 24

PROGRAM

ROM

4K x 24

(ADSP-21msp59)

CONTROL

LOGIC

TRANSMIT REG

RECEIVE REG

SERIAL

PORT 0

5

DATA

SRAM

2K x 16

COMPANDING

CIRCUITRY

TRANSMIT REG

RECEIVE REG

Figure 1. ADSP-21msp58/59 Block Diagram

–2–

SERIAL

PORT 1

ADDRESS

GENERATOR

5

BOOT

TIMER

FLAG

ADC, DAC

AND

FILTERS

MUX

MUX

HIP

CONTROL

HIP

REGISTER

POWER

DOWN

CONTROL

LOGIC

1

7

14

EXTERNAL

ADDRESS

BUS

EXTERNAL

24

DATA

BUS

10

8

HIP

DATA

BUS

1

REV. 0

ADSP-21msp58/59

seven wait states are automatically generated. This allows, for

example, a 38 ns ADSP-21msp58/59 to use a 250 ns EPROM

as external boot memory. Multiple programs can be selected

and loaded from the EPROM with no additional hardware. The

on-chip program memory can also be initialized through the

HIP.

The ADSP-21msp58/59 features a general purpose flag output

whose state is controlled through software. You can use this

output to signal an event to an external device. In addition, the

data input and output pins on SPORT1 can be alternatively

configured as an input and an output flag.

A programmable interval timer can generate periodic interrupts.

A 16-bit count register (TCOUNT) is decremented every n

cycles, where n–1 is a scaling value stored in an 8-bit register

(TSCALE). When the value of the count register reaches zero,

an interrupt is generated and the count register is reloaded from

a 16-bit period register (TPERIOD).

The ADSP-21msp58/59 instruction set provides flexible data

moves and multifunction (one or two data moves with a computation) instructions. Every instruction can be executed in a

single processor cycle. The ADSP-21msp58/59 uses an algebraic syntax for ease of coding and readability. A comprehensive

set of development tools supports program development.

Serial Ports

The ADSP-21msp58/59 processors include two synchronous serial ports (SPORT0 and SPORT1) for serial communications

and multiprocessor communication.

Here is a brief list of the capabilities of the ADSP-21msp58/59

SPORTs. Refer to the ADSP-2100 Family User’s Manual for further details.

• SPORTs are bidirectional with a separate, double-buffered

transmit and receive section.

• SPORTs can use an external serial clock or generate their own

clock internally.

• SPORTs have independent framing for the transmit and

receive sections. Sections run in a frameless mode or with

frame synchronization signals internally or externally generated. Frame sync signals are programmed to be active high or

low, with either of two pulse widths and timings.

• SPORTs support serial data word lengths from 3 to 16 bits

and provide optional A-law and µ-law companding according

to CCITT recommendation G.711.

• SPORTs receive and transmit sections generate separate

interrupts when the SPORTs are ready to read or write new

data.

• SPORTs can receive and transmit an entire circular buffer of

data with only one overhead cycle per data word (Autobuffering

Mode). An interrupt is generated after a complete data buffer

transfer.

• SPORT0 has a multichannel interface to selectively receive

and transmit a 24- or 32-word, time-division multiplexed

serial bit stream.

• SPORT1 can be reconfigured as two external interrupt inputs

(

IRQ0 and IRQ1) and the Flag In and Flag Out signals (FI,

FO). The internally generated serial clock may still be used in

this configuration.

Pin Descriptions

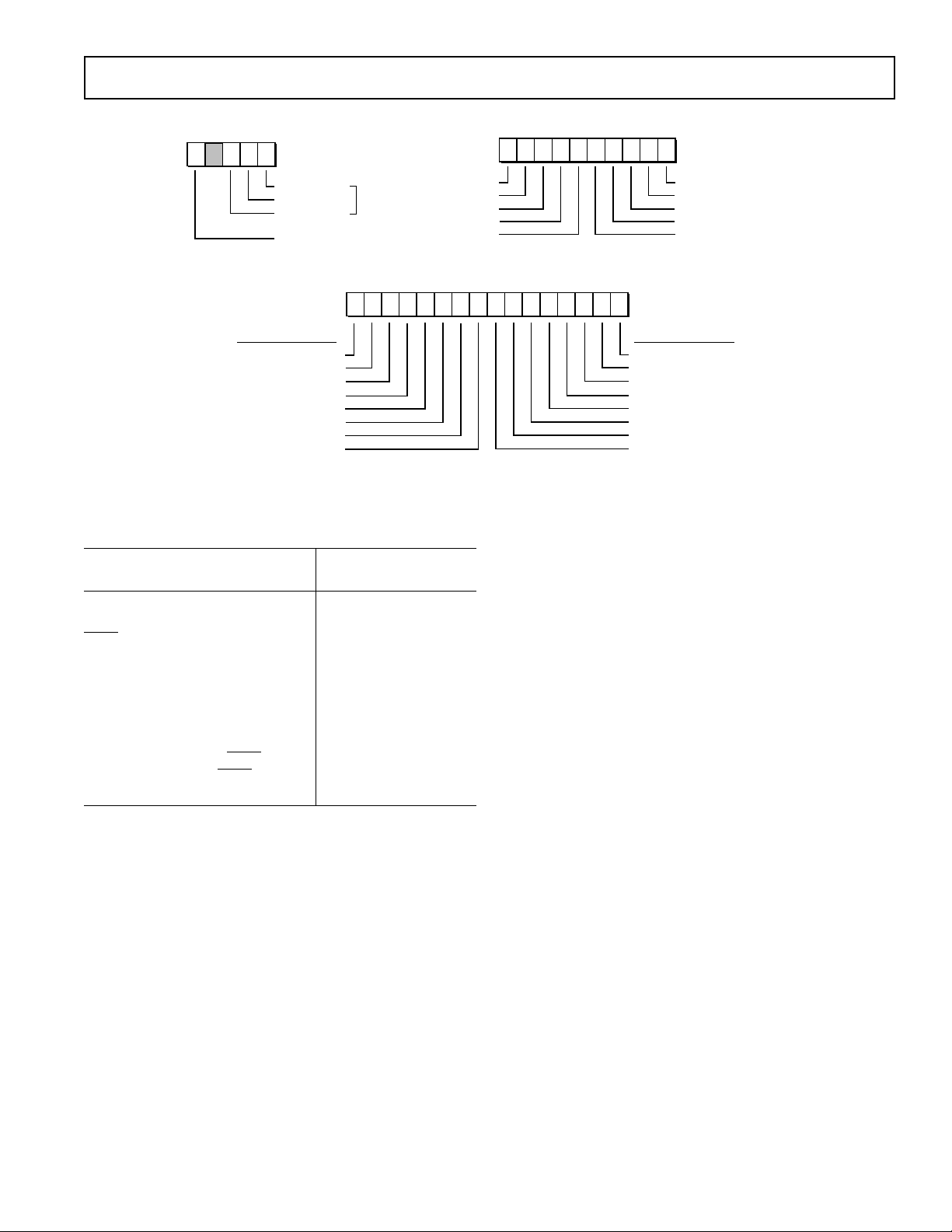

The ADSP-21msp58 and ADSP-21msp59 are available in a

100-lead TQFP package. Table I contains the pin descriptions.

Table I. ADSP-21msp58/59 Pin List

Pin #

Group of Input/

Name Pins Output Function

Digital Pins

Address 14 O Address output for program,

data and boot memory spaces

Data 24 I/O Data I/O pins for program

and data memories. Input

only for boot memory space,

with two MSBs used as boot

space addresses.

RESET 1 I Processor reset input

IRQ2 1 I External interrupt request #2

BR 1 I External bus request input

BG 1 O External bus grant output

PMS 1 O External program memory select

DMS 1 O External data memory select

BMS 1 O Boot memory select

RD 1 O External memory read enable

WR 1 O External memory write enable

MMAP 1 I Memory map select

CLKIN,

XTAL 2 I External clock or quartz crystal

input

CLKOUT 1 O Processor clock output

HACK 1 O HIP acknowledge output

HSEL 1 I HIP select input

BMODE 1 I Boot mode select (0 = Standard

EPROM Booting, 1 = HIP

Booting)

HMD0 1 I Bus strobe select (0 =

1 = RW/

HMD1 1 I HIP address/data mode select

(0 = Separate, 1 = Multiplexed)

HRD/HRW 1 I HIP read strobe or read/write

select

HWR/HDS 1 I HIP write strobe or host data

strobe select

HD7–0/

HAD7–0 8 I/O HIP data or HIP data and

address

HA2/ALE 1 I Host address 2 or address latch

enable

HA1–0/

(unused) 2 I Host address 1 and 0 inputs

SPORT0 5 I/O Serial port 0 pins (TFS0, RFS0,

DT0, DR0, SCLK0)

SPORT1 5 I/O Serial port 1 pins (TFS1, RFS1,

DT1, DR1, SCLK1)

or

DS)

RD/WR,

REV. 0

–3–

ADSP-21msp58/59

Pin #

Group of Input/

Name Pins Output Function

IRQ0 (RFS1) 1 I External interrupt request #0

IRQ1 (TFS1) 1 I External interrupt request #1

SCLK1 1 O Programmable clock output

FI (DR1) 1 I Flag input pin

FO (DT1) 1 O Flag output pin

FL0 1 O General purpose flag output pin

V

DD

4 Digital power supply pins

GND 5 Ground pins

PWD 1 I Powerdown pin

Analog Pins

VIN

NORM

1 I Input terminal of the NORM

amplifier for the encoder section

(ADC)

VIN

AUX

1 I Input terminal of the AUX

amplifier for the encoder section

(ADC)

Decouple 1 I Ground reference of the NORM

and AUX amplifiers for the

encoder section (ADC)

VOUT

P

1 O Noninverting output terminal of

the differential amplifier from

the decoder section (DAC)

VOUT

N

1 O Inverting output terminal of the

differential amplifier from the

decoder section (DAC)

V

REF

1 O Output voltage reference

REF_

FILTER 1 O Voltage reference external by-

pass filter node

V

CC

GND

A

Host Interface Port

1 Analog power supply

2 Analog ground

The ADSP-21msp58/59 host interface port (HIP) is a parallel

I/O port that allows for an easy connection to a host processor.

Through the HIP, the ADSP-21msp58/59 can be used as a

memory-mapped peripheral to a host computer. The HIP can

be thought of as an area of dual-ported memory, or mailbox registers, that allows communication between the computational

core of the ADSP-21msp58/59 and the host computer.

The host interface port is completely asynchronous. The host

processor can write data into the HIP while the ADSP21msp58/59 is operating at full speed.

The HIP can be configured with the following pins:

• BMODE (when MMAP = 0) determines whether the ADSP-

21msp58/59 boots from the host processor (through the HIP)

or external EPROM (through the data bus).

• HMD0 configures the bus strobes as separate read and write

strobes, or a single read/write select and a host data strobe.

• HMD1 selects separate address (3-bit) and data (8-bit) buses,

or a multiplexed 8-bit address/data bus with address latch

enable.

Tying these pins to appropriate values configures the ADSP21msp58/59 for straight-wire interface to a variety of industrystandard microprocessors and microcomputers.

When the host processor writes an 8-bit value to the HIP, the

upper eight bits of the HIP registers are all zeros. For additional

information, refer to the ADSP-2100 Family User’s Manual,

Chapter 7, for information about 8-bit configuration.

HIP Operation

The HIP contains six data registers (HDR5-0) and two status

registers (HSR7-6) with an associated HMASK register for

masking interrupts from individual HIP data registers. The HIP

data registers are memory-mapped in the internal data memory

of the ADSP-21msp58/59. HIP transfers can be managed using

either interrupts or polling. These registers are shown in the section “ADSP-21msp58/59 Registers.” The two status registers

provide status information to both the ADSP-21msp58/59 and

the host processor. HSR7 contains a software reset bit that can

be set by the ADSP-21msp58/59 and the host.

The HIP allows a software reset to be performed by the host

processor. The internal software reset signal is asserted for five

ADSP-21msp58/59 cycles.

The HIP generates an interrupt whenever an HDR register receives data from a host processor write. It also generates an interrupt when the host processor has performed a successful read

of any HDR. The read/write status of the HDRs is also stored in

the HSR registers.

The HMASK register bits can be used to mask the generation of

read or write interrupts from individual HDR registers. Bits in

the IMASK register enable and disable all HIP read interrupts

or all HIP write interrupts. So, for example, a write to HDR4

will cause an interrupt only if both the HDR4 Write bit in

HMASK and the HIP Write interrupt enable bit in IMASK are

set.

The HIP provides a second method of booting the ADSP21msp58/59 in which the host processor loads instructions into

the HIP. The ADSP-21msp58/59 automatically transfers the

data, in this case opcodes, to internal program memory. The

BMODE pin determines whether the ADSP-21msp58/59 boots

from the host processor through the HIP or from external

EPROM over the data bus.

Interrupts

The interrupt controller lets the processor respond to interrupts

and reset with a minimum of overhead. The ADSP-21msp58/59

provides up to three external interrupt input pins,

and

IRQ2. IRQ2 is always available as a dedicated pin;

SPORT1 may be reconfigured for

IRQ1 and IRQ0 and the flag.

IRQ0, IRQ1,

The ADSP-21msp58/59 also supports internal interrupts from

the timer, the host interface port, the serial ports, the analog interface, and the powerdown control circuit. The interrupts are

internally prioritized and individually maskable (except for

powerdown and

RESET). The input pins can be programmed

for either level- or edge-sensitivity. The priorities and vector addresses for the interrupts are shown in Table II; the interrupt

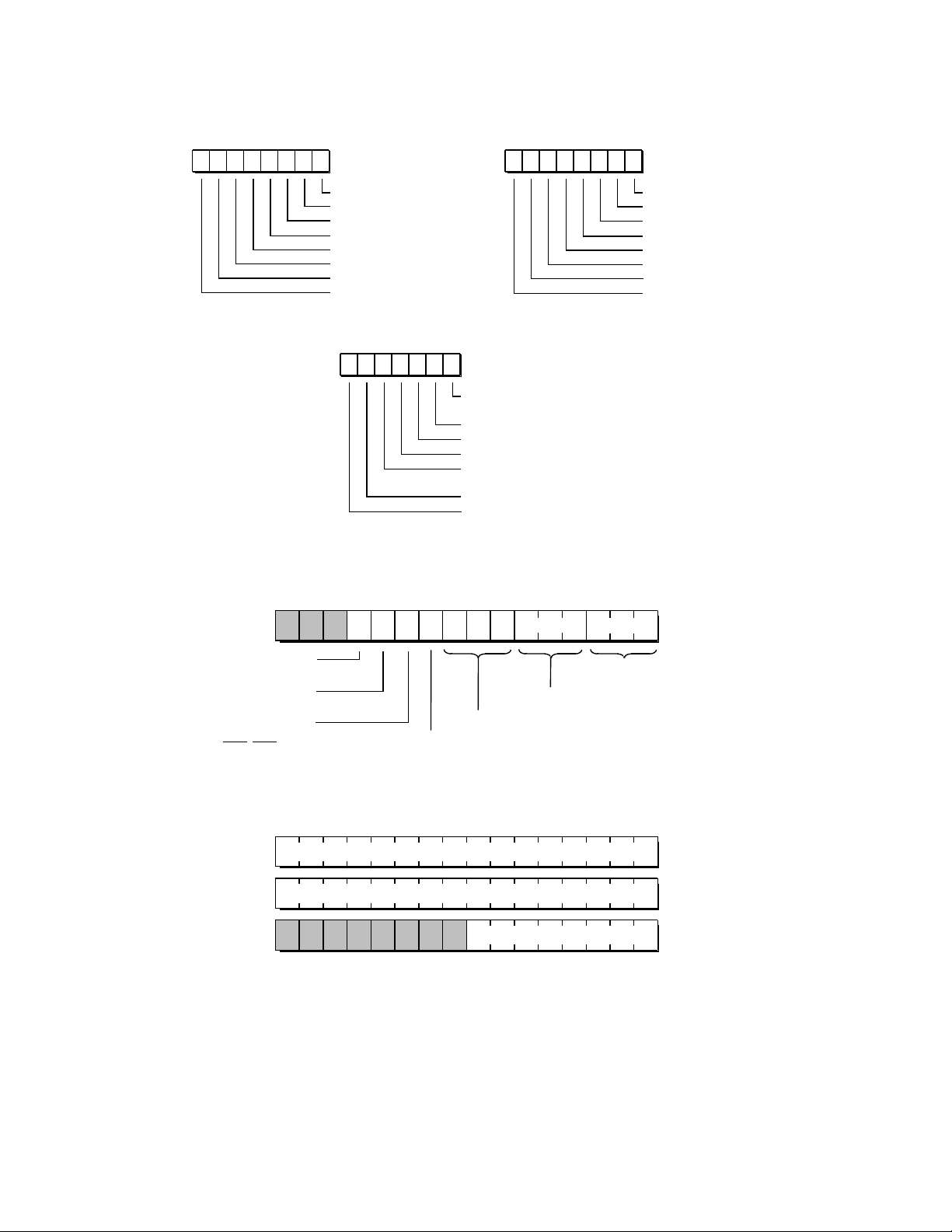

registers are shown in Figure 2.

–4–

REV. 0

ADSP-21msp58/59

ICNTL

43210

0

IRQ0 Sensitivity

IRQ1 Sensitivity

IRQ2 Sensitivity

Interrupt Nesting

1 = enable, 0 = disable

INTERRUPT FORCE

SPORT0 Transmit

SPORT0 Receive

Analog Transmit

SPORT1 Transmit or IRQ1

SPORT1 Receive or IRQ0

IRQ2

Analog Receive

Timer

1 = edge

0 = level

SPORT0 Transmit

SPORT0 Receive

1514131211109876543210

0000000000000000

IRQ2

HIP Write

HIP Read

IFC

Figure 2. Interrupt Registers

Table II. Interrupt Priority & Interrupt Vector Addresses

Interrupt Vector

Source of Interrupt Address (Hex)

Reset (or Power-Up with PUCR = 1) 0000 (Highest Priority)

Powerdown (Nonmaskable) 002C

IRQ2 0004

HIP Write 0008

HIP Read 000C

SPORT0 Transmit 0010

SPORT0 Receive 0014

Analog Interface Transmit 0018

Analog Interface Receive 001C

SPORT1 Transmit or (

SPORT1 Receive or (

IRQ1) 0020

IRQ0) 0024

Timer 0028 (Lowest Priority)

Interrupts can be masked or unmasked with the IMASK regis-

ter. Individual interrupt requests are logically ANDed with the

bits in IMASK; the highest priority unmasked interrupt is then

selected. The powerdown interrupt is non-maskable.

The interrupt control register, ICNTL, allows the external interrupts to be set as either edge- or level-sensitive. Interrupt service routines can either be nested (with higher priority interrupts

taking precedence) or be processed sequentially (with only one

interrupt service active at a time).

The interrupt force and clear register, IFC, is a write-only register used to force an interrupt or clear a pending edge-sensitive

interrupt.

On-chip stacks preserve the processor status and are automatically maintained during interrupt handling. The stack is twelve

levels deep to allow interrupt nesting.

Register bit values shown in Figure 2 are the default bit values

after reset. If no values are shown, the bits are indeterminate at

reset. Reserved bits are shown in gray; these bits should always

be written with zeros.

9876543210

0000000000

IMASK

Timer

IRQ0 or SPORT1 Receive

IRQ1 or SPORT1 Transmit

Analog Receive

Analog Transmit

1 = enable, 0 = disable

INTERRUPT CLEAR

Timer

SPORT1 Receive or IRQ0

SPORT1 Transmit or IRQ1

Analog Receive

Analog Transmit

SPORT0 Receive

SPORT0 Transmit

IRQ2

1 = enable, 0 = disable

The following instructions allow global enable or disable servicing of the interrupts (including powerdown), regardless of the

state of IMASK. Disabling the interrupts does not affect

autobuffering.

ENA INTS;

DIS INTS;

Interrupt servicing is enabled on processor reset.

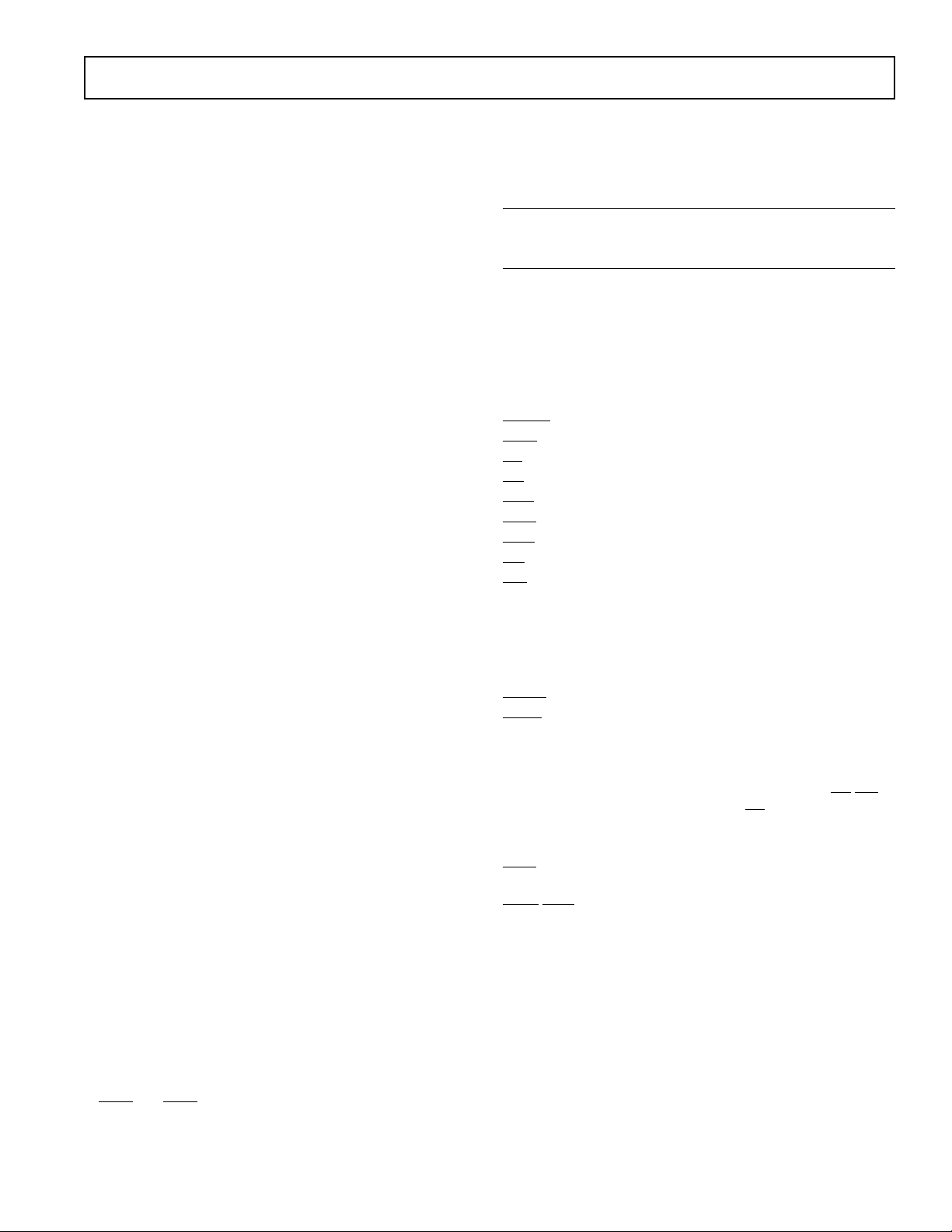

System Interface

Figure 3 shows a basic system configuration with the ADSP21msp58/59, two serial devices, a host processor, a boot

EPROM, optional external program and data memories, and an

analog interface. Up to 15K words of data memory and 16K

words of program memory can be supported. Programmable

wait state generation allows the processor to interface easily to

slow memories. The ADSP-21msp58/59 also provides one external interrupt and two serial ports or three external interrupts

and one serial port.

Clock Signals

The ADSP-21msp58/59 CLKIN input may be driven by a crystal or by a TTL-compatible external clock signal.

The CLKIN input may not be halted, changed in frequency

during operation, or operated at any frequency other the one

specified. Operating the ADSP-21msp58/59 at any other frequency changes the analog performance, which is not tested or

supported.

If an external clock is used, it should be a TTL-compatible signal running at half the instruction rate. The signal should be

connected to the processor’s CLKIN input; in this case, the

XTAL input must be left unconnected.

The ADSP-21msp58/59 uses an input clock with a frequency

equal to half the instruction rate; a 13 MHz input clock yields a

38.46 ns processor cycle (which is equivalent to 26 MHz). Normally, instructions are executed in a single processor cycle.

All device timing is relative to the internal instruction clock rate,

which is indicated by the CLKOUT signal when enabled. The

REV. 0

–5–

ADSP-21msp58/59

ANALOG

CLOCK OR

CRYSTAL

CLKIN

XTAL V

CLKOUT

RESET

IRQ2

BR

BG

MMAP

FL0

PMS RD WR ADDRESS DATA DMS BMS

24

ADCS

PROGRAM

MEMORY

(OPTIONAL)

NOTE: The two MSBs of the Boot EPROM Address are also the two MSBs of the Data Bus.

This is only for the 27C256 and 27C512.

INPUT

GND

CC

A

ADSP-21msp58/59

OE

WE

ANALOG

OUTPUT

4321

VDDGND

14

AD

OE

WE

MEMORY &

PERIPHERALS

(OPTIONAL)

D

DATA

54

23-8

HOST

MODE

24

16

3

CS

7

HIP

SERIAL

PORT 0

SERIAL

PORT 1

HIP CONTROL

HIP DATA/ADDR

8

SCLK

RFS

TFS

DT

DR

SCLK

RFS OR IRQ0

TFS OR IRQ1

DT OR FO

DR OR FI

14 2

OE

HOST

PROCESSOR

(OPTIONAL)

SERIAL DEVICE

(OPTIONAL)

SERIAL DEVICE

(OPTIONAL)

D

23-22

D

15-8

8

ADCS

BOOT

MEMORY

e.g., EPROM

27C64

27C128

27C256

27C512

Figure 3. ADSP-21msp58/59 Basic System Configuration

CLKOUT signal is enabled and disabled by the CLKODIS bit

in the SPORT0 Autobuffer Control Register, DM[0x3FF3].

Because the ADSP-21msp58/59 includes an on-chip oscillator

circuit, an external crystal may also be used. The crystal should

be connected across the CLKIN and XTAL pins, with two capacitors connected as shown in Figure 4. A parallel-resonant,

fundamental frequency, microprocessor-grade crystal should be

used.

CLKIN XTAL

ADSP-21msp58/59

CLKOUT

Figure 4. External Crystal Connections

Reset

The RESET signal initiates a master reset of the ADSP21msp58/59. The

power-up sequence to assure proper initialization.

RESET signal must be asserted during the

RESET dur-

ing initial power-up must be held long enough to allow the

processor’s internal clock to stabilize. If

RESET is asserted at

any time after power-up, the clock continues to run and does

not require stabilization time.

The power-up sequence is defined as the total time required for

the crystal oscillator circuit to stabilize after a valid V

DD

is applied to the processor and for the internal phase-locked loop

(PLL) to lock onto the specific crystal frequency. A minimum of

2000 CLKIN cycles will ensure that the PLL has locked (this

does not, however, include the crystal oscillator start-up time).

During this power-up sequence, the

held low. On any subsequent resets, the

meet the minimum pulse width specification, t

RESET input contains some hysteresis; however, if you use

The

an RC circuit to generate your

RESET signal should be

RESET signal must

.

RSP

RESET signal, the use of an ex-

ternal Schmidt trigger is recommended.

The master

RESET sets all internal stack pointers to the empty

stack condition, masks all interrupts, and clears the MSTAT

register. When

RESET is released, if there is no pending bus request and the chip is configured for booting (MMAP = 0), the

boot loading sequence is performed. Then the first instruction is

fetched from internal program memory location 0x0000 and execution begins.

Program Memory Interface

The on-chip program memory address bus (PMA) and on-chip

program memory data bus (PMD) are multiplexed with the onchip data memory buses (DMA, DMD), creating a single external data bus and a single external address bus. The data and

address busses are three-stated when the DSP runs from internal memory. Refer to the ADSP-2100 Family User’s Manual,

Chapter 10, “Memory Interface” for a detailed explanation. The

14-bit address bus directly addresses up to 16K words. See

“Program Memory Maps” for details on program memory

addressing.

The program memory data lines are bidirectional. The program

memory select (

memory and can be used as a chip select signal. The write (

PMS) signal indicates access to program

WR)

signal indicates a write operation and is used as a write strobe.

–6–

REV. 0

ADSP-21msp58/59

The read (RD) signal indicates a read operation and is used as a

read strobe or output enable signal. An external program

memory access should always be qualified with the

PMS signal.

The ADSP-21msp58/59 writes data from its 16-bit registers to

24-bit program memory using the PX register to provide the

lower eight bits. When the processor reads data (not instructions) from 24-bit program memory to a 16-bit data register, the

lower eight bits are placed in the PX register. The program

memory interface can generate zero to seven wait states for external memory devices; the default is seven wait states after

RESET.

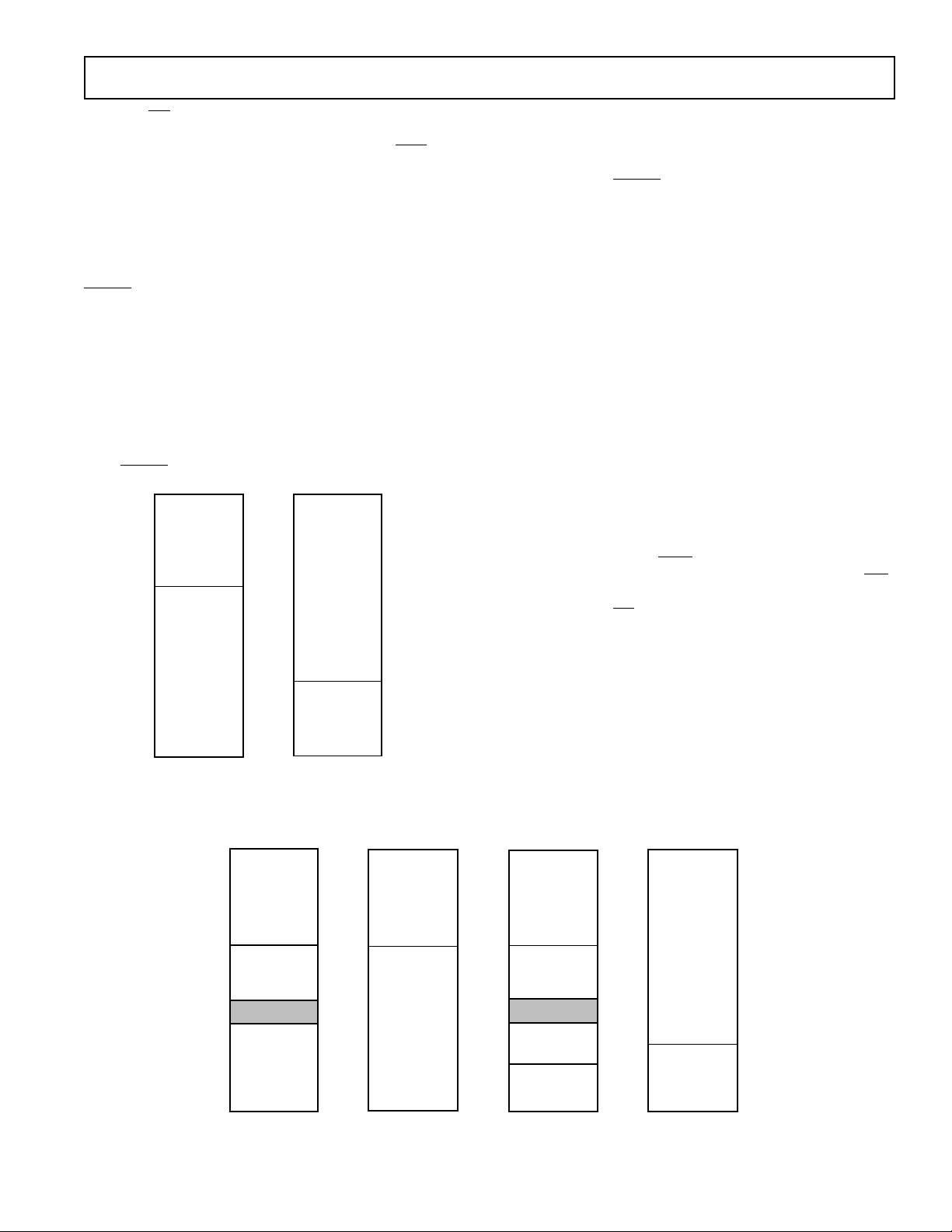

Program Memory Maps

ADSP-21msp58

ADSP-21msp58 Program memory can be mapped in two ways,

depending on the state of the MMAP pin. Figure 5 shows the

two configurations. When MMAP = 0, internal RAM occupies

2K words beginning at address 0x0000; external program

memory uses the remaining 14K words beginning at address

0x0800. In this configuration, the boot loading sequence (described in “Boot Memory Interface”) is automatically initiated

when

RESET is released.

INTERNAL

RAM

LOADED FROM

EXTERNAL

BOOT

MEMORY

EXTERNAL

MMAP=0

0000

07FF

0800

3FFF

EXTERNAL

INTERNAL

RAM

NOT LOADED

MMAP=1

0000

37FF

3800

3FFF

Figure 5. ADSP-21msp58 Program Memory Maps

When MMAP = 1, 14K words of external program memory begin at address 0x0000 and internal RAM is located in the upper

2K words, beginning at address 0x3800. In this configuration,

the boot loading sequence does not take place; execution begins

immediately after

RESET.

ADSP-21msp59

The ADSP-21msp59 is functionally identical to the ADSP21msp58. The ADSP-21msp59 includes an additional 4K by

24-bit mask programmable ROM (see Figure 6). The ROM

can be used to hold program instructions or data and can be

accessed twice in one instruction cycle if necessary. The ROM

always resides at locations PM[0x0800] through PM[0x17FF]

regardless of the state of the MMAP pin. Sixteen addresses at

the end of ROM (0x17F0–0x17FF) are reserved for Analog

Devices’ use. The ROM is enabled by setting the ROMENABLE

bit in the Data Memory Wait State control register, DM[0x3FFE].

When the ROMENABLE bit is set to 1, addressing program

memory in this range will access the on-chip ROM. When set

to 0, addressing program memory in this range will access external program memory. The ROMENABLE bit is set to 0 on

chip reset.

Data Memory Interface

The data memory address bus (DMA) is 14 bits wide. The bidirectional external data bus is 24 bits wide, with the upper 16

bits used for data memory data (DMD) transfers.

The data memory select (

memory and can be used as a chip select signal. The write (

DMS) signal indicates access to data

WR)

signal indicates a write operation and can be used as a write

strobe. The read (

RD) signal indicates a read operation and can

be used as a read strobe or output enable signal.

The ADSP-21msp58/59 supports memory-mapped I/O, with

the peripherals memory mapped into the data or program

memory address spaces and accessed by the processor in the

same manner.

Data Memory Map

The on-chip data memory RAM resides in the 2K words beginning at address 0x3000, as shown in Figure 7. In addition, data

memory locations from 0x3800 to the end of data memory at

0x3FFF are reserved. Control registers for the system, timer,

REV. 0

INTERNAL

RAM

LOADED FROM

EXTERNAL

BOOT

MEMORY

INTERNAL

MASK

PROGRAMMED

ROM

17F0 – 17FF

RESERVED

EXTERNAL

ROM ENABLE = 1

MMAP = 0

0000

07FF

0800

17FF

1800

3FFF

INTERNAL

RAM

LOADED FROM

EXTERNAL

BOOT

MEMORY

EXTERNAL

ROM ENABLE = 0

MMAP = 0

0000

07FF

0800

3FFF

EXTERNAL

INTERNAL

MASK

PROGRAMMED

ROM

17F0 – 17FF

RESERVED

EXTERNAL

INTERNAL

RAM

NOT LOADED

ROM ENABLE = 1

MMAP = 1

0000

07FF

0800

17FF

1800

37FF

3800

3FFF

Figure 6. ADSP-21msp59 Program Memory Maps

–7–

EXTERNAL

INTERNAL

RAM

NOT LOADED

ROM ENABLE = 0

MMAP = 1

0000

37FF

3800

3FFF

ADSP-21msp58/59

wait-state configuration, host interface port, codec, and serial

port operations are located in this region of memory.

The remaining 12K of data memory is external. External data

memory is divided into three zones, each associated with its own

wait-state generator. By mapping peripherals into different

zones, you can accommodate peripherals with different waitstate requirements. All zones default to seven wait states after

RESET.

For compatibility with other ADSP-2100 Family processors, bit

definitions for DWAIT3 and DWAIT4 are shown in the Data

Memory Wait State Control register, but they are not used by

the ADSP-21msp58/59.

DWAIT0

(1K EXTERNAL)

DWAIT1

(1K EXTERNAL)

DWAIT2

(10K EXTERNAL)

NO WAIT STATES

WAIT STATES

0000

03FF

0400

07FF

0800

2FFF

3000

3FFF

12K

EXTERNAL

2K

INTERNAL

1K

RESERVED

MEMORY MAPPED

REGISTERS

AND RESERVED

DATA MEMORY

0000

2FFF

3000

37FF

3800

3BFF

3C00

3FFF

Figure 7. ADSP-21msp58/59 Data Memory Maps

Boot Memory Interface

The ADSP-21msp58/59 can load on-chip memory from external boot memory space. The boot memory space consists of

64K by 8-bit space, divided into eight separate 8K by 8-bit

pages. Three bits in the System Control Register select which

page is loaded by the boot memory interface. Another bit in the

System Control Register allows the user to force a boot loading

sequence under software control. Boot loading from Page 0 after

RESET is initiated automatically if MMAP = 0.

The boot memory interface can generate zero to seven wait

states; it defaults to seven wait states after

RESET. This allows

the ADSP-21msp58/59 to boot from a single low cost EPROM

such as a 27C256. Program memory is booted one byte at a

time and converted to 24-bit program memory words.

The

BMS and RD signals are used to select and to strobe the

boot memory interface. Only 8-bit data is read over the data

bus, on pins D8–D15. To accommodate addressing up to eight

pages of boot memory, the two MSBs of the data bus are used

in the boot memory interface as the two MSBs of the boot

memory address.

The ADSP-2100 Family Assembler and Linker support the creation of programs and data structures requiring multiple boot

pages during execution.

RD and WR must always be qualified by PMS, DMS, or BMS

to ensure the correct program, data, or boot memory accessing.

HIP Booting

The ADSP-21msp58/59 can also boot programs through the

Host Interface Port. If BMODE = 1 and MMAP = 0, the

ADSP-21msp58/59 boots from the HIP. If BMODE = 0, the

ADSP-21msp58/59 boots through the data bus (in the same

way as the ADSP-2101), as described above in “Boot Memory

Interface.” For additional information about HIP booting, refer

to the ADSP-2100 Family User’s Manual, Chapter 7, “Host Interface Port.”

The ADSP-2100 Family Development Software includes a

utility program called the HIP Splitter. This utility allows the

creation of programs that can be booted through the ADSP21msp58/59 HIP, in a similar fashion as EPROM-bootable

programs generated by the PROM Splitter utility.

Bus Request and Bus Grant

The ADSP-21msp58/59 can relinquish control of the data and

address buses to an external device. When the external device

requires access to memory, it asserts the bus request signal

(

BR). If the ADSP-21msp58/59 is not performing an external

memory access, it responds to the active

BR input in the follow-

ing processor cycle by

• three-stating the data and address buses and the

PMS, DMS,

BMS, RD, and WR output drivers,

• asserting the bus grant (

BG) signal, and

• halting program execution.

If GoMode is enabled, the ADSP-21msp58/59 will not halt pro-

gram execution until it encounters an instruction that requires

an external memory access.

If the ADSP-21msp58/59 is performing an external memory access when the external device asserts the

not three-state the memory interfaces or assert the

BR signal, then it will

BG signal

until the cycle after the access is completed, which can be up to

eight cycles later depending on the number of wait states. The

instruction does not need to be completed when the bus is

granted. If a single instruction requires two external memory

accesses, the bus will be granted between the two accesses.

When the

BR signal is released, the processor releases the BG

signal, which reenables the output drivers, and continues program execution from the point where it stopped.

The bus request feature operates at all times, including when

the processor is booting and when

RESET is active.

LOW POWER OPERATION

The ADSP-21msp58/59 has three low power modes that significantly reduce the power dissipation when the device operates

under standby conditions. These modes are:

• Powerdown

• Idle

• Slow Idle

The CLKOUT pin may also be disabled to reduce external

power dissipation. The CLKOUT pin is controlled by Bit 14 of

SPORT0 Autobuffer Control Register, DM[0x3FF3].

Powerdown

The ADSP-21msp58/59 has a low power feature that lets the

processors enter a very low power dormant state through hardware or software control. Here is a brief list of powerdown features. Refer to the ADSP-2100 Family User’s Manual, Chapter 9,

–8–

REV. 0

ADSP-21msp58/59

“System Interface” for detailed information about the powerdown feature.

• Powerdown mode holds the processor in CMOS standby with

a maximum current of less than 100 µA in some modes.

• Quick recovery from powerdown. In some modes, the processor can begin executing instructions in less than 100 CLKIN

cycles.

• Support for an externally generated TTL or CMOS processor

clock. The external clock can continue running during

powerdown without affecting the lowest power rating and 100

CLKIN cycle recovery.

• Support for crystal operation includes disabling the oscillator

to save power (the processor automatically waits 4096 CLKIN

cycles for the crystal oscillator to start and stabilize), and

letting the oscillator run to allow 100 CLKIN cycle start-up.

• Powerdown is initiated by either the powerdown pin (

or the software powerdown force bit.

• Interrupt support allows an unlimited number of instructions

to be executed before optionally powering down. The powerdown interrupt also can be used as a non-maskable, edgesensitive interrupt.

• Context clear/save control lets the processor continue where it

left off or start with a clean context when leaving the powerdown state.

• The

RESET pin also can be used to terminate powerdown,

and the host software reset feature can be used to terminate

powerdown under certain conditions.

• Setting the CLKODIS bit (Bit 14 of the SPORT0 Autobuffer

Control Register [0x3FF3]) disables the CLKOUT pin during

powerdown.

Idle

When the ADSP-21msp58/59 is in the Idle Mode, the processor

waits indefinitely in a low power state until an interrupt occurs.

When an unmasked interrupt occurs, it is serviced; execution

then continues with the instruction following the IDLE instruction.

Slow Idle

The IDLE instruction is enhanced on the ADSP-21msp58/59 to

let the processor’s internal clock signal be slowed, further reducing power consumption. The reduced clock frequency, a programmable fraction of the normal clock rate, is specified by a

selectable divisor given in the IDLE instruction. The format of

the instruction is

IDLE (n);

where n = 16, 32, 64, or 128. This instruction keeps the processor fully functional, but operating at the slower clock rate. While

it is in this state, the processor’s other internal clock signals,

such as SCLK, and timer clock, are reduced by the same ratio.

CLKOUT remains at the normal rate; it is not reduced. The default form of the instruction, when no clock divisor is given, is

the standard IDLE instruction.

When the IDLE (n) instruction is used, it effectively slows down

the processor’s internal clock and thus its response time to incoming interrupts––the 1-cycle response time of the standard

idle state is increased by n, the clock divisor. When an enabled

interrupt is received, the ADSP-21msp58/59 remains in the idle

state for up to a maximum of n processor cycles (n = 16, 32, 64,

or 128) before resuming normal operation.

PWD)

When the IDLE (n) instruction is used in systems that have an

externally generated serial clock (SCLK), the serial clock rate

may be faster than the processor’s reduced internal clock rate.

Under these conditions, interrupts must not be generated at a

faster rate than can be serviced, due to the additional time the

processor takes to come out of the idle state (a maximum of n

processor cycles).

Standalone ROM Execution (ADSP-21msp59 Only)

When the MMAP and BMODE pins both are set to 1, the

ROM is automatically enabled and execution commences from

program memory location 0x0800 at the start of ROM. This

feature lets an embedded design operate without external

memory components. To operate in this mode, the ROM coded

program must copy an interrupt vector table to the appropriate

locations in program memory RAM. In this mode, the ROM

enable bit defaults to 1 during reset.

Table III. Boot Summary Table

BMODE = 0 BMODE = 1

MMAP = 0 Boot from EPROM, Boot from HIP, then

then execution starts execution starts at

at internal RAM internal RAM location

location 0x0000 0x0000

MMAP = 1 No booting, execution Stand Alone Mode,

starts at external memory execution starts at

location 0x0000 internal ROM location

0x0800

Ordering Procedure For ADSP-21msp59 ROM Processors

To place an order for a custom ROM-coded ADSP-21msp59

processor, you must:

1. Complete the following forms contained in the ADSP ROM

Ordering Package, available from your Analog Devices sales

representative:

ADSP-21msp59 ROM Specification Form

ROM Release Agreement

ROM NRE Agreement & Minimum Quantity Order (MQO)

Acceptance Agreement for Preproduction ROM Products

2. Return the forms to Analog Devices along with two copies of

the Memory Image File (.EXE file) of your ROM code. The

files must be supplied on two 3.5" or 5.25" floppy disks for

the IBM PC (DOS 2.01 or higher).

3. Place a purchase order with Analog Devices for nonrecurring

engineering changes (NRE) associated with ROM product

development.

After this information is received, it is entered into Analog

Devices’ ROM Manager System that assigns a custom ROM

model number to the product. This model number will be

branded on all prototype and production units manufactured to

these specifications.

To minimize the risk of code being altered during this process,

Analog Devices verifies that the .EXE files on both floppy disks

are identical, and recalculates the checksums for the .EXE file

entered into the ROM Manager System. The checksum data, in

the form of a ROM Memory Map, a hard copy of the .EXE file,

and a ROM Data Verification form are returned to you for

inspection.

REV. 0

–9–

ADSP-21msp58/59

A signed ROM Verification Form and a purchase order for production units are required prior to any product being manufactured. Prototype units may be applied toward the minimum

order quantity.

Upon completion of prototype manufacture, Analog Devices

will ship prototype units and a delivery schedule update for production units. An invoice against your purchase order for the

NRE charges is issued at this time.

There is a charge for each ROM mask generated and a minimum order quantity. Consult your sales representative for details. A separate order must be placed for parts of a specific

package type, temperature range, and speed grade.

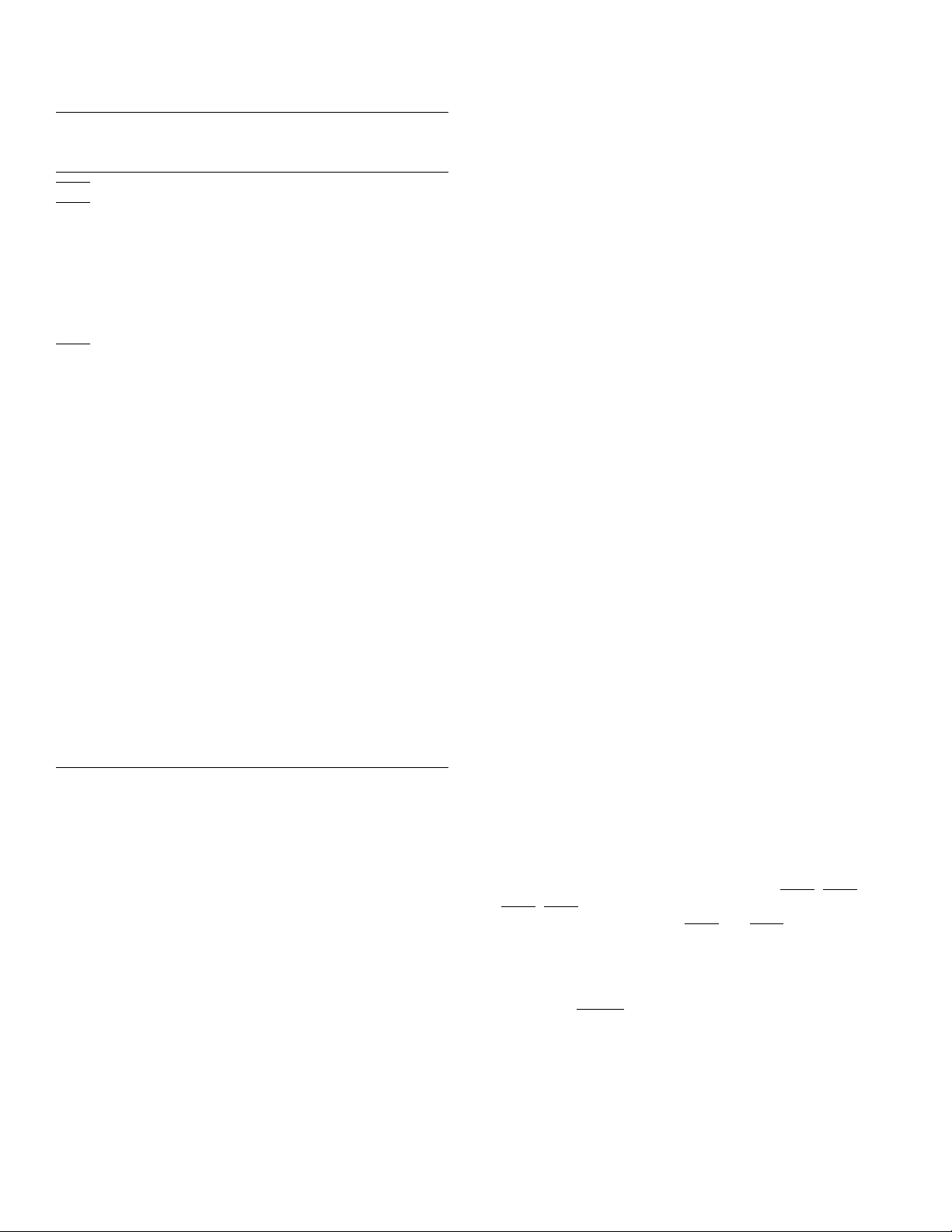

ANALOG INTERFACE

The analog interface contains encoding circuitry (ADC), decoding circuitry (DAC), and processor interface logic. A block diagram of the ADSP-21msp58/59 analog section is shown in

Figure 8.

The analog interface is configured through the Analog Control

Register and the Analog Autobuffer/Powerdown Register (refer

to “ADSP-21msp58/59 Registers”). The Analog Control Register DM[0x3FEE] configures the programmable gain stages, the

analog input multiplexer, and the analog interface powerdown

state. Note that the unused bits must be cleared to zero.

VIN

NORM

VIN

AUX

DECOUPLE

REF_FILTER

V

REF

VOUT

VOUT

MUX

BUF

P

N

DIFFERENTIAL AMP

OUTPUT

DAC

PGA

ADC

PGA

VOLTAGE

REFERENCE

ANALOG

SMOOTHING

FILTER

16-BIT

SIGMADELTA

ADC

16-BIT

SIGMADELTA

DAC

PROCESSOR

INTERFACE

16

Figure 8. Analog Interface Block Diagram

A/D Conversion

The A/D conversion circuitry of the analog interface consists of

an analog multiplexer, a programmable gain amplifier (ADC

PGA), and a 16-bit sigma-delta analog-to-digital converter

(ADC).

Analog Input Multiplexer and Amplifiers

The analog multiplexer selects either the NORM or AUX input

to the ADC’s sigma-delta modulator. The inputs should be ac

coupled.

The ADC PGA may be used to additionally increase the signal

level by +6 dB, +20 dB, or +26 dB. This gain is selected by bit

9 and bit 0 (IG0, IG1) of the analog control register. Input signal level to the sigma-delta ADC should not exceed the V

INMAX

specification.

Analog-To-Digital Converter

The analog interface’s analog-to-digital converter consists of a

4th-order analog sigma-delta modulator, an anti-aliasing decimation filter, and an optional digital high-pass filter. For a detailed

description of the ADC components, refer to the ADSP-2100

Family User’s Manual, Chapter 8, “Analog Interface.”

Bit 10 of the Analog Control Register (0x3FEE) may be set to

add an offset to the input of the ADC sigma-delta converter.

This offset moves ADC sigma-delta idle tones out of the 4.0

kHz speech band range. This added offset must be removed by

the ADC high-pass filter. Therefore, the high-pass filter must be

inserted when you use the offset feature.

D/A Conversion

The D/A conversion circuitry of the analog interface consists of

a sigma-delta digital-to-analog converter (DAC), an analog

smoothing filter, a programmable gain amplifier (DAC PGA),

and a differential output amplifier.

Digital-to-Analog Converter

The digital-to-analog converter consists of an optional digital

high-pass filter, an anti-imaging interpolation filter, and a

sigma-delta modulator. The digital filters and the sigma-delta

modulator have the same characteristics as the filters and

modulator of the ADC. For detailed description of the DAC

components, refer to the ADSP-2100 Family User’s Manual,

Chapter 8, “Analog Interface.”

Analog Smoothing Filter and Programmable Gain Amplifier

The analog smoothing filter consists of a 3rd-order switched capacitor filter with a 3 dB point at approximately 25 kHz.

The DAC’s programmable gain amplifier (DAC PGA) can be

used to adjust the output signal level by –15 dB to +6 dB in

3 dB increments. This gain is selected by bits 2–4 (OG0, OG1,

OG2) of the analog control register.

Differential Output Amplifier

The analog output signal (VOUTP, VOUTN) is produced by a

differential amplifier. The differential amplifier meets specifications for loads greater than 2 kΩ and has a maximum differential output swing of ±3.156 V peak-to-peak (3.17 dBm0). The

DAC will drive loads smaller than 2 kΩ, but with degraded

performance.

The output signal is dc-biased to the on-chip voltage reference

(V

) and can be ac-coupled directly to a load or dc-coupled to

REF

an external amplifier.

The VOUT

, VOUTN output must be used as a differential sig-

P

nal otherwise performance will be severely compromised. Do

not use either pin as a single-ended output.

OPERATING THE ANALOG INTERFACE

The analog interface is operated with several memory-mapped

control and data registers. The ADC and DAC I/O data is received and transmitted through two memory-mapped data registers. The data can also be autobuffered directly into (or from)

on-chip memory. In both cases, the I/O processing is interrupt

driven; two interrupts are dedicated to the analog interface, one

for the ADC receive data and one for the DAC transmit data.

The ADSP-21msp58/59 must have an input clock frequency of

13 MHz. At this frequency, analog-to-digital and digital-to-analog converted data is transmitted at an 8 kHz rate with a single

16-bit word transmitted every 125 µs.

For detailed information about the analog interface, refer to the

ADSP-2100 Family User’s Manual, Chapter 8, “Analog Interface.”

–10–

REV. 0

ADSP-21msp58/59

Autobuffering

In some applications, it is advantageous to perform block data

transfers between the analog converters and processor memory.

Analog interface autobuffering enables the automatic transfer of

data blocks directly from the ADC to on-chip processor data

memory or from on-chip processor data memory directly to the

DAC.

ADC and DAC Interrupts

The analog interface generates two interrupts that signal either:

(1) a 16-bit, 8 kHz analog-to-digital or digital-to-analog conversion has been completed, or (2) an autobuffer block transfer

has been completed (i.e., the data buffer contents have been

received or transferred).

When an analog interrupt occurs, the processor vectors to the

addresses listed in Table II, Interrupt Priority & Interrupt Vector

Addresses.

The ADC receive and DAC transmit interrupts occur at an

8 kHz rate, indicating when the data registers should be accessed. On the receive side, the ADC interrupt is generated each

time an A/D conversion cycle is completed and the 16-bit data

word is available in the ADC receive register. On the transmit

side, the DAC interrupt is generated each time an D/A conversion cycle is completed and the DAC transmit register is ready

for the next 16-bit data word.

Both interrupts are generated simultaneously at an 8 kHz rate,

occurring every 3250 instruction cycles with a 13 MHz internal

processor clock. The interrupts are generated continuously,

starting when the analog interface is powered up by setting the

APWD bits (Bits 5 and 6) to one in the analog control register.

Because both interrupts occur simultaneously, only one should

be enabled (in IMASK) to vector to a single service routine that

handles transmit and receive data. However, when using

autobuffer transfers, both interrupts should be enabled.

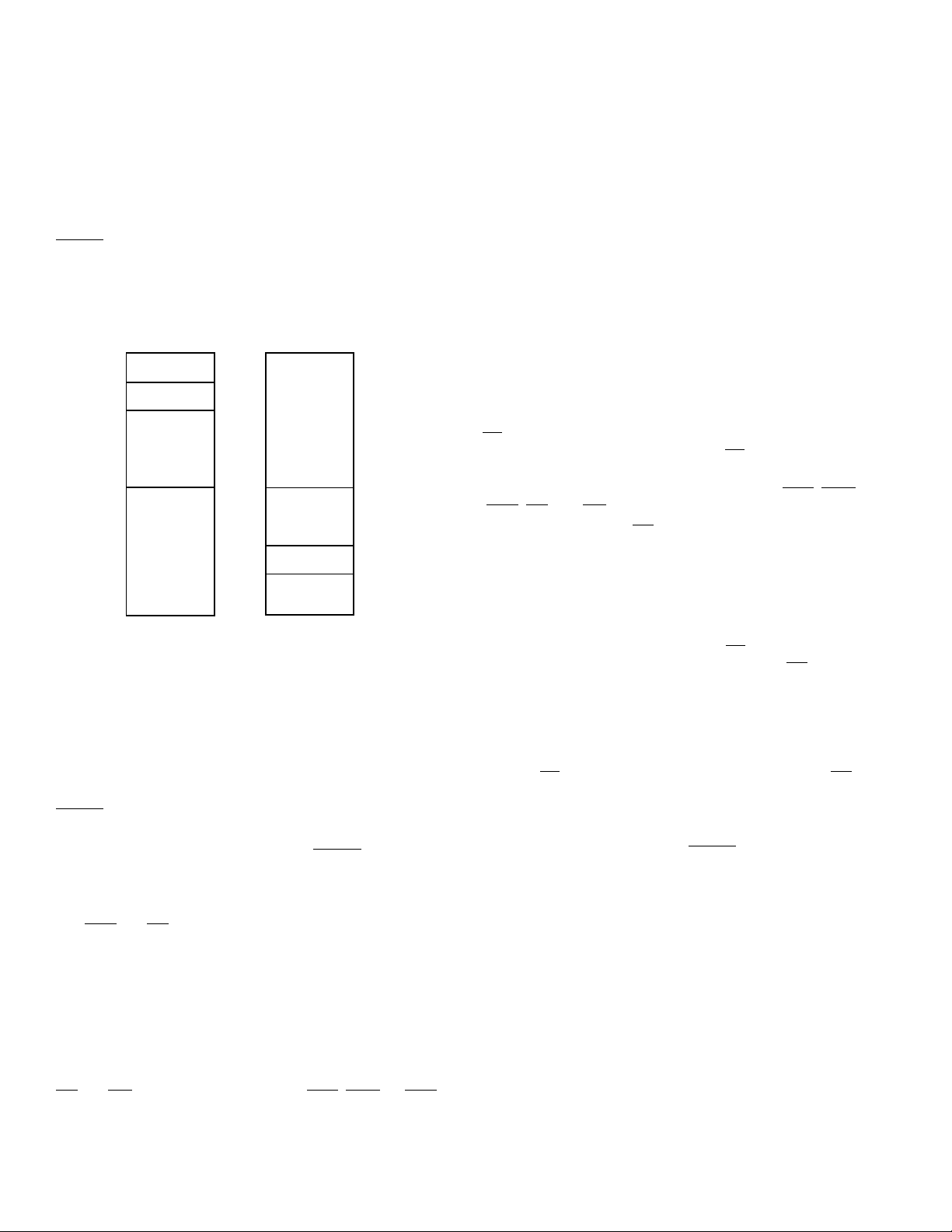

ADSP-21msp58/59 REGISTERS

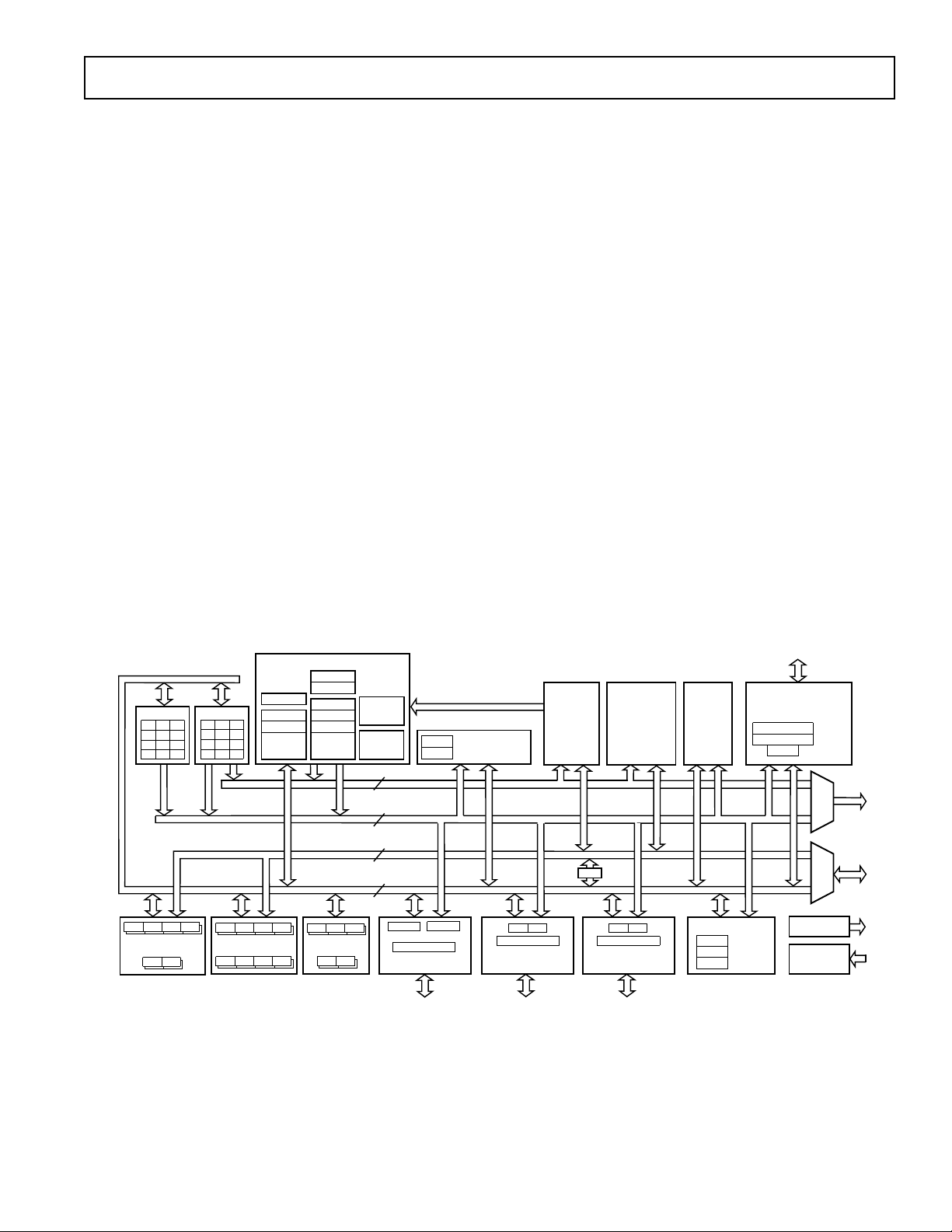

Figure 9 summarizes the ADSP-21msp58/59 registers. Some

registers store values. For example, AX0 stores an ALU operand; I4 stores a DAG2 pointer. Other registers consist of control

bits and fields, or status flags. For example ASTAT contains

status flags from arithmetic operations, and fields in DWAIT

control the number of wait states for different zones of data

memory.

A secondary set of registers in all computational units allows a

single-cycle context switch.

The bit and field definitions for control and status registers are

given in the rest of this section, except IMASK, ICNTL, and

IFC, which are defined earlier in this data sheet. The system

control register, DWAIT register, timer registers, HIP control

registers, HIP data registers, and SPORT control registers are

all mapped into data memory locations; that is, you access these

registers by reading and writing data memory locations rather

than register names. The particular data memory address is

shown with each memory-mapped register.

Register bit values shown on the following pages are the default

bit values after reset. If no values are shown, the bits are indeterminate at reset. Reserved bits are shown in gray; these bits

should always be written with zeros.

DAG 1

I0

M0

L0

I1

M1

L1

I2

M2

L2

I3

M3

L3

AX0 AX1 AY0 AY1

ALU

AFAR

DAG 2

I4

M4

L4

I5

M5

L5

I6

M6

L6

I7

M7

L7

MX0 MX1 MY0 MY1

MAC

MR0 MR1 MR2 MF

PROGRAM SEQUENCER

SSTAT

CNTR

OWRCNTR

COUNT

STACK

4 x 14

STATUS

SI SE SB

ICNTL

IFC

SR1SR0

LOOP

STACK

4 x 18

PC

STACK

16 x 14

14

14

24

16

0x3FFF

0x3FFE

PMA BUS

DMA BUS

PMD BUS

DMD BUS

0x3FEC 0x3FED

DAC

0x3FEE-0x3FEF

CONTROL REGISTERS

ANALOG INTERFACE

SYSTEM CONTROL

DM WAIT CONTROL

ADC

0x3FFA-0x3FF3

CONTROL REGISTERS

SPORT 0

IMASK

MSTAT

ASTAT

STACK

12 x 25

SHIFTER

Figure 9. ADSP-21msp58/59 Registers

TX0RX0

PROGRAM

SRAM

2K x 24

PX

CONTROL REGISTERS

PROGRAM

ROM

4K x 24

ADSP-21msp59

ONLY

TX1RX1

0x3FF2-0x3FEF

SPORT 1

DATA

SRAM

2K x 16

0x3FFD

0x3FFC

0x3FFB

TIMER

TPERIOD

TCOUNT

TSCALE

HOST

INTERFACE

PORT

0x3FE0-0x3FE5

0x3FE6-0x3FE7

0x3FE8

POWERDOWN

DATA

STATUS

HMASK

FLAG

CONTROL

LOGIC

REV. 0

–11–

ADSP-21msp58/59

ASTAT

76543210

00000000

1514131211109876543210

00000100001 11 111

AZ ALU Result Zero

AN ALU Result Negative

AV ALU Overflow

AC ALU Carry

AS ALU X Input Sign

AQ ALU Quotient

MV MAC Overflow

SS Shifter Input Sign

MSTAT

6543210

0000000

System Control Register

SSTAT (Read -Only)

76543210

01010101

PC Stack Empty

PC Stack Overflow

Count Stack Empty

Count Stack Overflow

Status Stack Empty

Status Stack Overflow

Loop Stack Empty

Loop Stack Overflow

Data Register Bank Select

0 = primary, 1 = secondary

Bit Reverse Mode Enable (DAG1)

ALU Overflow Latch Mode Enable

AR Saturation Mode Enable

MAC Result Placement

0 = fractional, 1 = integer

Timer Enable

Go Mode Enable

0x3FFF

SPORT0 Enable

1 = enabled, 0 = disabled

SPORT1 Enable

1 = enabled, 0 = disabled

SPORT1 Configure

0 = FI, FO, IRQ0

1 = serial port

, IRQ1, SCLK

PWAIT

Program Memory

Wait States

BFORCE

Boot Force Bit

BPAGE

Boot Page Select

BWAIT

Boot Wait States

Timer Registers

1514131211109876543210

TPERIOD Period Register

TCOUNT Counter Register

00000000

TCOUNT Scaling Register

Control Registers

0x3FFD

0x3FFC

0x3FFB

–12–

REV. 0

Loading...

Loading...