Analog Devices ADSP-21mod870-110 Datasheet

a

Internet Gateway Processor Software

ADSP-21mod870-110

FEATURES

ISDN B-Channel HDLC

DATA Modulations

CCITT V.90 (30k–56k)

K56Flex™ (30k–56k)

ITU-T V.34: 33600 Bits/s–2400 Bits/s

CCITT V.32bis: 14400 Bits/s–7200 Bits/s

CCITT V.32: 9600 Bits/s, 4800 Bits/s

CCITT V.23

CCITT V.22/V.22bis: 2400, 1200, 600 Bits/s

CCITT V.21: 300 Bits/s

Bell 212A: 1200 Bits/s

Bell 103: 300 Bits/s

Start-Up Procedures:

ITU-T V.8

Error Correction and Data Compression:

CCITT V.42 Error Correction (LAPM and MNP2-4)

CCITT V.42bis Data and MNP Class 5 Compression

FAX Modem

V.17/V.29/V.27ter/V.21 Channel 2

T.30 Protocol

V.120

V.110

PPP Asynchronous Framing Support (RFC 1662)

Low Power

80 mW Typical Active

Low Power and Sleep Modes

High Density

100-Lead LQFP Package

On-Chip DS0/DS1 Interface

Full Function DMA Port

No External Memory Required

0.4 Square Inch per Complete Modem Port

3.3 V Supply

Fully Upgradable RAM-Based Architecture

Fast Download

Full Image in 5 ms

High Speed 16-Bit Port Link Bus Provides Simple

Interface Between Host and Modem Pool

INTRODUCTION

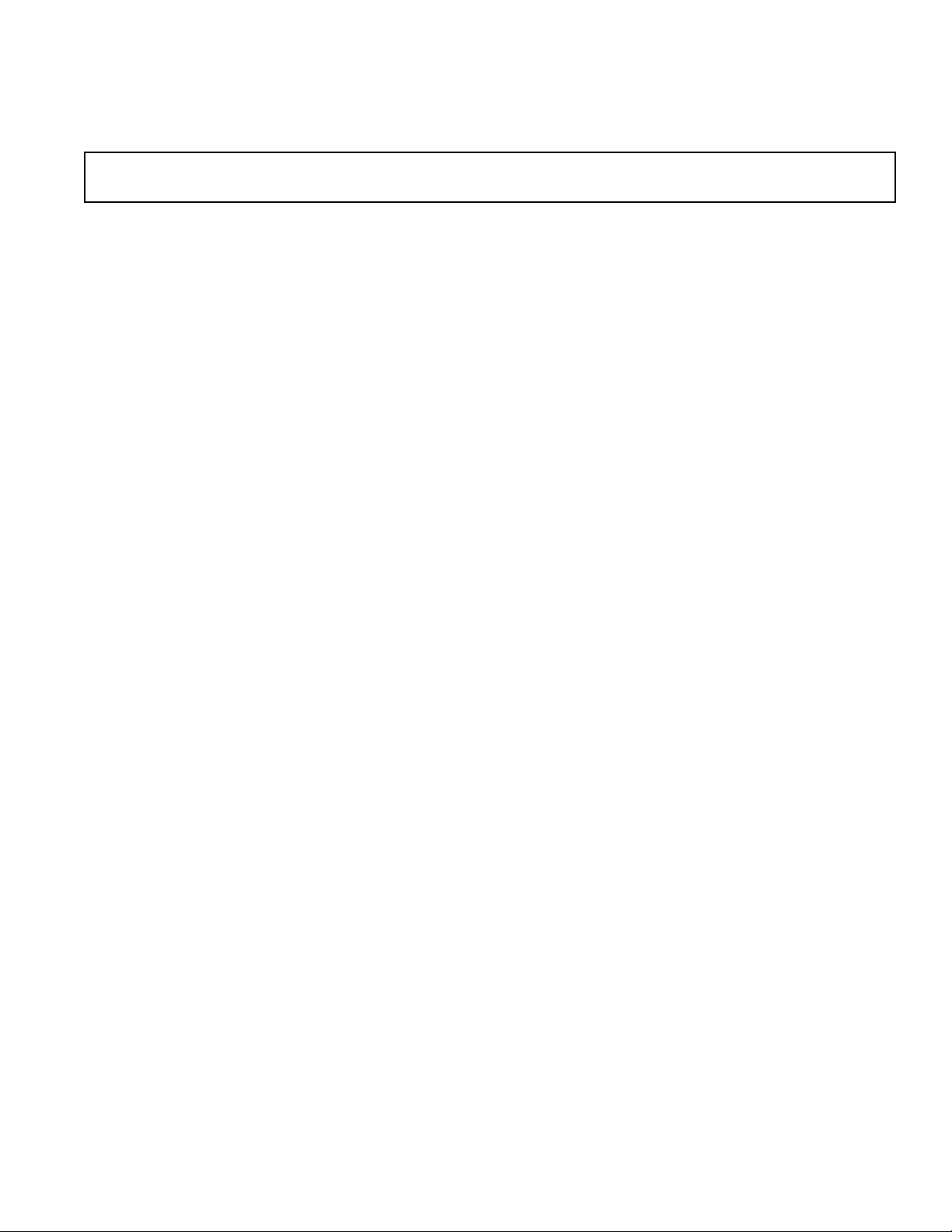

The ADSP-21mod870-110 is a complete single chip. All datapump and controller functions are implemented on a single

0.4 square-inch chip. This modem package allows the highest

modem port density, while achieving the lowest power consumption in a software upgradable platform.

The ADSP-21mod870-110 is designed for high density systems

such as remote access servers (see Figure 1). Its high performance DSP core, large on-chip SRAM, TDM serials port and

16-bit DMA port provide efficient control and data communication with minimal chip count. The modem software provides

a number of data modulations, such as V.34, 56K bps PCM,

and ISDN with a software upgrade path to future standards,

and new applications, such as voice over network. The host

interface allows system access to modem statistics such as call

progress, connect speed and modulation parameters such as

retrain count and symbol rate.

ON-CHIP SRAM

The ADSP-21mod870-110 processor integrates 160K bytes of

on-chip memory. The modem datapump and controller software, as well as data storage, are contained in the on-chip SRAM.

The SRAM cells are designed by Analog Devices. These cells

are optimized for high speed digital signal processing and low

power consumption. You can dynamically configure the ADSP21mod870 with software through the 16-bit DMA interface.

DMA INTERFACE

The 16-bit internal DMA port (IDMA port) provides transparent, direct access to the on-chip RAM of the ADSP-21mod870

processor. This high speed access to on-chip memory simplifies

control and data communication and system debug. Use the

16-bit DMA interface to dynamically configure the ADSP21mod870 with software.

K56Flex is a trademark of Rockwell International and Lucent Technologies.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

ADSP-21mod870-110

IDMA

ADSP-

21mod870

SP0

PORT LINK

IDMA

ADSP-

21mod870

SP0

DTMF DIALING

CALLER ID

HDLC PROTOCOL

T1, E1,

PRI, xDSL,

ATM

LINE

INTERFACE

CALL

CONTROL

IDMA

ADSP-

21mod870

SP0

IDMA

ADSP-

21mod870

SP0

ADSP-21mod870 FUNCTIONS

V.34/56k MODEM

V.17 FAX

V.42, V.42bis, MNP2-5

Figure 1. ADSP-21mod870 Network Access System

SERIAL PORTS

The ADSP-21mod870 processor incorporates two complete

synchronous, double-buffered serial ports for serial communications. The serial ports interface directly to a time-division

multiplexed (TDM) 1544 kbps (T1) or 2048 kbps (E1) serial

stream, to an 8K sample/s data stream, or to an 8-bit companded

(64 kb/s) data stream (DS0). The serial ports operate under

modem software control.

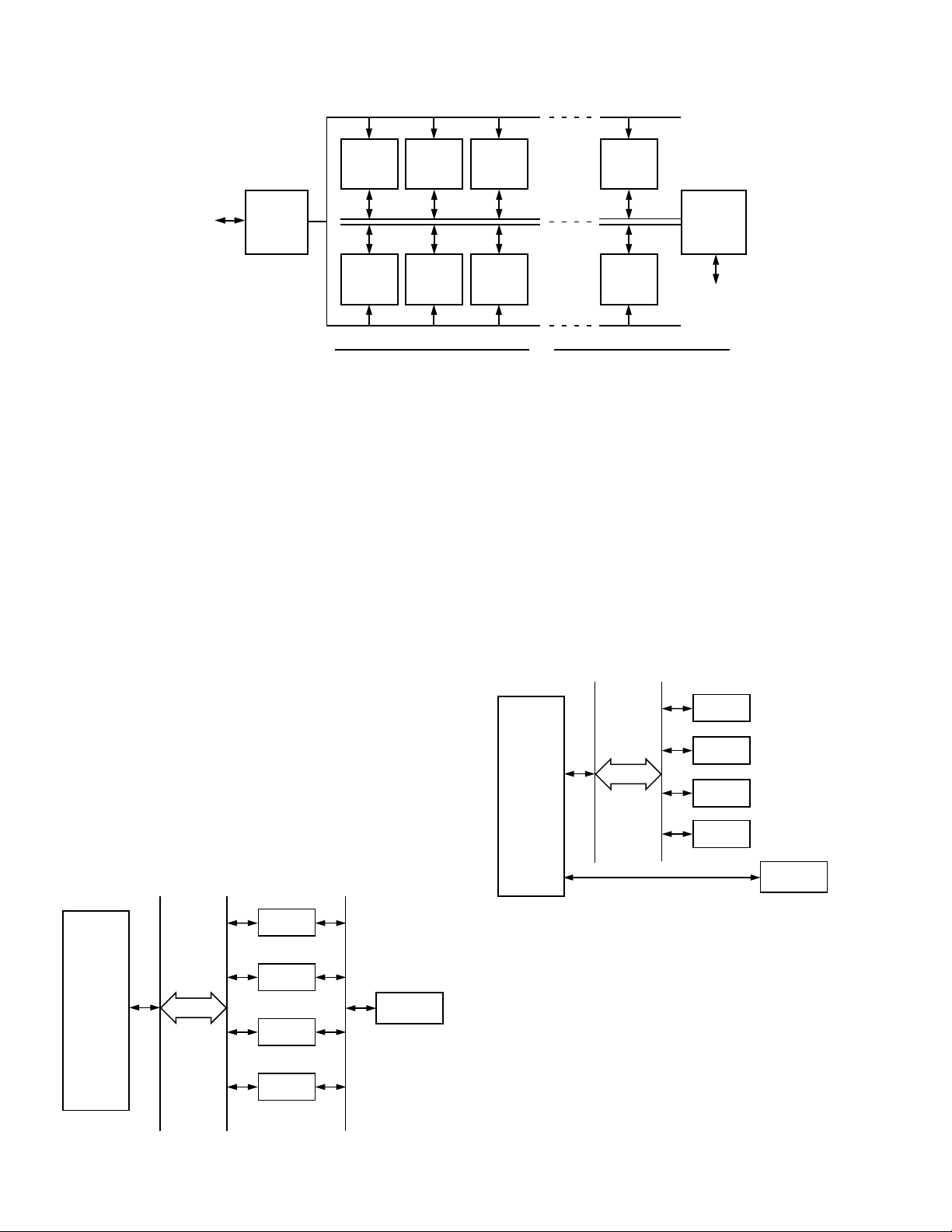

SUPPORTED SYSTEM ARCHITECTURES

The ADSP-21mod870-110 Internet Gateway Processor Software supports two system architectures: serial Telco PCM TDM

data stream and parallel Telco PCM data stream. The two architectures are differentiated by the method of proving Telco

PCM data to the DSP Modem.

Serial Telco PCM TDM Data Stream Architecture

The serial Telco PCM TDM data stream architecture, shown

in Figure 2, is the most common architecture. In this architecture, the modem pool may have a local Telco interface that

provides a serial TDM data stream of Telco PCM data to the

DSP through the DSP’s Serial Port. You can connect up to

24/32 DSPs, through the Serial Port, to a 24/32 channel serial

TDM data stream.

SERIAL PORTDMA PORTMEMORY I/F

BUS

IDMA

ADSP-

21mod870

SP0

IDMA

ADSP-

21mod870

SP0

HOST FUNCTIONS

MULTI-DSP CONTROL, OVERLAY

MANAGEMENT AND DATA TRANSFERS

IDMA

ADSP-

21mod870

SP0

IDMA

ADSP-

21mod870

SP0

HOST

(ADSP-2183)

LAN OR

INTERNET

Parallel Telco PCM Data Stream Architecture

The parallel Telco PCM data stream architecture, shown in

Figure 3, provides a single bus interface for all data and control.

In this architecture, the modem pool may have a remote Telco

interface that provides a parallel data stream of Telco PCM data

to the DSP through the DSP’s DMA Port. An arbitrary number

of DSPs can be connected, through the DMA Port, to a Host

that provides the parallel data stream.

Note: The number of parallel DSPs is limited only by the software loading constraints on the Host.

DMA PORTMEMORY I/F

ADSP-

21mod870

ADSP-

21mod870

HOST

ADSP-

21mod870

ADSP-

21mod870

TELCO PCM

I/F

ADSP-

21mod870

ADSP-

21mod870

HOST TELCO PCM

ADSP-

21mod870

ADSP-

21mod870

I/F

Figure 2. Serial Telco PCM TDM Data Stream Architecture

Figure 3. Parallel Telco PCM Data Stream Architecture

–2–

REV. 0

Loading...

Loading...