Page 1

ADSP-21065L SHARC® DSP

Technical Reference

Analog Devices, Inc.

One Technology Way

Norwood, Mass. 02062-9106

Revision 2.0, July 2003

Part Number

82-001903-01

a

Page 2

Copyright Information

©2003 Analog Devices, Inc., ALL RIGHTS RESERVED. This document

may not be reproduced in any form without prior, express written consent

from Analog Devices, Inc.

Printed in the USA.

Disclaimer

Analog Devices, Inc. reserves the right to change this product without

prior notice. Information furnished by Analog Devices is believed to be

accurate and reliable. However, no responsibility is assumed by Analog

Devices for its use; nor for any infringement of patents or other rights of

third parties which may result from its use. No license is granted by

implication or otherwise under the patent rights of Analog Devices, Inc.

Trademark and Service Mark Notice

The Analog Devices logo, the SHARC logo, EZ-ICE, and SHARC are

registered trademarks of Analog Devices, Inc.

VisualDSP++ is a trademark of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of

their respective owners.

Page 3

CONTENTS

PREFACE

For Additional Information About Analog Products ...................... -xiii

For Technical or Customer Support .............................................. -xiv

What’s This Book About and Who’s It For? ................................... -xiv

How to Use This Manual ............................................................. -xvi

Related Documents .................................................................... -xviii

Conventions of Notation .............................................................. -xix

INSTRUCTION SET REFERENCE

Instruction Summary ................................................................... A-2

Compute and Move/Modify Summary .................................... A-4

Program Flow Control Summary ............................................ A-6

Immediate Move Summary ..................................................... A-8

Miscellaneous Instructions Summary ...................................... A-9

Reference Notation Summary ............................................... A-11

Register Types Summary ....................................................... A-15

Memory Addressing Summary .............................................. A-18

Opcode Notation ....................................................................... A-19

Universal Register Codes ...................................................... A-24

ADSP-21065L SHARC DSP Technical Reference iii

Page 4

CONTENTS

Group I Instructions (Compute & Move) .................................... A-28

Compute/dregÙDM/dregÙPM (Type 1) ........................... A-30

Compute (Type 2) ................................................................ A-32

Compute/uregÙDM|PM, register modify (Type 3) .............. A-33

Compute/dreg

Compute/uregÙureg (Type 5) ............................................. A-37

Immediate Shift/dreg

Compute/modify (Type 7) .................................................... A-42

Group II Instructions (Program Flow Control) ............................ A-44

Direct Jump|Call (Type 8) ..................................................... A-45

Indirect Jump|Call / Compute (Type 9) ................................. A-48

Indirect Jump or Compute/dregÙDM (Type 10) ................. A-52

Return From Subroutine|Interrupt/Compute (Type 11) ......... A-55

Do Until Counter Expired (Type 12) ..................................... A-58

Do Until (Type 13) ............................................................... A-60

Group III Instructions (Immediate Move) ................................... A-62

ÙDM|PM (direct addressing) (Type 14) ....................... A-63

Ureg

Ureg

ÙDM|PM (indirect addressing) (Type 15) .................... A-65

ÙDM|PM, immediate modify (Type 4) ......... A-35

ÙDM|PM (Type 6) ............................. A-39

Immediate data

Immediate dataÖureg (Type 17) ........................................... A-69

Group IV Instructions (Miscellaneous) ........................................ A-70

System Register Bit Manipulation (Type 18) .......................... A-71

Register Modify/bit-reverse (Type 19) .................................... A-73

iv ADSP-21065L SHARC DSP Technical Reference

ÖDM|PM (Type 16) .................................... A-67

Page 5

CONTENTS

Push|Pop Stacks/Flush Cache (Type 20) ................................ A-75

Nop (Type 21) ..................................................................... A-77

Idle (Type 22) ...................................................................... A-78

Idle16 (Type 23) ................................................................... A-79

Cjump/Rframe (Type 24) ..................................................... A-81

COMPUTE OPERATION REFERENCE

Single-Function Operations .......................................................... B-2

ALU Operations ..................................................................... B-2

Rn = Rx + Ry ......................................................................... B-6

Rn = Rx – Ry ......................................................................... B-7

Rn = Rx + Ry + CI ................................................................. B-8

Rn = Rx – Ry + CI – 1 ............................................................ B-9

Rn = (Rx + Ry)/2 .................................................................. B-10

COMP(Rx, Ry) .................................................................... B-11

Rn = Rx + CI ....................................................................... B-12

Rn = Rx + CI – 1 .................................................................. B-13

Rn = Rx + 1 ......................................................................... B-14

Rn = Rx – 1 ......................................................................... B-15

Rn = –Rx ............................................................................. B-16

Rn = ABS Rx ........................................................................ B-17

Rn = PASS Rx ...................................................................... B-18

Rn = Rx AND Ry ................................................................. B-19

Rn = Rx OR Ry .................................................................... B-20

Rn = Rx XOR Ry ................................................................. B-21

ADSP-21065L SHARC DSP Technical Reference v

Page 6

CONTENTS

Rn = NOT Rx ...................................................................... B-22

Rn = MIN(Rx, Ry) ................................................................ B-23

Rn = MAX(Rx, Ry) ............................................................... B-24

Rn = CLIP Rx BY Ry ............................................................ B-25

Fn = Fx + Fy ......................................................................... B-26

Fn = Fx – Fy ......................................................................... B-27

Fn = ABS (Fx + Fy) ............................................................... B-28

Fn = ABS (Fx – Fy) ............................................................... B-29

Fn = (Fx + Fy)/2 ................................................................... B-30

COMP(Fx, Fy) ..................................................................... B-31

Fn = –Fx ............................................................................... B-32

Fn = ABS Fx ......................................................................... B-33

Fn = PASS Fx ........................................................................ B-34

Fn = RND Fx ....................................................................... B-35

Fn = SCALB Fx BY Ry .......................................................... B-36

Rn = MANT Fx .................................................................... B-37

Rn = LOGB Fx ..................................................................... B-38

Rn = FIX Fx

Rn = TRUNC Fx

Rn = FIX Fx BY Ry

Rn = TRUNC Fx BY Ry ..................................................... B-39

Fn = FLOAT Rx BY Ry

Fn = FLOAT Rx ................................................................. B-41

Fn = RECIPS Fx ................................................................... B-42

Fn = RSQRTS Fx .................................................................. B-44

vi ADSP-21065L SHARC DSP Technical Reference

Page 7

CONTENTS

Fn = Fx COPYSIGN Fy ....................................................... B-46

Fn = MIN(Fx, Fy) ................................................................ B-47

Fn = MAX(Fx, Fy)................................................................ B-48

Fn = CLIP Fx BY Fy ............................................................. B-49

Multiplier Operations ................................................................ B-50

Rn = Rx * Ry mod2

MRF = Rx * Ry mod2

MRB = Rx * Ry mod2 ....................................................... B-54

Rn = MRF + Rx * Ry mod2

Rn = MRB + Rx * Ry mod2

MRF = MRF + Rx * Ry mod2

MRB = MRB + Rx * Ry mod2 .......................................... B-55

Rn = MRF – Rx * Ry mod2

Rn = MRB – Rx * Ry mod2

MRF = MRF – Rx * Ry mod2

MRB = MRB – Rx * Ry mod2 .......................................... B-56

Rn = SAT MRF mod1

Rn = SAT MRB mod1

MRF = SAT MRF mod1

MRB = SAT MRB mod1 ................................................... B-57

Rn = RND MRF mod1

Rn = RND MRB mod1

MRF = RND MRF mod1

MRB = RND MRB mod1 .................................................. B-58

MRF = 0

MRB = 0 ....................................................................... B-59

MR = Rn/Rn = MR .............................................................. B-60

Fn = Fx * Fy ......................................................................... B-62

ADSP-21065L SHARC DSP Technical Reference vii

Page 8

CONTENTS

Shifter Operations ...................................................................... B-63

Rn = LSHIFT Rx BY Ry

Rn = LSHIFT Rx BY <data8> ............................................. B-65

Rn = Rn OR LSHIFT Rx BY Ry

Rn = Rn OR LSHIFT Rx BY <data8> ................................. B-66

Rn = ASHIFT Rx BY Ry

Rn = ASHIFT Rx BY <data8> ............................................ B-67

Rn = Rn OR ASHIFT Rx BY Ry

Rn = Rn OR ASHIFT Rx BY <data8> ................................ B-68

Rn = ROT Rx BY Ry

Rn = ROT Rx BY <data8> .................................................. B-69

Rn = BCLR Rx BY Ry

Rn = BCLR Rx BY <data8> ................................................ B-70

Rn = BSET Rx BY Ry

Rn = BSET Rx BY <data8> ................................................. B-71

Rn = BTGL Rx BY Ry

Rn = BTGL Rx BY <data8> ................................................ B-72

BTST Rx BY Ry

BTST Rx BY <data8> ......................................................... B-73

Rn = FDEP Rx BY Ry

Rn = FDEP Rx BY <bit6>:<len6> ....................................... B-74

Rn = Rn OR FDEP Rx BY Ry

Rn = Rn OR FDEP Rx BY <bit6>:<len6> ........................... B-76

Rn = FDEP Rx BY Ry (SE)

Rn = FDEP Rx BY <bit6>:<len6> (SE) .............................. B-78

Rn = Rn OR FDEP Rx BY Ry (SE)

Rn = Rn OR FDEP Rx BY <bit6>:<len6> (SE) ................... B-80

viii ADSP-21065L SHARC DSP Technical Reference

Page 9

CONTENTS

Rn = FEXT Rx BY Ry

Rn = FEXT Rx BY <bit6>:<len6> ...................................... B-82

Rn = FEXT Rx BY Ry (SE)

Rn = FEXT Rx BY <bit6>:<len6> (SE) ............................... B-84

Rn = EXP Rx ........................................................................ B-86

Rn = EXP Rx (EX) ............................................................... B-87

Rn = LEFTZ Rx ................................................................... B-88

Rn = LEFTO Rx .................................................................. B-89

Rn = FPACK Fx ................................................................... B-90

Fn = FUNPACK Rx ............................................................. B-92

Multifunction Computations ..................................................... B-94

Dual Add/Subtract (Fixed-Pt.) .............................................. B-96

Dual Add/Subtract (Floating-Pt.) .......................................... B-98

Parallel Multiplier and ALU (Fixed-Pt.) ................................ B-100

Parallel Multiplier & ALU (Floating-Point) .......................... B-101

Parallel Multiplier and Dual Add/Subtract ............................ B-104

ADSP-21065L SHARC DSP Technical Reference ix

Page 10

CONTENTS

NUMERIC FORMATS

Single-Precision Floating-Point Format ......................................... C-2

Extended-Precision Floating-Point Format .................................... C-4

Short Word Floating-Point Format ................................................ C-5

Fixed-Point Formats ..................................................................... C-8

JTAG TEST ACCESS PORT

Test Access Port (TAP) ................................................................. D-2

Instruction Register ..................................................................... D-3

Boundary Register ....................................................................... D-6

Device Identification Register .................................................... D-28

Built-In Self-Test Instructions (BIST) ........................................ D-28

Private Instructions .................................................................... D-29

References ................................................................................. D-29

CONTROL AND STATUS REGISTERS

System Registers ........................................................................... E-2

Latencies—Effect and Read ..................................................... E-4

System Register Bit Manipulation Instruction .......................... E-5

Bit Test Flag ............................................................................ E-6

ASTAT

Arithmetic Status Register .................................................... E-8

IMASK and IRPTL

Interrupt Mask and Latch Registers .................................... E-12

MODE1 Register .................................................................. E-16

MODE2 Register .................................................................. E-21

x ADSP-21065L SHARC DSP Technical Reference

Page 11

CONTENTS

Sticky Status Register (STKY) ................................................ E-27

IOP Registers .............................................................................. E-31

IOP Registers Summary ......................................................... E-31

IOP Register Access Restrictions ............................................ E-40

IOP Register Group Access Contention .................................. E-41

IOP Register Write Latencies ................................................. E-42

DMACx

External Port DMA Control Registers ................................. E-54

DMASTAT

DMA Channel Status Register ............................................ E-64

IOCTL

Programmable I/O and SDRAM Control Register ............... E-68

IOSTAT

Programmable I/O Status Register ....................................... E-75

RDIVx/TDIVx

SPORT Divisor Registers .................................................... E-78

SRCTLx

SPORT Receive Control Register ........................................ E-81

STCTLx

SPORT Transmit Control Register ...................................... E-90

SYSCON

System Configuration Register ............................................ E-99

SYSTAT

System Status Register ...................................................... E-106

WAIT

External Memory Wait State Control Register ................... E-111

ADSP-21065L SHARC DSP Technical Reference xi

Page 12

CONTENTS

SYMBOL DEFINITIONS FILE

(def21065L.h) ....................................................................... E-116

INTERRUPT VECTOR ADDRESSES

INDEX

xii ADSP-21065L SHARC DSP Technical Reference

Page 13

PREFACE

Listing 1-0.

Figure 1-0.

Table 1-0.

Congratulations on your purchase of Analog Devices ADSP-21065L

SHARC® DSP, the high-performance Digital Signal Processor of choice!

The ADSP-21065L is a 32-bit DSP with 544K bits of on-chip memory

that is designed to support a wide variety of applications—audio, automo-

tive, communications, industrial, and instrumentation.

For Additional Information About Analog Products

Analog Devices is online on the internet at http://www.analog.com. Our

Web pages provide information on the company and products, including

access to technical information and documentation, product overviews,

and product announcements. You may also obtain additional information

about Analog Devices and its products in any of the following ways:

• Visit our World Wide Web site at www.analog.com.

• FAX questions or requests for information to

• Send questions by mail to:

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

USA

ADSP-21065L SHARC DSP Technical Reference xiii

1(781)461-3010.

Page 14

For Technical or Customer Support

• Access the division’s File Transfer Protocol (FTP) site at ftp

ftp.analog.com or ftp 137.71.23.21 or ftp://ftp.anlog.com.

This site is a mirror of the BBS.

For Technical or Customer Support

You can reach our Customer Support group in the following ways:

• Visit our World Wide Web site at www.analog.com.

• Call the Analog Devices automated Customer Support Hot Line at

1(800)ANALOG-D.

• E-mail questions to dsp.support@analog.com or

dsp.europe@analog.com (European customer support).

What’s This Book About and Who’s It For?

The ADSP-21065L documentation set contains two manuals, the

ADSP-21065L SHARC DSP User’s Manual and the ADSP-21065L

SHARC DSP Technical Reference. These manuals are reference guides for

hardware and software engineers who want to develop applications using

the ADSP-21065L. These manuals assume that the user has a working

knowledge of the ADSP-21065L’s Super Harvard Architecture.

The ADSP-21065L SHARC DSP User’s Manual describes the architecture

and operation of the ADSP-21065L’s individual components, intercomponent connections and access, off-chip connections and access, and the

processor’s hardware/software interface.

xiv ADSP-21065L SHARC DSP Technical Reference

Page 15

Preface

The information in this book includes:

• Pin definitions and instructions for connecting the pins to external

devices and peripherals in single- and multiprocessor systems.

• Processor features and instructions for configuring the processor for

specific operation options.

• Internal and external data paths and instructions for moving data

between internal components and between the processor and external devices and peripherals.

• Timing, sequencing, and throughput of control signals and data

accesses.

The ADSP-21065L SHARC DSP Technical Reference provides detailed

technical information on programming the ADSP-21065L. This information includes:

• A description of each instruction in the processor’s instruction set,

supported numeric formats, and the default bit definitions for all of

the processor’s control and status registers.

• A description of the pins and the control and data registers of the

JTAG test access port.

• A list of all vector interrupts and their addresses.

To supplement the information in these manuals, users can attend scheduled workshops sponsored by Analog Devices, Inc. (ADI) and access other

ADI documentation related specifically to this product. For details, see

“Related Documents” on page xviii.

ADSP-21065L SHARC DSP Technical Reference xv

Page 16

How to Use This Manual

How to Use This Manual

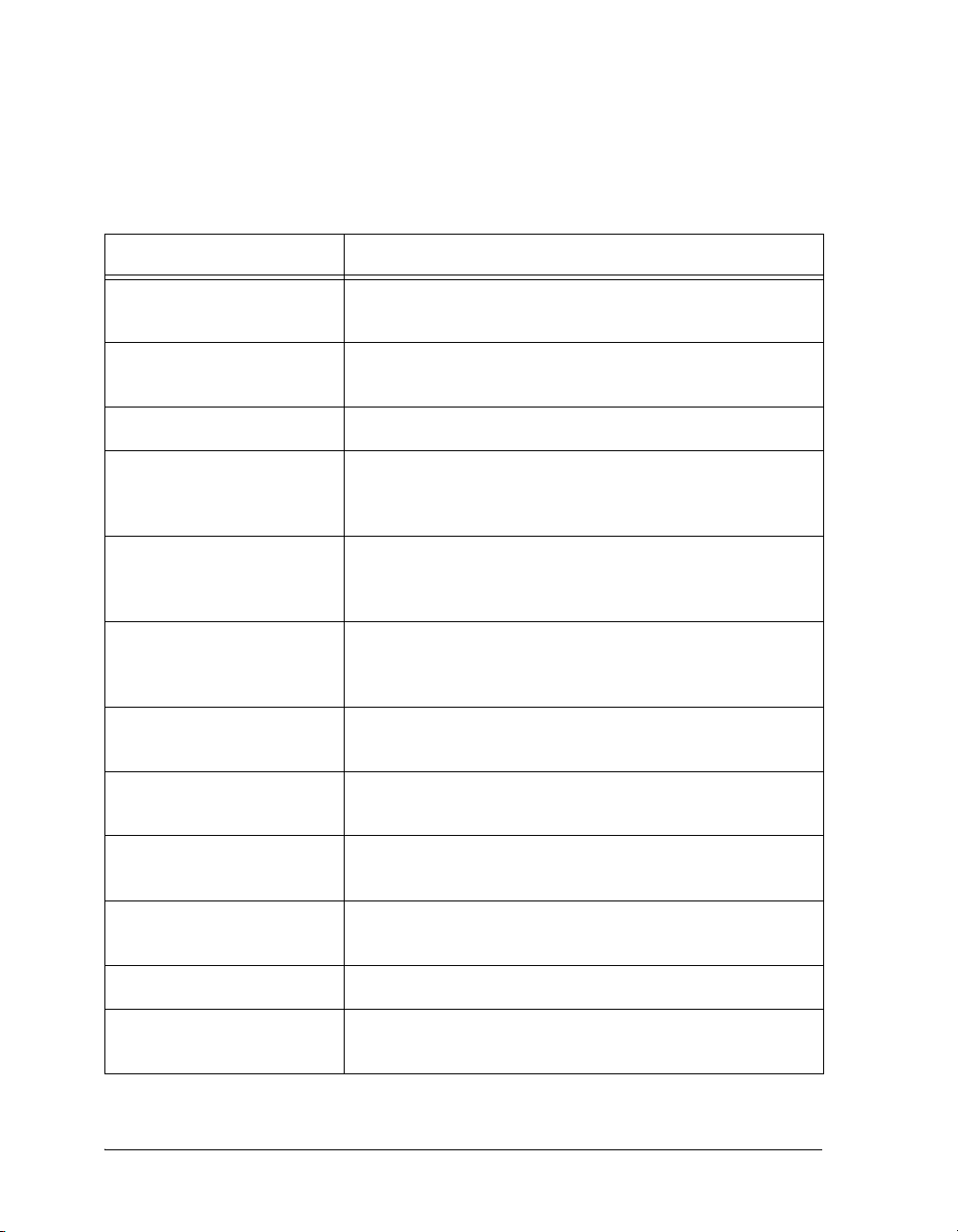

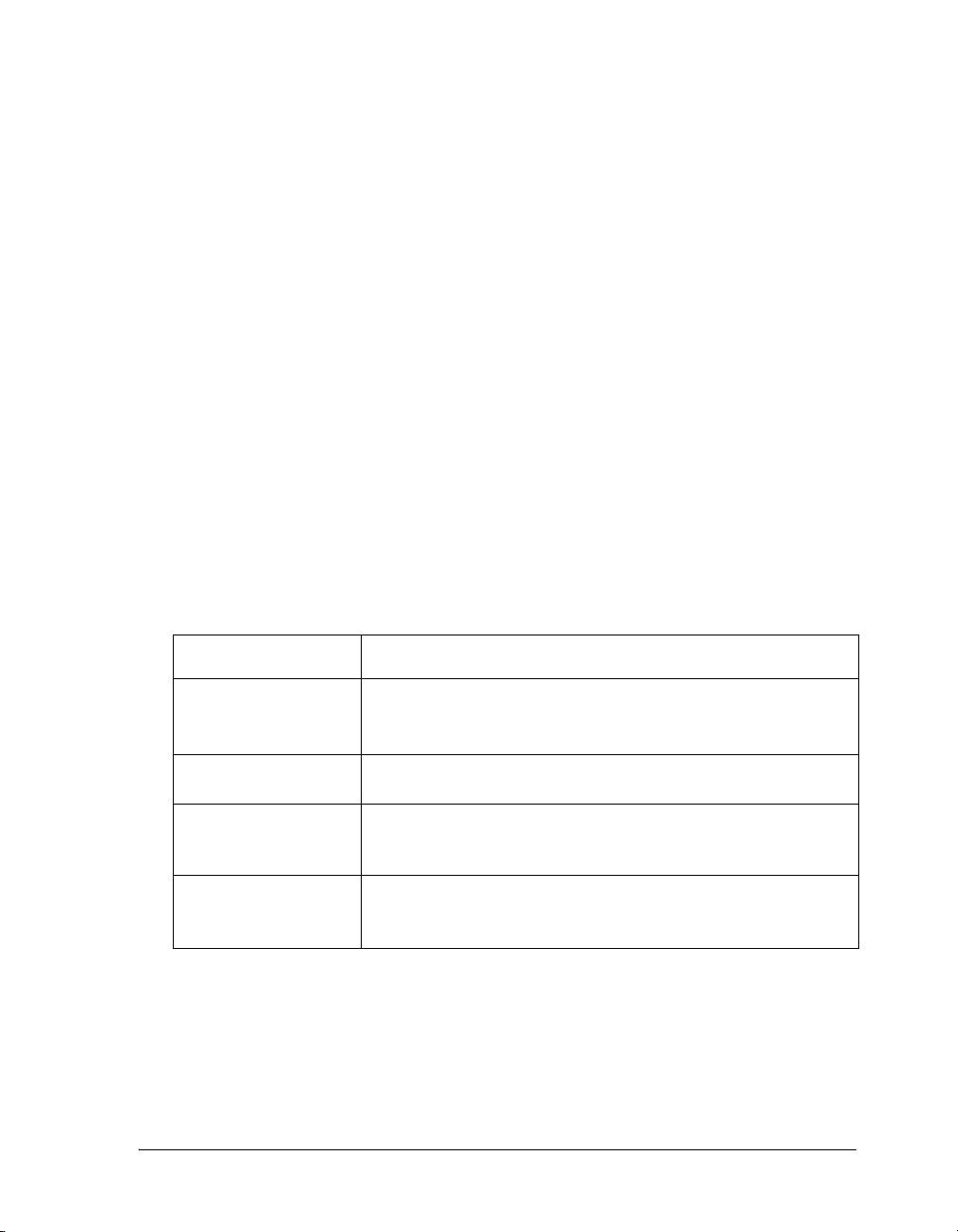

For information on… See…

ALU operation Chapter 2, Computation Units; Appendix B,

Compute Operation Reference

Address generation Chapter 4, Data Addressing; Chapter 5, Mem-

ory; Chapter 6, DMA

Booting Chapter 5, Memory; Chapter 7, System Design

Clock generation Chapter 9, Serial Ports; Chapter 11, Pro-

grammable Timers and I/O Ports; Chapter 12,

System Design

Computation units Chapter 2, Computation Units; Appendix B,

Compute Operation Reference; Appendix C,

Numeric Formats

Data delays,

latencies,

throughput

Data packing Chapter 6, DMA; Chapter 8, Host Interface;

DMA Chapter 6, DMA; Chapter 7, Multiprocessing;

External port Chapter 6, DMA; Chapter 7, Multiprocessing;

High-frequency design

issues

Host interface Chapter 8, Host Interface

Instruction cache Chapter 3, Program Sequencing; Chapter 5,

Chapter 10, SDRAM Interface; Chapter 12,

System Design

Chapter 9, Serial Ports

Chapter 8, Host Interface

Chapter 8, Host Interface

Chapter 12, System Design

Memory

xvi ADSP-21065L SHARC DSP Technical Reference

Page 17

Preface

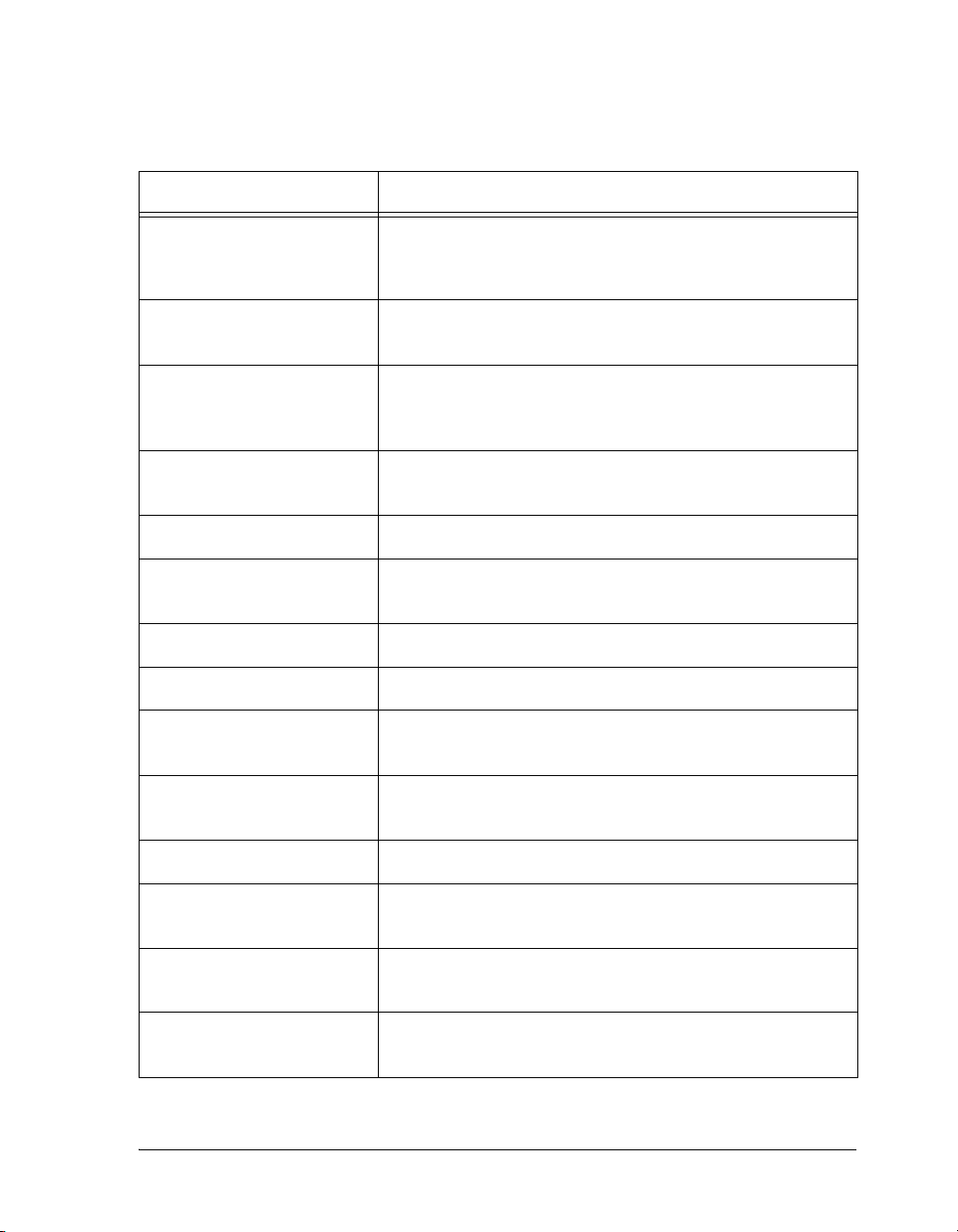

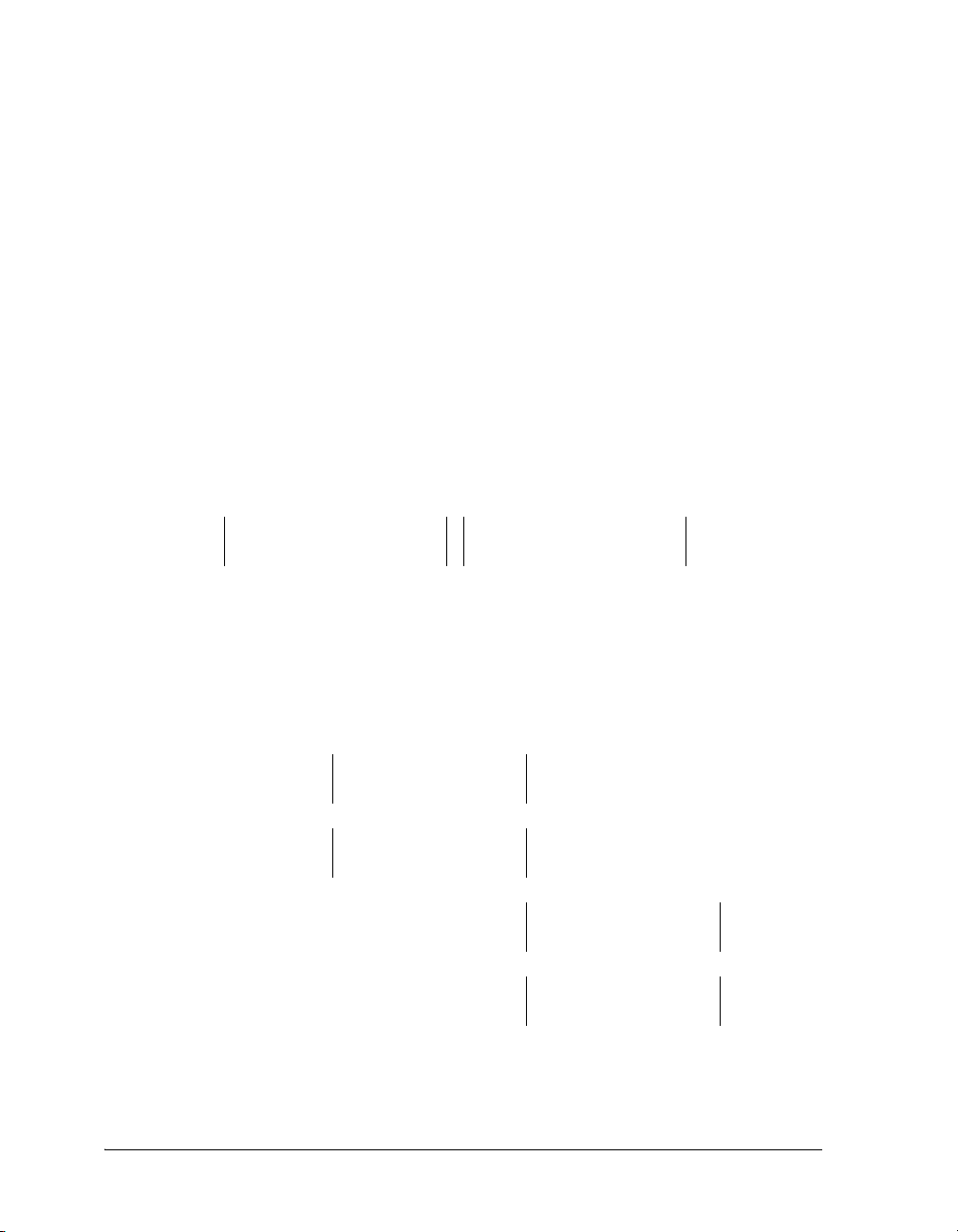

For information on… See…

Instruction set Appendix A, Instruction Set Reference;

Appendix B, Compute Operation Reference;

Appendix C, Numeric Formats

Internal buses Chapter 5, Memory; Chapter 6, DMA; Chapter

8, Host Interface

Interrupts Chapter 3, Program Sequencing; Chapter 5,

Memory; Appendix F, Interrupt Vector

Addresses

JTAG test port Chapter 12, System Design; Appendix D, JTAG

Test Access Port

Memory Chapter 5, Memory

Multiplier operation Chapter2, Computation Units; Appendix B,

Compute Operation Reference

Multiprocessing Chapter 7, Multiprocessing

Pin definitions Chapter 12, System Design

Processor

architecture

Processor

configuration

Program flow Chapter 3, Program Sequencing

Programmable I/O

ports

Programmable timers Chapter 11, Programmable Timers and I/O

Programming

considerations

Chapter 1, Introduction

Appendix E, Control and Status Registers

Chapter 11, Programmable Timers and I/O

Ports

Ports

Chapter 13, Programming Considerations

ADSP-21065L SHARC DSP Technical Reference xvii

Page 18

Related Documents

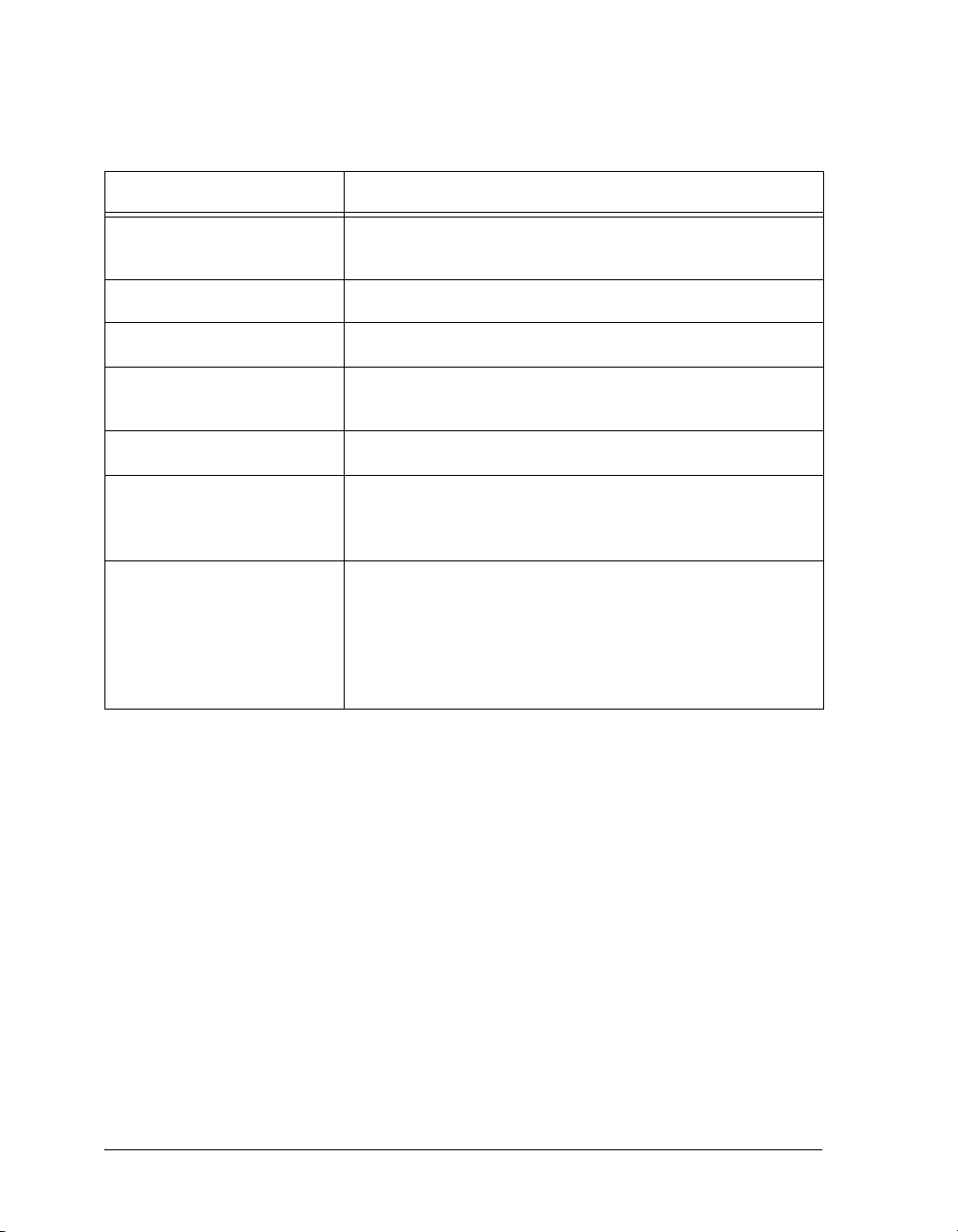

For information on… See…

Reset Chapter 7, Multiprocessing; Chapter 9,

Serial Ports; Chapter 12, System Design

SDRAM interface Chapter 10 SDRAM Interface

Serial ports Chapter 9, Serial Ports

Shifter operation Chapter 2, Computation Units; Appendix B,

Compute Operation Reference

System Design Chapter 12, System Design

Wait states Chapter 5, Memory; Chapter 12, System

Design; Appendix E, Control and Status Registers

Indexes Both manuals are cross-indexed. Pages with

an alphabetic prefix (as C-12) reference

information in ADSP-21065L SHARC DSP Techni-

cal Reference. Pages with a numeric prefix

(as 5-41) reference information in

ADSP-21065L SHARC DSP User’s Manual.

Related Documents

For information on related products, see the following documents available from Analog Devices, Inc.:

• ADSP-21065L SHARC DSP, 198 MFLOPS, 3.3v Data Sheet

(Rev. C, 6/03)

• VisualDSP++ Quick Installation Reference Card

• VisualDSP++ 3.0 User’s Guide for SHARC DSPs

• VisualDSP++ 3.0 Getting Started Guide for SHARC DSPs

xviii ADSP-21065L SHARC DSP Technical Reference

Page 19

Preface

• VisualDSP++ 3.0 C/C++ Compiler and Library Manual for SHARC

DSPs

• VisualDSP++ 3.0 Linker and Utilities Manual for SHARC DSPs

• VisualDSP++ 3.0 Assembler and Preprocessor Manual for SHARC

DSPs

• VisualDSP++ 3.0 Kernel (VDK) User’s Guide

• VisualDSP++ 3.0 Component Software Engineering User’s Guide

Conventions of Notation

The following conventions apply to all chapters within this manual. Additional conventions that apply to specific chapters only are documented at

the beginning of the chapter in which they appear.

This notation… Denotes…

Letter Gothic

font

Italics Special terminology; titles of books.

*

,

Code, software or command line options or keywords; input you must enter from the keyboard.

A hint or tip.

A warning or caution.

ADSP-21065L SHARC DSP Technical Reference xix

Page 20

Conventions of Notation

xx ADSP-21065L SHARC DSP Technical Reference

Page 21

A INSTRUCTION SET

REFERENCE

Figure A-0.

Table A-0.

Listing A-0.

Appendix A and B describe the processor’s instruction set. This appendix

explains each instruction type, including the assembly language syntax and

opcodes, which result from instruction assembly.

Many instructions’ opcodes contain a COMPUTE field that specifies a compute operation using the ALU, Multiplier, or Shifter. Because a large

number of options are available for computations, their descriptions

appear in Appendix B.

Because data moves between the MR registers and the Register File are

considered Multiplier operations, their descriptions appear in Appendix B.

ADSP-21065L SHARC DSP Technical Reference A-1

Page 22

Instruction Summary

Instruction Summary

Each instruction is specified in this appendix. The reference page for an

instruction shows the syntax of the instruction, describes its function,

gives one or two assembly-language examples, and identifies fields of its

opcode. The instruction types are organized into four groups:

• “Group I Instructions (Compute & Move)” on page A-28

These instruction specify a compute operation in parallel with one

or two data moves or an index register modify.

• “Group II Instructions (Program Flow Control)” on page A-44

These instructions specify various types of branches, calls, returns,

and loops. Some may also specify a compute operation or a data

move.

• “Group III Instructions (Immediate Move)” on page A-62

These instructions use immediate instruction fields as operators for

addressing.

• “Group IV Instructions (Miscellaneous)” on page A-70

These instructions include bit modify, bit test, no operation, and

idle.

The instructions are referred to by type, ranging from 1 to 23. These types

correspond to the opcodes that the processor recognizes, but are for reference only and have no bearing on programming.

Some instructions have more than one syntactical form; for example,

instruction “Compute/dregÙDM|PM, immediate modify (Type 4)” on

page A-35 has four distinct forms.

A-2 ADSP-21065L SHARC DSP Technical Reference

Page 23

Instruction Set Reference

Many instructions can be conditional. These instructions are prefaced by

IF COND; for example:

If COND compute, |DM(Ia,Mb)| = ureg;

In a conditional instruction, the execution of the entire instruction is

based on the specified condition.

ADSP-21065L SHARC DSP Technical Reference A-3

Page 24

Instruction Summary

Compute and Move/Modify Summary

Compute and move/modify instructions are classed as Group I instructions, and they provide math, conditional, memory or register access

services. For a complete description of these instructions, see the noted

pages.

*

For all compute and move/modify instructions, IF

COND is optional.

“Compute/dregÙDM/dregÙPM (Type 1)” page A-30

compute , DM(Ia, Mb) = dreg1 , PM(Ic, Md) = dreg2 ;

, dreg1 = DM(Ia, Mb) , dreg2 = PM(Ic, Md)

“Compute (Type 2)” on page A-32

IF COND compute ;

“Compute/uregÙDM|PM, register modify (Type 3)” on page A-33

IF COND compute , DM(Ia, Mb) = ureg ;

, PM(Ic, Md)

, DM(Mb, Ia) = ureg ;

, PM(Md, Ic)

, ureg = DM(Ia, Mb) ;

PM(Ic, Md) ;

, ureg = DM(Mb, Ia) ;

PM(Md, Ic) ;

A-4 ADSP-21065L SHARC DSP Technical Reference

Page 25

Instruction Set Reference

“Compute/dregÙDM|PM, immediate modify (Type 4)” on page A-35

IF COND compute , DM(Ia, <data6>) = dreg ;

, PM(Ic, <data6>)

, DM(<data6>, Ia) = dreg ;

, PM(<data6>, Ic)

, dreg = DM(Ia, <data6>) ;

PM(Ic, <data6>) ;

, dreg = DM(<data6>, Ia) ;

PM(<data6>, Ic) ;

“Compute/uregÙureg (Type 5)” on page A-37

IF COND compute, ureg1 = ureg2 ;

“Immediate Shift/dregÙDM|PM (Type 6)” on page A-39

IF COND shiftimm , DM(Ia, Mb) = dreg ;

, PM(Ic, Md)

, dreg = DM(Ia, Mb) ;

PM(Ic, Md) ;

“Compute/modify (Type 7)” on page A-42

IF COND compute , MODIFY (Ia, Mb) ;

(Ic, Md) ;

ADSP-21065L SHARC DSP Technical Reference A-5

Page 26

Instruction Summary

Program Flow Control Summary

Program flow control instructions are classed as Group II instructions,

and they provide control of program execution flow. For a complete

description of these instructions, see the noted pages.

*

instructions, IF COND is optional.

“Direct Jump|Call (Type 8)” on page A-45

For all program flow control instructions, except type 10

IF COND

JUMP

IF COND

CALL

<addr24> (DB) ;

(PC, <reladdr24>) (LA)

(CI)

(DB, LA)

(DB, CI)

<addr24> (DB) ;

(PC, <reladdr24>)

“Indirect Jump|Call / Compute (Type 9)” on page A-48

IF COND

JUMP

(Md, Ic) (DB) , compute ;

(PC, <reladdr6>) (LA) , ELSE compute

(CI)

(DB, LA)

(DB, CI)

IF COND

CALL

(Md, Ic) (DB) , compute ;

(PC, <reladdr6>) , ELSE compute

“Indirect Jump or Compute/dregÙDM (Type 10)” on page A-52

IF COND

Jump

(Md, Ic) , Else compute, DM(Ia, Mb) = dreg ;

(PC, <reladdr6> compute, dreg = DM(Ia, Mb) ;

A-6 ADSP-21065L SHARC DSP Technical Reference

Page 27

Instruction Set Reference

“Return From Subroutine|Interrupt/Compute (Type 11)” on page A-55

IF COND RTS (DB) , compute ;

(LR) , ELSE compute

(DB, LR)

IF COND RTI (DB) , compute ;

, ELSE compute

“Do Until Counter Expired (Type 12)” on page A-58

LCNTR = <data16> , DO <addr24> UNTIL LCE ;

ureg (<PC, reladdr24>)

“Do Until (Type 13)” on page A-60

DO <addr24> UNTIL termination ;

(PC, <reladdr24>)

ADSP-21065L SHARC DSP Technical Reference A-7

Page 28

Instruction Summary

Immediate Move Summary

Immediate move instructions are classed as Group III instructions, and

they provide memory and register access services. For a complete description of these instructions, see the noted pages.

“UregÙDM|PM (direct addressing) (Type 14)” on page A-63

DM(<addr32>)

PM(<addr24>)

ureg = DM(<addr32>) ;

= ureg ;

PM(<addr24>)

“UregÙDM|PM (indirect addressing) (Type 15)” on page A-65

DM(<data32>, Ia)

PM(<data24>, Ic)

ureg = DM(<data32>, Ia) ;

= ureg ;

PM(<data24>, Ic) ;

“Immediate dataÖDM|PM (Type 16)” on page A-67

DM(Ia, Mb)

PM(Ic, Md)

= <data32> ;

“Immediate dataÖureg (Type 17)” on page A-69

ureg = <data32> ;

A-8 ADSP-21065L SHARC DSP Technical Reference

Page 29

Instruction Set Reference

Miscellaneous Instructions Summary

Miscellaneous instructions are classed as Group IV instructions, and they

provide system register, bit manipulation, and low power services. For a

complete description of these instructions, see the noted pages.

“System Register Bit Manipulation (Type 18)” on page A-71

BIT SET sreg <data32> ;

CLR

TGL

TST

XOR

“Register Modify/bit-reverse (Type 19)” on page A-73

MODIFY (Ia, <data32>) ;

(Ic, <data24>)

BITREV (Ia, <data32>) ;

(Ic, <data24>)

“Push|Pop Stacks/Flush Cache (Type 20)” on page A-75

PUSH LOOP , PUSH STS , PUSH PCSTK , FLUSH CACHE ;

POP POP POP

“Nop (Type 21)” on page A-77

NOP ;

“Idle (Type 22)” on page A-78

IDLE ;

ADSP-21065L SHARC DSP Technical Reference A-9

Page 30

Instruction Summary

“Idle16 (Type 23)” on page A-79

IDLE16 ;

“Cjump/Rframe (Type 24)” on page A-81

CJUMP function (DB) ;

(PC, <reladdr24>)

RFRAME ;

A-10 ADSP-21065L SHARC DSP Technical Reference

Page 31

Instruction Set Reference

Reference Notation Summary

The conventions for instruction syntax descriptions appear in Table A-1.

This section also covers other parts of the instruction syntax and opcode

information.

Table A-1. Instruction set notation

Notation Meaning

Ù, Ö

UPPERCASE Explicit syntax—assembler keyword (notation

; Semicolon (instruction terminator)

, Comma (separates parallel operations in an

italics Optional part of instruction

{comment} Brackets enclose comments or remarks that

|option1|

| option2 |

compute ALU, Multiplier, Shifter or multifunction oper-

shiftimm Shifter immediate operation (see Appendix B,

Data transfer (read/write) direction.

only; assembler is case-insensitive and lowercase is the preferred programming convention)

instruction)

explain code. Ignored by assembler.

List of options between vertical bars (choose

one)

ation (see Appendix B, Compute Operation Refer-

ence)

Compute Operation Reference)

condition Status condition (see Table A-2 on page A-13)

termination Loop termination condition (see Table A-2 on

page A-13)

ADSP-21065L SHARC DSP Technical Reference A-11

Page 32

Instruction Summary

Table A-1. Instruction set notation (Cont’d)

Notation Meaning

ureg Universal register

sreg System register

dreg Data register (Register File): R15-R0 or F15-F0

Ia I7-I0 (DAG1 index register)

Mb M7-M0 (DAG1 modify register)

Ic I15-I8 (DAG2 index register)

Md M15-M8 (DAG2 modify register)

<datan> n-bit immediate data value

<addrn> n-bit immediate address value

<reladdrn> n-bit immediate PC-relative address value

(DB) Delayed branch

(LA) Loop abort (pop loop and PC stacks on branch)

(CI) Clear interrupt

A-12 ADSP-21065L SHARC DSP Technical Reference

Page 33

Instruction Set Reference

In a conditional instruction, execution of the entire instruction depends

on the specified condition (cond or terminate). Table A-2 lists the codes

that you can use in conditionals.

Table A-2. Condition and termination codes (IF & DO UNTIL)

Condition Description

EQ ALU equal zero

LT ALU less than zero

LE ALU less than or equal zero

AC ALU carry

AV ALU overflow

MV Multiplier overflow

MS Multiplier sign

SV Shifter overflow

SZ Shifter zero

FLAG0_IN Flag 0 input

FLAG1_IN Flag 1 input

FLAG2_IN Flag 2 input

FLAG3_IN Flag 3 input

TF Bit test flag

BM Bus master

LCE Loop counter expired (DO UNTIL)

ADSP-21065L SHARC DSP Technical Reference A-13

Page 34

Instruction Summary

Table A-2. Condition and termination codes (IF & DO UNTIL) (Cont’d)

Condition Description

NOT LCE Loop counter not expired (IF)

NE ALU not equal to zero

GE ALU greater than or equal zero

GT ALU greater than zero

NOT AC Not ALU carry

NOT AV Not ALU overflow

NOT MV Not Multiplier overflow

NOT MS Not Multiplier sign

NOT SV Not Shifter overflow

NOT SZ Not Shifter zero

NOT FLAG0_IN Not Flag 0 input

NOT FLAG1_IN Not Flag 1 input

NOT FLAG2_IN Not Flag 2 input

NOT FLAG3_IN Not Flag 3 input

NOT TF Not bit test flag

NBM Not bus master

FOREVER Always false (DO UNTIL)

TRUE Always true (IF)

A-14 ADSP-21065L SHARC DSP Technical Reference

Page 35

Instruction Set Reference

Register Types Summary

The processor contains three types of registers: Universal registers, Multiplier registers, and IOP registers. Table A-3 and Table A-4 list the

Universal and Multiplier registers, which are associated with the processor’s core. The IOP registers are associated with the processor’s I/O

processor and are described in Appendix E, Control and Status Registers.

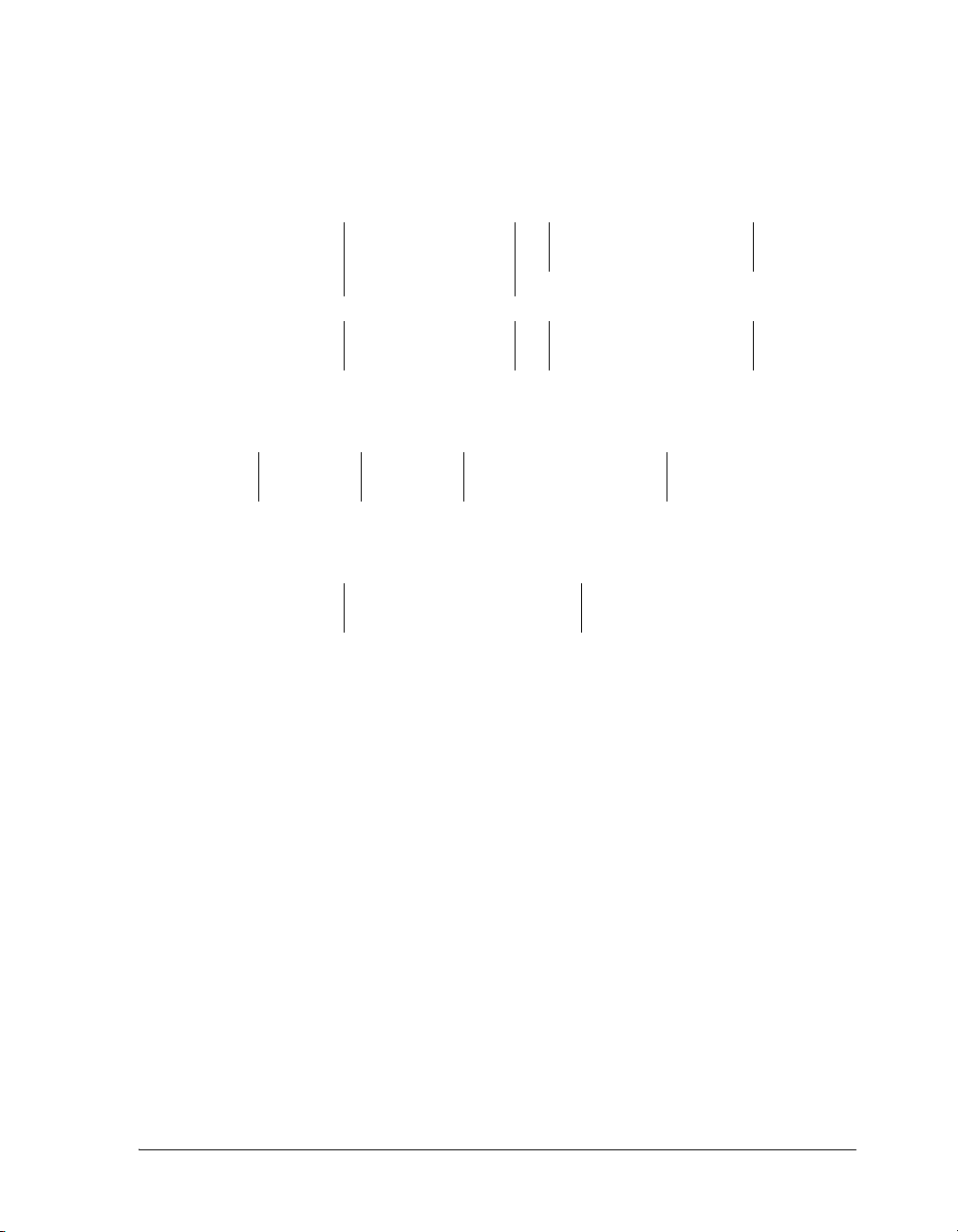

Table A-3. Universal registers (UREG)

Type Subregisters Function

Register File R0–R15 Register file locations,

fixed-point

F0–F15 Register file locations,

floating-point

Program

Sequencer

Data Address

Generators

PC Program counter (read-only)

PCSTK Top of PC stack

PCSTKP PC stack pointer

FADDR Fetch address (read-only)

DADDR Decode address (read-only)

LADDR Loop termination address,

code; top of loop address stack

CURLCNTR Current loop counter; top of

loop count stack

LCNTR Loop count for next nested

counter-controlled loop

I0–I7 DAG1 index registers

ADSP-21065L SHARC DSP Technical Reference A-15

Page 36

Instruction Summary

Table A-3. Universal registers (UREG) (Cont’d)

Type Subregisters Function

Data Address M0–M7 DAG1 modify registers

Generators L0–L7 DAG1 length registers

(Cont’d) B0–B7 DAG1 base registers

I8–I15 DAG2 index registers

M8– M15 DAG2 modify registers

L8–L15 DAG2 length registers

B8–B15 DAG2 base registers

Bus Exchange PX1 PMD-DMD bus exchange 1 (16

bits)

PX2 PMD-DMD bus exchange 2 (32

bits)

PX 48-bit combination of PX1 and

PX2

System Registers (core)

MODE1 Mode control and status

MODE2 Mode control and status

IRPTL Interrupt latch

IMASK Interrupt mask

IMASKP Interrupt mask pointer (for

nesting)

ASTAT Arithmetic status flags, bit

test flag, etc.

A-16 ADSP-21065L SHARC DSP Technical Reference

Page 37

Instruction Set Reference

Table A-3. Universal registers (UREG) (Cont’d)

Type Subregisters Function

System

Registers

(Cont’d) USTAT1 User status register 1

STKY Sticky arithmetic status

flags, stack status flags,

etc.

USTAT2 User status register 2

Table A-4. Multiplier registers

Registers Function

MR, MR0–MR2 Multiplier results

MRF, MR0F–MR2F Multiplier results, foreground

MRB, MR0B–MR2B Multiplier results, background

ADSP-21065L SHARC DSP Technical Reference A-17

Page 38

Instruction Summary

Memory Addressing Summary

The processor supports the following types of addressing:

Direct Addressing

Absolute address (Instruction Types 8, 12, 13, 14)

dm(0x000015F0) = astat;

if ne jump label2; {'label2' is an address label}

PC-relative address (Instruction Types 8, 9, 10, 12, 13)

call(pc,10), r0=r6+r3;

do(pc,length) until sz; {'length' is a variable}

Indirect Addressing (using DAG registers):

Postmodify with M register, update I register

(Instruction Types 1, 3, 6, 16)

f5=pm(i9,m12);

dm(i0,m3)=r3, r1=pm(i15,m10);

Premodify with M register, no update

(Instruction Types 3, 9, 10)

r1=pm(m10,i15);

jump(m13,i11);

Postmodify with immediate value, update I register

(Instruction Type 4)

f15=dm(i0,6);

if av r1=pm(i15,0x11);

Premodify with immediate value, no update

(Instruction Types 4, 15)

if av r1=pm(0x11,i15);

dm(127,i5)=laddr;

A-18 ADSP-21065L SHARC DSP Technical Reference

Page 39

Instruction Set Reference

Opcode Notation

In the processor’s opcodes, some bits are explicitly defined as zeros (0s) or

ones (1s). The values of other bits or fields set various parameters for the

instruction. The processor ignores unspecified bits when it decodes the

instruction, but reserves the bits for future use. Table A-5 lists and defines

the bits, fields, and states of these opcodes.

Table A-5. Opcode acronyms

Bit/Field Description States

A Loop abort code

ADDR Immediate address field

AI Computation unit regis-

ter

B Branch type

BOP Bit Operation select

codes

0 Do not pop loop, PC

stacks on branch

1 Pop loop, PC stacks

on branch

0000 MR0F

0001 MR1F

0010 MR2F

0100 MR0B

0101 MR1B

0110 MR2B

0 Jump

1 Call

000 Set

001 Clear

010 Toggle

100 Test

101 XOR

ADSP-21065L SHARC DSP Technical Reference A-19

Page 40

Opcode Notation

Table A-5. Opcode acronyms (Cont’d)

Bit/Field Description States

COMPUTE Compute operation field

(see Appendix B, Com-

pute Operation Reference)

COND Status Condition codes

CI Clear interrupt code

CU Computation unit select

codes

DATA Immediate data field

DEC Counter decrement code

DMD Memory access direction

DMI Index (I) register num-

bers, DAG1

DMM Modify (M) register

numbers, DAG1

0–31

0 Do not clear current

interrupt

1 Clear current inter-

rupt

00 ALU

01 Multiplier

10 Shifter

0 No counter decrement

1 Counter decrement

0 Read

1 Write

0–7

0–7

DREG Register file locations

E ELSE clause code

0–15

0 No ELSE clause

1 ELSE clause

A-20 ADSP-21065L SHARC DSP Technical Reference

Page 41

Instruction Set Reference

Table A-5. Opcode acronyms (Cont’d)

Bit/Field Description States

FC Flush cache code

G DAG/Memory select

INC Counter increment code

J Jump Type

LPO Loop stack pop code

LPU Loop stack push code

LR Loop reentry code

NUM Interrupt vector

OPCODE Computation unit

opcodes (see

Appendix B, Compute

Operation Reference)

0 No cache flush

1 Cache flush

0 DAG1 or Data Memory

1 DAG2 or Program Mem-

ory

0 No counter increment

1 Counter increment

0 nondelayednondelayed

1 Delayed

0 No stack pop

1 Stack pop

0 No stack push

1 Stack push

0 No loop reentry

1 Loop reentry

0 - 7

PMD Memory access direction

PMI Index (I) register num-

bers, DAG2

ADSP-21065L SHARC DSP Technical Reference A-21

0 Read

1 Write

8–15

Page 42

Opcode Notation

Table A-5. Opcode acronyms (Cont’d)

Bit/Field Description States

PMM Modify (M) register

numbers, DAG2

PPO PC stack pop code

PPU PC stack push code

RELADDR PC-relative address

field

SPO Status stack pop code

SPU Status stack push code

SREG System Register code

TERM Termination Condition

codes

U Update, index (I) reg-

ister

8–15

0 No stack pop

1 Stack pop

0 No stack push

1 Stack push

0 No stack pop

1 Stack pop

0 No stack push

1 Stack push

0–15 (see “Universal

Register Codes” on

page A-24)

0–31

0 Premodify, no update

1 Postmodify with

update

UREG Universal Register code

RA, RM, RN,

RS, RX, RY

Register file locations for compute operands and results

0–256 (see “Universal

Register Codes” on

page A-24)

0–15

A-22 ADSP-21065L SHARC DSP Technical Reference

Page 43

Instruction Set Reference

Table A-5. Opcode acronyms (Cont’d)

Bit/Field Description States

RXA ALU x-operand Register

File location for multifunction operations

RXM Multiplier x-operand

Register File location

for multifunction operations

RYA ALU y-operand Register

File location for multifunction operations

RYM Multiplier y-operand

Register File location

for multifunction operations

8–11

0–3

12–15

4–7

ADSP-21065L SHARC DSP Technical Reference A-23

Page 44

Opcode Notation

Universal Register Codes

Table A-6, Table A-7, Table A-8, Table A-9, and Table A-10 in this sec-

tion list the bit codes for registers that appear within opcode fields.

Table A-6. Map 1 registers

Register Description

PC program counter

PCSTK top of PC stack

PCSTKP PC stack pointer

FADDR fetch address

DADDR decode address

LADDR loop termination address

CURLCNTR current loop counter

LCNTR loop counter

R15–R0 Register File locations

I15 –I0 DAG1 and DAG2 index registers

M15–M0 DAG1 and DAG2 modify registers

L15–L0 DAG1 and DAG2 length registers

B15–B0 DAG1 and DAG2 base registers

A-24 ADSP-21065L SHARC DSP Technical Reference

Page 45

Table A-7. Map 1 system registers

Register Description

MODE1 mode control 1

MODE2 mode control 2

IRPTL interrupt latch

IMASK interrupt mask

IMASKP interrupt mask pointer

ASTAT arithmetic status

STKY sticky status

USTAT1 user status reg 1

Instruction Set Reference

USTAT2 user status reg 2

Table A-8. Map 2 registers

Register Description

PX 48-bit PX1 and PX2 combination

PX1 bus exchange 1 (16 bits)

PX2 bus exchange 2 (32 bits)

ADSP-21065L SHARC DSP Technical Reference A-25

Page 46

Opcode Notation

Table A-9. Map 1, universal register codes

Bits Bits:7654

3210 0000 0001 0010 0011 0100 0101 0110 0111

0000 R0 I0 M0 L0 B0 FADDR USTAT1

0001 R1 I1 M1 L1 B1 DADDR USTAT2

0010 R2 I2 M2 L2 B2

0011 R3 I3 M3 L3 B3 PC

0100 R4 I4 M4 L4 B4 PCSTK

0101 R5 I5 M5 L5 B5 PCSTKP

0110 R6 I6 M6 L6 B6 LADDR

0111 R7 I7 M7 L7 B7 CURL-

1000 R8 I8 M8 L8 B8 LCNTR

1001 R9 I9 M9 L9 B9 IRPTL

1010 R10 I10 M10 L10 B10 MODE2

1011 R11 I11 M11 L11 B11 MODE1

1100 R12 I12 M12 L12 B12 ASTAT

1101 R13 I13 M13 L13 B13 IMASK

1110 R14 I14 M14 L14 B14 STKY

1111 R15 I15 M15 L15 B15 IMASKP

CNTR

A-26 ADSP-21065L SHARC DSP Technical Reference

Page 47

Instruction Set Reference

Table A-10. Map 2, universal register codes

Bits: Bits: 7654

3210 1000 1001 1010 1011 1100 1101 1110 1111

0000

.

.

.

1011 PX

1100 PX1

1101 PX2

.

.

.

1111

ADSP-21065L SHARC DSP Technical Reference A-27

Page 48

Group I Instructions (Compute & Move)

Group I Instructions (Compute & Move)

• “Compute/dregÙDM/dregÙPM (Type 1)” on page A-30.

Parallel data memory and program memory transfers with Register

File, optional compute operation.

• “Compute (Type 2)” on page A-32.

Compute operation, optional condition.

• “Compute/uregÙDM|PM, register modify (Type 3)” on

page A-33.

Transfer between data or program memory and universal register,

optional condition, optional compute operation.

• “Compute/dregÙDM|PM, immediate modify (Type 4)” on

page A-35.

PC-relative transfer between data or program memory and Register

File, optional condition, optional compute operation.

• “Compute/uregÙureg (Type 5)” on page A-37.

Transfer between two universal registers, optional condition,

optional compute operation.

• “Immediate Shift/dregÙDM|PM (Type 6)” on page A-39.

Immediate shift operation, optional condition, optional transfer

between data or program memory and Register File.

A-28 ADSP-21065L SHARC DSP Technical Reference

Page 49

Instruction Set Reference

• “Compute/modify (Type 7)” on page A-42.

Index register modify, optional condition, optional compute operation.

*

For all compute and move/modify instructions, IF

COND is optional.

ADSP-21065L SHARC DSP Technical Reference A-29

Page 50

Group I Instructions (Compute & Move)

Compute/dregÙDM/dregÙPM (Type 1)

Parallel data memory and program memory transfers with Register File,

option compute operation.

Syntax

compute , DM(Ia, Mb) = dreg1 , PM(Ic, Md) = dreg2 ;

, dreg1 = DM(Ia, Mb) , dreg2 = PM(Ic, Md)

Function

Parallel accesses to data memory and program memory from the Register

File. The specified I registers address data memory and program memory.

The I values are postmodified and updated by the specified M registers.

Premodify offset addressing is not supported. For more information on

register restrictions, see Chapter 4, Data Addressing, in ADSP-21065L

SHARC DSP User’s Manual.

Examples

R7=BSET R6 BY R0, DM(I0,M3)=R5, PM(I11,M15)=R4;

R8=DM(I4,M1), PM(I12 M12)=R0;

Type 1 Opcode

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

001DM

222120191817161514131211109876543210

DMI DMMPMDDM DREG PMI PMM PM DREG

D

COMPUTE

A-30 ADSP-21065L SHARC DSP Technical Reference

Page 51

Instruction Set Reference

Bits Description

DMD, PMD Select the access types (read or write).

DM DREG,

PM DREG

DMI, PMI Specify I registers for data and program memory.

DMM, PMM Specify M registers used to update the I regis-

COMPUTE Defines a compute operation to be performed in

Specify Register File locations.

ters.

parallel with the data accesses; this is a NOP if

no compute operation is specified in the instruction.

ADSP-21065L SHARC DSP Technical Reference A-31

Page 52

Group I Instructions (Compute & Move)

Compute (Type 2)

Compute operation, optional condition.

Syntax

IF COND compute ;

Function

Conditional compute instruction. The instruction is executed if the specified condition tests true.

Examples

IF MS MRF=0;

F6=(F2+F3)/2;

Type 2 Opcode

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

000 00001 COND

222120191817161514131211109876543210

COMPUTE

Bits Description

COND Selects whether the operation specified in the

COMPUTE field is executed. If the COND is true,

the compute is executed. If no condition is specified, COND is TRUE condition, and the compute is

executed.

A-32 ADSP-21065L SHARC DSP Technical Reference

Page 53

Instruction Set Reference

Compute/uregÙDM|PM, register modify (Type 3)

Transfer operation between data or program memory and universal register, optional condition, optional compute operation.

Syntax

IF COND compute , DM(Ia, Mb) = ureg ;

, PM(Ic, Md)

, DM(Mb, Ia) = ureg ;

, PM(Md, Ic)

, ureg = DM(Ia, Mb) ;

PM(Ic, Md) ;

, ureg = DM(Mb, Ia) ;

PM(Md, Ic) ;

Function

Access between data memory or program memory and a universal register.

The specified I register addresses data memory or program memory. The I

value is either premodified (M, I order) or postmodified (I, M order) by

the specified M register. If it is postmodified, the I register is updated with

the modified value. If a compute operation is specified, it is performed in

parallel with the data access. If a condition is specified, it affects entire

instruction. Note that the UREG may not be from the same DAG (i.e.

DAG1 or DAG2) as Ia/Mb or Ic/Md. For more information on register

restrictions, see Chapter 4, Data Addressing, in ADSP-21065L SHARC

DSP User’s Manual.

Examples

R6=R3-R11, DM(I0,M1)=ASTAT;

IF NOT SV F8=CLIP F2 BY F14, PX=PM(I12,M12);

ADSP-21065L SHARC DSP Technical Reference A-33

Page 54

Group I Instructions (Compute & Move)

Type 3 Opcode

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

010 U I M COND G D UREG

222120191817161514131211109876543210

COMPUTE

Bits Description

COND Specifies the test condition. If no condition is

specified, COND is TRUE, and the instruction is

executed.

D Selects the access type (read or write).

G Selects data memory or program memory.

UREG Specifies the universal register.

I Specifies the I register.

M Specifies the M register.

U Selects either premodify without update or post-

modify with update.

COMPUTE Defines a compute operation to be performed in

parallel with the data access; this is a no-operation if no compute operation is specified in the

instruction.

A-34 ADSP-21065L SHARC DSP Technical Reference

Page 55

Instruction Set Reference

Compute/dregÙDM|PM, immediate modify (Type

4)

PC-relative transfer between data or program memory and Register File,

optional condition, optional compute operation.

Syntax

IF COND compute , DM(Ia, <data6>) = dreg ;

, PM(Ic, <data6>)

, DM(<data6>, Ia) = dreg ;

, PM(<data6>, Ic)

, dreg = DM(Ia, <data6>) ;

PM(Ic, <data6>) ;

, dreg = DM(<data6>, Ia) ;

PM(<data6>, Ic) ;

Function

Access between data memory or program memory and the Register File.

The specified I register addresses data memory or program memory. The I

value is either premodified (data order, I) or postmodified (I, data order)

by the specified immediate data. If it is postmodified, the I register is

updated with the modified value. If a compute operation is specified, it is

performed in parallel with the data access. If a condition is specified, it

affects entire instruction. For more information on register restrictions,

see Chapter 4, Data Addressing, in ADSP-21065L SHARC DSP User’s

Manual.

Examples

IF FLAG0_IN F1=F5*F12, F11=PM(I10,40);

R12=R3 AND R1, DM(6,I1)=R6;

ADSP-21065L SHARC DSP Technical Reference A-35

Page 56

Group I Instructions (Compute & Move)

Type 4 Opcode

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

011 0 I G D U COND DATA DREG

222120191817161514131211109876543210

COMPUTE

Bits Description

COND Specifies the test condition. If no condition is

specified, COND is TRUE, and the instruction is

executed.

D Selects the access type (read or write).

G Selects data memory or program memory.

DREG Specifies the Register File location.

I Specifies the I register.

DATA Specifies a 6-bit, twos-complement modify value.

U Selects either premodify without update or post-

modify with update.

COMPUTE Defines a compute operation to be performed in

parallel with the data access; this is a no-operation if no compute operation is specified in the

instruction.

A-36 ADSP-21065L SHARC DSP Technical Reference

Page 57

Instruction Set Reference

Compute/uregÙureg (Type 5)

Transfer between two universal registers, optional condition, optional

compute operation.

Syntax

IF COND compute, ureg1 = ureg2 ;

Function

Transfer from one universal register to another. If a compute operation is

specified, it is performed in parallel with the data access. If a condition is

specified, it affects entire instruction.

Examples

IF TF MRF=R2*R6(SSFR), M4=R0;

LCNTR=L7;

Type 5 Opcode

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

011 1 SRC UREG COND DEST UREG

222120191817161514131211109876543210

COMPUTE

Bits Description

COND Specifies the test condition. If no condition is

specified, COND is TRUE, and the instruction is

executed.

ADSP-21065L SHARC DSP Technical Reference A-37

Page 58

Group I Instructions (Compute & Move)

Bits Description

SRC UREG Identifies the universal register source.

DEST UREG Identifies the universal register destination.

COMPUTE Defines a compute operation to be performed in

parallel with the data transfer; this is a

no-operation if no compute operation is specified

in the instruction.

A-38 ADSP-21065L SHARC DSP Technical Reference

Page 59

Instruction Set Reference

Immediate Shift/dregÙDM|PM (Type 6)

Immediate shift operation, optional condition, optional transfer between

data or program memory and Register File.

Syntax

IF COND shiftimm , DM(Ia, Mb) = dreg ;

, PM(Ic, Md)

, dreg = DM(Ia, Mb) ;

PM(Ic, Md) ;

Function

An immediate shift operation is a Shifter operation that takes immediate

data as its y-operand. The immediate data is one 8-bit value or two 6-bit

values, depending on the operation. The x-operand and the result are Register File locations.

If an access to data or program memory from the Register File is specified,

it is performed in parallel with the Shifter operation. The I register

addresses data or program memory. The I value is postmodified by the

specified M register and updated with the modified value. If a condition is

specified, it affects entire instruction.

For more information on register restrictions, see Chapter 4, Data

Addressing, in ADSP-21065L SHARC DSP User’s Manual.

Examples

IF GT R2=R6 LSHIFT BY 30, DM(I4,M4)=R0;

IF NOT SZ R3=FEXT R1 BY 8:4;

ADSP-21065L SHARC DSP Technical Reference A-39

Page 60

Group I Instructions (Compute & Move)

Type 6 Opcode (with data access)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

100 0 I M COND G D DATAEX DREG

222120191817161514131211109876543210

0 SHIFTOP DATA RN RX

Type 6 Opcode (without data access)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

000 00010 COND DATAEX

222120191817161514131211109876543210

0 SHIFTOP DATA RN RX

Bits Description

COND Specifies the test condition. If no condition is

specified, COND is TRUE, and the instruction is

executed.

SHIFTOP Specifies the Shifter operation.

DATA Specifies an 8-bit immediate shift value. For

Shifter operations requiring two 6-bit values (a

shift value and a length value), the DATAEX field

adds 4 MSBs to the DATA field, creating a 12-bit

immediate value. The six LSBs are the shift value,

and the six MSBs are the length value.

A-40 ADSP-21065L SHARC DSP Technical Reference

Page 61

Instruction Set Reference

Bits Description

D Selects the access type (read or write) if a mem-

ory access is specified.

G Selects data memory or program memory.

DREG Specifies the Register File location.

I Specifies the I register, which is postmodified

and updated by the M register.

M Identifies the M register for postmodify.

ADSP-21065L SHARC DSP Technical Reference A-41

Page 62

Group I Instructions (Compute & Move)

Compute/modify (Type 7)

Index register modify, optional condition, optional compute operation.

Syntax

IF COND compute , MODIFY (Ia, Mb) ;

(Ic, Md) ;

Function

Update of the specified I register by the specified M register. If a compute

operation is specified, it is performed in parallel with the data access. If a

condition is specified, it affects entire instruction. For more information

on register restrictions, see Chapter 4, Data Addressing, in ADSP-21065L

SHARC DSP User’s Manual.

Examples

IF NOT FLAG2_IN R4=R6*R12(SUF), MODIFY(I10,M8);

IF NOT LCE MODIFY(I3,M1);

Type 7 Opcode

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

000 00100 G COND I M

222120191817161514131211109876543210

COMPUTE

A-42 ADSP-21065L SHARC DSP Technical Reference

Page 63

Instruction Set Reference

Bits Description

COND Specifies the test condition. If no condition is

specified, COND is TRUE, and the instruction is

executed.

G Selects DAG1 or DAG2.

I Specifies the I register.

M Specifies the M register.

COMPUTE Defines a compute operation to be performed in

parallel with the data access; this is a no-operation if no compute operation is specified in the

instruction.

ADSP-21065L SHARC DSP Technical Reference A-43

Page 64

Group II Instructions (Program Flow Control)

Group II Instructions (Program Flow

Control)

• “Direct Jump|Call (Type 8)” on page A-45.

Direct (or PC-relative) jump/call, optional condition.

• “Indirect Jump|Call / Compute (Type 9)” on page A-48.

Indirect (or PC-relative) jump/call, optional condition, optional

compute operation.

• “Indirect Jump or Compute/dregÙDM (Type 10)” on page A-52.

Indirect (or PC-relative) jump or optional compute operation with

transfer between data memory and Register File.

• “Return From Subroutine|Interrupt/Compute (Type 11)” on page

A-55.

Return from subroutine or interrupt, optional condition, optional

compute operation.

• “Do Until Counter Expired (Type 12)” on page A-58.

Load loop counter, do loop until loop counter expired.

• “Do Until (Type 13)” on page A-60.

Do until termination.

*

A-44 ADSP-21065L SHARC DSP Technical Reference

For all program flow control instructions, except type

10 instructions, IF COND is optional.

Page 65

Instruction Set Reference

Direct Jump|Call (Type 8)

Direct (or PC-relative) jump/call, optional condition.

Syntax

IF COND

JUMP

IF COND

CALL

<addr24> (DB) ;

(PC, <reladdr24>) (LA)

(CI)

(DB, LA)

(DB, CI)

<addr24> (DB) ;

(PC, <reladdr24>)

Function

A jump or call to the specified address or PC-relative address. The PC-relative address is a 24-bit, twos-complement value. If the delayed branch

(DB) modifier is specified, the branch is delayed; otherwise, it is nondelayed. If the loop abort (LA) modifier is specified for a jump, the loop

stacks and PC stack are popped when the jump is executed. Use the (LA)

modifier if the jump transfers program execution outside of a loop. If

there is no loop or the jump address is within the loop, do not use the

(LA) modifier.

The clear interrupt (CI) modifier enables reuse of an interrupt while it is

being serviced. Normally, the processor ignores and does not latch an

interrupt that reoccurs while its service routine is already executing.

Locate the JUMP (CI) instruction within the interrupt service routine.

JUMP (CI) clears the status of the current interrupt without leaving the

interrupt service routine and reduces the interrupt routine to a normal

subroutine. This allows the interrupt to occur again, as a result of a different event or task in the processor system. For details on interrupts, see

ADSP-21065L SHARC DSP Technical Reference A-45

Page 66

Group II Instructions (Program Flow Control)

Chapter 3, Program Sequencing, in ADSP-21065L SHARC DSP User’s

Manual.

The JUMP (CI) instruction reduces an interrupt service routine to a normal subroutine by clearing the appropriate bit in the interrupt latch

register (IRPTL) and interrupt mask pointer (IMASKP). The processor

then allows the interrupt to occur again.

When returning from a subroutine that a JUMP (CI) instruction has

reduced from an interrupt service routine, your application must use the

(LR) modifier of the RTS instruction if the interrupt occurred during the

last two instructions of a loop. For related information, see “Return From

Subroutine|Interrupt/Compute (Type 11)” on page A-55.

Examples

IF AV JUMP(PC,0x00A4)(LA);

CALL init (DB); {init is a program label}

JUMP (PC,2) (DB,CI); {clear current int. for reuse}

Type 8 Opcode (with direct branch)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24

000 00110 B A COND J

23 222120191817161514131211109876543210

ADDR

A-46 ADSP-21065L SHARC DSP Technical Reference

C

I

Page 67

Instruction Set Reference

Type 8 Opcode (with PC-relative branch)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24

000 00111 B A COND J

23 222120191817161514131211109876543210

RELADDR

Bits Description

COND Specifies the test condition. If no condition is

specified, COND is TRUE, and the instruction is

executed.

B Selects the branch type, jump or call. For calls,

A and CI are ignored.

J Determines whether the branch is delayed or nonde-

layed.

ADDR Specifies a 24-bit program memory address.

A Activates loop abort.

C

I

CI Activates clear interrupt.

RELADDR Holds a 24-bit, twos-complement value that is

added to the current PC value to generate the

branch address.

ADSP-21065L SHARC DSP Technical Reference A-47

Page 68

Group II Instructions (Program Flow Control)

Indirect Jump|Call / Compute (Type 9)

Indirect (or PC-relative) jump/call, optional condition, optional compute

operation.

Syntax

IF COND

JUMP

IF COND

CALL

(Md, Ic) (DB) , compute ;

(PC, <reladdr6>) (LA) , ELSE compute

(CI)

(DB, LA)

(DB, CI)

(Md, Ic) (DB) , compute ;

(PC, <reladdr6>) , ELSE compute

Function

A jump or call to the specified PC-relative address or premodified I register value. The PC-relative address is a 6-bit, twos-complement value. If an

I register is specified, it is modified by the specified M register to generate

the branch address. The I register is not affected by the modify operation.

The jump or call is executed if a condition is specified and is true. If a

compute operation is specified without the ELSE, it is performed in parallel with the jump or call. If a compute operation is specified with the

ELSE, it is performed only if the condition specified is false. Note that a

condition must be specified if an ELSE compute clause is specified.

If the delayed branch (DB) modifier is specified, the jump or call is

delayed; otherwise, it is nondelayed. If the loop abort (LA) modifier is

specified for a jump, the loop stacks and PC stack are popped when the

jump is executed. You should use the (LA) modifier if the jump will transfer program execution outside of a loop. If there is no loop, or if the jump

address is within the loop, you should not use the (LA) modifier.

A-48 ADSP-21065L SHARC DSP Technical Reference

Page 69

Instruction Set Reference

The clear interrupt (CI) modifier allows the reuse of an interrupt while it

is being serviced. Normally the processor ignores and does not latch an

interrupt that reoccurs while its service routine is already executing.

Locate the JUMP (CI) instruction within the interrupt service routine.

JUMP (CI) clears the status of the current interrupt without leaving the

interrupt service routine and reduces the interrupt routine to a normal

subroutine. This allows the interrupt to occur again, as a result of a different event. For more information on interrupts, see Chapter 3, Program

Sequencing, in ADSP-21065L SHARC DSP User’s Manual.

The JUMP (CI) instruction reduces an interrupt service routine to a normal subroutine by clearing the appropriate bit in the interrupt latch

register (IRPTL) and interrupt mask pointer (IMASKP). The processor

then permits the interrupt to occur again.

When returning from a subroutine that a JUMP (CI) instruction has

reduced from an interrupt service routine, your application must use the

(LR) modifier of the RTS instruction if the interrupt occurred during the

last two instructions of a loop. (See “Return From Subroutine|Inter-

rupt/Compute (Type 11)” on page A-55).

For more information on indirect branches, see Chapter 4, Data Addressing, in ADSP-21065L SHARC DSP User’s Manual.

Examples

JUMP(M8,I12), R6=R6-1;

IF EQ CALL(PC,17)(DB) , ELSE R6=R6-1;

ADSP-21065L SHARC DSP Technical Reference A-49

Page 70

Group II Instructions (Program Flow Control)

Type 9 Opcode (with indirect branch)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

000 01000 B A COND PMI PMM J E

222120191817161514131211109876543210

C

I

COMPUTE

Type 9 Opcode (with PC-relative branch)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

000 01001 B A COND RELADDR J E

222120191817161514131211109876543210

COMPUTE

Bits Description

C

I

COND Specifies the test condition. If no condition is

specified, COND is true, and the instruction is

executed.

E Specifies whether or not an ELSE clause is used.

B Selects the branch type, jump or call. For calls,

A and CI are ignored.

J Determines whether the branch is delayed or nonde-

layed.

A-50 ADSP-21065L SHARC DSP Technical Reference

Page 71

Instruction Set Reference

Bits Description

A Activates loop abort.

CI Activates clear interrupt.

COMPUTE Defines a compute operation to be performed in

parallel with the data access; this is a NOP if no

compute operation is specified in the instruction.

RELADDR Holds a 6-bit, twos-complement value that is added

to the current PC value to generate the branch

address.

PMI Specifies the I register for indirect branches.

The I register is premodified but not updated by

the M register.

PMM Specifies the M register for premodifies.

ADSP-21065L SHARC DSP Technical Reference A-51

Page 72

Group II Instructions (Program Flow Control)

Indirect Jump or Compute/dregÙDM (Type 10)

Indirect (or PC-relative) jump or optional compute operation with transfer between data memory and Register File.

,

Syntax

IF COND Jump (Md, Ic) , Else compute, DM(Ia, Mb) = dreg ;

Function

Conditional jump to the specified PC-relative address or premodified I

register value, or optional compute operation in parallel with a transfer

between data memory and the Register File. In this instruction, the IF

condition and ELSE keyword are not optional and must be used. If the

specified condition is true, the jump is executed. If the specified condition

is false, the compute operation and data memory transfer are performed in

parallel. Only the compute operation is optional in this instruction.

The PC-relative address for the jump is a 6-bit, twos-complement value. If

an I register is specified (Ic), it is modified by the specified M register

(Md) to generate the branch address. The I register is not affected by the

modify operation. Note that the delay branch (DB), loop abort (LA), and

clear interrupt (CI) modifiers are not available for this jump instruction.

Type 10 instructions require IF COND.

(PC, <reladdr6> compute, dreg = DM(Ia, Mb) ;

For the data memory access, the I register (Ia) provides the address. The I

register value is postmodified by the specified M register and is updated

with the modified value. Premodify addressing is not available for this

data memory access.

A-52 ADSP-21065L SHARC DSP Technical Reference

Page 73

Instruction Set Reference

For more information on indirect branches, see Chapter 4, Data Addressing, in ADSP-21065L SHARC DSP User’s Manual.

Examples

IF TF JUMP(M8, I8),

ELSE R6=DM(I6, M1);

IF NE JUMP(PC, 0x20),

ELSE F12=FLOAT R10 BY R3, R6=DM(I5, M0);

Type 10 Opcode (with indirect jump)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

110 D DMI DMM COND PMI PMM DREG

222120191817161514131211109876543210

COMPUTE

Type 10 Opcode (with PC-relative jump)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

111 D DMI DMM COND RELADDR DREG

222120191817161514131211109876543210

COMPUTE

ADSP-21065L SHARC DSP Technical Reference A-53

Page 74

Group II Instructions (Program Flow Control)

Bits Description

COND Specifies the condition to test.

PMI Specifies the I register for indirect branches.

The I register is premodified, but not updated by

the M register.

PMM Specifies the M register for premodifies.

D Selects the data memory access type (read or

write).

DREG Specifies the Register File location.

DMI Specifies the I register which is postmodified and

updated by the M register.

DMM Identifies the M register for postmodifies.

COMPUTE Defines a compute operation to be performed in

parallel with the data access; this is a NOP if no

compute operation is specified in the instruction.

RELADDR Holds a 6-bit, twos-complement value that is added

to the current PC value to generate the branch

address.

A-54 ADSP-21065L SHARC DSP Technical Reference

Page 75

Instruction Set Reference

Return From Subroutine|Interrupt/Compute

(Type 11)

Indirect (or PC-relative) jump or optional compute operation with transfer between data memory and Register File.

Syntax

IF COND RTS (DB) , compute ;

(LR) , ELSE compute

(DB, LR)

IF COND RTI (DB) , compute ;

, ELSE compute

Function

A return from a subroutine (RTS) or return from an interrupt service routine (RTI). If the delayed branch (DB) modifier is specified, the return is

delayed; otherwise, it is nondelayed.

A return causes the processor to branch to the address stored at the top of

the PC stack. The difference between RTS and RTI is that the RTI

instruction not only pops the return address off the PC stack, but also 1)

pops status stack if the ASTAT and MODE1 status registers have been

pushed (if the interrupt was IRQ

, the timer interrupt, or the VIRPT

2-0

vector interrupt), and 2) clears the appropriate bit in the interrupt latch

register (IRPTL) and the interrupt mask pointer (IMASKP).

The return is executed if a condition is specified and is true. If a compute

operation is specified without the ELSE, it is performed in parallel with

the return. If a compute operation is specified with the ELSE, it is performed only if the condition is false. Note that a condition must be

specified if an ELSE compute clause is specified.

If a nondelayed call is used as one of the last three instructions of a loop,

the loop reentry (LR) modifier must be used with the RTS instruction

ADSP-21065L SHARC DSP Technical Reference A-55

Page 76

Group II Instructions (Program Flow Control)

that returns from the subroutine. The (LR) modifier assures proper

reentry into the loop. In counter-based loops, for example, the

termination condition is checked by decrementing the current loop

counter (CURLCNTR) during execution of the instruction two locations

before the end of the loop. The RTS (LR) instruction prevents the loop

counter from being decremented again (i.e. twice for the same loop

iteration).

The (LR) modifier of RTS must also be used when returning from a subroutine which has been reduced from an interrupt service routine with a

JUMP (CI) instruction (in case the interrupt occurred during the last two

instructions of a loop). For a description of JUMP (CI), refer to “Direct

Jump|Call (Type 8)” on page A-45 or “Indirect Jump|Call / Compute

(Type 9)” on page A-48.

Examples

RTI, R6=R5 XOR R1;

IF NOT GT RTS(DB);

IF SZ RTS, ELSE R0=LSHIFT R1 BY R15;

Type 11 Opcode (return from subroutine)

47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23

000 01010 COND J E

222120191817161514131211109876543210

COMPUTE

L

R