Micropower, Low Noise Precision

Voltage References with

Shutdown

FEATURES

Compact TSOT-23-5 packages

Low temperature coefficient

B grade: 9 ppm/°C

A grade: 25 ppm/°C

Initial accuracy

B grade: +

A grade: +

Ultralow output noise: 5 µV p-p (0.1 Hz to 10 Hz)

Low dropout: 300 mV

Low supply current

3 µA maximum in shutdown

120 µA maximum in operation

No external capacitor required

Output current: 5 mA

Wide temperature range

−40°C to + 125°C

APPLICATIONS

Battery-powered instrumentations

Portable medical instrumentations

Data acquisition systems

Industrial process controls

Automotive

GENERAL DESCRIPTION

4 mV maximum

6 mV maximum

ADR390/ADR391/ADR392/ADR395

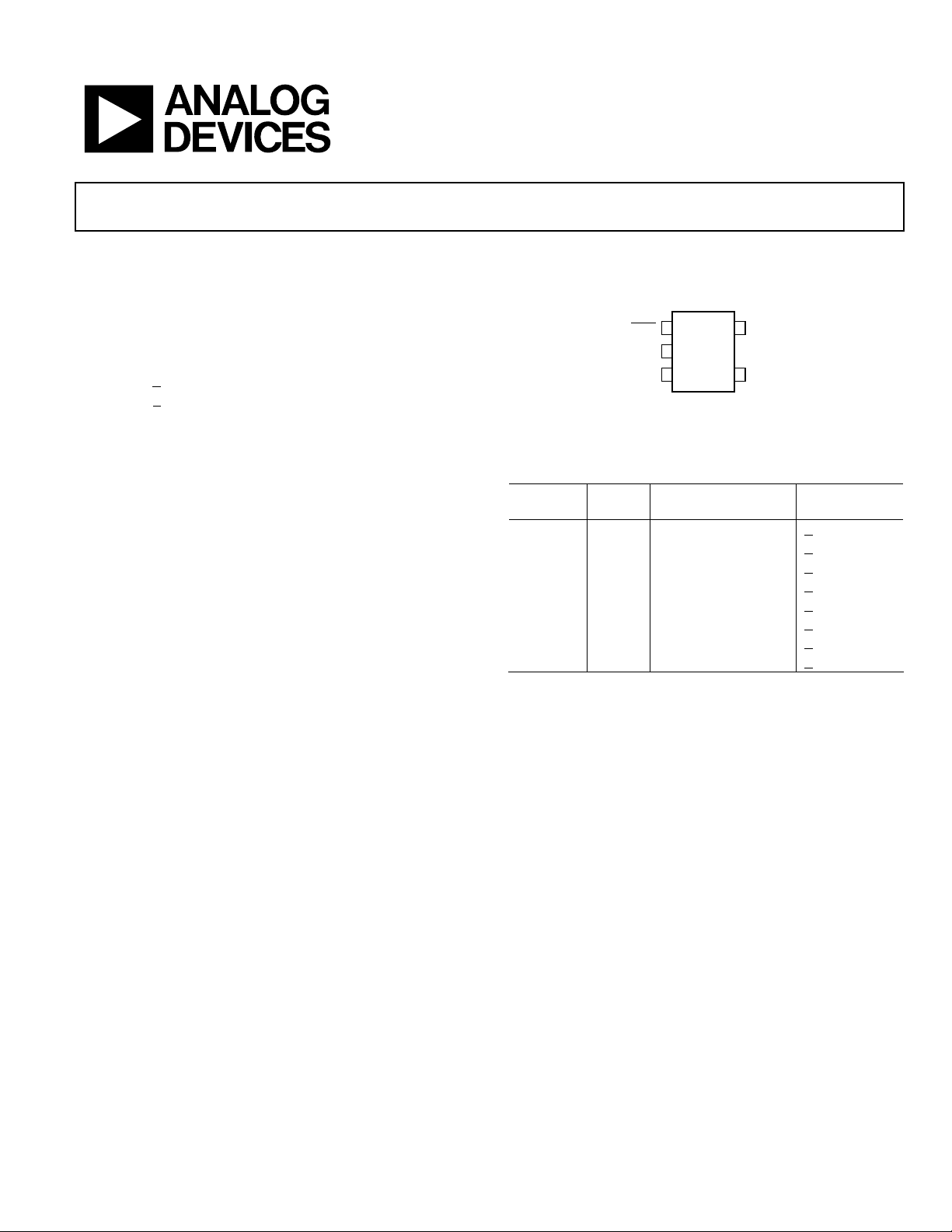

FUNCTIONAL BLOCK DIAGRAM

1

SHDN

V

OUT (SENSE)

Figure 1. 5-Lead TSOT (UJ Suffix)

V

IN

ADR390/

ADR391/

2

ADR392/

ADR395

3

(Not to Scale)

Table 1.

Temperature

Model V

OUT

(V)

Coefficient (ppm/°C) Accuracy (mV)

ADR390B 2.048 9 +4

ADR390A 2.048 25 +6

ADR391B 2.5 9 +4

ADR391A 2.5 25 +6

ADR392B 4.096 9 +5

ADR392A 4.096 25 +6

ADR395B 5.0 9 +5

ADR395A 5.0 25 +6

Contact Analog Devices, Inc. for other voltage options.

5

GND

4

V

OUT (FORCE)

00419-D-001

The ADR390, ADR391, ADR392, and ADR395 are precision

2.048 V, 2.5 V, 4.096 V, and 5 V band gap voltage references

that feature low power and high precision in a tiny footprint.

Using ADI’s patented temperature drift curvature correction

techniques, the ADR39x references achieve a low 9 ppm/°C of

temperature drift in the TSOT package.

The ADR39x family of micropower, low dropout voltage

references provides a stable output voltage from a minimum

supply of 300 mV above the output. Their advanced design

eliminates the need for external capacitors, which further

reduces board space and system cost. The combination of

low power operation, small size, and ease of use makes the

ADR39x precision voltage references ideally suited for batteryoperated applications.

Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

ADR390/ADR391/ADR392/ADR395

TABLE OF CONTENTS

ADR390—Specifications ................................................................. 3

REVISION HISTORY

ADR391—Specifications ................................................................. 4

ADR392—Specifications ................................................................. 5

ADR395—Specifications ................................................................. 6

Absolute Maximum Ratings............................................................ 7

Thermal Resistance ...................................................................... 7

ESD Caution.................................................................................. 7

Terminology ...................................................................................... 8

Typical Performance Characteristics ............................................. 9

Theory of Operation ...................................................................... 16

Applications..................................................................................... 17

Basic Voltage Reference Connection ....................................... 17

Outline Dimensions....................................................................... 19

Ordering Guide........................................................................... 19

4/04—Data Sheet Changed from Rev. D to Rev. E

Changes to ADR390—Specifications............................................ 3

Changes to ADR391—Specifications............................................ 4

Changes to ADR392—Specifications............................................ 5

Changes to ADR395—Specifications............................................ 6

4/04—Data Sheet Changed from Rev. C to Rev. D

Updated Format.................................................................Universal

Changes to Title............................................................................... 1

Changes to Features ........................................................................ 1

Changes to Applications................................................................. 1

Changes to General Description ...................................................1

Changes to Table 1........................................................................... 1

Changes to ADR390—Specifications............................................ 3

Changes to ADR391—Specifications............................................ 4

Changes to ADR392—Specifications............................................ 5

Changes to ADR395—Specifications............................................ 6

Changes to Absolute Maximum Ratings ...................................... 7

Changes to Thermal Resistance..................................................... 7

Moved ESD Caution .......................................................................7

Changes to Figure 3, Figure 4, Figure 7, and Figure 8................. 9

Changes to Figure 11, Figure 12, Figure 13, and Figure 14 ......10

Changes to Figure 15, Figure 16, Figure 19, and Figure 20 ......11

Changes to Figure 23 and Figure 24............................................ 12

Changes to Figure 27.....................................................................13

Changes to Ordering Guide......................................................... 19

Updated Outline Dimensions...................................................... 19

10/02—Data Sheet Changed from Rev. B to Rev. C

Add parts ADR392 and ADR395 ....................................Universal

Changes to Features ........................................................................ 1

Changes to General Description ...................................................1

Additions to Table I......................................................................... 1

Changes to Specifications............................................................... 2

Changes to Ordering Guide........................................................... 4

Changes to Absolute Maximum Ratings ...................................... 4

New TPCs 3, 4, 7, 8, 11, 12, 15, 16, 19, and 20............................... 6

New Figures 4 and 5...................................................................... 13

Deleted A Negative Precision Reference

without Precision Resistors Section............................................ 13

Edits to General-Purpose Current Source Section ................... 13

Updated Outline Dimensions...................................................... 15

5/02—Data Sheet Changed from Rev. A to Rev. B

Edits to Layout...................................................................Universal

Changes to Figure 6....................................................................... 13

Rev. E | Page 2 of 20

ADR390/ADR391/ADR392/ADR395

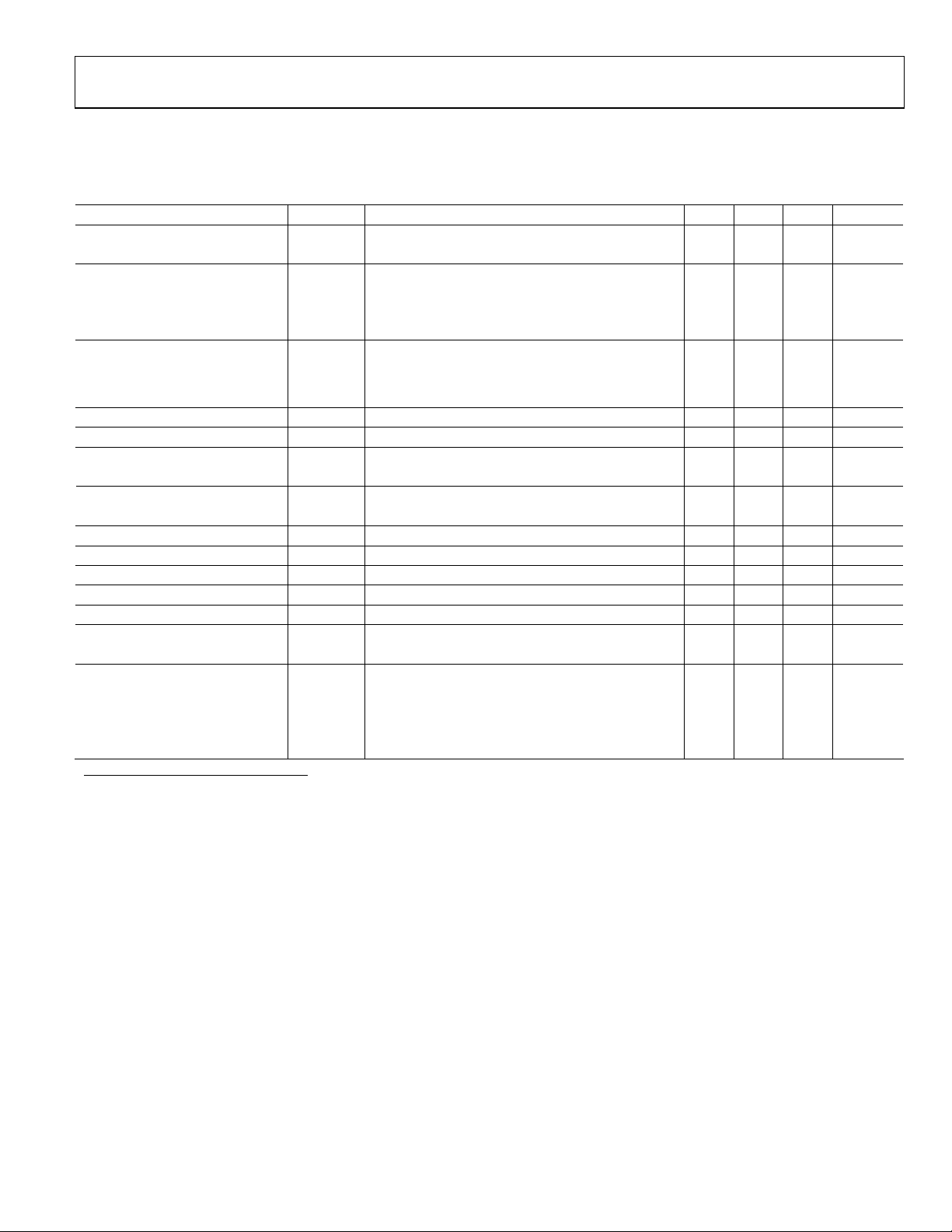

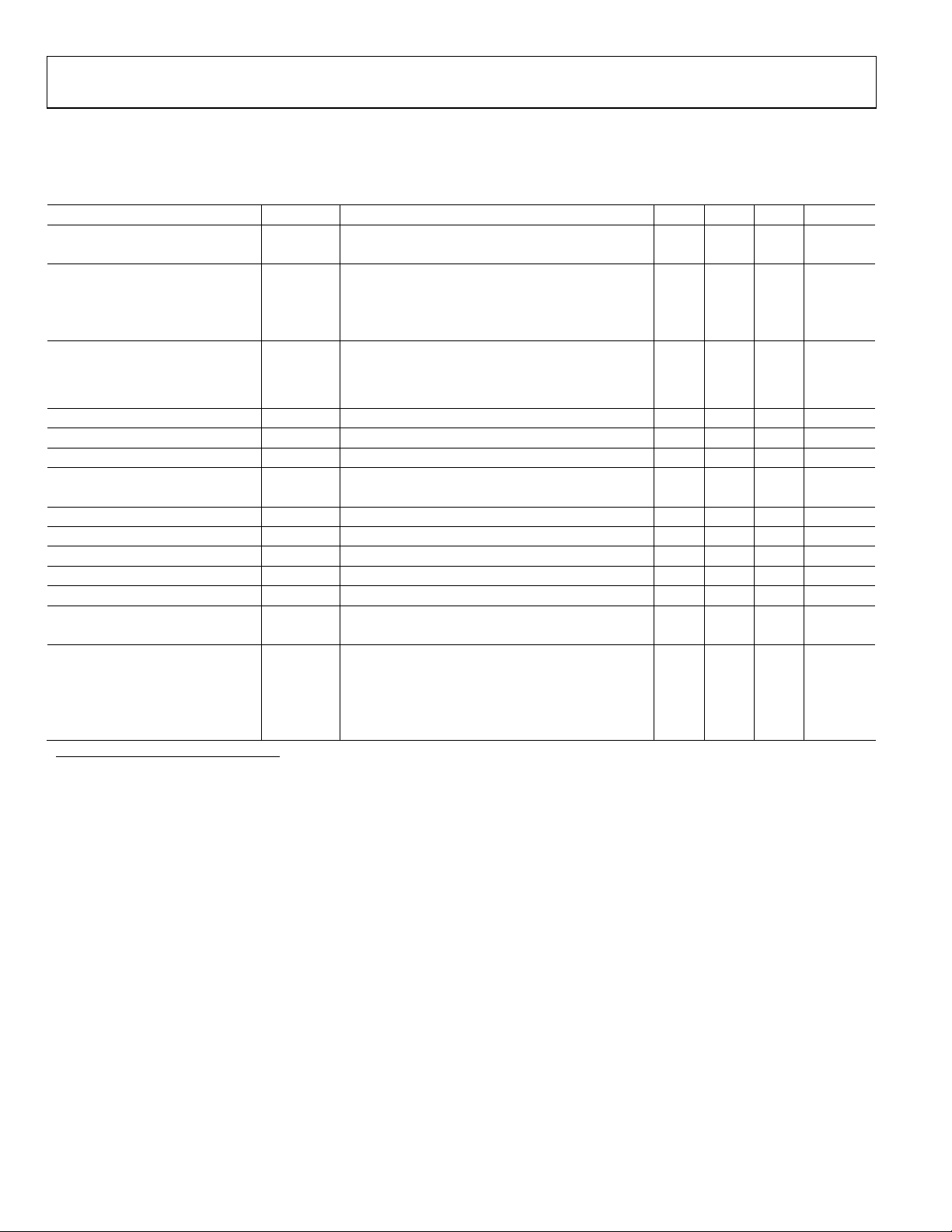

ADR390—SPECIFICATIONS

Electrical Characteristics, VIN = 2.5 V to 15 V, TA = 25°C, unless otherwise noted.

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE V

V

INITIAL ACCURACY V

V

V

V

O

B Grade 2.044 2.048 2.052 V

O

OERR

A Grade 0.29 %

OERR

B Grade 4 mV

OERR

B Grade 0.19 %

OERR

A Grade 2.042 2.048 2.054 V

A Grade 6 mV

A Grade, −40°C < TA < +125°C 25 ppm/°C TEMPERATURE COEFFICIENT TCVO

B Grade, −40°C < T

< +125°C 9 ppm/°C

A

SUPPLY VOLTAGE HEADROOM VIN − VO 300 mV

LINE REGULATION ∆VO/∆VIN VIN = 2.5 V to 15 V, −40°C < TA < +125°C 10 25 ppm/V

I

= 0 mA to 5 mA, −40°C < TA < +85°C, VIN = 3 V 60 ppm/mA LOAD REGULATION ∆VO/∆I

LOAD

LOAD

I

= 0 mA to 5 mA, −40°C < TA < +125°C, VIN = 3 V 140 ppm/mA

LOAD

No Load 120 µA QUIESCENT CURRENT IIN

< +125°C 140 µA

A

VOLTAGE NOISE e

−40°C < T

0.1 Hz to 10 Hz 5 µV p-p

N p-p

TURN-ON SETTLING TIME tR 20 µs

LONG-TERM STABILITY1 ∆VO 1, 000 Hours 50 ppm

OUTPUT VOLTAGE HYSTERESIS ∆V

100 ppm

O_HYS

RIPPLE REJECTION RATIO RRR fIN = 60 kHz 80 dB

VIN = 5 V 25 mA SHORT CIRCUIT TO GND ISC

V

= 15 V 30 mA

IN

SHUTDOWN PIN

Shutdown Supply Current I

Shutdown Logic Input Current I

Shutdown Logic Low V

Shutdown Logic High V

3 µA

SHDN

500 nA

LOGIC

0.8 V

INL

2.4 V

INH

1

The long-term stability specification is noncumulative. The drift subsequent 1,000 hour periods is significantly lower than in the first 1,000 hour period.

Rev. E | Page 3 of 20

ADR390/ADR391/ADR392/ADR395

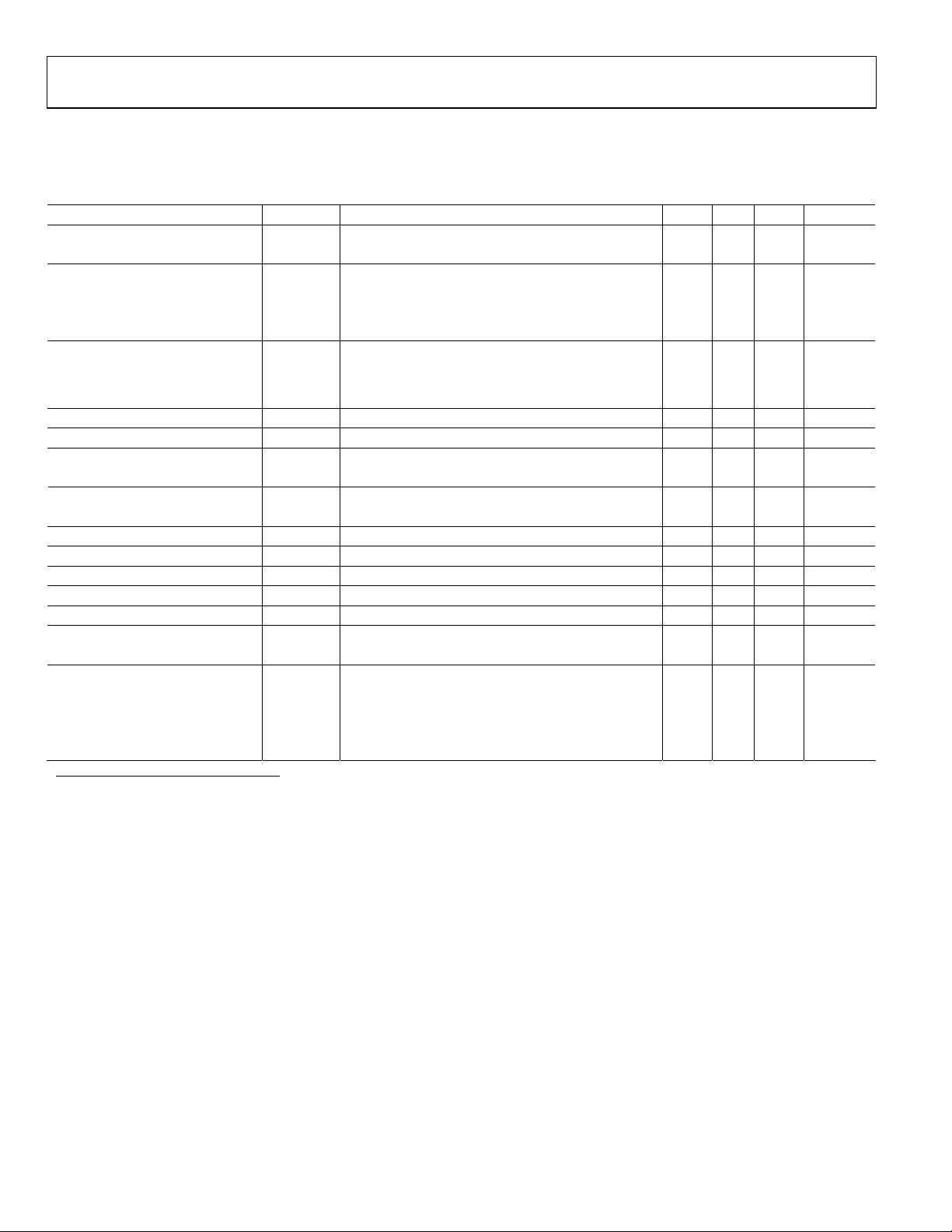

ADR391—SPECIFICATIONS

Electrical characteristics, VIN = 2.8 V to 15 V, TA = 25°C, unless otherwise noted.

Table 3.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE VO A Grade 2.494 2.5 2.506 V

V

V

V

B Grade 2.496 2.5 2.504 V

O

V

A Grade 6 mV INITIAL ACCURACY

OERR

A Grade 0.24 %

V

OERR

B Grade 4 mV

OERR

B Grade 0.16 %

OERR

A Grade, −40°C < TA < +125°C 25 ppm/°C TEMPERATURE COEFFICIENT TCVO

B Grade, −40°C < T

< +125°C 9 ppm/°C

A

SUPPLY VOLTAGE HEADROOM VIN − VO 300 mV

LINE REGULATION ∆VO/∆VIN VIN = 2.8 V to 15 V, −40°C < TA < +125°C 10 25 ppm/V

I

= 0 mA to 5 mA, −40°C < TA < +85°C, VIN = 3 V 60 ppm/mA LOAD REGULATION ∆VO/∆I

LOAD

LOAD

= 0 mA to 5 mA, −40°C < TA < +125°C, VIN = 3 V 140 ppm/mA

I

LOAD

No Load 120 µA QUIESCENT CURRENT IIN

VOLTAGE NOISE e

−40°C < T

0.1 Hz to 10 Hz 5 µV p-p

N p-p

< +125°C 140 µA

A

TURN-ON SETTLING TIME tR 20 µs

LONG-TERM STABILITY1 ∆VO 1, 000 Hours 50 ppm

OUTPUT VOLTAGE HYSTERESIS ∆V

100 ppm

O_HYS

RIPPLE REJECTION RATIO RRR fIN = 60 kHz 80 dB

VIN = 5 V 25 mA SHORT CIRCUIT TO GND ISC

= 15 V 30 mA

V

IN

SHUTDOWN PIN

Shutdown Supply Current I

Shutdown Logic Input Current I

Shutdown Logic Low V

Shutdown Logic High V

3 µA

SHDN

500 nA

LOGIC

0.8 V

INL

2.4 V

INH

1

The long-term stability specification is noncumulative. The drift subsequent 1,000 hour periods is significantly lower than in the first 1,000 hour period.

Rev. E | Page 4 of 20

ADR390/ADR391/ADR392/ADR395

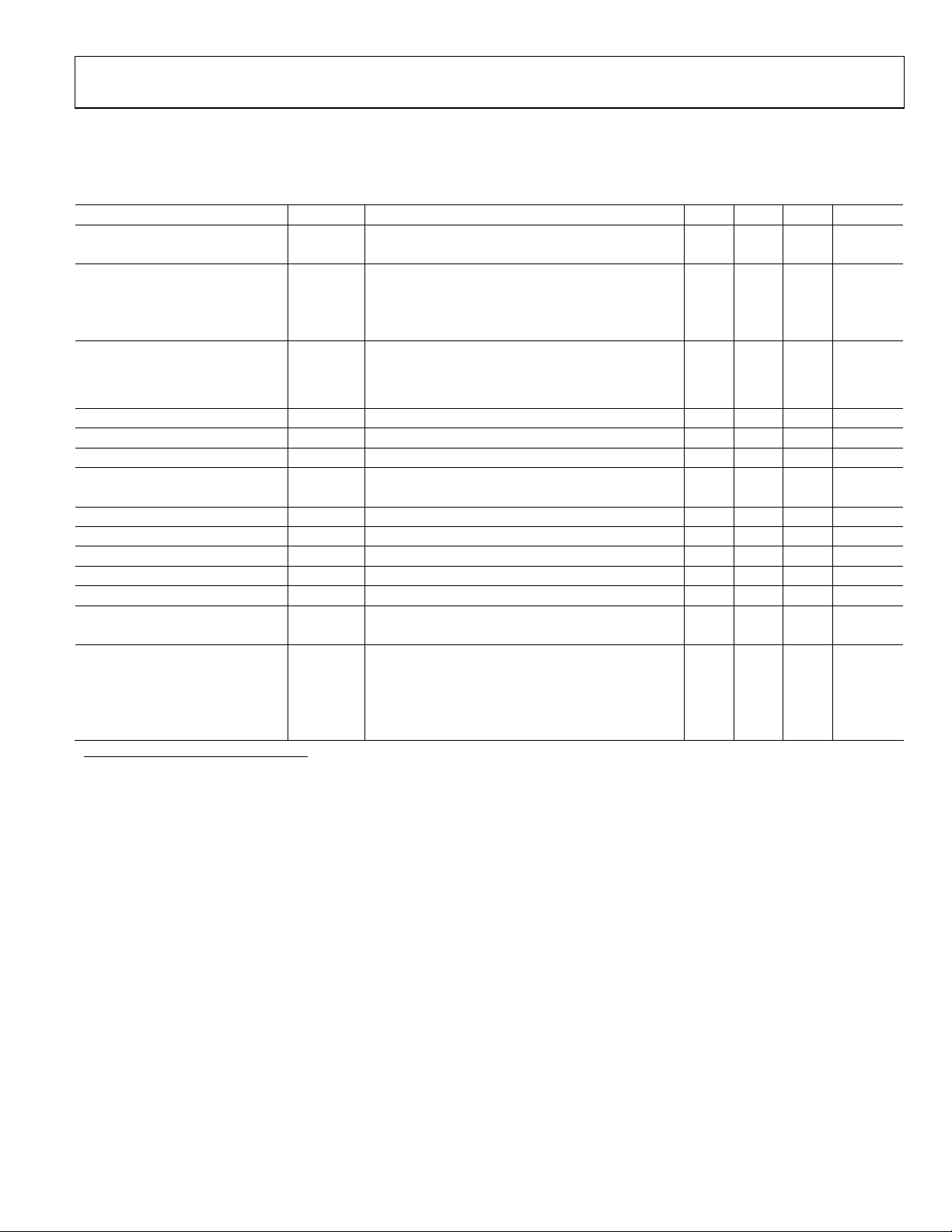

ADR392—SPECIFICATIONS

Electrical characteristics, VIN = 4.3 V to 15 V, TA = 25°C, unless otherwise noted.

Table 4.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE VO A Grade 4.090 4.096 4.102 V

V

V

V

B Grade 4.091 4.096 4.101 V

O

V

A Grade 6 mV INITIAL ACCURACY

OERR

A Grade 0.15 %

V

OERR

B Grade 5 mV

OERR

B Grade 0.12 %

OERR

A Grade, −40°C < TA < +125°C 25 ppm/°C TEMPERATURE COEFFICIENT TCVO

B Grade, −40°C < T

< +125°C 9 ppm/°C

A

SUPPLY VOLTAGE HEADROOM VIN − VO 300 mV

LINE REGULATION ∆VO/∆VIN VIN = 4.3 V to 15 V, −40°C < TA < +125°C 10 25 ppm/V

LOAD REGULATION ∆VO/∆I

LOAD

I

= 0 mA to 5 mA, −40°C < TA < +125°C, VIN = 5 V 140 ppm/mA

LOAD

No Load 120 µA QUIESCENT CURRENT IIN

< +125°C 140 µA

A

VOLTAGE NOISE e

−40°C < T

0.1 Hz to 10 Hz 7 µV p-p

N p-p

TURN-ON SETTLING TIME tR 20 µs

LONG-TERM STABILITY1 ∆VO 1, 000 Hours 50 ppm

OUTPUT VOLTAGE HYSTERESIS ∆V

100 ppm

O_HYS

RIPPLE REJECTION RATIO RRR fIN = 60 kHz 80 dB

VIN = 5 V 25 mA SHORT CIRCUIT TO GND ISC

V

= 15 V 30 mA

IN

SHUTDOWN PIN

Shutdown Supply Current I

Shutdown Logic Input Current I

Shutdown Logic Low V

Shutdown Logic High V

3 µA

SHDN

500 nA

LOGIC

0.8 V

INL

2.4 V

INH

1

The long-term stability specification is noncumulative. The drift subsequent 1,000 hour periods is significantly lower than in the first 1,000 hour period.

Rev. E | Page 5 of 20

ADR390/ADR391/ADR392/ADR395

ADR395—SPECIFICATIONS

Electrical characteristics, VIN = 5.3 V to 15 V, TA = 25°C, unless otherwise noted.

Table 5.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE VO A Grade 4.994 5.000 5.006 V

V

V

V

B Grade 4.995 5.000 5.005 V

O

V

A Grade 6 mV INITIAL ACCURACY

OERR

B Grade 0.12 %

V

OERR

B Grade 5 mV

OERR

B Grade 0.10 %

OERR

A Grade, −40°C < TA < +125°C 25 ppm/°C TEMPERATURE COEFFICIENT TCVO

B Grade, −40°C < T

< +125°C 9 ppm/°C

A

SUPPLY VOLTAGE HEADROOM VIN − VO 300 mV

LINE REGULATION ∆VO/∆VIN VIN = 4.3 V to 15 V, −40°C < TA < +85°C 10 25 ppm/V

LOAD REGULATION ∆VO/∆I

LOAD

I

= 0 mA to 5 mA, −40°C < TA < +85°C, VIN = 6 V 140 ppm/mA

LOAD

No Load 120 µA QUIESCENT CURRENT IIN

< +125°C 140 µA

A

VOLTAGE NOISE e

−40°C < T

0.1 Hz to 10 Hz 8 µV p-p

N p-p

TURN-ON SETTLING TIME tR 20 µs

LONG-TERM STABILITY1 ∆VO 1, 000 Hours 50 ppm

OUTPUT VOLTAGE HYSTERESIS ∆V

100 ppm

O_HYS

RIPPLE REJECTION RATIO RRR fIN = 60 kHz 80 dB

VIN = 5 V 25 mA SHORT CIRCUIT TO GND ISC

V

= 15 V 30 mA

IN

SHUTDOWN PIN

Shutdown Supply Current I

Shutdown Logic Input Current I

Shutdown Logic Low V

Shutdown Logic High V

3 µA

SHDN

500 nA

LOGIC

0.8 V

INL

2.4 V

INH

1

The long-term stability specification is noncumulative. The drift subsequent 1,000 hour periods is significantly lower than in the first 1,000 hour period.

Rev. E | Page 6 of 20

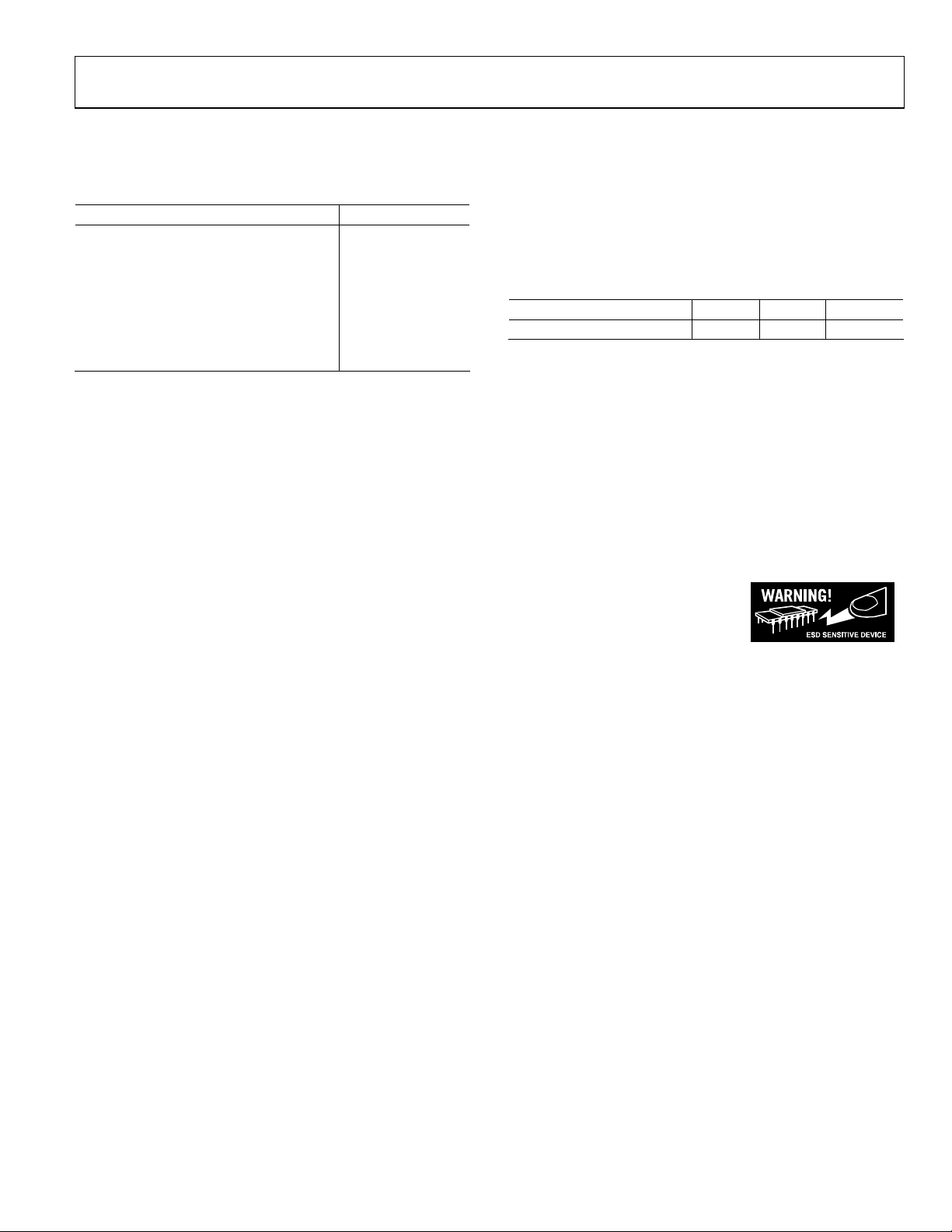

ADR390/ADR391/ADR392/ADR395

ABSOLUTE MAXIMUM RATINGS

At 25°C, unless otherwise noted.

Table 6.

Parameter Rating

Supply Voltage 18 V

Output Short-Circuit Duration to GND

Storage Temperature Range –65°C to +125°C

Operating Temperature Range –40°C to +125°C

Junction Temperature Range –65°C to +125°C

Lead Temperature Range

(Soldering, 60 sec)

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

See Derating

Curves

300°C

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, i.e., θJA is specified

for a device soldered in a circuit board for surface-mount

packages.

Table 7. Thermal Resistance

Package Type θJA θ

TSOT-23-5 (UJ-5) 230 146 °C/W

Unit

JC

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. E | Page 7 of 20

ADR390/ADR391/ADR392/ADR395

(

TERMINOLOGY

Temperature Coefficient

= VO(25°C) – V

V

O_HYS

O_TC

The change of output voltage with respect to operating

temperature changes normalized by the output voltage at 25°C.

This parameter is expressed in ppm/°C and can be determined

by the following equation:

–

() ()

[]

O

Cppm/TCV

O

=°

()

O

TVTV

2

1

O

×°

–25

()

TTCV

12

6

×

10

where:

V

(25°C) = VO at 25°C

O

V

(T1) = VO at Temperature 1

O

V

(T2) = VO at Temperature 2

O

Line Regulation

The change in output voltage due to a specified change in input

voltage. This parameter accounts for the effects of self-heating.

Line regulation is expressed in either percent per volt, partsper-million per volt, or microvolts per volt change in input

voltage.

Load Regulation

The change in output voltage due to a specified change in load

current. This parameter accounts for the effects of self-heating.

Load regulation is expressed in either microvolts per milliampere, parts-per-million per milliampere, or ohms of dc

output resistance.

Long-Term Stability

Typical shift of output voltage at 25°C on a sample of parts

subjected to a test of 1,000 hours at 25°C.

)

VCV

°

[]

ppmV

O_HYS

O

=

–25

O_TC

()

CV

°

25

O

6

×

10

where:

(25°C) = VO at 25°C

V

O

V

= VO at 25°C after a temperature cycle from + 25°C

O_TC

to –40°C to +125°C and back to +25°C

NOTES

Input Capacitor

Input capacitors are not required on the ADR39x. There is no

limit for the value of the capacitor used on the input, but a

1 µF to 10 µF capacitor on the input will improve transient

response in applications where the supply suddenly changes.

An additional 0.1 µF in parallel will also help reduce noise

from the supply.

Output Capacitor

The ADR39x does not require output capacitors for stability

under any load condition. An output capacitor, typically 0.1 µF,

will filter out any low level noise voltage and will not affect the

operation of the part. On the other hand, the load transient

response can improve with an additional 1 µF to 10 µF output

capacitor in parallel. A capacitor here will act as a source of

stored energy for a sudden increase in load current. The only

parameter that will degrade by adding an output capacitor is the

turn-on time, and it depends on the size of the capacitor chosen.

200

DATA TAKEN IN CONTROLLED

ENVIRONMENT @ 50

150

°C ± 1°C

∆V

= VO(t0) – VO(t1)

O

()

⎛

[]

ppmV

O

O

⎜

⎝

–

0

O

()

O

()

tV

0

tVtV

⎞

1

6

10

×=∆

⎟

⎠

where:

(T0) = VO at 25°C at Time 0

V

O

(T1) = VO at 25°C after 1,000 hours operation at 25°C

V

O

Thermal Hysteresis

The change of output voltage after the device is cycled through

temperatures from +25°C to –40°C to +125°C and back to

100

50

0

DRIFT (ppm)

–50

–100

–150

0

86 176 250 324 440 640 840 1040

Figure 2. ADR391 Typical Long-Term Drift over 1,000 Hours

TIME (Hours)

00419-D-002

+25°C. This is a typical value from a sample of parts put

through such a cycle.

Rev. E | Page 8 of 20

ADR390/ADR391/ADR392/ADR395

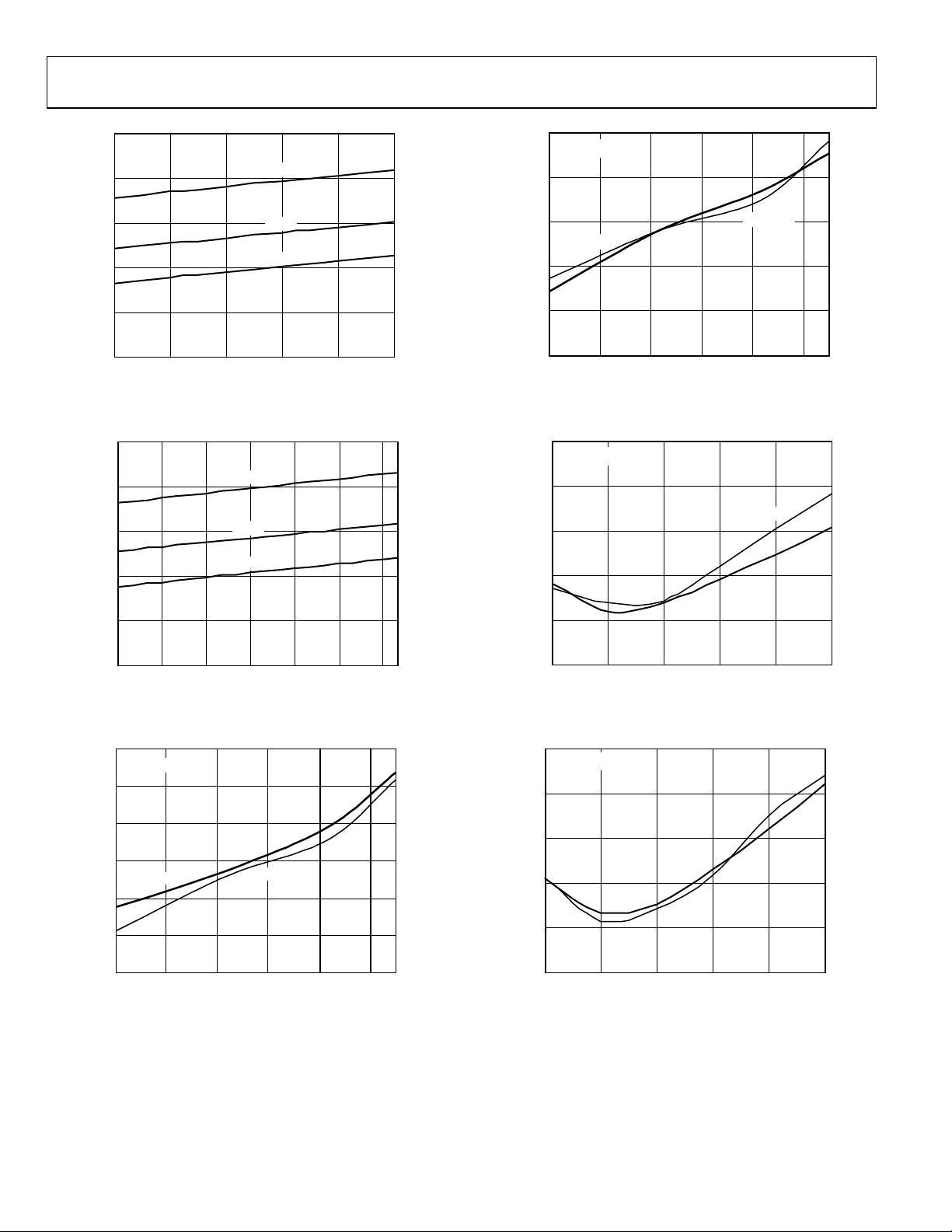

TYPICAL PERFORMANCE CHARACTERISTICS

2.060

5.006

2.056

(V)

2.052

2.048

OUTPUT VOLTAGE

SAMPLE 1

2.044

2.040

–40 –5

SAMPLE 2

30 65 100 125

TEMPERATURE (°C)

Figure 3. ADR390 Output Voltage vs. Temperature

2.506

2.504

SAMPLE 1

2.502

(V)

2.500

OUT

V

2.498

2.496

SAMPLE 3

SAMPLE 2

SAMPLE 3

00419-D-003

5.004

SAMPLE 3

5.002

SAMPLE 2

(V)

5.000

OUT

V

4.998

4.996

4.994

–40 –5 30 65 125

SAMPLE 1

TEMPERATURE (°C)

100

Figure 6. ADR395 Output Voltage vs. Temperature

140

+125

°

A)

µ

SUPPLY CURRENT (

120

100

80

60

+85°C

+25

–40

C

°

C

°

C

00419-D-006

2.494

–40 –5

30 65 100 125

TEMPERATURE (°C)

Figure 4. ADR391 Output Voltage vs. Temperature

4.100

4.098

SAMPLE 3

4.096

(V)

4.094

OUT

SAMPLE 1

V

4.092

4.090

4.088

–40 0 40 80 125

SAMPLE 2

TEMPERATURE (°C)

Figure 5. ADR392 Output Voltage vs. Temperature

00419-D-004

00419-D-005

40

2.5 15.05.0

7.5 10.0 12.5

INPUT VOLTAGE (V)

Figure 7. ADR390 Supply Current vs. Input Voltage

140

120

A)

µ

100

80

SUPPLY CURRENT (

60

40

2.5 15.05.0

+85°C

+25

°

C

7.5 10.0 12.5

INPUT VOLTAGE (V)

Figure 8. ADR391 Supply Current vs. Input Voltage

–40

00419-D-007

°

C

00419-D-008

Rev. E | Page 9 of 20

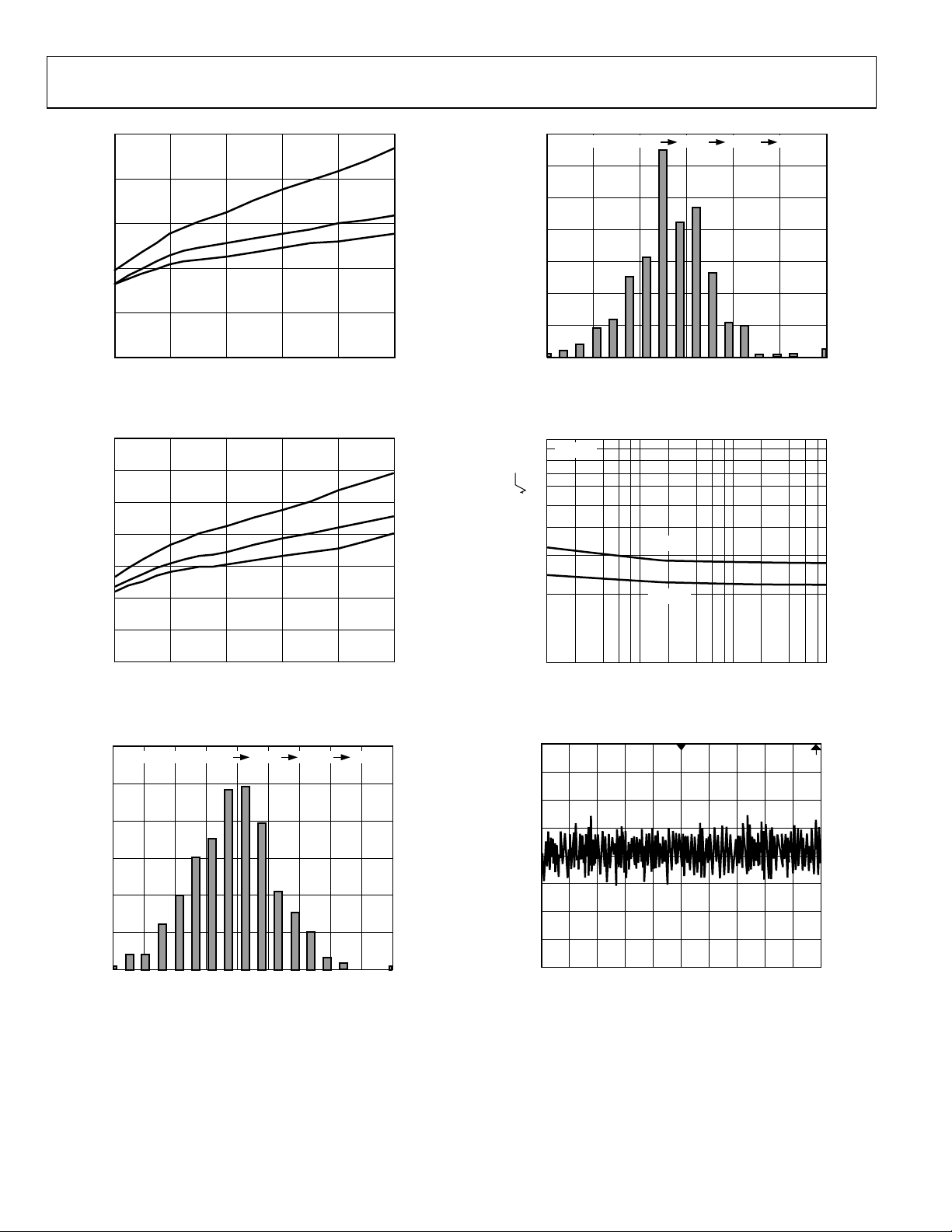

ADR390/ADR391/ADR392/ADR395

140

120

+125°C

180

IL= 0mA TO 5mA

160

100

80

SUPPLY CURRENT (µA)

60

40

57911 15

INPUT VOLTAGE(V)

+25°C

–40°C

13

Figure 9. ADR392 Supply Current vs. Input Voltage

140

120

100

80

SUPPLY CURRENT (µA)

60

40

5.5 7.0 8.5 10.0 14.5

+125°C

+25°C

–40°C

11.5

INPUT VOLTAGE (V)

13.0

Figure 10. ADR395 Supply Current vs. Input Voltage

120

IL= 0mA TO 5mA

100

80

60

VIN = 3.0V

40

VIN = 5.0V

00419-D-009

00419-D-010

140

VIN = 3.0V

120

LOAD REGULATION (ppm/mA)

100

80

–40 –10

20

TEMPERATURE (

50 80 110 125

VIN = 5.0V

°C)

Figure 12. ADR391 Load Regulation vs. Temperature

90

IL= 0mA TO 5mA

80

VIN = 7.5V

70

60

LOAD REGULATION (ppm/mA)

50

40

–40 –5 30 65 125

TEMPERATURE (

100

°C)

Figure 13. ADR392 Load Regulation vs. Temperature

80

IL= 0mA TO 5mA

70

60

50

V

= 7.5V

IN

VIN = 5V

V

= 5V

IN

00419-D-012

00419-D-013

LOAD REGULATION (ppm/mA)

20

0

–40 –10

20 50 80 125

TEMPERATURE (

°C)

Figure 11. ADR390 Load Regulation vs. Temperature

110

00419-D-011

Rev. E | Page 10 of 20

LOAD REGULATION (ppm/mA)

40

30

–40 –5 30 65 125

TEMPERATURE (°C)

100

Figure 14. ADR395 Load Regulation vs. Temperature

00419-D-014

ADR390/ADR391/ADR392/ADR395

25

14

20

15

10

LINE REGULATION (ppm/V)

5

0

–

40

–

10

20 80 110 125

TEMPERATURE (°C)

50

Figure 15. ADR390 Line Regulation vs. Temperature

25

20

15

10

LINE REGULATION (ppm/V)

5

00419-D-015

12

10

8

6

4

LINE REGULATION (ppm/V)

2

0

–40–53065 125

VIN = 5.3V TO 15V

TEMPERATURE (°

100

C)

Figure 18. ADR395 Line Regulation vs. Temperature

3.0

+125°

2.8

2.6

2.4

VIN_MIN (V)

+85°

C

2.2

+25°

–40°

C

C

C

00419-D-018

0

–

40

–

10

20 80 110 125

TEMPERATURE (°C)

50

Figure 16. ADR391 Line Regulation vs. Temperature

14

12

10

8

6

4

LINE REGULATION (ppm/V)

2

0

–40–53065 125

VIN = 4.4V TO 15V

TEMPERATURE (°

100

00419-D-017

C)

Figure 17. ADR392 Line Regulation vs. Temperature

00419-D-016

2.0

01

234

LOAD CURRENT (mA)

Figure 19. ADR390 Minimum Input Voltage vs. Load Current

3.6

3.4

3.2

3.0

VIN_MIN (V)

2.8

2.6

01

2345

LOAD CURRENT (mA)

+125

+85

Figure 20. ADR391 Minimum Input Voltage vs. Load Current

+25

–40

00419-D-019

5

°

C

°

C

°

C

°

C

00419-D-020

Rev. E | Page 11 of 20

ADR390/ADR391/ADR392/ADR395

4.8

°

C

4.6

4.4

4.2

VIN_MIN (V)

4.0

+125

+25°C

–40

°

C

70

TEMPERATURE: +25°C

60

50

40

30

FREQUENCY

20

10

–40

°C

+125

°C +25°C

3.8

0123 5

LOAD CURRENT (mA)

4

Figure 21. ADR392 Minimum Input Voltage vs. Load Current

6.0

5.8

°

C

5.6

5.4

5.2

VIN_MIN (V)

5.0

4.8

4.6

0123 5

LOAD CURRENT (mA)

+125

+25

–40

°

C

°

C

4

Figure 22. ADR395 Minimum Input Voltage vs. Load Current

60

TEMPERATURE: +25

50

40

30

FREQUENCY

20

10

0

–0.18 –0.06

–0.24

Figure 23. ADR390 V

–0.12

V

–40°C

°C

0 0.06 0.18

DEVIATION (mV)

OUT

Hysteresis Distribution

OUT

+125°C +25°C

0.12 0.24

0.30

00419-D-021

00419-D-022

00419-D-023

0

–0.41 –0.11

–0.56 –0.26

Figure 24. ADR391 V

1k

VIN = 5V

VOLTAGE NOISE DENSITY (nV/ Hz)

100

10 10k100

V

DEVIATION (mV)

OUT

OUT

ADR391

ADR390

FREQUENCY(Hz)

0.04 0.19

Hysteresis Distribution

1k

Figure 25. Voltage Noise Density vs. Frequency

0

0

0

0

V/DIV)

µ

0

0

VOLTAGE (2

0

0

0

TIME (1 Sec/DIV)

Figure 26. ADR391 Typical Voltage Noise 0.1 Hz to 10 Hz

0.34

00419-D-024

00419-D-025

00419-D-026

Rev. E | Page 12 of 20

ADR390/ADR391/ADR392/ADR395

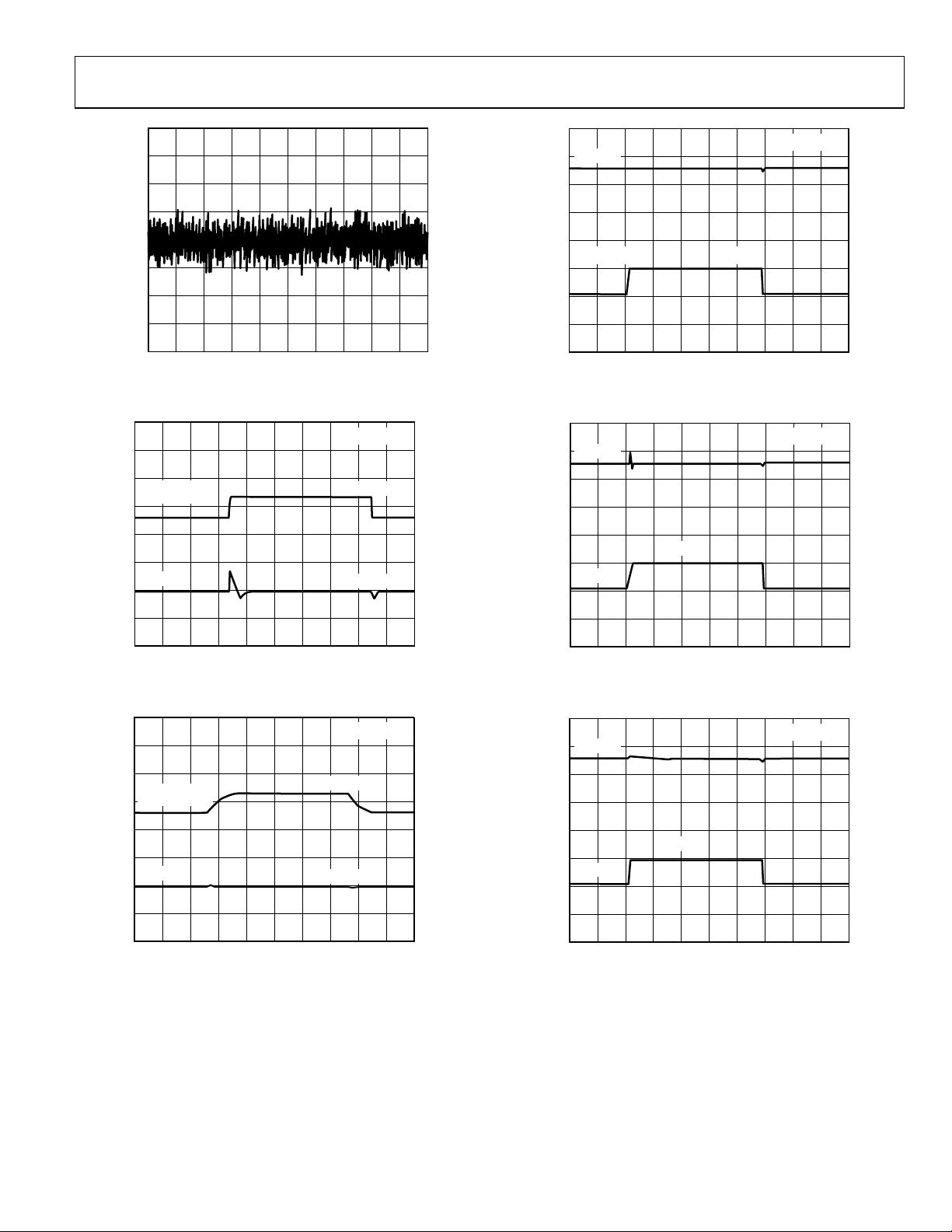

CL = 0nF

00419-D-030

CL = 1nF

VOLTAGE (100µV/DIV)

TIME (10µs/DIV)

Figure 27. ADR391 Voltage Noise 10 Hz to 10 kHz

C

BYPASS

= 0µF

V

OUT

V

ON

LOAD

VOLTAGE (1V/DIV)

TIME (200

LOAD OFF

µs/DIV)

Figure 30. ADR391 Load Transient Response

V

OUT

LINE

INTERRUPTION

VOLTAGE

V

OUT

TIME (10µs/DIV)

Figure 28. ADR391 Line Transient Response

LINE

INTERRUPTION

VOLTAGE

V

OUT

C

BYPASS

0.5V/DIV

1V/DIV

0.5V/DIV

1V/DIV

= 0.1

LOAD OFF

VOLTAGE (1V/DIV)

V

ON

LOAD

00419-D-028

TIME (200

µ

s/DIV)

00419-D-031

Figure 31. ADR391 Load Transient Response

µF

V

OUT

LOAD OFF

V

LOAD

ON

VOLTAGE (1V/DIV)

CL = 100nF

TIME (10

µs/DIV)

Figure 29. ADR391 Line Transient Response

00419-D-029

Rev. E | Page 13 of 20

TIME (200

µs/DIV)

Figure 32. ADR391 Load Transient Response

00419-D-032

ADR390/ADR391/ADR392/ADR395

VIN= 15V

RL= 500

Ω

5V/DIV

V

IN

VOLTAGE

V

OUT

2V/DIV

TIME (20µs/DIV)

Figure 33. ADR391 Turn-On Response Time at 15 V

VIN= 15V

VOLTAGE

V

V

IN

OUT

5V/DIV

2V/DIV

00419-D-033

V

VOLTAGE

OUT

V

IN

2V/DIV

5V/DIV

TIME (200µs/DIV)

Figure 36. ADR391 Turn-On/Turn-Off Response at 5 V

RL= 500

Ω

CL= 100nF

V

OUT

VOLTAGE (5V/DIV)

V

IN

2V/DIV

5V/DIV

00419-D-036

TIME (40µs/DIV)

Figure 34. ADR391 Turn-Off Response at 15 V

C

= 0.1µF

BYPASS

V

OUT

VOLTAGE

V

IN

2V/DIV

5V/DIV

TIME (200

µ

s/DIV)

Figure 35. ADR391 Turn-On/Turn-Off Response at 5 V

00419-D-034

00419-D-035

TIME (200

µ

s/DIV)

Figure 37. ADR391 Turn-On/Turn-Off Response at 5 V

80

60

40

20

0

–20

–40

–60

RIPPLE REJECTION (dB)

–80

–100

–120

10 1M100

1k 10k 100k

FREQUENCY (Hz)

Figure 38. Ripple Rejection vs. Frequency

00419-D-037

00419-D-038

Rev. E | Page 14 of 20

ADR390/ADR391/ADR392/ADR395

100

90

80

)

Ω

70

60

50

40

30

OUTPUT IMPEDANCE (

20

10

0

10 1M100

CL = 1µF

1k 10k 100k

FREQUENCY (Hz)

CL = 0µF

CL = 0.1µF

00419-D-039

Figure 39. Output Impedance vs. Frequency

Rev. E | Page 15 of 20

ADR390/ADR391/ADR392/ADR395

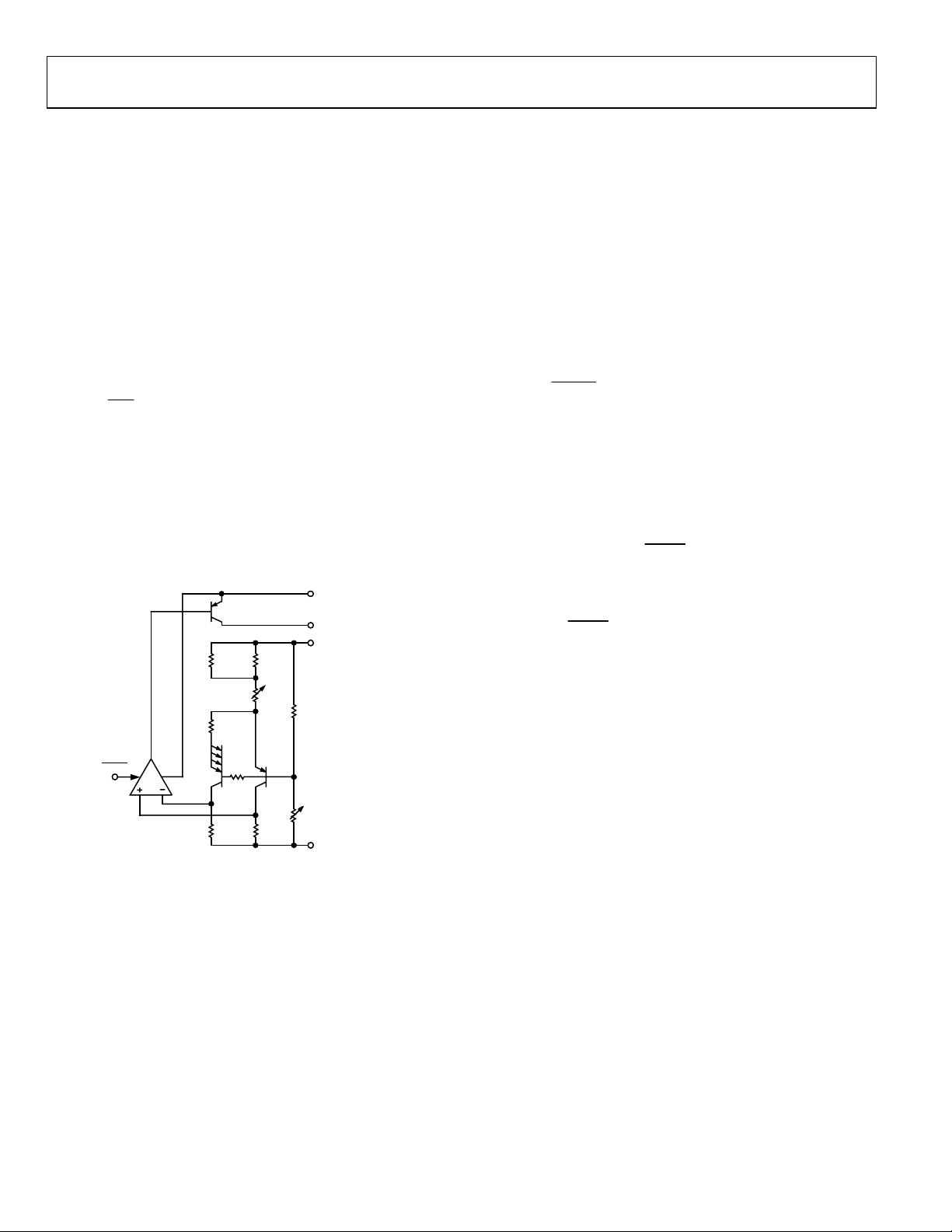

THEORY OF OPERATION

Band gap references are the high performance solution for low

supply voltage and low power voltage reference applications,

and the ADR390/ADR391/ADR392/ADR395 are no exception.

The uniqueness of these devices lies in the architecture. As

shown in Figure 40, the ideal zero TC band gap voltage is

referenced to the output, not to ground. Therefore, if noise

exists on the ground line, it will be greatly attenuated on V

The band gap cell consists of the PNP pair, Q51 and Q52,

running at unequal current densities. The difference in V

results in a voltage with a positive TC, which is amplified by a

ratio of

R58

2 ×

R54

This PTAT voltage, combined with V

s of Q51 and Q52,

BE

produces a stable band gap voltage.

Reduction in the band gap curvature is performed by the ratio

of the resistors R44 and R59, one of which is linearly

temperature dependent. Precision laser trimming and other

patented circuit techniques are used to further enhance the drift

performance.

V

IN

Q1

R59 R44

V

OUT (FORCE)

V

OUT (SENSE)

.

OUT

BE

Device Power Dissipation Considerations

The ADR390/ADR391/ADR392/ADR395 are capable of

delivering load currents to 5 mA with an input voltage that

ranges from 2.8 V (ADR391 only) to 15 V. When these devices

are used in applications with large input voltages, care should be

taken to avoid exceeding the specified maximum power

dissipation or junction temperature because it could result in

premature device failure. The following formula should be used

to calculate a device’s maximum junction temperature or

dissipation:

T–T

J

Pθ=

D

In this equation, T

ambient temperatures, P

θ

is the device package thermal resistance.

JA

A

JA

and TA are, respectively, the junction and

J

is the device power dissipation, and

D

Shutdown Mode Operation

The ADR390/ADR391/ADR392/ADR395 include a shutdown

feature that is TTL/CMOS level compatible. A Logic Low or a

SHDN

zero volt condition on the

pin is required to turn the

devices off. During shutdown, the output of the reference

becomes a high impedance state where its potential would then

be determined by external circuitry. If the shutdown feature is

SHDN

not used, the

pin should be connected to VIN (Pin 2).

SHDN

R58

R54

Q51

R60

Figure 40. Simplified Schematic

R49

R53

Q52

R48

R61

GND

00419-D-040

Rev. E | Page 16 of 20

ADR390/ADR391/ADR392/ADR395

APPLICATIONS

BASIC VOLTAGE REFERENCE CONNECTION

The circuit shown in Figure 41 illustrates the basic configuration

for the ADR39x family. Decoupling capacitors are not required

for circuit stability. The ADR39x family is capable of driving

capacitive loads from 0 µF to 10 µF. However, a 0.1 µF ceramic

output capacitor is recommended to absorb and deliver the

charge as required by a dynamic load.

SHUTDOWN

INPUT

C

*NOT REQUIRED

*

0.1µF

B

SHDN

V

IN

V

OUT(S)

Figure 41. Basic Configuration for the ADR39x Family

ADR39x

V

OUT(F)

GND

OUTPUT

*

0.1µF

C

B

00419-D-041

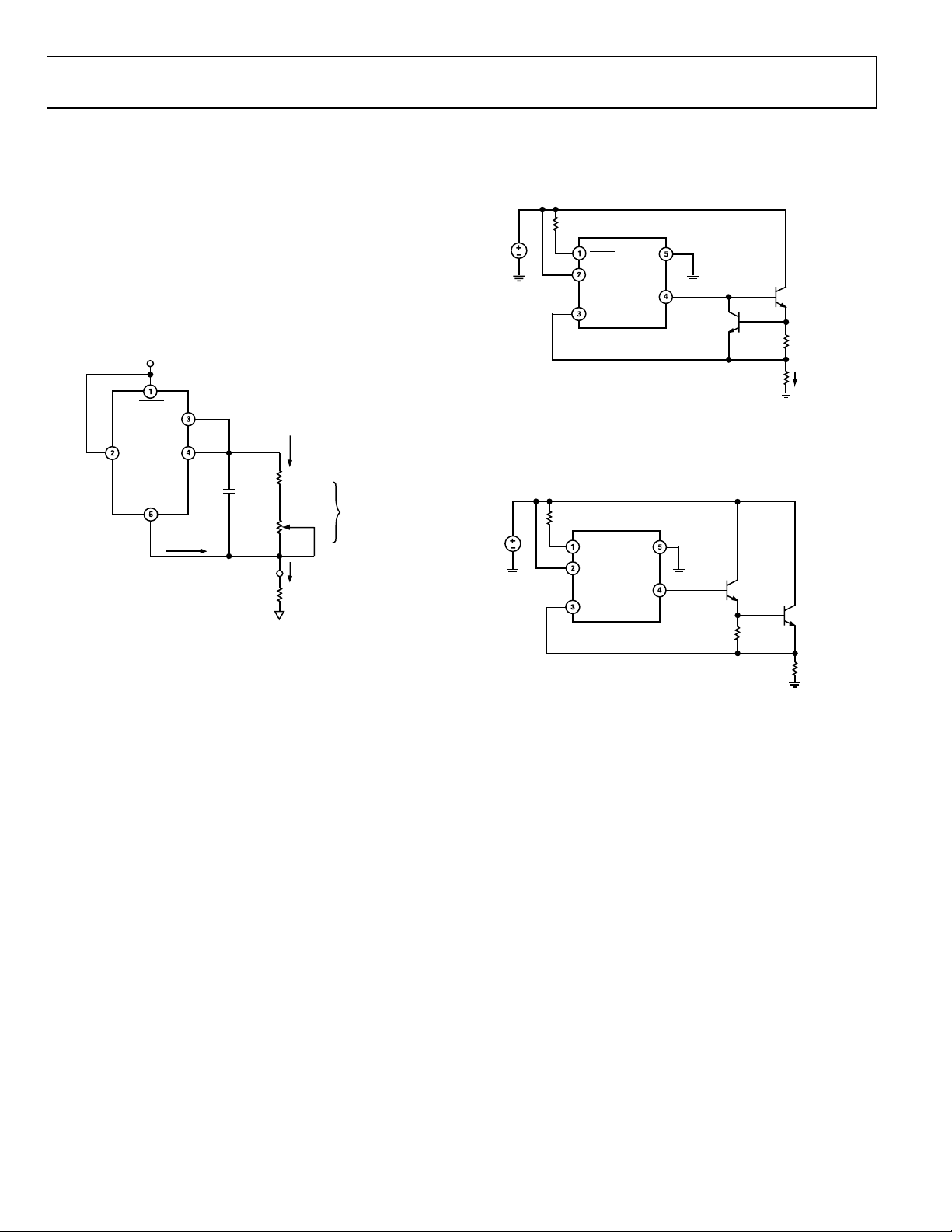

Stacking Reference ICs for Arbitrary Outputs

Some applications may require two reference voltage sources,

which are a combined sum of standard outputs. Figure 42 shows

how this “stacked output” reference can be implemented.

OUTPUTTABLE

U1/U2

ADR390/ADR390

ADR391/ADR391

ADR392/ADR392

ADR395/ADR395

V

IN

1

C2

0.1

µ

F

1

C2

0.1

µ

F

SHDN

SHDN

V

OUT1

2.048

2.5

4.096

5

2

V

GND

5

2

V

GND

5

IN

IN

(V)

U2

V

OUT(F)

V

OUT(S)

U1

V

OUT(F)

V

OUT(S)

V

OUT2

4.096

5.0

8.192

10

(V)

4

3

4

3

V

V

OUT2

OUT1

Two reference ICs are used, fed from an unregulated input, V

.

IN

The outputs of the individual ICs are simply connected in

series, which provides two output voltages, V

is the terminal voltage of U1, while V

V

OUT1

and V

OUT1

is the sum of

OUT2

OUT2

.

this voltage and the terminal voltage of U2. U1 and U2 are

simply chosen for the two voltages that supply the required

outputs (see the Output Table in Figure 42). For example, if both

U1 and U2 are ADR391s, V

is 2.5 V and V

OUT1

OUT2

is 5.0 V.

While this concept is simple, a precaution is in order. Since the

lower reference circuit must sink a small bias current from U2

plus the base current from the series PNP output transistor in

U2, either the external load of U1 or R1 must provide a path for

this current. If the U1 minimum load is not well defined, the R1

resistor should be used and set to a value that will conservatively

pass 600 µA of current with the applicable V

across it. Note

OUT1

that the two U1 and U2 reference circuits are treated locally as

macrocells; each has its own bypasses at input and output for

best stability. Both U1 and U2 in this circuit can source dc

currents up to their full rating. The minimum input voltage, V

is determined by the sum of the outputs, V

, plus the dropout

OUT2

IN

voltage of U2.

A Negative Precision Reference without Precision Resistors

A negative reference can be easily generated by adding an op

amp, A1, and is configured as shown in Figure 43. V

are at virtual ground and, therefore, the negative reference

V

OUTS

OUTF

and

can be taken directly from the output of the op amp. The op

amp must be dual-supply, low offset, and rail-to-rail if the

negative supply voltage is close to the reference output.

+V

DD

2

V

V

OUT(F)

V

OUT(S)

GND

5

IN

SHDN

1

–V

REF

4

3

A1

,

00419-D-042

Figure 42. Stacking Voltage References with the

ADR390/ADR391/ADR392/ADR395

–V

DD

Figure 43. Negative Reference

00419-D-043

Rev. E | Page 17 of 20

ADR390/ADR391/ADR392/ADR395

General-Purpose Current Source

Many times in low power applications, the need arises for a

precision current source that can operate on low supply

voltages. ADR390/ADR391/ADR392/ADR395 can be

configured as a precision current source. As shown in Figure 45,

the circuit configuration is a floating current source with a

grounded load. The reference’s output voltage is bootstrapped

across R

this configuration, circuit precision is maintained for load

currents in the range from the reference’s supply current,

typically 90 µA to approximately 5 mA.

High Power Performance with Current Limit

In some cases, the user may want higher output current

delivered to a load and still achieve better than 0.5% accuracy

out of the ADR39x. The accuracy for a reference is normally

specified on the data sheet with no load. However, the output

voltage changes with load current.

The circuit in Figure 45 provides high current without

compromising the accuracy of the ADR39x. The series pass

transistor Q1 provides up to 1 A load current. The ADR39x

delivers only the base drive to Q1 through the force pin. The

sense pin of the ADR39x is a regulated output and is connected

to the load.

, which sets the output current into the load. With

SET

V

IN

SHDN

V

OUT

ADR39x

V

V

OUT

IN

GND

(I

I

SY

SET

0.1µF

ADJUST

)

I

SET

R1

R1

R

= I

SET

P1

+ ISY(I

SET

SET

I

SY

I

OUT

R

L

Figure 44. A General-Purpose Current Source

)

00419-D-044

The transistor Q2 protects Q1 during short-circuit limit faults

by robbing its base drive. The maximum current is

≈ 0.6 V/RS

I

LMAX

R1

Ω

4.7k

V

IN

U1

SHDN

V

IN

V

OUT (FORCE)

V

OUT (SENSE)

ADR39x

GND

Q2N2222

Q2

R

R

Q1

Q2N4921

S

L

I

L

00419-D-045

Figure 45. ADR39x for High Power Performance with Current Limit

A similar circuit function can also be achieved with the

Darlington transistor configuration, as shown in see Figure 46.

R1

4.7k

Ω

SHDN

V

IN

V

OUT (FORCE)

V

OUT (SENSE)

ADR39x

U1

GND

Q2N2222

Q1

Q2

Q2N4921

R

S

R

L

V

IN

Figure 46. ADR39x for High Output Current

with Darlington Drive Configuration

00419-D-046

Rev. E | Page 18 of 20

ADR390/ADR391/ADR392/ADR395

OUTLINE DIMENSIONS

2.90 BSC

45

0.50

0.30

2.80 BSC

0.95 BSC

1.00 MAX

SEATING

PLANE

(UJ-5)

0.20

0.08

8°

4°

0.60

0.45

0.30

1.60 BSC

13

2

PIN 1

0.90

0.87

0.84

0.10 MAX

Figure 47. 5-Lead Thin Small Outline Transistor Package [TSOT ]

1.90

BSC

COMPLIANT TO JEDEC STANDARDS MO-193AB

Dimensions shown in millimeters

ORDERING GUIDE

Models

ADR390AUJZ-REEL71 2.048 6 0.29 25 TSOT UJ-5 R0A 3,000 –40°C to +125°C

ADR390AUJZ-R21 2.048 6 0.29 25 TSOT UJ-5 R0A 250 –40°C to +125°C

ADR390BUJZ-REEL71 2.048 4 0.19 9 TSOT UJ-5 R0B 3,000 –40°C to +125°C

ADR390BUJZ-R21 2.048 4 0.19 9 TSOT UJ-5 R0B 250 –40°C to +125°C

ADR391AUJZ-REEL71 2.5 6 0.24 25 TSOT UJ-5 R1A 3,000 –40°C to +125°C

ADR391AUJZ-R21 2.5 6 0.24 25 TSOT UJ-5 R1A 250 –40°C to +125°C

ADR391BUJZ-REEL71 2.5 4 0.16 9 TSOT UJ-5 R1B 3,000 –40°C to +125°C

ADR391BUJZ-R21 2.5 4 0.16 9 TSOT UJ-5 R1B 250 –40°C to +125°C

ADR392AUJZ-REEL71 4.096 6 0.15 25 TSOT UJ-5 RCA 3,000 –40°C to +125°C

ADR392AUJZ-R21 4.096 6 0.15 25 TSOT UJ-5 RCA 250 –40°C to +125°C

ADR392BUJZ-REEL71 4.096 5 0.12 9 TSOT UJ-5 RCB 3,000 –40°C to +125°C

ADR392BUJZ-R21 4.096 5 0.12 9 TSOT UJ-5 RCB 250 –40°C to +125°C

ADR395AUJZ-REEL71 5.0 6 0.12 25 TSOT UJ-5 RDA 3,000 –40°C to +125°C

ADR395AUJZ-R21 5.0 6 0.12 25 TSOT UJ-5 RDA 250 –40°C to +125°C

ADR395BUJZ-REEL71 5.0 5 0.10 9 TSOT UJ-5 RDB 3,000 –40°C to +125°C

ADR395BUJZ-R21 5.0 5 0.10 9 TSOT UJ-5 RDB 250 –40°C to +125°C

1

Z = Pb-free part.

Output

Voltage

(V

)

O

Initial

Accuracy

(mV) (%)

Temperature

Coefficient

(ppm/°C)

Package

Description

Package

Option

Branding

Number

of Parts

per Reel

Temperature

Range

Rev. E | Page 19 of 20

ADR390/ADR391/ADR392/ADR395

NOTES

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

C00419–0 –4/04(E)

Rev. E | Page 20 of 20

Loading...

Loading...