Analog Devices ADM9240 Datasheet

Low Cost Microprocessor

a

FEATURES

Six Direct Voltage Measurement Inputs (Including Two

Processor Core Voltages) with On-Chip Attenuators

On-Chip Temperature Sensor

Five Digital Inputs for VID Bits

Fully Supports Intel’s LANDesk Client Manager (LDCM)

Register-Compatible with LM7x Products

Two Fan Speed Monitoring Inputs

2C®

I

Compatible System Management Bus (SMBus)

Chassis Intrusion Detect

Interrupt Output

Programmable RESET I/O Pin

Shutdown Mode to Minimize Power Consumption

Limit Comparison of all Monitored Values

APPLICATIONS

Network Servers and Personal Computers

Microprocessor-Based Office Equipment

Test Equipment and Measuring Instruments

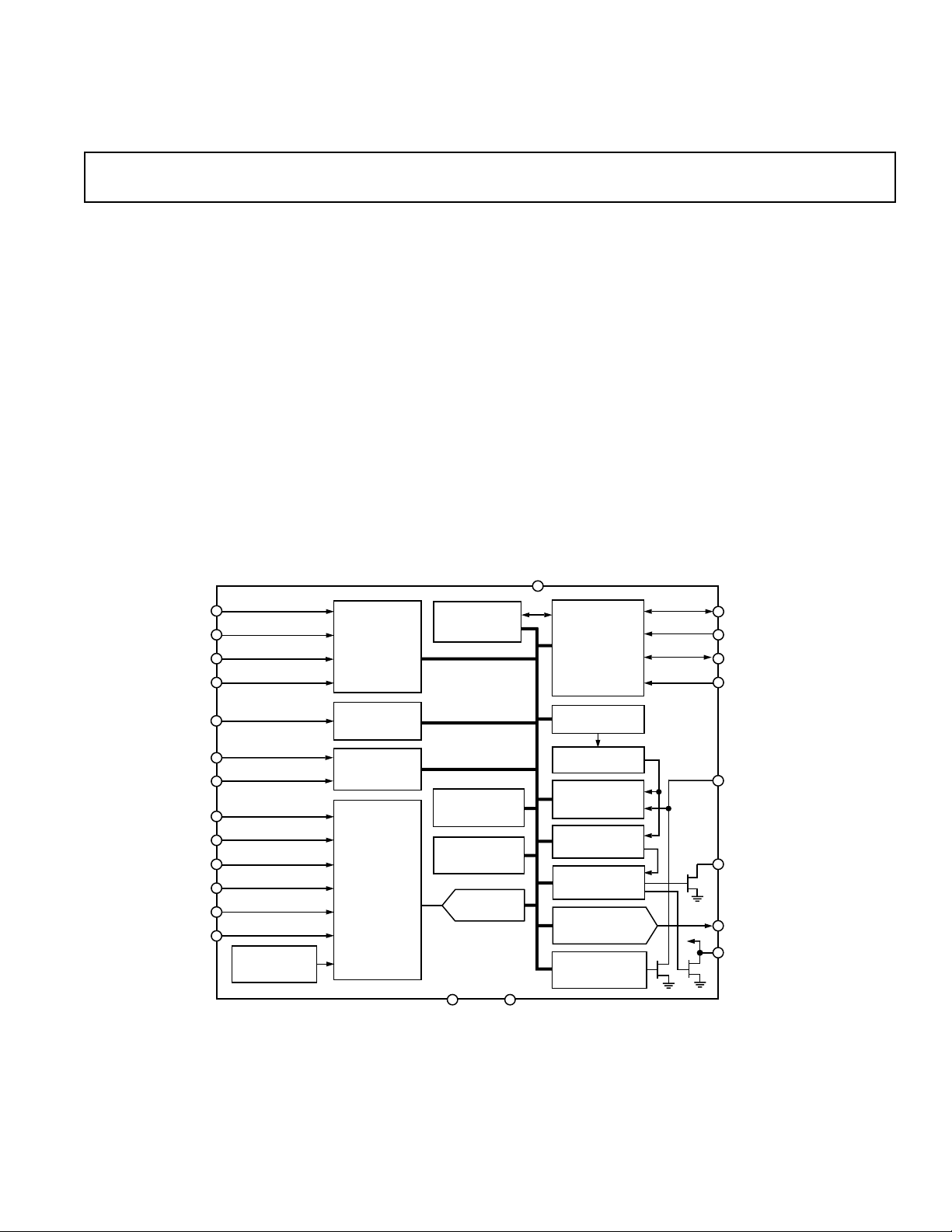

FUNCTIONAL BLOCK DIAGRAM

System Hardware Monitor

ADM9240

PRODUCT DESCRIPTION

The ADM9240 is a complete system hardware monitor for

microprocessor-based systems, providing measurement and

limit comparison of up to four power supplies and two processor core voltages, plus temperature, two fan speeds and chassis

intrusion. Measured values can be read out via an I

ible serial System Management Bus, and values for limit comparisons can be programmed in over the same serial bus. The

high speed successive approximation ADC allows frequent

sampling of all analog channels to ensure a fast interrupt

response to any out-of-limit measurement.

The ADM9240’s 2.85 V to 5.75 V supply voltage range, low

supply current and I

2

C compatible interface, make it ideal for a

wide range of applications. These include hardware monitoring

and protection applications in personal computers, electronic

test equipment and office electronics.

V

CC

2

C-compat-

VID0

VID1

VID2

VID3

VID4

FAN1

FAN2 CI

+V

CCP1

+2.5V

IN

+3.3V

IN

+5V

IN

+12V

IN

+V

CCP2

BANDGAP

TEMPERATURE

SENSOR

VID0 - 3 AND

FAN DIVISOR

REGISTERS

VID4 AND

DEVICE ID

REGISTER

FAN SPEED

COUNTER

INPUT

ATTENUATORS

AND

ANALOG

MULTIPLEXER

SERIAL BUS

ADDRESS

REGISTER

ADDRESS

POINTER

REGISTER

TEMPERATURE

CONFIGURATION

REGISTER

9-BIT ADC

ADM9240

GNDA GNDD

SERIAL BUS

INTERFACE

VALUE AND LIMIT

REGISTERS

LIMIT

COMPARATORS

INTERRUPT

STATUS

REGISTERS

INT MASK

REGISTERS

CONFIGURATION

REGISTER

ANALOG

OUTPUT REGISTER

AND 8-BIT DAC

CHASSIS

INTRUSION

CLEAR REGISTER

NTEST_OUT/A0

A1

SDA

SCL

INT

NTEST_IN/AOUT

RESET

I2C is a registered trademark of Philips Corporation.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1998

1, 2

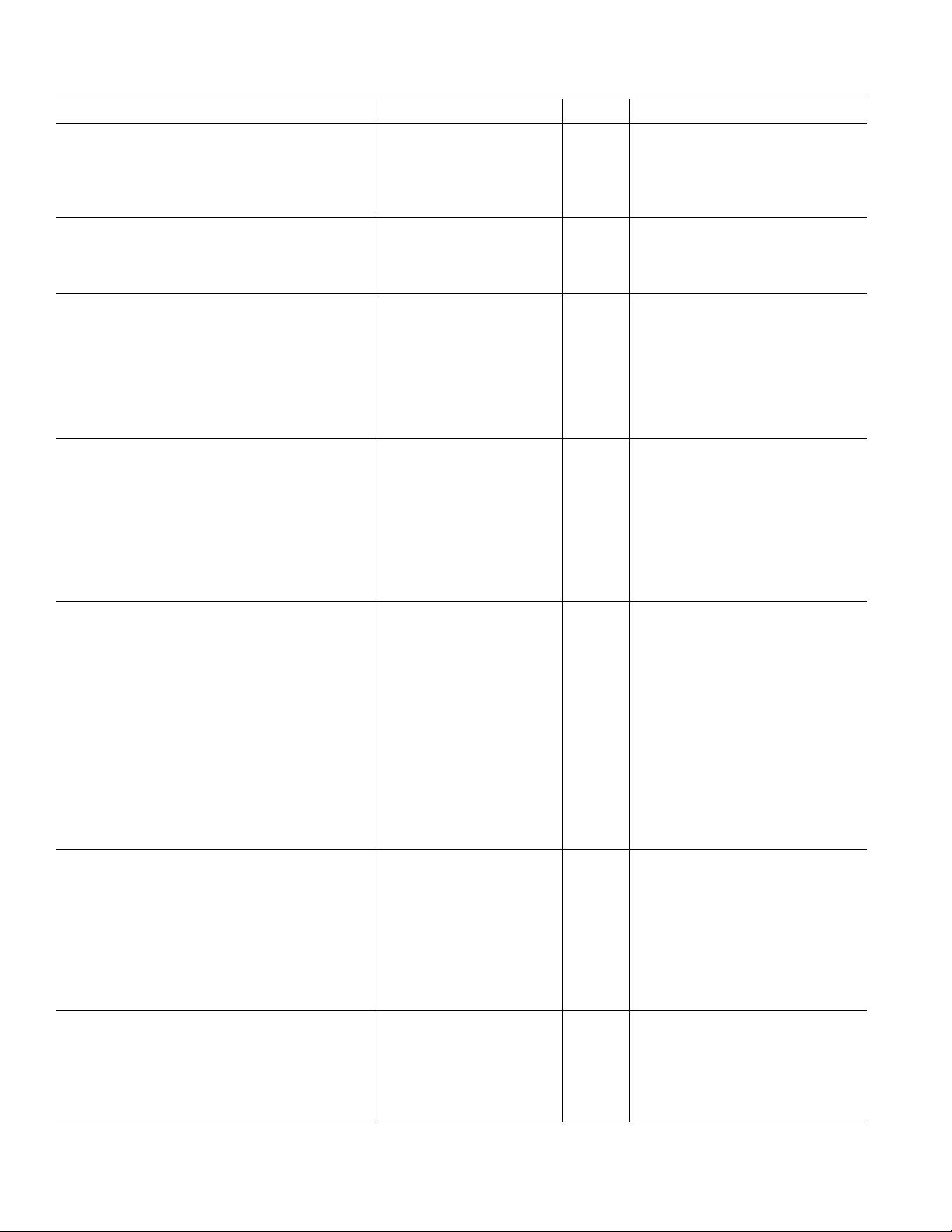

ADM9240–SPECIFICA TIONS

(TA = T

Parameter Min Typ Max Units Test Conditions/Comments

POWER SUPPLY

Supply Voltage, V

Supply Current, I

CC

CC

2.85 5 5.75 V

TEMPERATURE-TO-DIGITAL CONVERTER

Accuracy ± 3 °C –40°C ≤ T

Resolution ±0.5 °C

ANALOG-TO-DIGITAL CONVERTER

(INCLUDING MUX AND ATTENUATORS)

Total Unadjusted Error, TUE ±2 % Note 3

Differential Nonlinearity, DNL ±1 LSB

Power Supply Sensitivity ±1 %/V

Total Monitoring Cycle Time 311 331 µs +25°C ≤ T

Input Resistance 100 140 200 kΩ

ANALOG OUTPUT

Output Voltage Range 0 1.25 V

Total Unadjusted Error, TUE ±3% I

Full-Scale Error ±1 ±3%

Zero Error 2 LSB No Load

Differential Nonlinearity, DNL ±1 LSB

Integral Nonlinearity ±1 LSB Monotonic by Design

Output Source Current 2 mA

Output Sink Current 1 mA

FAN RPM-TO-DIGITAL CONVERTER

Accuracy ±6 % +25°C ≤ T

Full-Scale Count 255

FAN1 and FAN2 Nominal Input RPM 8800 rpm Divisor = 1, Fan Count = 153

Internal Clock Frequency 21.1 22.5 23.9 kHz +25°C ≤ T

19.8 22.5 25.2 kHz –40oC ≤ TA ≤ +125°C

DIGITAL OUTPUT NTEST_OUT

Output High Voltage, V

OH

2.4 V I

2.4 V I

Output Low Voltage, V

OL

OPEN-DRAIN DIGITAL OUTPUTS

(INT, RESET, CI)

Output Low Voltage, V

High Level Output Current, I

OL

OH

RESET and CI Pulsewidth 20 45 ms

to T

MIN

, VCC = V

MAX

MIN

to V

, unless otherwise noted)

MAX

1.4 2.0 mA Interface Inactive, ADC Active

1.0 mA ADC Inactive, DAC Active

25 100 µA Shutdown Mode

≤ +125°C

A

±2 °C T

311 353 µs –40°C ≤ T

±12 % –40

= +25°C

A

≤ +125°C (Note 4)

A

≤ +125°C (Note 4)

A

= 2 mA

L

≤ +125°C

A

o

C ≤ TA ≤ +125°C

(Note 5)

4400 rpm Divisor = 2, Fan Count = 153

(Note 5)

2200 rpm Divisor = 3, Fan Count = 153

(Note 5)

1100 rpm Divisor = 4, Fan Count = 153

(Note 5)

≤ +125°C

A

= 5.0 mA,

OUT

= 4.25 V–5.75 V

V

CC

= 3.0 mA,

OUT

= 2.85 V–3.45 V

V

0.4 V I

0.4 V I

CC

= –5.0 mA,

OUT

= 4.25 V–5.75 V

V

CC

= –3.0 mA,

OUT

VCC = 2.85 V–3.45 V

0.4 V I

0.4 V I

0.1 100 µAV

= –5.0 mA, VCC = 5.75 V

OUT

= –3.0 mA, VCC = 3.45 V

OUT

= V

OUT

CC

–2– REV. 0

ADM9240

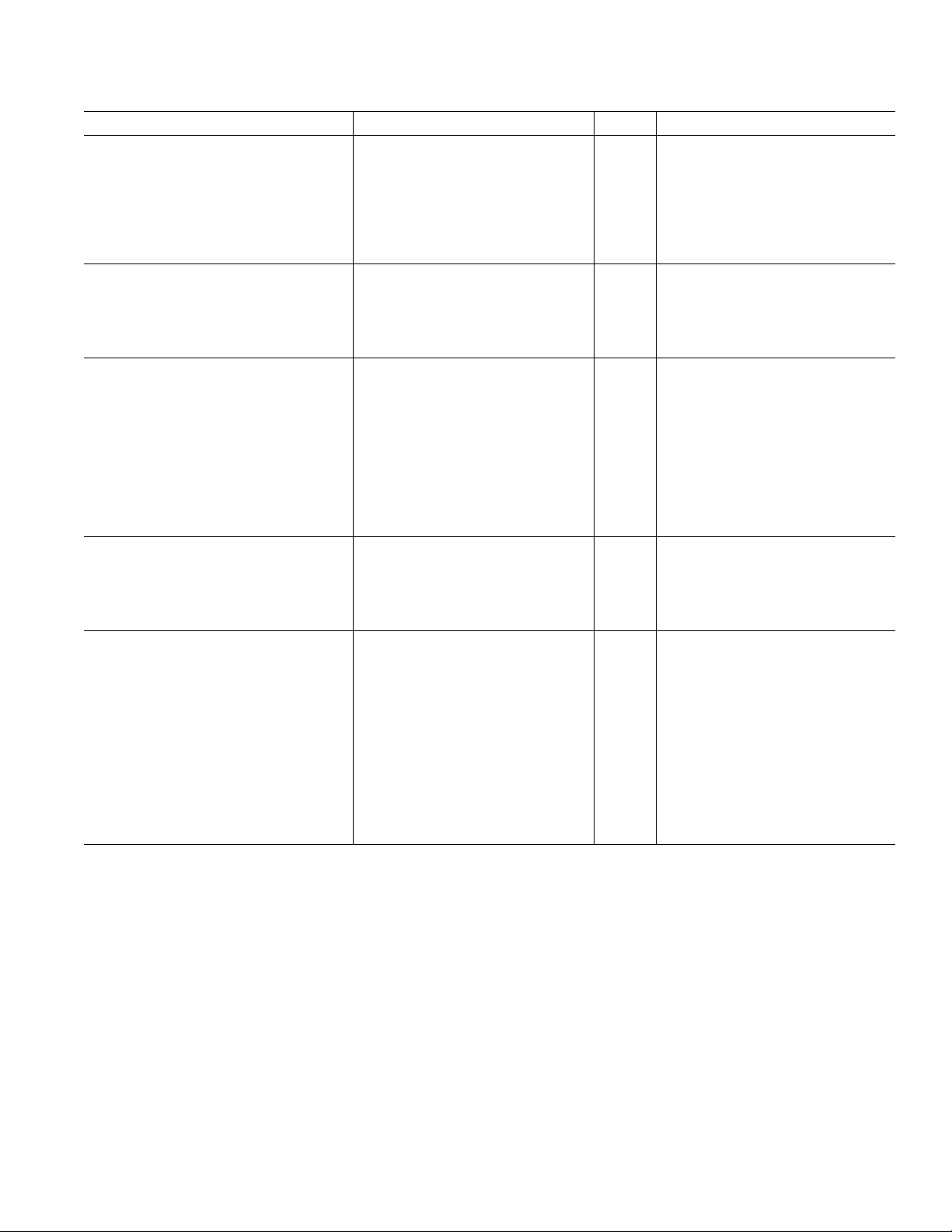

Parameter Min Typ Max Units Test Conditions/Comments

OPEN-DRAIN SERIAL DATA BUS

OUTPUT (SDA)

Output Low Voltage, V

OL

0.4 V I

0.4 V I

High Level Output Current, I

OH

0.1 100 µAV

SERIAL BUS DIGITAL INPUTS

(SCL, SDA)

Input High Voltage, V

Input Low Voltage, V

IL

IH

0.7 × V

CC

0.3 × V

CC

V

V

Hysteresis 500 mV

DIGITAL INPUT LOGIC LEVELS

(A0, A1, CI, RESET, VID0 – VID4,

FAN1, FAN2)

Input High Voltage, V

Input Low Voltage, V

IL

Input High Voltage, V

Input Low Voltage, V

IL

IH

IH

2.4 V VCC = 4.25 V–5.75 V

0.8 V VCC = 4.25 V–5.75 V

2.0 V VCC = 2.85 V–3.45 V

0.4 V VCC = 2.85 V–3.45 V

NTEST_IN

Input High Voltage, V

Input High Voltage, V

IH

IH

2.4 V VCC = 4.25 V–5.75 V

2.0 V VCC = 2.85 V–3.45 V

DIGITAL INPUT CURRENT

Input High Current, I

Input High Current, A0, A1, I

Input Low Current, I

Input Capacitance, C

SERIAL BUS TIMING

Clock Frequency, f

Glitch Immunity, t

Bus Free Time, t

Start Setup Time, t

Start Hold Time, t

SCL Low Time, t

SCL High Time, t

SCL, SDA Rise Time, t

SCL, SDA Fall Time, t

Data Setup Time, t

Data Hold Time, t

NOTES

1

All voltages are measured with respect to GND, unless otherwise noted.

2

Typicals are at TA = +25°C and represent most likely parametric norm. Shutdown current typ is measured with VCC = 3.3 V.

3

TUE (Total Unadjusted Error) includes Offset, Gain and Linearity errors of the ADC, multiplexer and on-chip input attenuators, including an external series input

protection resistor value between zero and 1 k Ω.

4

Total monitoring cycle time is the time taken to measure all six analog inputs plus the temperature sensor.

5

The total fan count is based on 2 pulses per revolution of the fan tachometer output.

6

A0 and A1 have internal 75 kΩ pull-down.

7

Timing specifications are tested at logic levels of V

Specifications subject to change without notice.

SCLK

SW

BUF

SU;STA

HD;STA

LOW

HIGH

SU;DAT

HD;DAT

IH

IH

IL

IN

7

R

F

= 0.3 × VCC for a falling edge and V

IL

–1 µAV

–200 75 µAV

1 µAV

20 pF

400 kHz See Figure 1

50 ns See Figure 1

1.3 µs See Figure 1

600 ns See Figure 1

600 ns See Figure 1

1.3 µs See Figure 1

0.6 µs See Figure 1

300 ns See Figure 1

300 µs See Figure 1

100 ns See Figure 1

900 ns See Figure 1

= 0.7 × VCC for a rising edge.

IH

= –3.0 mA,

OUT

= 4.25 V–5.75 V

V

CC

= –3.0 mA

OUT

= 2.85 V–3.45 V

V

CC

= V

OUT

IN

IN

IN

= V

= V

= 0

CC

CC

(Note 6)

CC

–3–REV. 0

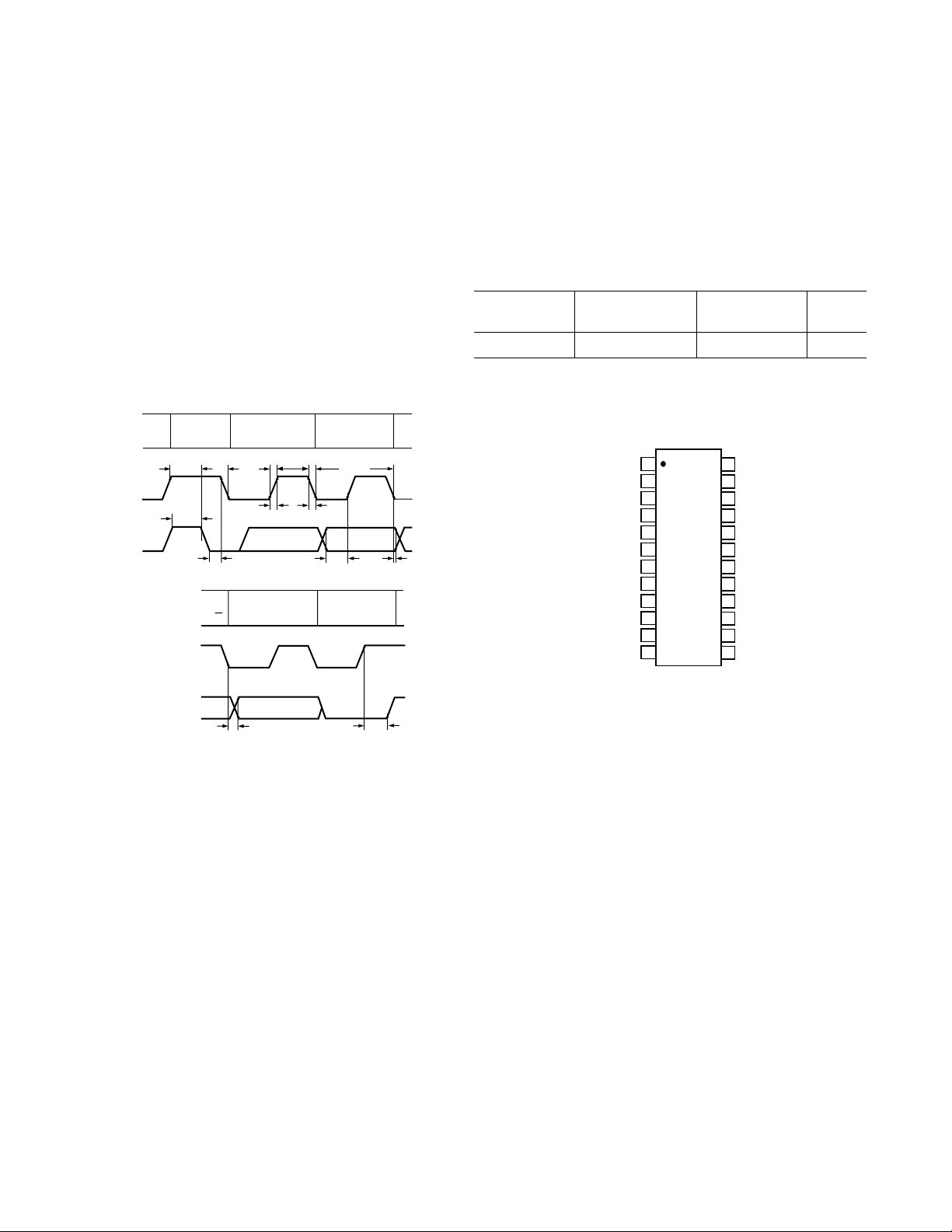

ADM9240

TOP VIEW

(Not to Scale)

24

23

22

21

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

9

10

11

12

ADM9240

RESET

NTEST_IN/AOUT

INT

V

CC

GNDD

NTEST_OUT/A0

A1

SDA

SCL

CI

FAN2

FAN1

GNDA

+V

CCP2

+12V

IN

+5V

IN

+3.3V

IN

VID0

VID1

VID2

VID3

+2.5V

IN

+V

CCP1

VID4

ABSOLUTE MAXIMUM RATINGS*

Positive Supply Voltage (VCC) . . . . . . . . . . . . . . . . . . . . . 6.5 V

Voltage on Any Input or Output Pin . . –0.3 V to (V

+ 0.3 V)

CC

(Except Analog Inputs)

16 V V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +16 V

IN

All Other Analog Inputs . . . . . . . . . . . . . . . . . . . . . . . . . +7.5 V

Ground Difference (GNDD–GNDA) . . . . . . . . . . . . ±300 mV

Input Current At Any Pin . . . . . . . . . . . . . . . . . . . . . . . ±5 mA

Package Input Current . . . . . . . . . . . . . . . . . . . . . . . . ±20 mA

Maximum Junction Temperature (T

max) . . . . . . . . . . 150°C

J

Storage Temperature Range . . . . . . . . . . . . .–65°C to +150°C

Lead Temperature, Soldering

Vapor Phase 60 (sec) . . . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared 15 (sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . +200°C

ESD Rating All Pins Except Pin 15 . . . . . . . . . . . . . . . .2000 V

ESD Rating Pin 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 V

PROTOCOL

SCL

SDA

PROTOCOL

Condition

t

SU;STA

t

BUF

Start

(S)

t

HD;STA

Bit 0

LSB

(R/W)

Bit 7

MSB

(A7)

t

t

LOW

t

r

Acknowledge

(A)

HIGH

t

f

1/f

t

SU;DAT

Stop

Condition

Bit 6

(A6)

(P)

SCL

t

HD;DAT

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

THERMAL CHARACTERISTICS

24-Lead Small Outline Package:

= 50°C/Watt, θ

θ

JA

= 10°C/Watt

JC

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

ADM9240ARU –40°C to +125°C 24-Lead TSSOP RU-24

PIN CONFIGURATION

SCL

SDA

t

VD;DAT

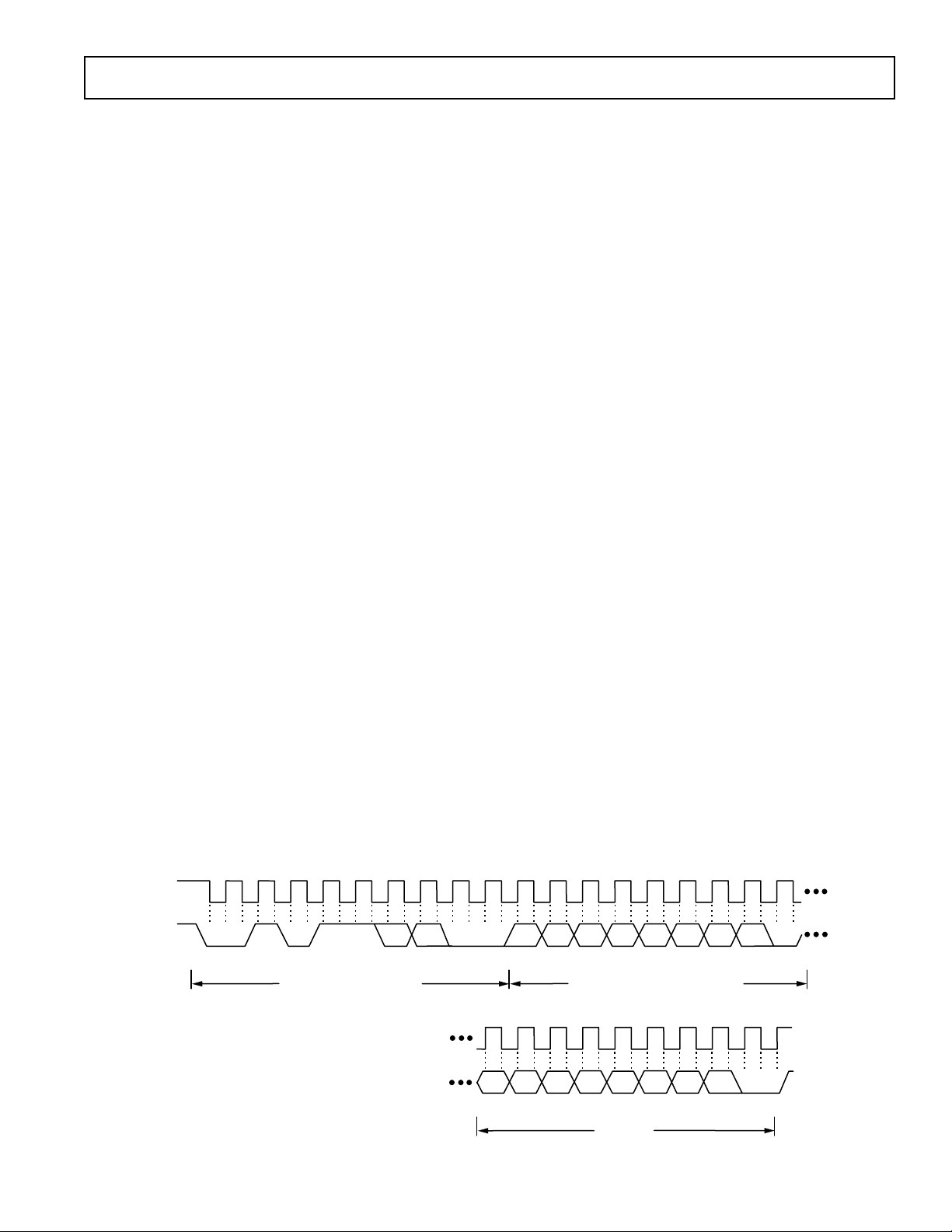

Figure 1. Diagram for Serial Bus Timing

t

SU;STO

–4– REV. 0

ADM9240

PIN FUNCTION DESCRIPTIONS

Pin Number Mnemonic Description

1 NTEST_OUT/A0 Digital I/O. Dual Function Pin. The lowest order programmable bit of the Serial Bus Address.

This pin functions as an output when doing a NAND Tree test.

2 A1 Digital Input. The highest order programmable bit of the Serial Bus Address.

3 SDA Digital I/O. Serial Bus Bidirectional Data. Open-drain output.

4 SCL Digital Input. Serial Bus Clock.

5 FAN1 Digital Input. 0 to V

6 FAN2 Digital Input. 0 to V

7 CI Digital I/O. An active high input from an external circuit that latches a Chassis Intrusion

event. This line can go high without any clamping action regardless of the powered state of

the ADM9240. The ADM9240 provides an internal open drain on this line, controlled by

Bit 6 of Register 40h or Bit 7 of Register 46h, to provide a minimum 20 ms pulse on this line,

to reset the external Chassis Intrusion Latch.

8 GNDD Digital Ground. Internally connected to all of the digital circuitry.

9V

CC

Power (+2.85 V to +5.75 V). Typically powered from +3.3 V or +5 V power rail. Bypass with

the parallel combination of 10 µF (electrolytic or tantalum) and 0.1 µF (ceramic) bypass

capacitors.

10 INT Digital Output. Interrupt Request (open drain). The output is enabled when Bit 1 of the

Configuration Register is set to 1. The default state is disabled.

11 NTEST_IN/AOUT Digital Input/Analog Output. An active-high input that enables NAND Tree mode board-

level connectivity testing. Refer to section on NAND Tree testing. Also functions as a pro-

grammable analog output when NAND Tree is not selected

12 RESET Digital I/O. Master Reset, 5 mA driver (open drain), active low output with a 20 ms minimum

pulsewidth. Available when enabled via Bit 7 in Register 44h, and set using Bit 4 in Register

40h. Also acts as reset input when pulled low (e.g., power-on reset).

13 GNDA Analog Ground. Internally connected to all analog circuitry. The ground reference for all

analog inputs.

14 +V

CCP2

Analog Input. Monitors processor core voltage +V

monitor the –12 V supply by adding two external resistors.

15 +12 V

16 +5 V

IN

17 +3.3 V

18 +2.5 V

19 +V

CCP1

IN

IN

IN

Analog Input. Monitors +12 V supply.

Analog Input. Monitors +5 V supply.

Analog Input. Monitors +3.3 V supply.

Analog Input. Monitors +2.5 V supply.

Analog Input. Monitors processor core voltage +V

20 VID4 Digital Input. Core Voltage ID readouts from the processor. This value is read into the

VID4 Status Register.

21 VID3 Digital Input. Core Voltage ID readouts from the processor. This value is read into the

VID0–VID3 Status Register.

22 VID2 Digital Input. Core Voltage ID readouts from the processor. This value is read into the

VID0–VID3 Status Register.

23 VID1 Digital Input. Core Voltage ID readouts from the processor. This value is read into the

VID0–VID3 Status Register.

24 VID0 Digital Input. Core Voltage ID readouts from the processor. This value is read into the

VID0–VID3 Status Register.

amplitude fan tachometer input.

CC

amplitude fan tachometer input.

CC

CCP2

CCP1

(0 V–3.6 V). Can also be used to

(0 V–3.6 V).

–5–REV. 0

ADM9240

GENERAL DESCRIPTION

The ADM9240 is a complete system hardware monitor for

microprocessor-based systems. The device communicates with

the system via a serial System Management Bus. The serial bus

controller has two hardwired address lines for device selection

(Pin 1 and Pin 2), a serial data line for reading and writing

addresses and data (Pin 3), and an input line for the serial clock

(Pin 4). All control and programming functions of the ADM9240

are performed over the serial bus.

An on-chip analog-to-digital converter with six multiplexed

analog inputs measures power supply voltages (+12 V, +5 V,

+3.3 V, +2.5 V—Pins 15 to 18) and processor core voltages

CCP1

and +V

(+V

input from an on-chip bandgap temperature sensor that monitors system ambient temperature.

Two count inputs (Pins 5 and 6) are provided for monitoring

the speed of fans with tachometer outputs. To accommodate

fans with different speeds and different tacho outputs, a divisor

of 1, 2, 4 or 8 can be programmed into the counter.

Five digital inputs (VID4 to VID0—Pins 20 to 24) read the

processor Voltage ID code, while a chassis intrusion input

(Pin 7) is provided to detect unauthorized tampering with the

equipment.

When the ADM9240 monitoring sequence is started, it cycles

sequentially through the measurement of analog inputs and the

temperature sensor, while at the same time the fan speed inputs

are independently monitored. Measured values from these inputs are stored in value registers. These can be read out over the

serial bus, or can be compared with programmed limits stored

in the limit registers. The results of out-of-limit comparisons are

stored in the interrupt status registers and will generate an interrupt on the INT line (Pin 10).

Any or all of the Interrupt Status Bits can be masked by appropriate programming of the Interrupt Mask Register.

A RESET input/output (Pin 12) is provided. Pulling this pin

low will reset all ADM9240 internal registers to default values.

The ADM9240 can also be programmed to give a low-going

20 ms reset pulse at this pin.

The ADM9240 contains an on-chip, 8-bit digital-to-analog

converter with an output range of zero to 1.25 V (Pin 11). This

is typically used to implement a temperature-controlled fan by

controlling the speed of a fan dependent upon the temperature

measured by the on-chip temperature sensor.

Testing of board level connectivity is simplified by providing a

NAND tree test function. The AOUT (Pin 11) also doubles as

a NAND test input, while Pin 1 doubles as a NAND tree output.

—Pins 19 and 14). The ADC also accepts

CCP2

INTERNAL REGISTERS OF THE ADM9240

A brief description of the ADM9240’s principal internal registers is given below. More detailed information on the function

of each register is given in Tables V to XVII.

Configuration Register: Provides control and configuration.

Serial Address Register: Stores the serial bus address of the

ADM9240.

Address Pointer Register: Contains the address that selects

one of the other internal registers. When writing to the ADM9240,

the first byte of data is always a register address, which is written

to the Address Pointer Register.

Interrupt (INT) Status Registers: Two registers to provide

status of each Interrupt event.

Interrupt (INT) Mask Registers: Allow masking of individual Interrupt sources.

Temperature Configuration Register: The configuration of

the temperature interrupt is controlled by the lower three bits of

this register.

VID/Fan Divisor Registers: The status of the VID0 to VID4

pins of the processor can be written to and read from these

registers. Divisor values for fan-speed measurement are also

stored in one of these registers.

Value and Limit Registers: The results of analog voltage

inputs, temperature and fan speed measurements are stored in

these registers, along with their limit values.

Analog Output Register: The code controlling the analog

output DAC is stored in this register.

Chassis Intrusion Clear Register: A signal latched on the

chassis intrusion pin can be cleared by writing to this register.

–6– REV. 0

ADM9240

SERIAL BUS INTERFACE

Control of the ADM9240 is carried out via the serial bus. The

ADM9240 is connected to this bus as a slave device, under the

control of a master device, e.g., the PIIX4.

The ADM9240 has a 7-bit serial bus address. When the device

is powered up, it will do so with a default serial bus address.

The five MSBs of the address are set to 01011, the two LSBs

are determined by the logical states of Pin 1(NTEST_OUT/A0)

and Pin 2 (A1) at power-up. These pins have internal 75 kΩ

pull-down resistors, so if they are left open-circuit the default

address will be 0101100.

The facility to make hardwired changes to A1 and A0 allows the

user to avoid conflicts with other devices sharing the same serial

bus, for example if more than one ADM9240 is used in a system. Once the ADM9240 has been powered up, the five MSBs

of the serial bus address may be changed by writing a 7-bit word

to the serial Address Pointer Register (the hardwired values of

A0 and A1 cannot be overwritten). Thereafter, the new serial

bus address must be used to select the ADM9240, until it is

changed again, or the device is powered off.

The serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a START

condition, defined as a high-to-low transition on the serial

data line SDA while the serial clock line SCL remains high.

This indicates that an address/data stream will follow. All

slave peripherals connected to the serial bus respond to the

START condition, and shift in the next eight bits, consisting

of a 7-bit address (MSB first) plus an R/W bit, which determines the direction of the data transfer, i.e., whether data

will be written to or read from the slave device.

The peripheral whose address corresponds to the transmitted

address responds by pulling the data line low during the low

period before the ninth clock pulse, known as the acknowledge bit. All other devices on the bus now remain idle while

the selected device waits for data to be read from or written

to it. If the R/W bit is a 0, the master will write to the slave

device. If the R/W bit is a 1, the master will read from the

slave device.

2. Data is sent over the serial bus in sequences of nine clock

pulses, eight bits of data followed by an acknowledge bit

from the slave device. Transitions on the data line must

occur during the low period of the clock signal and remain

stable during the high period, as a low-to-high transition

when the clock is high may be interpreted as a STOP signal.

The number of data bytes that can be transmitted over the

serial bus in a single READ or WRITE operation is limited

only by what the master and slave devices can handle.

3. When all data bytes have been read or written, stop conditions are established. In WRITE mode, the master will pull

the data line high during the tenth clock pulse to assert a

STOP condition. In READ mode, the master device will

override the acknowledge bit by pulling the data line high

during the low period before the ninth clock pulse. This is

known as No Acknowledge. The master will then take the

data line low during the low period before the tenth clock

pulse, then high during the tenth clock pulse to assert a

STOP condition.

Any number of bytes of data may be transferred over the serial

bus in one operation, but it is not possible to mix read and write

in one operation, because the type of operation is determined at

the beginning and cannot subsequently be changed without

starting a new operation.

In the case of the ADM9240, write operations contain either

one or two bytes, and read operations contain one byte and

perform the following functions:

To write data to one of the device data registers or read data

from it, the Address Pointer Register must be set so that the

correct data register is addressed, then data can be written into

that register or read from it. The first byte of a write operation

always contains an address that is stored in the Address Pointer

Register. If data is to be written to the device, then the write

operation contains a second data byte that is written to the

register selected by the Address Pointer Register.

This is illustrated in Figure 2a. The device address is sent over

the bus followed by R/W set to 0. This is followed by two data

bytes. The first data byte is the address of the internal data

register to be written to, which is stored in the Address Pointer

Register. The second data byte is the data to be written to the

internal data register.

SCL

SDA

START BY

MASTER

19

0

1 0 1 1 A1 A0 D7

FRAME 1

SERIAL BUS ADDRESS BYTE

SCL (CONTINUED)

SDA (CONTINUED)

R/W

ACK. BY

ADM9240

1

1

D7 D6

D6

D5 D4 D3

ADDRESS POINTER REGISTER BYTE

D5 D4 D3

FRAME 2

FRAME 3

DATA BYTE

D2

D2

D1 D0

D1

ACK. BY

ADM9240

D0

9

9

ACK. BY

ADM9240

STOP BY

MASTER

Figure 2a. Writing a Register Address to the Address Pointer Register, then Writing Data to the Selected Register

–7–REV. 0

Loading...

Loading...