Analog Devices ADM691A 3A 800 Datasheet

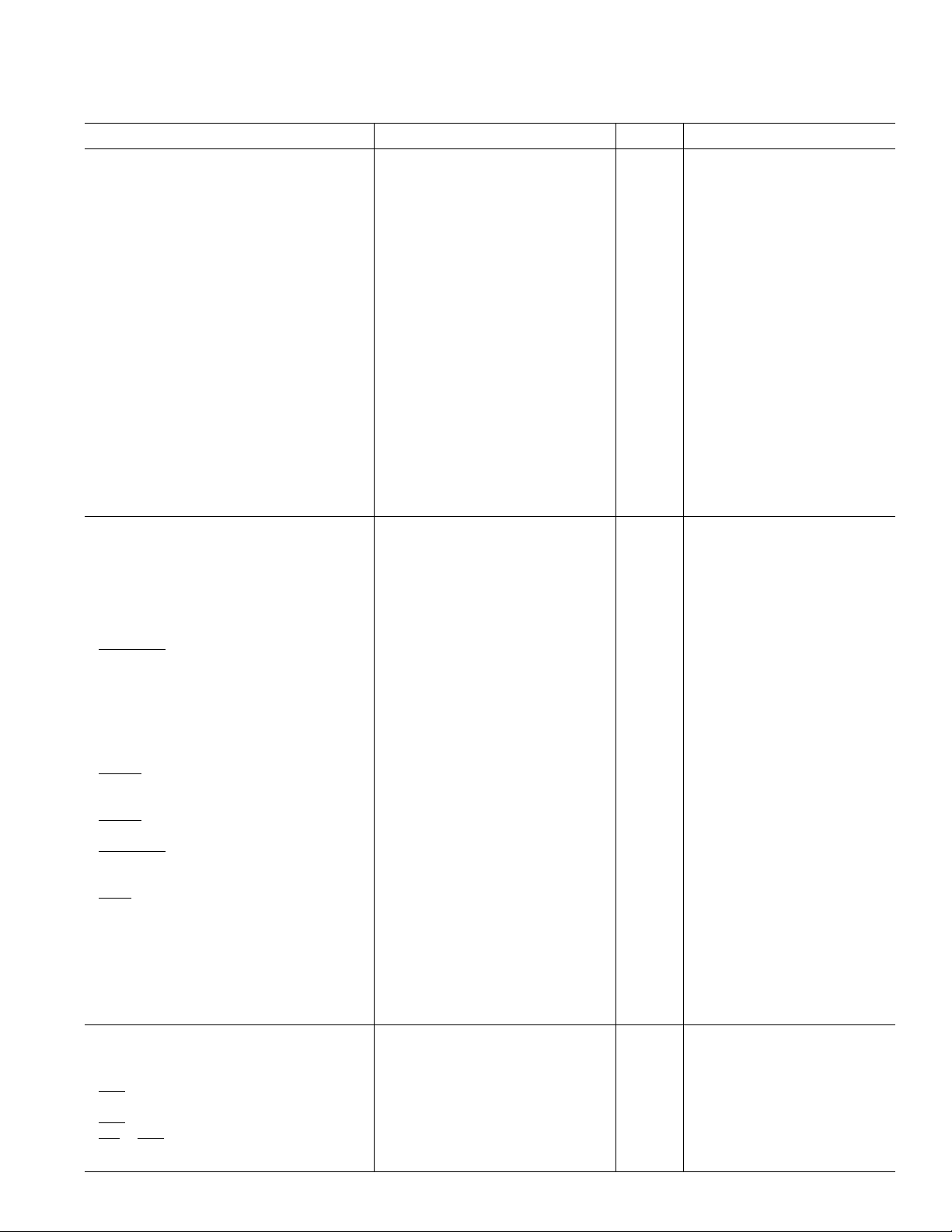

Microprocessor

V

BATT

V

CC

CMOS

RAM

CE

IN

OSC IN

OSC SEL

BAT

ON

LOW LINE

V

OUT

CE

OUT

RESET RESET

PFO

WDI

V

CC

WDO

I/O LINE

NMI

A0–A15

µP

POWER

µP

ADDRESS

DECODE

ADM691A

ADM693A

ADM800L

ADM800M

GND

PFI

BATTERY

0.1µF

+5V

NC

R2

R1

INPUT

POWER

7805

SYSTEM

STATUS

INDICATORS

a

ADM691A/ADM693A/ADM800L/M

FEATURES

Low Power Consumption:

Precision Voltage Monitor

62% Tolerance on ADM800L/M

Reset Time Delay—200 ms, or Adjustable

1 mA Standby Current

Automatic Battery Backup Power Switching

Fast Onboard Gating of Chip Enable Signals

Also Available in TSSOP Package (ADM691A)

APPLICATIONS

Microprocessor Systems

Computers

Controllers

Intelligent Instruments

Automotive Systems

Critical mP Power Monitoring

GENERAL DESCRIPTION

The ADM691A/ADM693A/ADM800L/ADM800M family of

supervisory circuits offers complete single chip solutions for

power supply monitoring and battery control functions in

microprocessor systems. These functions include µP reset,

backup-battery switchover, watchdog timer, CMOS RAM write

protection, and power-failure warning. The family of products

provides an upgrade for the MAX691A/93A/800M family of

products.

All parts are available in 16-pin DIP and SO packages. The

ADM691A is also available in a space-saving TSSOP package.

The following functionality is provided:

1. Power-on reset output during power-up, power-down and

brownout conditions. The circuitry remains operational with

V

as low as 1 V.

CC

2. Battery backup switching for CMOS RAM, CMOS microprocessor or other low power logic.

3. A reset pulse if the optional watchdog timer has not been

toggled within a specified time.

4. A 1.25 V threshold detector for power fail warning, low battery detection, or to monitor a power supply other than +5 V.

V

V

BATT

CE

OSC IN

OSC SEL

WATCHDOG

INPUT (WDI)

POWER FAIL

INPUT (PFI)

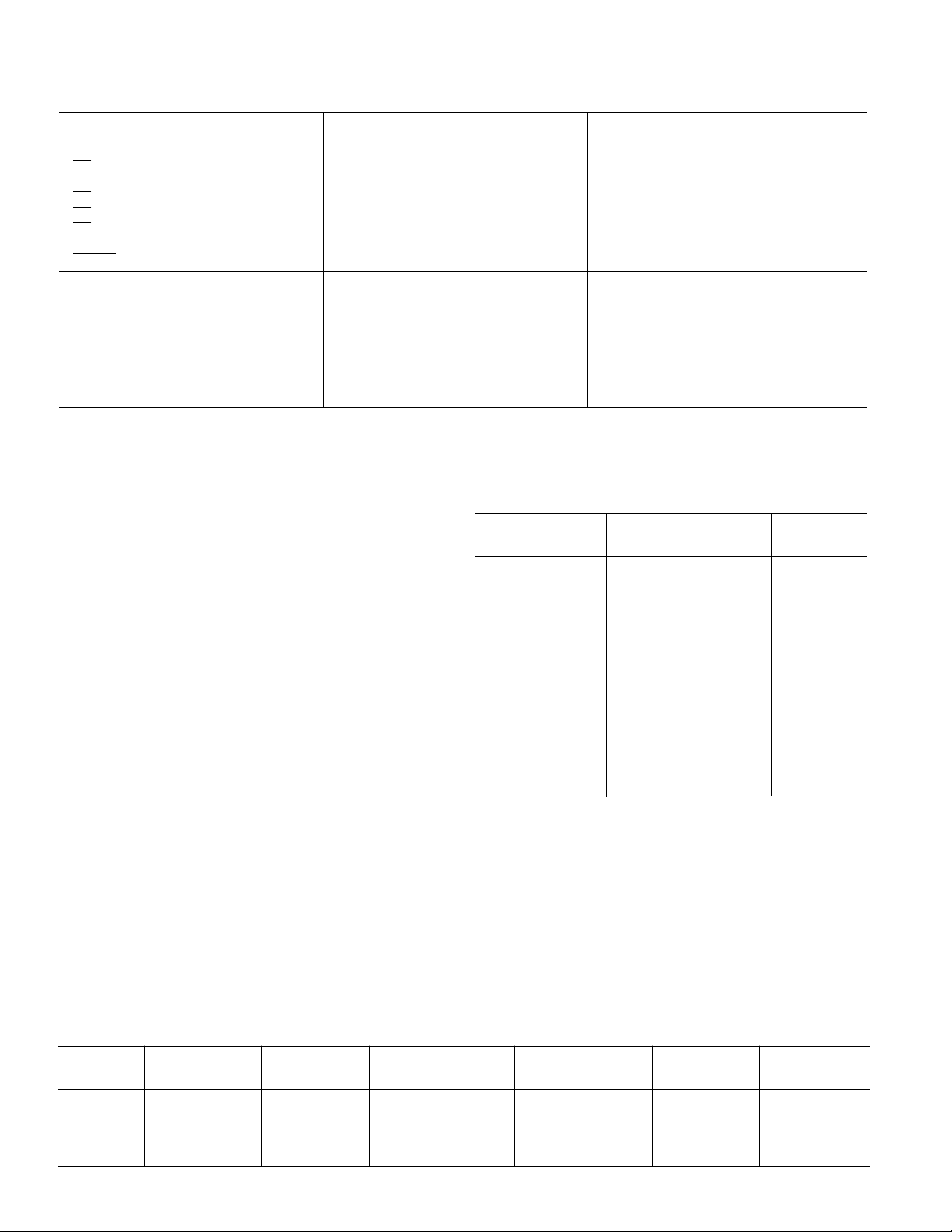

Supervisory Circuits

FUNCTIONAL BLOCK DIAGRAM

BATT ON

1

4.65V

CC

CHIP ENABLE

OUTPUT

CONTROL

IN

RESET &

WATCHDOG

TIMEBASE

WATCHDOG

TRANSITION DETECTOR

1.25V

1

VOLTAGE DETECTOR = 4.4V (ADM693A/ADM800M)

RESET &

GENERATOR

WATCHDOG

TIMER

ADM691A/ADM693A

ADM800L/ADM800M

LOW LINE

V

OUT

CE

OUT

RESET

RESET

WATCHDOG

OUTPUT (WDO)

POWER FAIL

OUTPUT (PFO

)

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

Figure 1. Typical Application

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1996

ADM691A/ADM693A/ADM800L/M–SPECIFICATIONS

(VCC = 4.75 V to 5.5 V (ADM691A, ADM800L) 4.5 V to 5.5 V (ADM693A, ADM800M) V

Parameter Min Typ Max Unit Test Conditions/Comments

BATTERY BACKUP SWITCHING

, V

V

CC

V

OUT

V

CC

V

OUT

V

BATT

Supply Current (Excludes I

Supply Current in B. Backup (Excludes I

Battery Standby Current 5.5 V > V

(+ = Discharge, – = Charge) –0.1 +0.02 µA(V

Battery Switchover Threshold V

V

CC–VBATT

Battery Switchover Hysteresis 60 mV

BATT ON Output Voltage Low 0.1 0.4 V I

BATT ON Output Short Circuit Current 60 mA Sink Current

RESET AND WATCHDOG TIMER

Reset Voltage Threshold

ADM691A, ADM800L 4.5 4.65 4.75 V

ADM693A, ADM800M 4.25 4.40 4.50 V

ADM800L, V

ADM800M, V

Reset Threshold Hysteresis 15 mV

V

CC

LOW LINE to RESET Delay 800 ns

Reset Timeout Period Internal Oscillator 140 200 280 ms Power Up

Reset Timeout Period External Clock 2048 Cycles Power Up

Watchdog Timeout Period, Internal Oscillator 1.0 1.6 2.25 s Long Period

Watchdog Timeout Period, External Clock 4096 Cycles Long Period

Minimum WDI Input Pulse Width 100 ns V

RESET Output Voltage 0.004 0.3 V I

RESET Output Short Circuit Current 7 20 mA

RESET Output Voltage Low 0.1 0.4 V I

LOW LINE Output Voltage 0.4 V I

LOW LINE Short Circuit Source Current 1 15 100 µA

WDO Output Voltage 0.4 V I

WDO Short Circuit Source Current 3 10 mA

WDI Input Threshold

Logic Low 0.8 V

Logic High 0.75 × V

WDI Input Current –50 –10 µA WDI = 0 V

POWER FAIL DETECTOR

PFI Input Threshold ADM69xA 1.2 1.25 1.3 V V

PFI Input Threshold ADM800L/M 1.225 1.25 1.275 V V

PFI Input Current ±0.01 ±25 nA

PFO Output Voltage 0.4 V I

PFO Short Circuit Source Current 1 15 100 µA

PFI to PFO Delay 25 µsV

Operating Voltage Range 0 5.5 V

BATT

Output Voltage VCC – 0.05 VCC – 0.02 V I

– 0.3 VCC – 0.2 V I

V

to V

Output Resistance 0.8 1.2 Ω VCC = 4.5 V

OUT

in Battery Backup Mode V

to V

Output Resistance 12 Ω V

OUT

) 70 100 µAVCC > (V

OUT

) 0.04 1 µAVCC < (V

OUT

CC

– 0.3 V V

BATT

– 0.25 V V

V

BATT

– 0.15 V V

V

BATT

–1.0 +0.02 µA(V

BATT

V

BATT

0.7 1.5 V I

1 15 100 µA Source Current

Falling 4.55 4.70 V TA = +25°C

CC

Falling 4.3 4.45 V TA = +25°C

CC

to RESET Delay 80 µs Power Down

70 100 140 ms Short Period

1024 Cycles Short Period

0.1 0.4 V I

3.5 V I

3.5 V I

3.5 V I

CC

20 50 µA WDI = V

3.5 I

60 µsV

= +2.8 V, TA = T

BATT

20 Ω V

25 Ω V

MIN

to T

unless otherwise noted)

MAX

= 25 mA

OUT

= 250 mA

OUT

= 4.5 V, I

BATT

= 2.8 V, I

BATT

= 2.0 V, I

BATT

= 4.5 V

BATT

= 2.8 V

BATT

= 2.0 V

BATT

BATT

BATT

CC

+0.2 V) < V

BATT

+0.2 V) < V

BATT

+ 0.03 V Power Up

– 0.03 V Power Down

= 3.2 mA

SINK

= 25 mA

SINK

= 0.4, VIH = 0.75 × V

IL

= 50 µ A, VCC = 1 V, V

SINK

= 3.2 mA, VCC = 4.25 V

SINK

= 1.6 mA, VCC = 5 V

SOURCE

= 3.2 mA

SINK

= 3.2 mA, VCC = 4.25 V

SINK

= 1 µA, VCC = 5 V

SOURCE

= 3.2 mA, VCC = 4.25 V

SINK

= 500 µA, VCC = 5 V

SOURCE

V

OUT

= 5 V

CC

= 5 V

CC

= 3.2 mA

SINK

= 1 µA

SOURCE

= –20 mV

IN

= 20 mV

IN

= 20 mA

OUT

= 10 mA

OUT

= 5 mA

OUT

– 1 V)

– 1.2 V), V

> V

BATT

+ 0.2 V

CC

CC

= 2.8 V

BATT

, TA = +25°C

CC

BATT

= 0 V

–2–

REV. 0

ADM691A/ADM693A/ADM800L/M

Parameter Min Typ Max Units Test Conditions/Comments

CHIP ENABLE GATING

CE

Leakage Current ±0.005 ±1 µA Disable Mode

IN

CEIN to CE

CEIN to CE

CE

OUT

CE

OUT

RESET to CE

OSCILLATOR

OSC IN Input Current 0.1 ±5 µA OSC SEL = 0 V

OSC In Input Pullup Current 10 100 µA OSC SEL = V

OSC SEL Input Pullup Current 10 100 µA OSC SEL = 0 V

OSC IN Frequency Range 500 kHz OSC SEL = 0 V

OSC IN Threshold Voltage V

OSC IN Frequency with Ext Capacitor 100 kHz OSC SEL = 0 V, C

NOTES

1

Either VCC or V

Specifications subject to change without notice.

Resistance 40 150 Ω Enable Mode

OUT

Propagation Delay 6 10 ns RIN = 50 Ω, C

OUT

LOAD

Short-Circuit Current 0.1 0.75 2.0 mA Disable Mode, CE

Output Voltage 3.5 V VCC = 5 V, I

Propagation Delay 12 µs Power Down

OUT

– 0.4 V

OUT

– 0.6 V V

OUT

3.65 2.00 V V

can be 0 V if the other > +2.0 V.

BATT

2.7 V V

= 0 V, V

CC

IH

IL

= –100 µA

OUT

BATT

OUT

= 50 pF

= 0 V

OUT

= 2.8 V, I

or Floating

= 47 pF

OSC

OUT

= 1 µ A

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C unless otherwise noted)

VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

V

All Other Inputs . . . . . . . . . . . . . . . . . –0.3 V to V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

BATT

OUT

+ 0.5 V

Input Current

V

(Peak) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000 mA

CC

V

(Continuous) . . . . . . . . . . . . . . . . . . . . . . . . . . . 250 mA

CC

V

(Peak) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250 mA

BATT

V

(Continuous) . . . . . . . . . . . . . . . . . . . . . . . . . . 25 mA

BATT

GND, BATT ON . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100 mA

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . . 25 mA

Power Dissipation, N-16 DIP . . . . . . . . . . . . . . . . . . 842 mW

θ

Thermal Impedance . . . . . . . . . . . . . . . . . . . . .135°C/W

ϑA

Power Dissipation, R-16 Narrow SOIC . . . . . . . . . . . 700 mW

θ

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . .110°W

JA

Power Dissipation, R-16 Wide SOIC . . . . . . . . . . . . . 762 mW

θ

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 110°C/W

JA

Power Dissipation, RU-16 TSSOP . . . . . . . . . . . . . . 500 mW

θ

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 158°C/W

JA

Operating Temperature Range

Industrial (A Version) . . . . . . . . . . . . . . . . –40°C to +85°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . +300°C

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . . 215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

*Stresses above those listed under “Absolute Maximum Ratings” may cause perma-

nent damage to the device. This is a stress rating only and functional operation of

the device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum ratings

for extended periods of time may affect device reliability.

ORDERING GUIDE

Temperature Package

Model Range Option

ADM691AAN –40°C to +85°C N-16

ADM691AARN –40°C to +85°C R-16N

ADM691AARW –40°C to +85°C R-16W

ADM691AARU –40°C to +85°C RU-16

ADM693AAN –40°C to +85°C N-16

ADM693AARN –40°C to +85°C R-16N

ADM693AARW –40°C to +85°C R-16W

ADM800LAN –40°C to +85°C N-16

ADM800LARN –40°C to +85°C R-16N

ADM800LARW –40°C to +85°C R-16W

ADM800MAN –40°C to +85°C N-16

ADM800MARN –40°C to +85°C R-16N

ADM800MARW –40°C to +85°C R-16W

Table I. Product Selection Table

Power On Low V

CC

Watchdog Battery Backup Base Drive Chip Enable

Part No. Reset Time Threshold Timeout Switching Ext PNP Signals

ADM691A 200 ms or Adj. 4.65 V ± 3% 100 ms, 1.6 s, Adj. Yes Yes Yes

ADM693A 200 ms or Adj. 4.4 V ± 3% 100 ms, 1.6 s, Adj. Yes Yes Yes

ADM800M 200 ms or Adj. 4.4 V ± 2% 100 ms, 1.6 s, Adj. Yes Yes Yes

ADM800L 200 ms or Adj. 4.65 V ± 2% 100 ms, 1.6 s, Adj. Yes Yes Yes

REV. 0

–3–

ADM691A/ADM693A/ADM800L/M

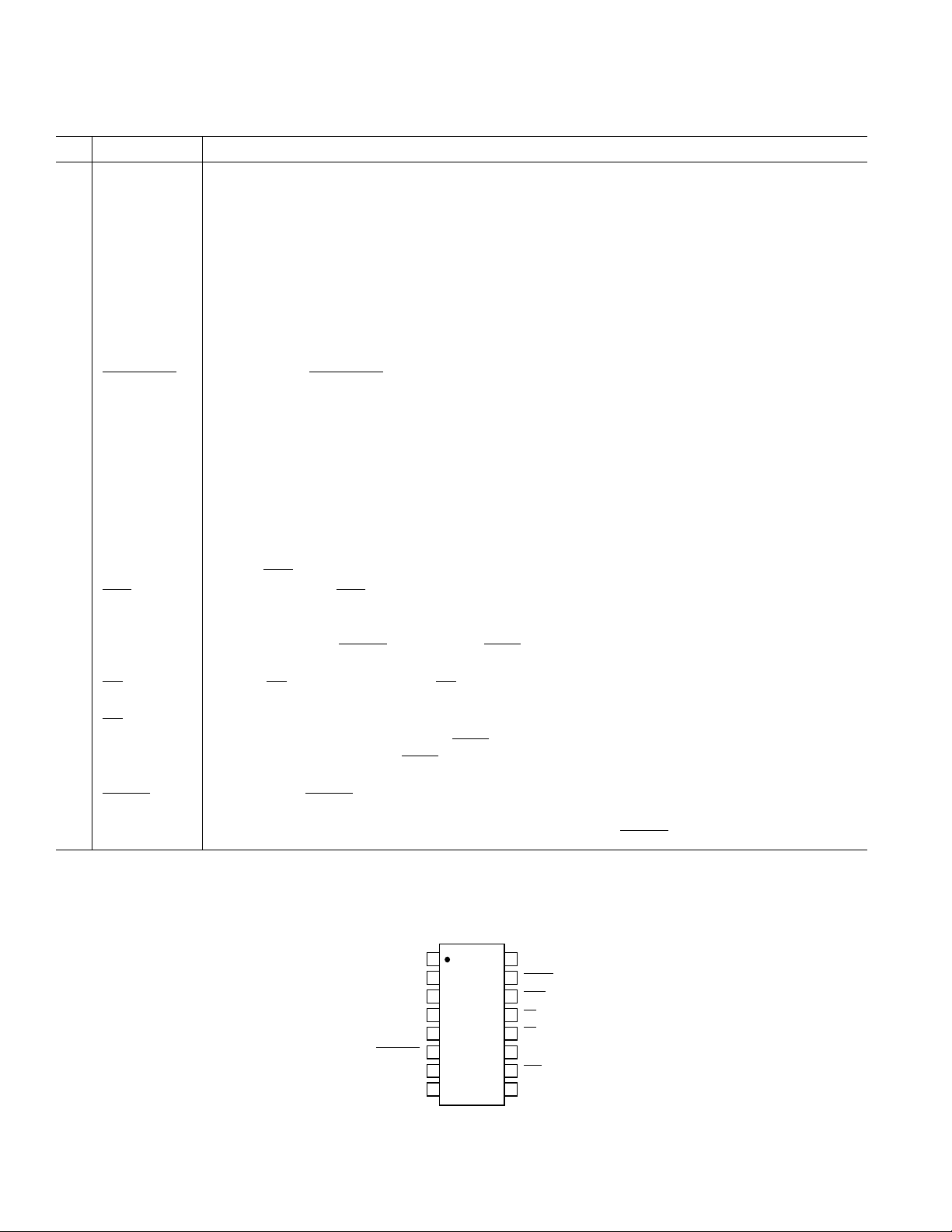

Pin Mnemonic Function

PIN DESCRIPTIONS

1V

BATT

Backup Battery Input. Connect to external battery or capacitor. Connect to ground if a backup battery is

not used.

2V

3V

OUT

CC

Output Voltage, VCC or V

tial. When V

When V

V

if a backup battery is not being used.

CC

is higher than V

CC

is lower than V

CC

is internally switched to V

BATT

BATT

and below the reset threshold, V

BATT

Power Supply Input; +5 V.

depending on which is at the highest poten-

OUT

and is also higher than the reset threshold, VCC is switched to V

is switched to V

BATT

. Connect V

OUT

OUT

OUT

.

to

4 GND 0 V. Ground reference for all signals.

5 BATT ON Logic Output. BATT ON goes high when V

V

is internally switched to VCC. The output may also be used to drive the base (via a resistor) of an ex-

OUT

ternal PNP transistor to increase the output current above the 250 mA rating of V

6

7 OSC

LOW LINE Logic Output. LOW LINE goes low when VCC falls below the reset threshold. It returns high as soon as

V

rises above the reset threshold.

CC

IN Oscillator Logic Input. With OSC SEL high or floating, the internal oscillator is enabled and sets the reset

delay and the watchdog timeout period. Connecting OSC

is internally switched to the V

OUT

IN low selects 100 ms while leaving it floating

input. It goes low when

BATT

.

OUT

selects 1.6 sec. With OSC SEL low, OSC IN can be driven by an external clock signal or an external capacitor can be connected between OSC IN and GND. This sets both the reset active pulse timing and the

watchdog timeout period. (See Table II and Figure 4.)

8 OSC SEL Logic Oscillator Select Input. When OSC SEL is unconnected (floating) or driven high, the internal oscil-

lator sets the reset active time and watchdog timeout period. When OSC SEL is low, the external oscillator

input, OSC

IN, is enabled. OSC SEL has a 10 µA internal pullup.

9 PFI Power Fail Input. PFI is the noninverting input to the Power Fail Comparator. When PFI is less than

10

1.25 V,

PFO Power Fail Output. PFO is the output of the Power Fail Comparator. It goes low when PFI is less than

PFO goes low. Connect PFI to GND or V

OUT

when not used.

1.25 V.

11 WDI Watchdog Input. WDI is a three level input. If WDI remains either high or low for longer than the watch-

dog timeout period,

RESET pulses low and WDO goes low. The timer resets with each transition on the

WDI line. The Watchdog Timer may be disabled if WDI is left floating or is driven to midsupply.

12

13

14 WDO Logic Output. The Watchdog Output,

CE

CE

OUT

IN

Output. CE

reset is asserted, CE

Chip Enable Input. The input to the CE gating circuit. Connect to GND or V

goes low only when CEIN is low and VCC is above the reset threshold. If CEIN is low when

OUT

will remain low for 15 µs or until CE

OUT

goes high, whichever occurs first.

IN

if not used.

OUT

WDO, goes low if WDI remains either high or low for longer than

the Watchdog timeout period.

WDO is set high by the next transition at WDI. WDO remains high if WDI

is unconnected.

15

RESET Logic Output. RESET goes low if VCC falls below the Reset Threshold. It remains low for 200 ms typ after

V

goes above the reset threshold.

CC

16 RESET Logic Output. RESET is an open-drain output. It is the inverse of RESET.

PIN CONFIGURATIONS

V

BATT

V

OUT

V

GND

BATT ON

LOW LINE

OSC IN

OSC SEL

CC

1

2

3

ADM691A

ADM693A

4

ADM800L

5

ADM800M

6

TOP VIEW

(Not to Scale)

7

8

16

15

14

13

12

11

10

9

RESET

RESET

WDO

CE

CE

WDI

PFO

PFI

–4–

IN

OUT

REV. 0

Loading...

Loading...