Analog Devices ADM6821 25 prb Datasheet

Low Voltage Supervisory Circuits with

Watchdog and Manual Reset in 5-Lead SOT-23

Preliminary Technical Data

FEATURES

Precision low voltage monitoring down to 1.8 V

9 reset threshold options:

1.58 V to 4.63 V

140 ms (min) reset timeout

Watchdog timer with 1.6s timeout

Manual reset input

Reset output stages

Push-pull active-low

Open-drain active-low

Push-pull active-high

Low power consumption (3 µA)

Guaranteed reset output valid to V

Power supply glitch immunity

Specified from –40°C to +125°C

5-lead SOT-23 package

APPLICATIONS

Microprocessor systems

Computers

Controllers

Intelligent instruments

Portable equipment

GENERAL DESCRIPTION

The ADM6821–ADM6825 are supervisory circuits that monitor

power supply voltage levels and code execution integrity in

microprocessor-based systems. As well as providing power on

reset signals, an on-chip watchdog timer can reset the

microprocessor if it fails to strobe within a preset timeout

period. A reset signal can also be asserted by means of an

external push-button, through a manual reset input. The parts

feature different combinations of watchdog input, manual reset

Table 1. Selection Table

Part No. Watchdog Timer Manual Reset

ADM6821 Yes Yes - Push-Pull

ADM6822 Yes Yes Open-Drain -

ADM6823 Yes Yes Push-Pull ADM6824 Yes - Push-Pull Push-Pull

ADM6825 - Yes Push-Pull Push-Pull

= 1 V

CC

ADM6821–ADM6825

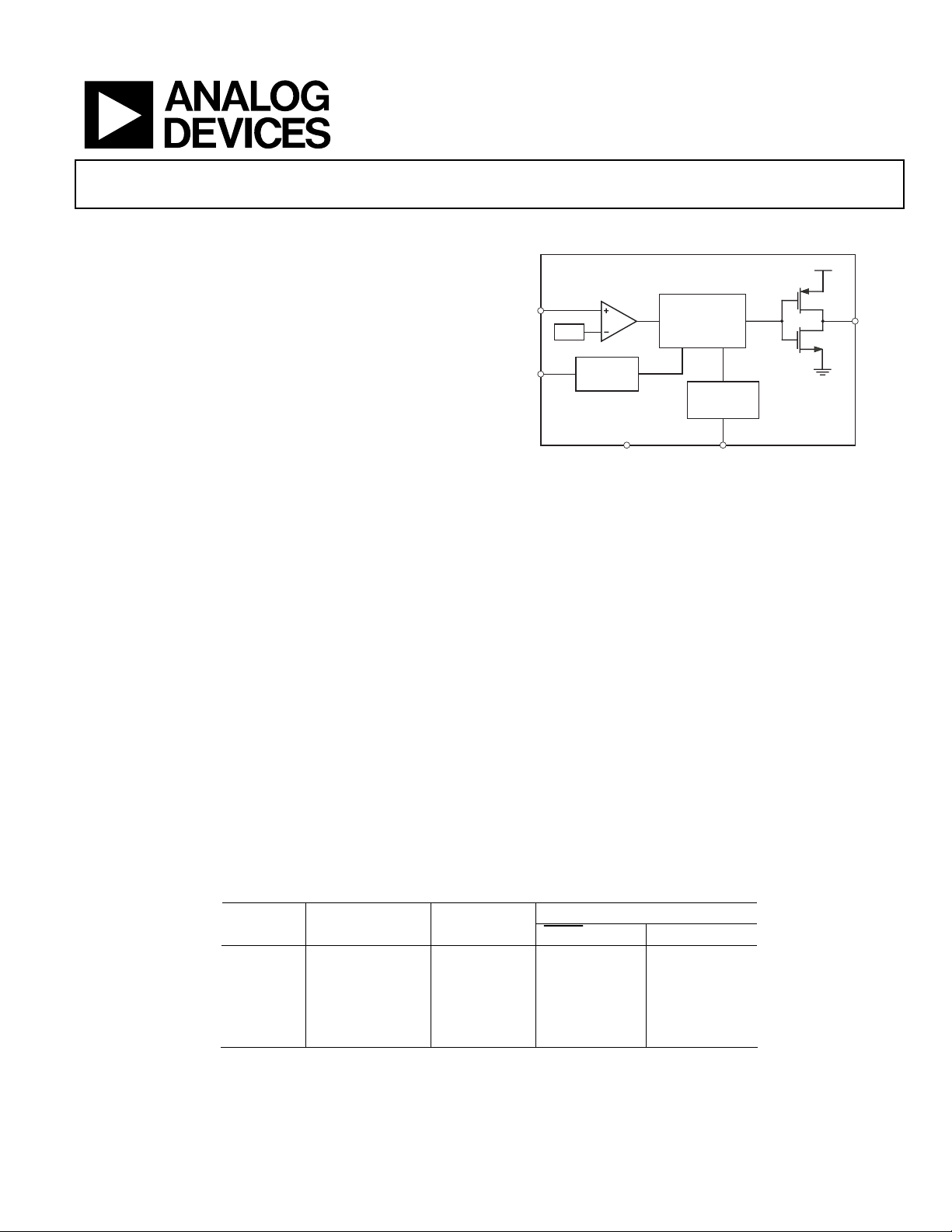

FUNCTIONAL BLOCK DIAGRAM

V

ADM6823

V

MR

CC

V

REF

DEBOUNCE

GND

RESET

GENERATOR

WATCHDOG

DETECTOR

WDI

Figure 1.

input and output stage configuration, as shown in table 1.

Each part is available in a choice of nine reset threshold options

ranging from 1.58 V to 4.63 V. The reset and watchdog timeout

periods are fixed at 140 ms (min) and 1.6s (typ), respectively.

The ADM6821–ADM6825 are available in 5-lead SOT-23

packages and typically consume only 3 µA, making them

suitable for use in low power portable applications.

Output Stage

RESET

RESET

CC

RESET

Rev. PrB

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

ADM6821–ADM6825 Preliminary Technical Data

TABLE OF CONTENTS

Specifications..................................................................................... 3

Watchdog Input.............................................................................9

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Pin Configurations And Functional Descriptions ....................... 6

Typical Performance Characteristics ............................................. 7

Circuit Description........................................................................... 9

Reset Output ................................................................................. 9

Manual Reset Input ...................................................................... 9

REVISION HISTORY

Revision 0: Initial Version

Application Information................................................................ 10

Watchdog Input Current........................................................... 10

Negative-Going V

Ensuring Reset Valid to V

Watchdog Software Considerations......................................... 10

Outline Dimensions....................................................................... 11

ORDERING GUIDE.................................................................. 11

Transients ................................................ 10

CC

= 0 V............................................ 10

CC

Rev. PrB | Page 2 of 11

Preliminary Technical Data ADM6821–ADM6825

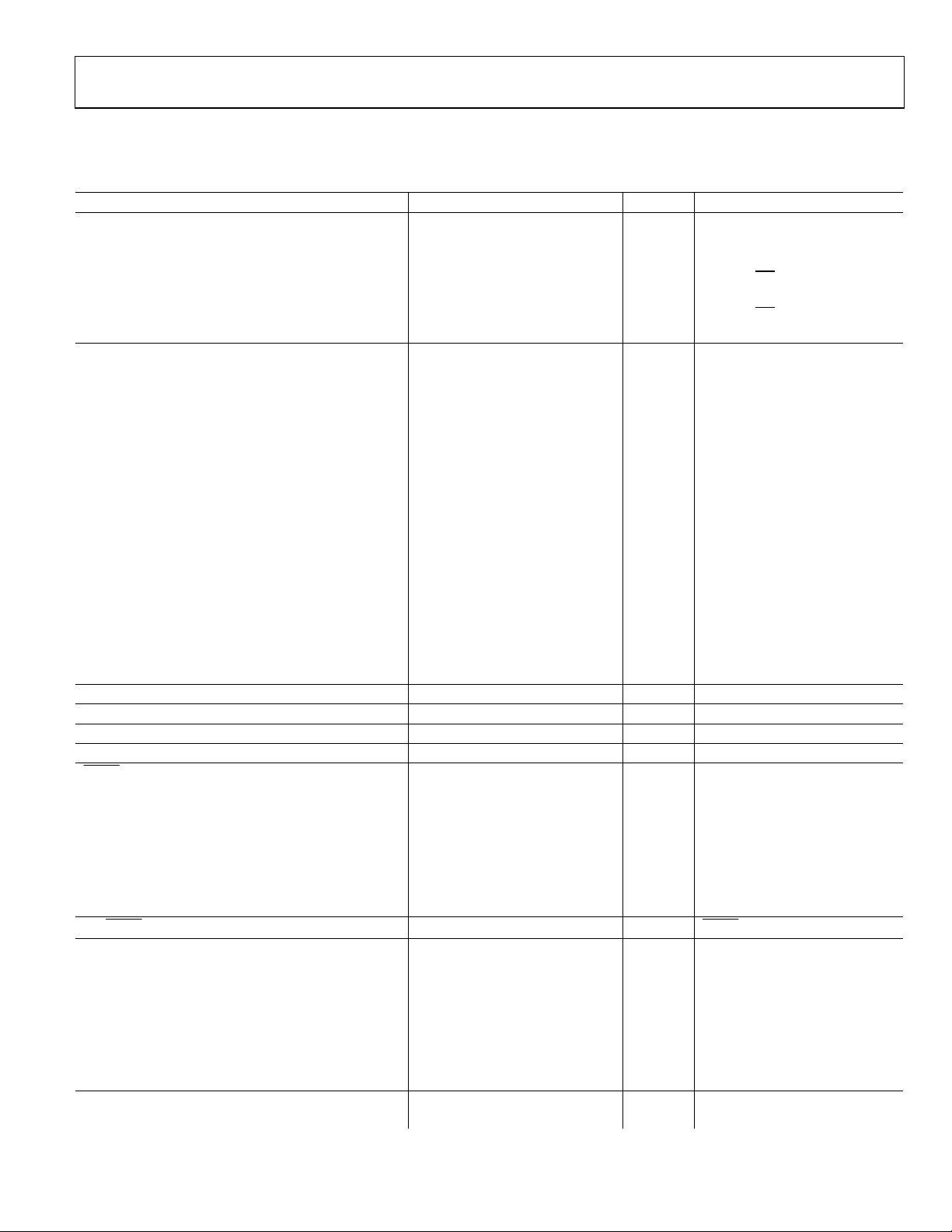

SPECIFICATIONS

Table 1. VCC = 4. 5 V to 5.5 V for ADM682_L/M, VCC = 2.7 V to 3.6 V for ADM682_T/S/R, VCC = 2.1 V to 2.75 V for

ADM682_Z/Y, V

Parameter Min Typ Max Unit Test Conditions/Comments

SUPPLY

VCC Operating Voltage Range 1 5.5 V TA = 0°C to +85°C

1.2 V TA = -40°C to 125°C

Supply Current 10 20 µA

7 16 µA

RESET THRESHOLD VOLTAGE

ADM682_L

V

ADM682_M

V

ADM682_T

V

ADM682_S

V

ADM682_R

V

ADM682_Z

V

ADM682_Y

V

ADM682_W

ADM682_V

RESET THRESHOLD TEMPERATURE COEFFICIENT 60 ppm/°C

RESET THRESHOLD HYSTERESIS 10 mV

RESET TIMEOUT PERIOD 140 200 280 ms

VCC TO RESET DELAY 40 µs VTH − VCC = 100mV

RESET

Output Voltage

VOL 0.3 V V

0.3 V V

0.3 V VCC >=2.55V, I

0.4 V VCC>=4.25V, I

VOH 0.8 × VCC V V

0.8 × VCC V V

0.8 × VCC V V

RESET

Output leakage Current

RESET Output Voltage

VOL 0.3 V V

0.3 V V

0.4 V VCC >=4.75V, I

VOH 0.8 × VCC V V

0.8 × VCC V V

0.8 × VCC V V

0.8 × VCC V V

WATCHDOG INPUT (ADM6821/2/3/4)

Watchdog Timeout Period 1.12 1.6 2.40 s

= 1.53 V to 2.0 V for ADM682_W/V, TA = –40°C to +125°C, unless otherwise noted

CC

4.50 4.63 4.75 V

4.25 4.38 4.50 V

3.00 3.08 3.15 V

2.85 2.93 3.00 V

2.55 2.63 2.70 V

2.25 2.32 2.38 V

2.13 2.19 2.25 V

1.62 1.67 1.71 V

1.52 1.58 1.62 V

1 µA

WDI and MR unconnected,

V

=5.5V

CC

WDI and MR unconnected,

V

=3.6V

CC

>=1V, I

CC

>=1.2V, I

CC

>=1.8V, I

CC

>=3.15V, I

CC

>=4.75V, I

CC

RESET

>=1.8V, I

CC

>=3.15V, I

CC

> = 1V, I

CC

>=1.5V, I

CC

>=2.55V, I

CC

>=4.25V, I

CC

= 50µA

SINK

= 100µA

SINK

= 1.2mA

SINK

= 3.2mA

SINK

= 200µA

SOURCE

SOURCE

SOURCE

not asserted

= 500µA

SINK

= 1.2mA

SINK

= 3.2mA

SINK

= 1µA

SOURCE

= 100µA

SOURCE

SOURCE

SOURCE

= 500µA

= 800µA

= 500µA

= 800µA

Rev. PrB | Page 3 of 11

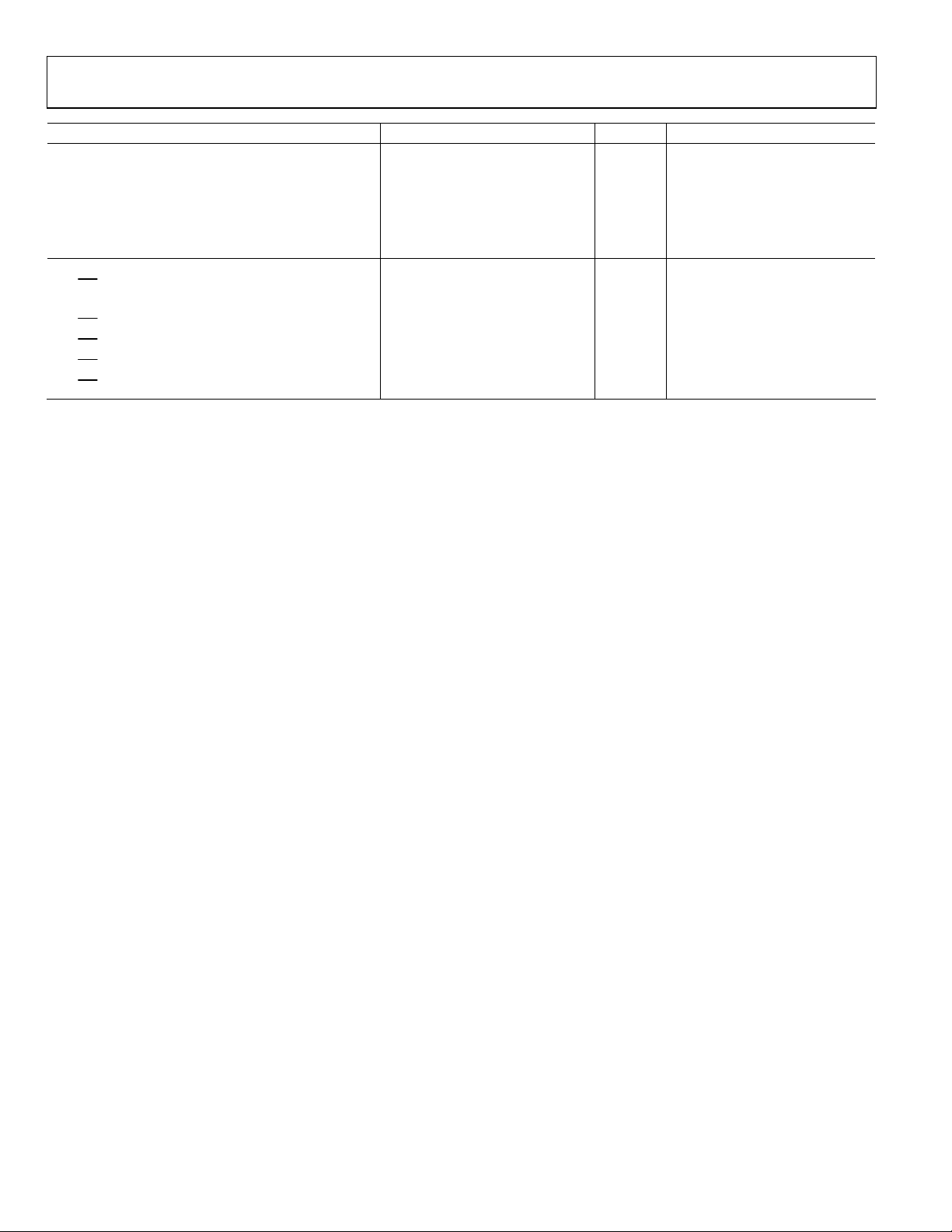

ADM6821–ADM6825 Preliminary Technical Data

Parameter Min Typ Max Unit Test Conditions/Comments

WDI Pulse Width 50 ns

WDI Input Threshold

VIL 0.3 × VCC V

VIH 0.7 × VCC V

WDI Input Current 120 160 µA V

−20 −15 µA V

MANUAL RESET INPUT (ADM6821/2/3/5)

MR

Input Threshold

0.3 × V

V

CC

0.7 × VCC V

MR

Input Pulse Width

MR

Glitch Rejection

MR

Pull-up Resistance

MR

to Reset Delay

1 µs

100 ns

25 52 75

k⍀

200 ns

V

= 0.4 V, V

IL

= VCC, time average

WDI

= 0, time average

WDI

= 0.8×V

IH

CC

Rev. PrB | Page 4 of 11

Loading...

Loading...