www.BDTIC.com/ADI

Triple Processor Supervisors

FEATURES

Triple supervisory circuits

Supply voltage range of 2.0 V to 5.5 V

Pretrimmed threshold options: 1.8 V, 2.5 V, 3.3 V, and 5 V

Adjustable 0.6 V and 1.25 V voltage references

Maximum supply current of 40 μA

140 ms (minimum) reset timeout

RESET valid from V

Push-pull RESET and

8-lead, narrow body SOIC package

Temperature range: −40°C to +85°C

APPLICATIONS

Supervising DSPs/microcontrollers

Industrial and portable equipment

Wireless systems

Notebook/desktop computers

GENERAL DESCRIPTION

The ADM13307 is a triple voltage supervisor designed to

monitor up to three voltage levels in DSP and microprocessorbased systems.

There are five models available, all of which feature a combination of internally pretrimmed undervoltage threshold options

for monitoring 1.8 V, 2.5 V, 3.3 V, and 5 V supplies. There are

also two adjustable input options with undervoltage thresholds of

either 0.6 V or 1.25 V.

The ADM13307-18, ADM13307-25, and ADM13307-33

models have two internally fixed thresholds and one externally

programmable threshold via a resistor string. The ADM13307-4

and ADM13307-5 offer one internally fixed threshold and two

externally programmable thresholds. See the Ordering Guide

for a list of all available options.

During power-up,

exceeds 1.1 V. The device then monitors the SENSEv input

pins and holds the

pins remain below the rising threshold voltage, V

Once the supplies monitored at the SENSEv inputs rise above

their associated thresholds, the reset signal remains low for the

reset timeout period before deasserting. Subsequently, if a voltage monitored by the SENSEv pins falls below its associated

falling input threshold voltage, V

≥ 1.1 V

DD

outputs

RESET

is asserted when the supply voltage

RESET

output low as long as the SENSEv

RESET

, the

RESET

IT−

.

IT+

output asserts.

ADM13307

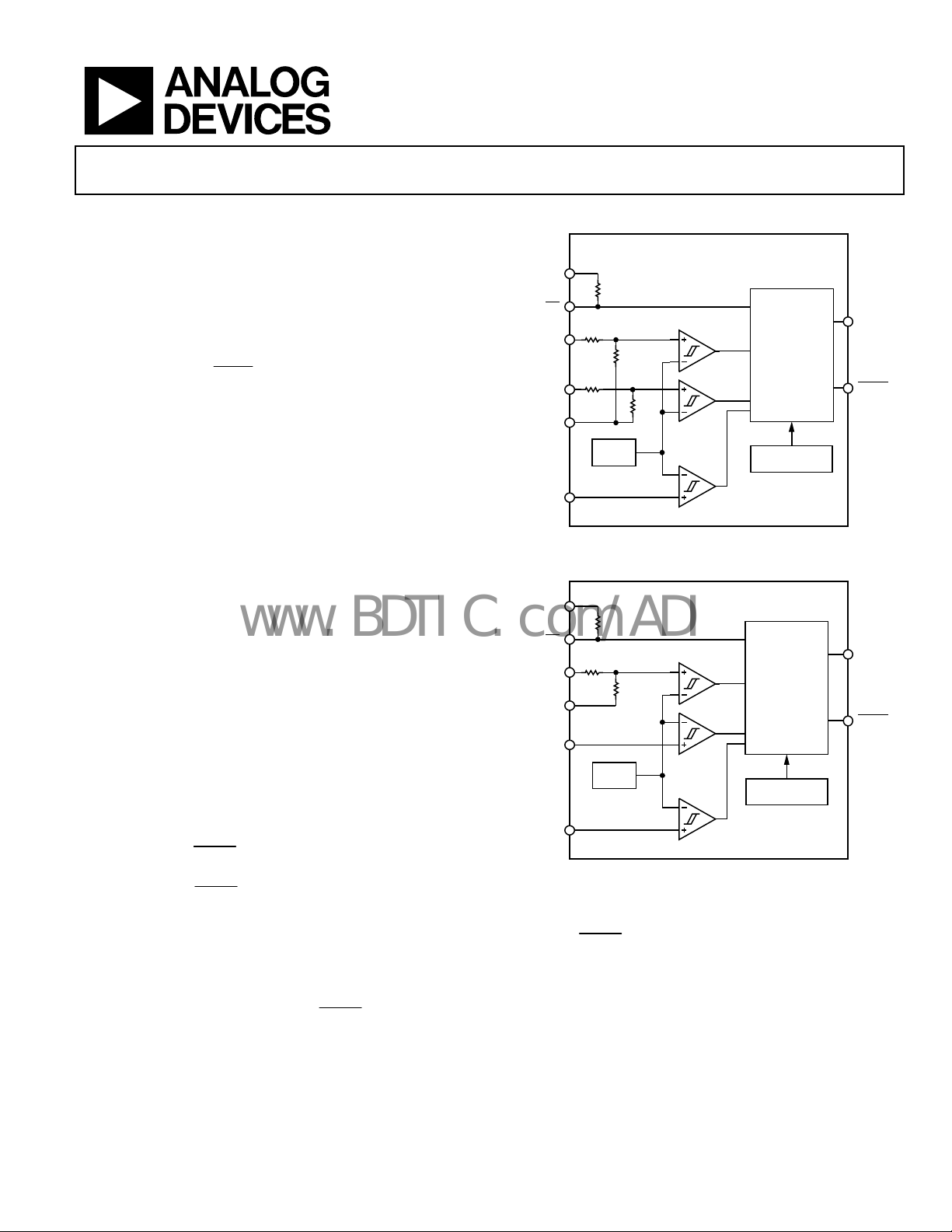

FUNCTIONAL BLOCK DIAGRAMS

ADM13307-18

V

DD

14kΩ

MR

SENSE1

SENSE2

GND

SENSE3

R1

R2

R3

R4

1.25V

Figure 1.

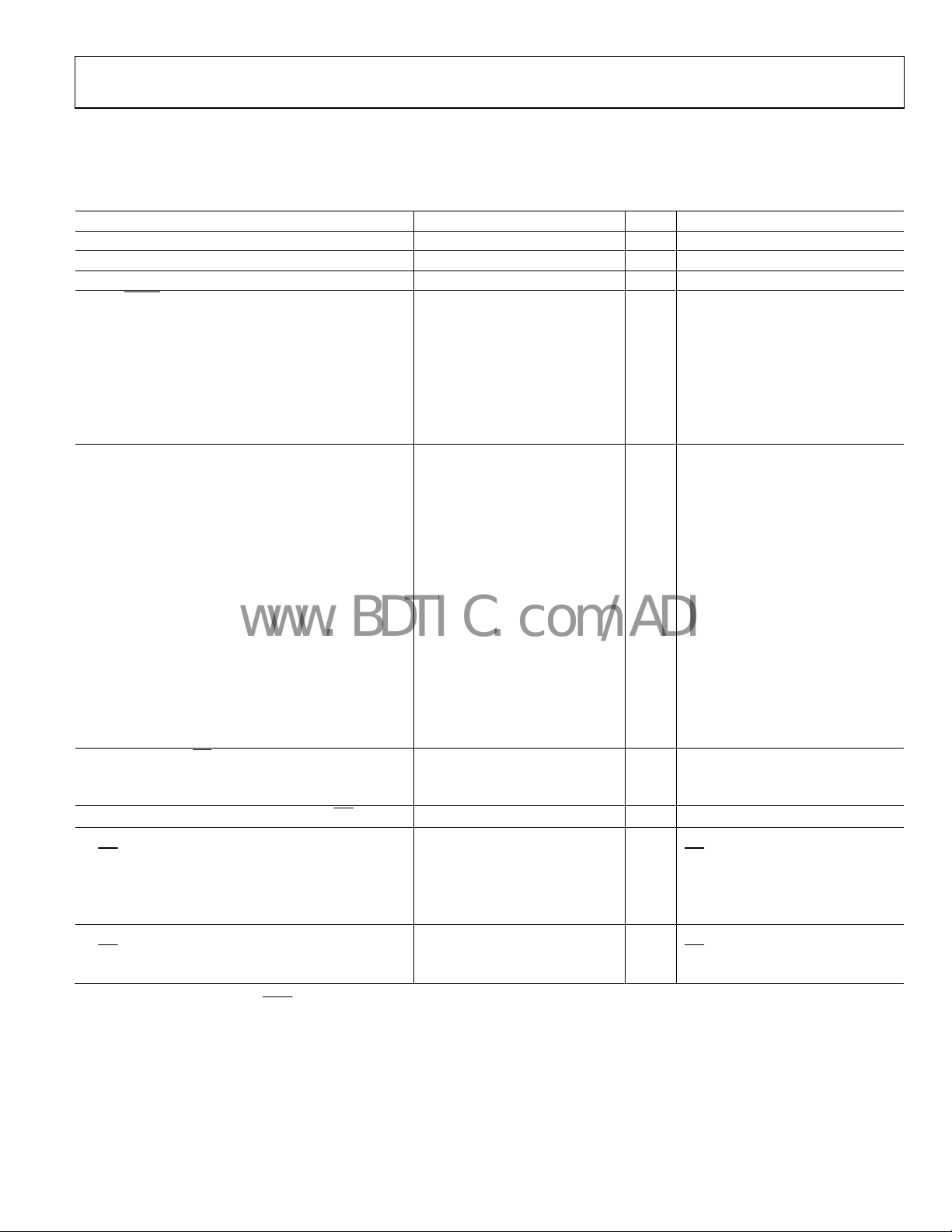

V

DD

14kΩ

MR

SENSE1

GND

SENSE2

SENSE3

R1

R2

0.6V

Figure 2.

The ADM13307 features both an active high RESET and an

active low

RESET

output.

The manual reset input of the ADM13307 can be used to initiate

a reset by means of an external push button or logic signal.

The ADM13307 is available in an 8-lead narrow body SOIC

package. The device operates over the extended industrial

temperature range of −40°C to +85°C.

ADM13307-25

ADM13307-33

RESET

LOGIC + TIMER

OSCIL LATO R

ADM13307-4

ADM13307-5

RESET

LOGIC + TIMER

OSCILLATOR

RESET

RESET

RESET

RESET

06923-002

06923-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

ADM13307

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagrams ............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Timing Requirements .................................................................. 5

Switching Characteristics ............................................................ 5

Functional Truth Table ................................................................ 5

Absolute Maximum Ratings ............................................................ 6

REVISION HISTORY

8/07—Revision 0: Initial Version

Thermal Resistance .......................................................................6

ESD Caution...................................................................................6

Pin Configuration and Function Descriptions ..............................7

Typical Performance Characteristics ..............................................8

Theory of Operation ...................................................................... 10

Input Configuration ................................................................... 10

Reset Output ............................................................................... 10

Manual Reset (MR) .................................................................... 10

Outline Dimensions ....................................................................... 11

Ordering Guide .......................................................................... 11

Rev. 0 | Page 2 of 12

ADM13307

www.BDTIC.com/ADI

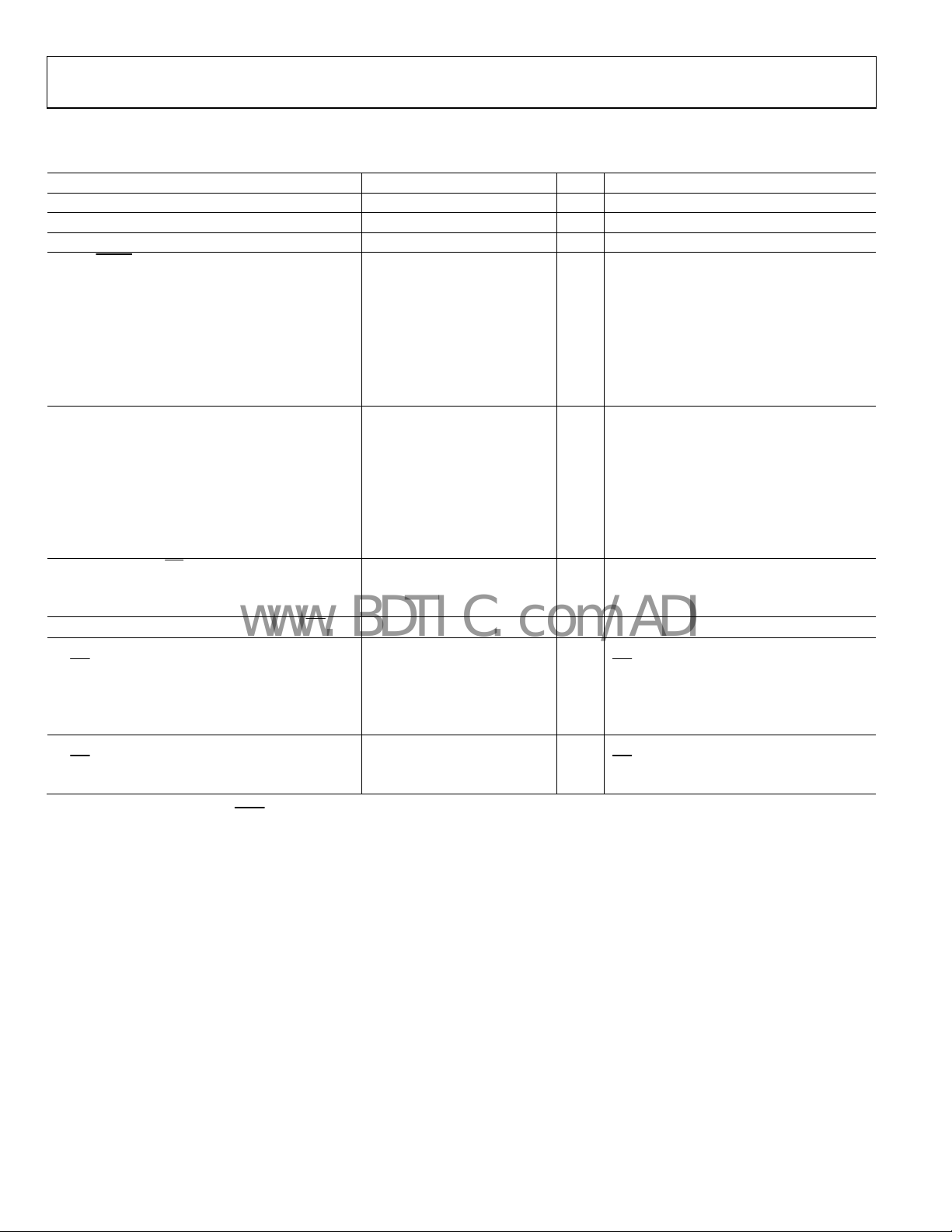

SPECIFICATIONS

VDD = 2.0 V to 5.5 V, −40°C ≤ TA ≤ +85°C, unless otherwise noted.

Table 1. ADM13307-18, ADM13307-25, and ADM13307-33

Parameter Min Typ Max Unit Test Conditions/Comments

OPERATING VOLTAGE RANGE, VDD 2.0 5.5 V

SUPPLY CURRENT, I

INPUT CAPACITANCE, CI 10 pF VI = 0 V to VDD

RESET, RESET Output

High Level Output Voltage, VOH V

V

V

Low Level Output Voltage, VOL 0.2 V IOL = 20 μA

0.4 V IOL = 2 mA, VDD = 3.3 V

0.4 V IOL = 3 mA, VDD = 5.5 V

Power-Up Reset Voltage1 0.4 V IOL = 20 μA, VDD ≥ 1.1 V

SENSE INPUTS

Falling Input Threshold Voltage, V

1.64 1.68 1.72 V TA = 0°C to 85°C

2.20 2.25 2.30 V TA = 0°C to 85°C

2.86 2.93 3.00 V TA = 0°C to 85°C

4.46 4.55 4.64 V TA = 0°C to 85°C

1.22 1.25 1.29 V TA = −40°C to +85°C

1.64 1.68 1.73 V TA = −40°C to +85°C

2.20 2.25 2.32 V TA = −40°C to +85°C

2.86 2.93 3.02 V TA = −40°C to +85°C

4.46 4.55 4.67 V TA = −40°C to +85°C

Hysteresis at SENSEv Inputs, V

15 mV V

20 mV V

30 mV V

40 mV V

INPUT VOLTAGE AT MR

High Level, VIH

Low Level, VIL

INPUT TRANSITION RISE AND FALL RATE AT MR

HIGH LEVEL INPUT CURRENT, I

MR

SENSE1 5 8 μA SENSE1 = VDD = 5.5 V

SENSE2 6 9 μA SENSE2 = VDD = 5.5 V

SENSE3 −25 +25 nA SENSE3 = VDD

LOW LEVEL INPUT CURRENT, IL

MR

SENSEv −25 +25 nA SENSE1, SENSE2, SENSE3 = 0 V

1

The lowest supply voltage at which

40 μA

DD

− 0.2 V IOH = −20 μA

DD

− 0.4 V IOH = −2 mA, VDD = 3.3 V

DD

− 0.4 V IOH = −3 mA, VDD = 5.5 V

DD

1.22 1.25 1.28 V TA = 0°C to 85°C

IT−

10 mV V

HYS

0.7 × V

0.3 × V

V

DD

V

DD

= 1.25 V

IT−

= 1.68 V

IT−

= 2.25 V

IT−

= 2.93 V

IT−

= 4.55 V

IT−

50 ns/V

H

RESET

becomes active. tr, VDD ≥ 15 μs/V.

−130 −180 μA

−430 −600 μA

MR = 0.7 × VDD, VDD = 5.5 V

MR = 0 V, VDD = 5.5 V

Rev. 0 | Page 3 of 12

ADM13307

www.BDTIC.com/ADI

VDD = 2.0 V to 5.5 V, −40°C ≤ TA ≤ +85°C, unless otherwise noted.

Table 2. ADM13307-4 and ADM13307-5

Parameter Min Typ Max Unit Test Conditions/Comments

OPERATING VOLTAGE RANGE, VDD 2.0 5.5 V

SUPPLY CURRENT, I

INPUT CAPACITANCE, CI 10 pF VI = 0 V to VDD

RESET, RESET Output

High Level Output Voltage, VOH V

V

V

Low Level Output Voltage, VOL 0.2 V IOL = 20 μA

0.4 V IOL = 2 mA, VDD = 3.3 V

0.4 V IOL = 3 mA, VDD = 5.5 V

Power-Up Reset Voltage

SENSE INPUTS

Falling Input Threshold Voltage, V

0.5952 0.6 0.6048 V TA = −40°C to +85°C, 2.35 V ≤ VDD ≤ 5.5 V

2.23 2.25 2.29 V TA = −40°C to +85°C

2.90 2.93 2.98 V TA = −40°C to +85°C

Hysteresis at SENSEv Inputs, V

20 mV V

30 mV V

INPUT VOLTAGE AT MR

High Level, V

Low Level, V

INPUT TRANSITION RISE AND FALL RATE AT MR

HIGH LEVEL INPUT CURRENT, IH

MR

SENSE1 5 8 μA SENSE1 = VDD = 5.5 V

SENSE2 −50 +50 nA SENSE2 = VDD = 5.5 V

SENSE3 −25 +25 nA SENSE3 = VDD

LOW LEVEL INPUT CURRENT, IL

MR

SENSEv −25 +25 nA SENSE1, SENSE2, SENSE3 = 0 V

1

The lowest supply voltage at which

40 μA

DD

− 0.2 V IOH = −20 μA

DD

− 0.4 V IOH = −2 mA, VDD = 3.3 V

DD

− 0.4 V IOH = −3 mA, VDD = 5.5 V

DD

1

0.5946 0.6 0.6048 V TA = −40°C to +85°C

IT−

0 mV V

HYS

IH

IL

0.4 V IOL = 20 μA, VDD ≥ 1.1 V

= 0.6 V

IT−

= 2.25 V

IT−

= 2.93 V

IT−

0.7 × VDD V

0.3 × VDD V

50 ns/V

RESET

becomes active. tr, VDD ≥ 15 μs/V.

−130 −180 μA

−430 −600 μA

= 0.7 × VDD, VDD = 5.5 V

MR

= 0 V, VDD = 5.5 V

MR

Rev. 0 | Page 4 of 12

Loading...

Loading...