Hot-Swap Controller and Digital Power

ADM1275

Q

1

GATE

SENSE+

TIMER

TIMER

ADM1275-1

GND

R

SENSE

SENSE–

VCC

V

CP

2V TO 20V

2.95V

TO

20V

VCAP

IOUT

UV

OV

1.0V

1.0V

VOUT

VOUT

12-BIT

ADC

SCL

SDA

ADR

SENSE+

IOUT

LDO

CHARGE

PUMP

TIMEOUT

GPO2/ALERT2

PWRGD

GPO1/ALERT1/CONV

LATCH

TIMER

ON

TIMER

ON

V

CBOS

SS

CURRENT

LIMIT

FLB

ISET

TIMEOUT

CURRENT

LIMIT

CONTROL

REF

SELECT

1.0V

GATE

DRIVE/

LOGIC

LOGIC

AND

PMBus

×50

+

+

–

–

+

–

+

–

08931-001

FEATURES

Controls supply voltages from 2 V to 20 V

370 ns response time to short circuit

Resistor-programmable 5 mV to 25 mV current limit

±1% accurate, 12-bit ADC for current, V

Charge-pumped gate drive for multiple external N-channel FETs

High gate drive voltage to ensure lowest R

Foldback for tighter FET SOA protection

Automatic retry or latch-off on current fault

Programmable current limit timer for SOA

Programmable, multifunction GPOs

Power-good status output

Analog UV and OV protection

ENABLE pin (ADM1275-3 only)

Peak detect registers for current and voltage

PMBus fast mode compliant interface

16-lead QSOP and 20-lead QSOP and LFCSP

APPLICATIONS

Power monitoring and control/power budgeting

Central office equipment

Telecommunication and data communication equipment

PCs/servers

IN/VOUT

DSON

readback

Monitor with PMBus Interface

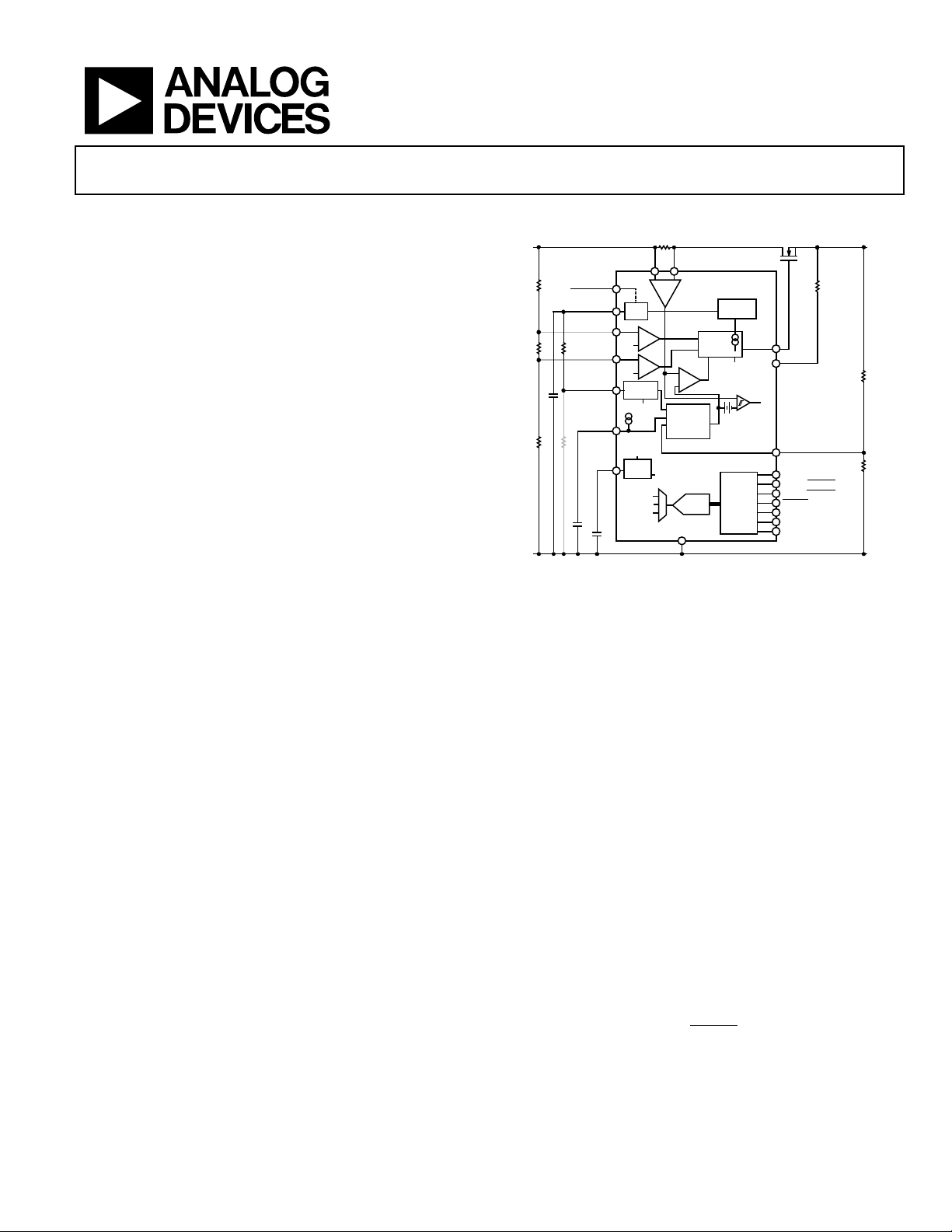

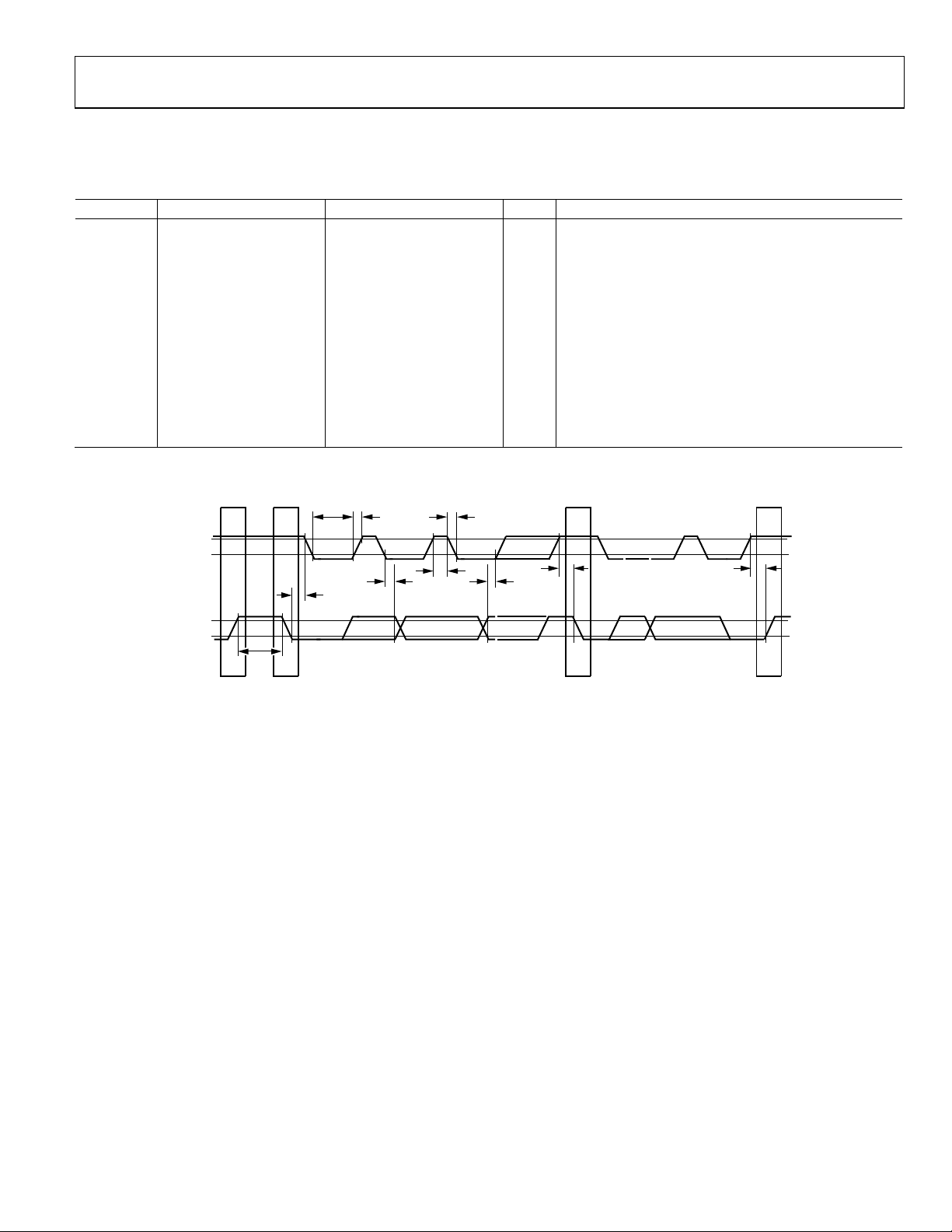

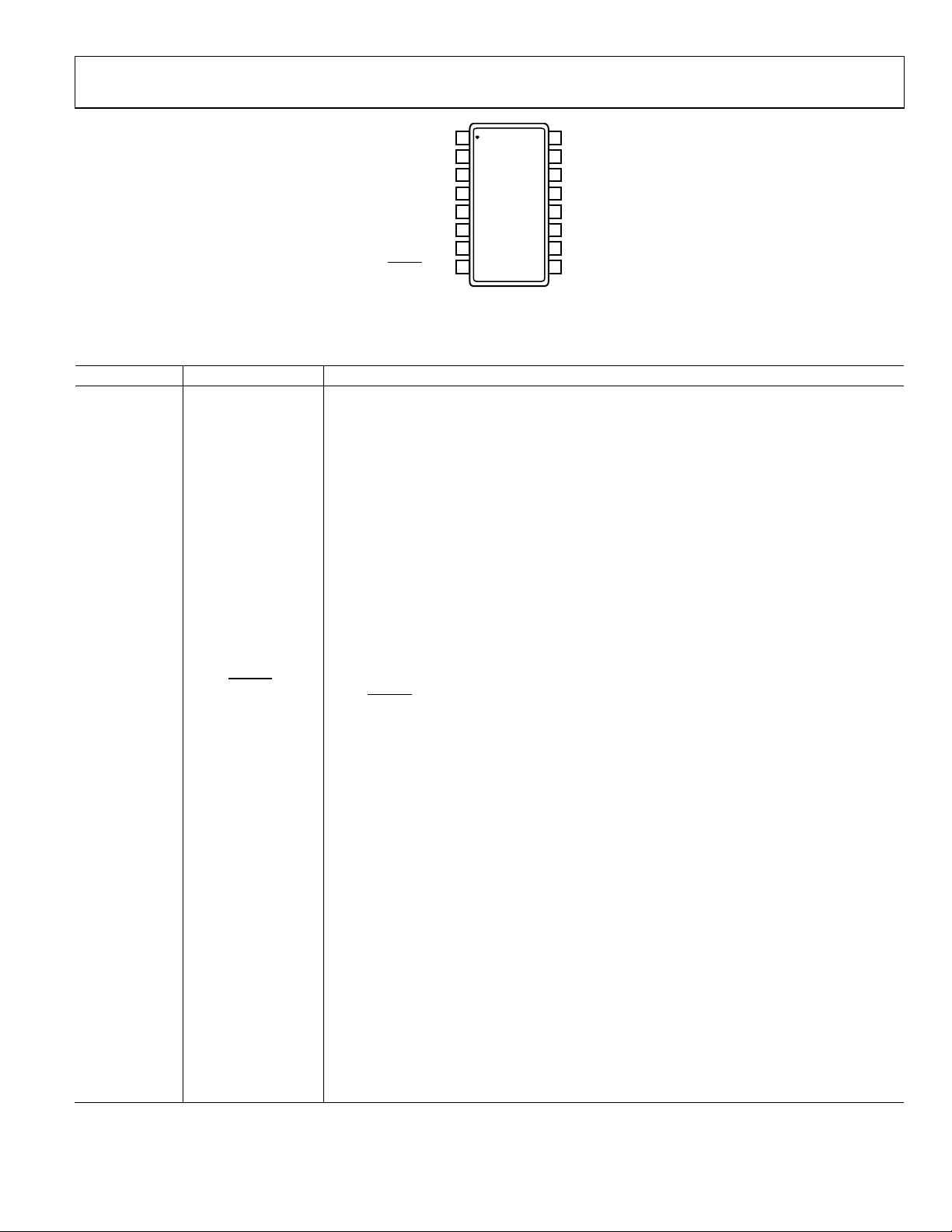

APPLICATIONS DIAGRAM

Figure 1.

GENERAL DESCRIPTION

The ADM1275 is a hot-swap controller that allows a circuit board

to be removed from or inserted into a live backplane. It also features

current and voltage readback via an integrated 12-bit analog-todigital converter (ADC), accessed using a PMBus™ interface.

The load current is measured using an internal current sense

amplifier that measures the voltage across a sense resistor in

the power path via the SENSE+ and SENSE− pins. A default

limit of 20 mV is set, but this limit can be adjusted, if required,

using a resistor divider network from the internal reference

voltage to the ISET pin.

The ADM1275 limits the current through the sense resistor by

controlling the gate voltage of an external N-channel FET in the

power path, via the GATE pin. The sense voltage—and, therefore,

the load current—is maintained below the preset maximum. The

ADM1275 protects the external FET by limiting the time that the

FET remains on while the current is at its maximum value. This

current limit time is set by the choice of capacitor connected to

the TIMER pin. In addition, a foldback resistor network can be

used to actively lower the current limit as the voltage across the

FET is increased. This helps to maintain constant power in the

FET and allows the safe operating area (SOA) to be adhered to

in an effective manner.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

In case of a short-circuit event, a fast internal overcurrent detector responds within 370 ns and signals the gate to shut down. A

1500 mA pull-down device ensures a fast FET response. The

ADM1275 features overvoltage and undervoltage protection,

programmed using external resistor dividers on the UV and OV

pins. A PWRGD signal can be used to detect when the output

supply is valid, using the FLB pin to monitor the output. GPO

pins can be configured as various output signals that can be

asserted when a programmed current or voltage level is reached.

The 12-bit ADC can measure the current in the sense resistor,

as well as the supply voltage on the SENSE+ pin or the output

voltage. A PMBus interface allows a controller to read current

and voltage data from the ADC. Measurements can be initiated

by a PMBus command. Alternatively, the ADC can run continuously, and the user can read the latest conversion data whenever

required. Up to four unique PMBus addresses can be selected,

depending on the way that the ADR pin is connected.

The ADM1275-1 and ADM1275-3 are available in a 20-lead QSOP

and 20-lead LFCSP and have a

for automatic retry or latch-off when an overcurrent fault occurs.

The ADM1275-2 is available in a 16-lead QSOP with latch-off

mode only.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 ©2010–2011 Analog Devices, Inc. All rights reserved.

LATCH

pin that can be configured

www.analog.com

ADM1275

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Applications Diagram ...................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 3

Specifications ..................................................................................... 4

Serial Bus Timing Characteristics .............................................. 7

Absolute Maximum Ratings ............................................................ 8

Thermal Characteristics .............................................................. 8

ESD Caution .................................................................................. 8

Pin Configurations and Function Descriptions ........................... 9

Typical Performance Characteristics ........................................... 14

Functional Block Diagrams ........................................................... 20

Theory of Operation ...................................................................... 21

Powering the ADM1275 ............................................................ 21

Current Sense Inputs .................................................................. 21

Current Limit Reference ............................................................ 22

Setting the Current Limit (ISET).............................................. 22

Soft Start ...................................................................................... 23

Foldback ....................................................................................... 23

Timer ............................................................................................ 24

Hot-Swap Retry Duty Cycle ...................................................... 24

FET Gate Drive Clamps ............................................................. 24

Fast Response to Severe Overcurrent ...................................... 25

Undervoltage and Overvoltage ................................................. 25

ENABLE Input (ADM1275-3 Only) ........................................ 25

Power Good ................................................................................. 25

VOUT Measurement ................................................................. 26

FET Health .................................................................................. 26

Power Monitor ............................................................................ 26

PMBus Interface ............................................................................. 27

Device Addressing ...................................................................... 27

SMBus Protocol Usage ............................................................... 27

Packet Error Checking ............................................................... 27

SMBus Message Formats ........................................................... 28

Group Commands ...................................................................... 29

Hot-Swap Control Commands ................................................. 30

ADM1275 Information Commands ........................................ 30

Status Commands ....................................................................... 30

GPO and Alert Pin Setup Commands ..................................... 31

Rev. B | Page 2 of 48

Power Monitor Commands ...................................................... 31

Warning Limit Setup Commands ............................................ 32

PMBus Direct Format Conversion .......................................... 32

Voltage and Current Conversion using LSB values ............... 33

ADM1275 Alert Pin Behavior ...................................................... 34

Faults and Warnings .................................................................. 34

Generating an Alert ................................................................... 34

Handling/Clearing an Alert ...................................................... 34

SMBus Alert Response Address ............................................... 35

Example Use of SMBus Alert Response Address ................... 35

PMBus Command Reference........................................................ 36

OPERATION .............................................................................. 37

CLEAR_FAULTS ........................................................................ 37

CAPABILITY .............................................................................. 37

VOUT_OV_WARN_LIMIT ..................................................... 37

VOUT_UV_WARN_LIMIT ..................................................... 37

IOUT_OC_WARN_LIMIT ...................................................... 37

IOUT_WARN2_LIMIT ............................................................. 38

VIN_OV_WARN_LIMIT ......................................................... 38

VIN_UV_WARN_LIMIT ......................................................... 38

STATUS_BYTE .......................................................................... 38

STAT US_WORD ........................................................................ 38

STATUS_VOUT ......................................................................... 39

STATUS_IOUT .......................................................................... 39

STATUS_INPUT ........................................................................ 39

STATUS_MFR_SPECIFIC ........................................................ 40

READ_VIN ................................................................................. 40

READ_VOUT ............................................................................. 41

READ_IOUT .............................................................................. 41

PMBUS_REVISION .................................................................. 41

MFR_ID ....................................................................................... 41

MFR_MODEL ............................................................................ 41

MFR_REVISION ........................................................................ 42

PEAK_IOUT ............................................................................... 42

PEAK_VIN.................................................................................. 42

PEAK_VOUT ............................................................................. 42

PMON_CONTROL ................................................................... 42

PMON_CONFIG ....................................................................... 43

ALERT1_CONFIG ..................................................................... 43

ALERT2_CONFIG ..................................................................... 44

ADM1275

DEVICE_CONFIG ..................................................................... 45

POWER_CYCLE ......................................................................... 45

REVISION HISTORY

6/11—Rev. A to Rev. B

Changes to t

Added Conditions Statement to Table 2 ....................................... 7

Changes to VOUT Pin Description, Table 5 ............................... 10

Changes to VOUT Pin Description, Table 6 ............................... 13

Changes to Figure 42 ..................................................................... 19

Changes to Current Sense Inputs Section .................................... 21

Added PMBus Direct Format Conversion Section..................... 32

Added Voltage and Current Conversion Using LSB

Values Section .................................................................................. 33

Changes to Handling/Clearing and Alert Section ...................... 34

10/10—Rev. 0 to Rev. A

Added 20-Lead LFCSP ...................................................... Universal

Changes to Table 4 ............................................................................ 8

Added Figure 4; Renumbered Figures Sequentially ..................... 9

Changes to Table 5 ............................................................................ 9

Added Table 6; Renumbered Tables Sequentially ....................... 11

Added Figure 7 and Table 7 ........................................................... 12

Updated Outline Dimensions ........................................................ 48

Changes to Ordering Guide ........................................................... 48

9/10—Revision 0: Initial Version

Parameter ................................................................ 7

BUF

Outline Dimensions ........................................................................ 46

Ordering Guide ........................................................................... 47

Rev. B | Page 3 of 48

ADM1275

SPECIFICATIONS

VCC = 2.95 V to 20 V, VCC ≥ V

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments

POWER SUPPLY

Operating Voltage Range, VCC 2.95 20 V

Undervoltage Lockout 2.4 2.7 V VCC rising

Undervoltage Hysteresis 90 120 mV

Quiescent Current, ICC 5 mA GATE on and power monitor running

UV PIN

Input Current, IUV 100 nA UV ≤ 3.6 V

UV Threshold, UVTH 0.97 1.0 1.03 V UV falling

UV Threshold Hysteresis, UV

UV Glitch Filter, UVGF 2 7 μs 50 mV overdrive

UV Propagation Delay, UVPD 5 8 μs UV low to GATE pull-down active

OV PIN ADM1275-1 and ADM1275-3

Input Current, IOV 100 nA OV ≤ 3.6 V

OV Threshold, O VTH 0.97 1.0 1.03 V OV rising

OV Threshold Hysteresis, OV

OV Glitch Filter, OVGF 0.5 1.5 μs 50 mV overdrive

OV Propagation Delay, OVPD 1.0 2 μs OV high to GATE pull-down active

SENSE+ AND SENSE− PINS

Input Current, I

Input Imbalance, I

150 μA Per individual pin; SENSE+, SENSE− = 20 V

SENSEx

5 μA I

ΔSENSE

VCAP PIN

Internally Regulated Voltage, V

ISET PIN

Reference Select Threshold, V

Internal Reference, V

1 V Accuracies included in total sense voltage accuracies

CLREF

Gain of Current Sense Amplifier, AV

Input Current, I

100 nA V

ISET

GAT E PIN Maximum voltage on the gate is always clamped to ≤31 V

Gate Drive Voltage, ΔV

GAT E

10 12 14 V 17 V ≥ VCC ≥ 8 V; I

4.5 13 V 20 V ≥ VCC ≥ 17 V; I

8 10 V V

4.5 6 V V

Gate Pull-Up Current, I

GAT EU P

Gate Pull-Down Current, I

Gate Pull-Down Current, I

Gate Pull-Down Current, I

Gate Holdoff Resistance 20 Ω VCC = 0 V

HOT-SWAP SENSE VOLTAGE

Hot-Swap Sense Voltage Current Limit,

V

SENSECL

Foldback Inactive V

24.6 25 25.4 mV V

19.6 20 20.4 mV V

9.6 10 10.4 mV V

4.6 5 5.4 mV V

Foldback Active 3.5 4 4.5 mV V

9.6 10 10.4 mV V

, V

SENSE+

40 50 60 mV

HYST

50 60 70 mV

HYST

VCAP

ISETRSTH

= 2 V to 20 V, V

SENSE+

2.66 2.7 2.74 V 0 µA ≤ I

1.35 1.5 1.65 V If V

50 V/V Accuracies included in total sense voltage accuracies

CSAMP

SENSE

= (V

SENSE+

− V

) = 0 V, TA = −40°C to +85°C, unless otherwise noted.

SENSE−

ΔV

−20 −30 μA V

GATEDN_REG

GATEDN_SLOW

GATEDN_FAST

45 60 75 μA V

5 10 15 mA V

750 1500 2000 mA V

19.6 20 20.4 mV V

I

V

Rev. B | Page 4 of 48

= (I

ΔSENSE

GAT E

SENSE+

≤ 100 µA; C

VCAP

> V

ISET

ISETRS TH

≤ V

ISET

GAT E

SENSE+

SENSE+

GAT E

GAT E

GAT E

GAT E

ISET

VCAP

= V

− V

GAT E

= VCC = 5 V; I

= VCC = 2.95 V; I

= 0 V

≥ 2 V; V

ISET

≥ 2 V

≥ 12 V; VCC ≥ 12 V

> 1.65 V; V

= 0 μA; VSS ≥ 2 V

= (SENSE+) + 3 V; I

GAT E

= 1.25 V; V

ISET

= 1.0 V; V

ISET

= 0.5 V; V

ISET

= 0.25 V; V

ISET

= 0 V; V

FLB

ISET

≥ 1 V

SS

> 1.0 V; V

GAT E

FLB

) − (I

)

SENSE−

= 1 μF

VCAP

, an internal 1 V reference (V

SENSE+

≤ 5 μA

GAT E

≤ 5 μA

GAT E

≤ 5 μA

GATE

≤ 1 μA

GAT E

CLREF

) is used

= 1.0 V; (SENSE+) − (SENSE−) = 30 mV

> 1.12 V; V

FLB

> 1.395 V

FLB

> 1.12 V

FLB

> 0.57 V

FLB

> 0.295 V

FLB

= (SENSE+) + 3 V; I

= 0.5 V; V

= (SENSE+) + 3 V;

GAT E

= 0 μA; VSS ≥ 2 V

GAT E

GAT E

= (SENSE+) + 3 V; I

GAT E

= 0 μA; VSS ≥ 1 V

GAT E

= 0 μA;

ADM1275

Parameter Min Typ Max Unit Test Conditions/Comments

Circuit Breaker Offset, V

SEVERE OVERCURRENT

Voltage Threshold, V

9.5 13.0 mV V

Short Glitch Filter Duration 90 200 ns V

Long Glitch Filter Duration (Default) 530 900 ns V

Response Time

With Short Glitch Filter 180 370 ns 2 mV overdrive maximum severe overcurrent threshold

With Long Glitch Filter 645 1020 ns

SOFT START (SS PIN)

SS Pull-Up Current, ISS −12 −10 −8 µA VSS = 0 V

Default V

Limit 0.5 1.25 1.8 mV When V

SENSECL

SS Pull-Down Current 100 µA VSS = 1 V

TIMER PIN

Timer Pull-Up Current (POR), I

Timer Pull-Up Current (OC Fault), I

Timer Pull-Down Current (Retry), I

Timer Retry/OC Fault Current Ratio 3.33 3.8 % Defines the limits of the autoretry duty cycle

Timer Pull-Down Current (Hold),

I

TIMERDNHOLD

Timer High Threshold, V

Timer Low Threshold, V

FOLDBACK (FLB PIN)

FLB and PWRGD Threshold, V

Input Current, I

100 nA V

FLB

100 nA V

Hysteresis Current 1.7 2.3 μA

Internal Hysteresis Voltage 1.9 3.1 mV Voltage drop across the internal 1.3 kΩ resistor

Power-Good Glitch Filter, PWRGDGF 0.3 0.7 1 μs 50 mV overdrive

Minimum Foldback Clamp 200 mV Accuracies included in total sense voltage accuracies

VOUT PIN ADM1275-1 and ADM1275-3

Input Current 20 μA VOUT = 20 V

PIN ADM1275-1 and ADM1275-3

LATC H

Output Low Voltage, V

1.5 V I

Leakage Current 100 nA V

1 µA V

GPO1/

/CONV PIN (ADM1275-1 and

ALERT1

ADM1275-2), ENABLE PIN (ADM1275-3)

Output Low Voltage, V

1.5 V I

Leakage Current 100 nA V

1 µA V

Input High Voltage, VIH 1.1 V

Input Low Voltage, VIL 0.8 V

GPO2/

PIN ADM1275-1 and ADM1275-3

ALERT2

Output Low Voltage, V

1.5 V I

Leakage Current 100 nA V

1 µA V

0.6 0.88 1.12 mV Circuit breaker trip voltage, VCB = V

CBOS

40 50 mV V

SENSEOC

= 1.0 V; V

ISET

= 0.25 V; V

ISET

> 1.65 V; V

ISET

> 1.1 V; VSS ≥ 2 V

FLB

> 1.1 V; VSS ≥ 2 V

FLB

driven from 18 mV to 52 mV;

SENSE

selectable via PMBus

driven from 18 mV to 52 mV

SENSE

reaches this level, ISS is enabled, ramping

SENSE

; VSS = 0 V

V

SENSECL

TIMERUPPOR

−2 −3 −4 µA Initial power-on reset; V

−57 −60 −63 µA Overcurrent fault; 0.2 V ≤ V

TI ME RU PFLT

1.7 2 2.3 µA After fault when GATE is off; V

TIMERDNRT

100 µA Holds TIMER at 0 V when inactive; V

0.98 1.0 1.02 V

TIMERH

0.18 0.2 0.22 V

TIMERL

1.08 1.1 1.12 V FLB rising; V

FLBTH

0.4 V I

OL_LATCH

≤ 1.0 V; V

FLB

≤ V

VCAP

= 1 mA

LAT CH

= 5 mA

LAT CH

LAT CH

LAT CH

≤ 2 V;

= 20 V;

≤ 20 V

FLB

= 1.0 V

ISET

= 1.25 V

ISET

output high-Z

LATC H

LATC H

No internal pull-up present on these pins

0.4 V I

OL_GPO1

0.4 V I

OL_GPO2

= 1 mA

GPO1

= 5 mA

GPO1

≤ 2 V; GPO output high-Z

GPO1

= 20 V; GPO output high-Z

GPO1

= 1 mA

GPO2

= 5 mA

GPO2

≤ 2 V; GPO output high-Z

GPO2

= 20 V; GPO output high-Z

GPO2

= 0.5 V

TIMER

≤ 1 V

TIMER

TIMER

output high-Z

SENSECL

= 0.5 V

TIMER

− V

CBOS

= 0.5 V

Rev. B | Page 5 of 48

ADM1275

Parameter Min Typ Max Unit Test Conditions/Comments

PWRGD PIN

Output Low Voltage, V

1.5 V I

VCC That Guarantees Valid Output 1 V I

Leakage Current 100 nA V

1 µA V

CURRENT AND VOLTAGE MONITORING

Current Sense Absolute Error 25 mV input range; 128 sample averaging (unless

±0.2 ±0.7 % V

±0.08 % V

±1.0 % V

±0.08 % V

±0.2 % V

±1.0 % V

±0.08 % V

±0.2 % V

±2.8 % V

±0.09 % V

±0.2 % V

±0.7 % V

±0.04 % V

±0.15 % V

±0.75 % V

±0.8 % V

±1.1 % V

±2.0 % V

±4.3 % V

SENSE+/VOUT Absolute Error ±1.0 % Low input range; input voltage ≥ 3 V

±1.0 % High input range; input voltage ≥ 10 V

ADC Conversion Time 250 305 µs 1 sample of voltage and current; from command

4000 4880 µs 16 samples of voltage and current averaged; from

ADR PIN

Address Set to 00 0 0.8 V Connect to GND

Input Current for Address 00 −40 −22 μA V

Address Set to 01 135 150 165 kΩ Resistor to GND

Address Set to 10 −1 +1 μA No connect state; maximum leakage current allowed

Address Set to 11 2 V Connect to VCAP

Input Current for Address 11 3 10 μA V

SERIAL BUS DIGITAL INPUTS (SDA, SCL)

Input High Voltage, VIH 1.1 V

Input Low Voltage, VIL 0.8 V

Output Low Voltage, VOL 0.4 V IOL = 4 mA

Input Leakage, I

LEAK-PIN

−5 +5 μA Device is not powered

Nominal Bus Voltage, VDD 2.7 5.5 V 3 V to 5 V ± 10%

Capacitance for SDA, SCL Pin, C

Input Glitch Filter, tSP 0 50 ns

0.4 V I

OL_PWRGD

−10 +10 μA

5 pF

PIN

= 1 mA

PWRGD

= 5 mA

PWRGD

= 100 μA; V

SINK

≤ 2 V; PWRGD output high-Z

PWRGD

= 20 V; PWRGD output high-Z

PWRGD

OL_PWRGD

= 0.4 V

otherwise noted)

= 20 mV; V

SENSE

= 20 mV; V

SENSE

= 20 mV

SENSE

= 20 mV; TA = 25°C

SENSE

= 20 mV; TA = 0°C to 65°C

SENSE

= 20 mV; 16 sample averaging

SENSE

= 20 mV; 16 sample averaging; TA = 25°C

SENSE

= 20 mV; 16 sample averaging; TA = 0°C to 65°C

SENSE

= 20 mV; 1 sample averaging

SENSE

= 20 mV; 1 sample averaging; TA = 25°C

SENSE

= 20 mV; 1 sample averaging; TA = 0°C to 65°C

SENSE

= 25 mV; V

SENSE

= 25 mV; V

SENSE

= 25 mV; V

SENSE

= 20 mV; V

SENSE

= 15 mV; V

SENSE

= 10 mV; V

SENSE

= 5 mV; V

SENSE

= 2.5 mV; V

SENSE

= 12 V; TA = 0°C to 65°C

SENSE+

= 12 V; TA = 25°C

SENSE+

= 12 V

SENSE+

= 12 V; TA = 25°C

SENSE+

= 12 V; TA = 0°C to 65°C

SENSE+

= 12 V

SENSE+

= 12 V

SENSE+

= 12 V

SENSE+

= 12 V

SENSE+

= 12 V

SENSE+

received to valid data in register

command received to valid data in register

= 0 V to 0.8 V

ADR

= 2.0 V to VCAP; must not exceed the maximum

ADR

allowable current draw from VCAP

Rev. B | Page 6 of 48

ADM1275

t

LOW

t

BUF

t

HD;DAT

t

SU;DAT

t

SU;STA

t

HD;STA

t

HIGH

t

R

t

F

t

SU;STO

PSSP

V

IH

V

IL

V

IH

V

IL

SCL

SDA

08931-002

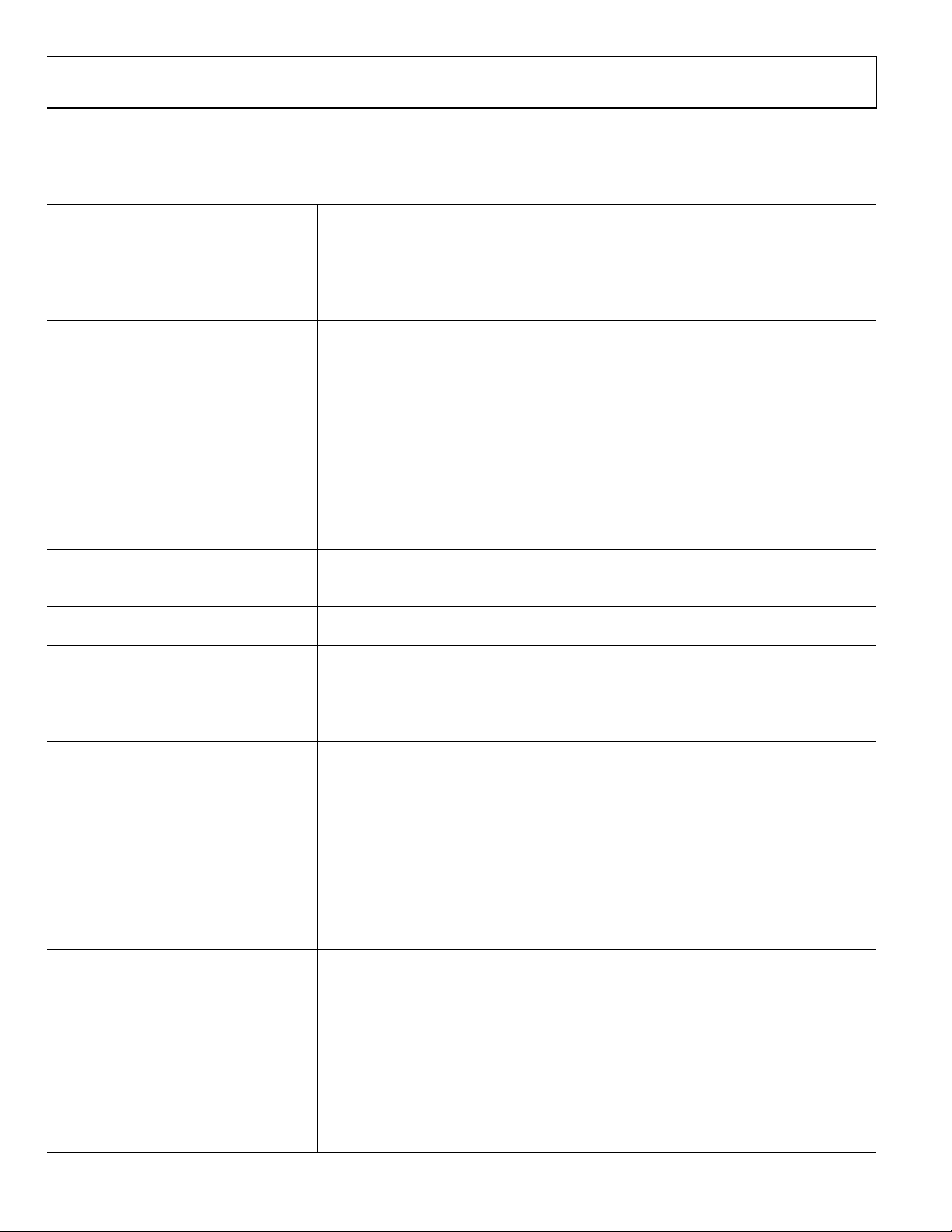

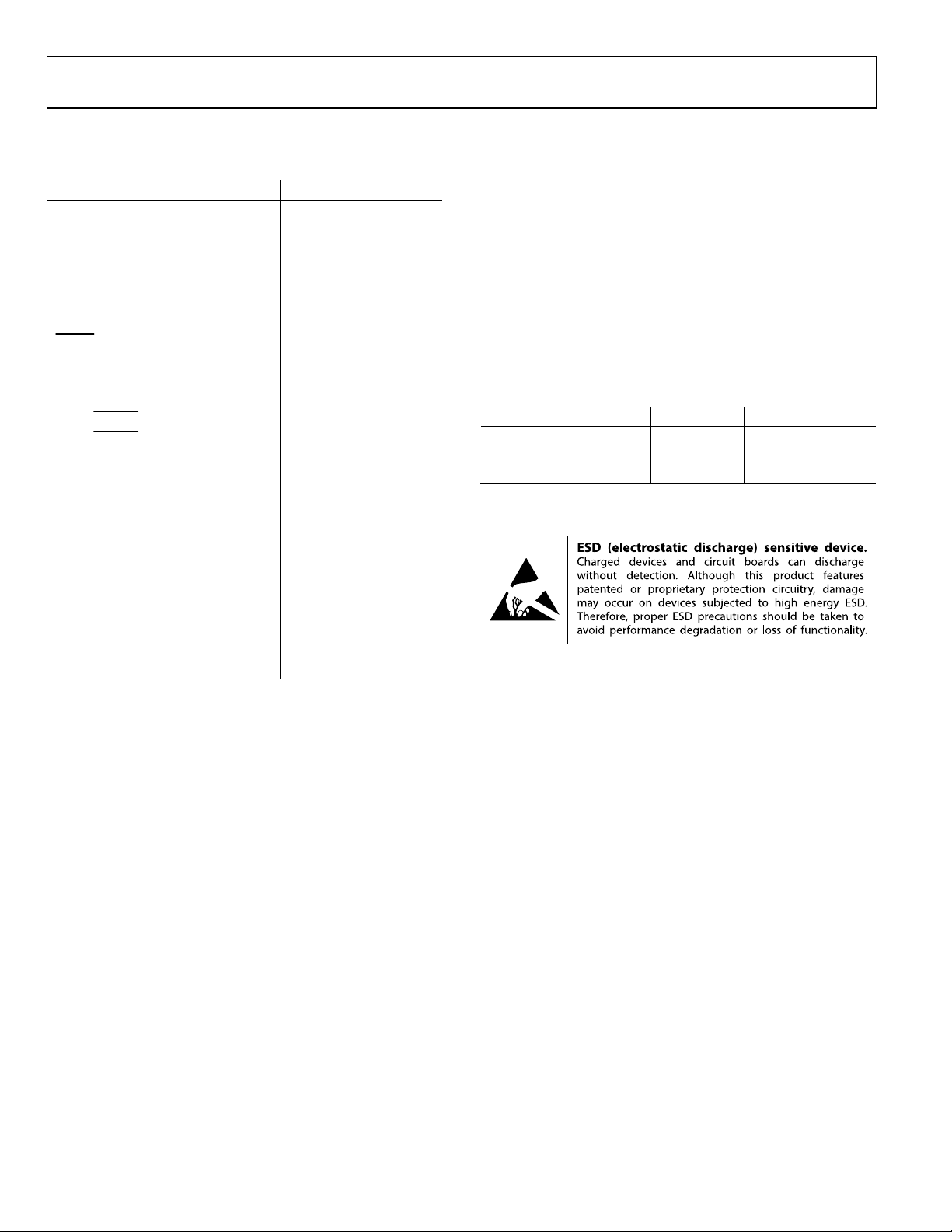

SERIAL BUS TIMING CHARACTERISTICS

tR = (V

Table 2.

Parameter Description Min Ty p Max Unit Test Conditions/Comments

f

Clock frequency 400 kHz

SCLK

t

Bus free time 1.3 µs Following the stop condition of a read transaction

BUF

4.7 µs Following the stop condition of a write transaction

t

HD ;STA

t

SU;STA

t

SU;STO

t

HD ;D AT

t

SU ;D AT

t

SCL low time 1.3 µs

LOW

t

SCL high time 0.6 µs

HIGH

tR SCL, SDA rise time 20 300 ns

tF SCL, SDA fall time 20 300 ns

Timing Diagram

IL(MAX )

– 0.15) to (V

+ 0.15) and tF = 0.9VDD to (V

IH3V3

– 0.15); where V

IL(MAX)

Start hold time 0.6 µs

Start setup time 0.6 µs

Stop setup time 0.6 µs

SDA hold time 300 900 ns

SDA setup time 100 ns

= 2.1 V and VDD = 3.3 V.

IH3V3

Figure 2. Serial Bus Timing Diagram

Rev. B | Page 7 of 48

ADM1275

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

VCC Pin −0.3 V to +25 V

UV Pin −0.3 V to +4 V

OV Pin −0.3 V to +4 V

SS Pin −0.3 V to VCAP + 0.3 V

TIMER Pin −0.3 V to VCAP + 0.3 V

VCAP Pin −0.3 V to +4 V

ISET Pin −0.3 V to VCAP + 0.3 V

LATCH Pin

−0.3 V to +25 V

SCL Pin −0.3 V to +6.5 V

SDA Pin −0.3 V to +6.5 V

ADR Pin −0.3 V to VCAP + 0.3 V

GPO1/ALERT1/CONV Pin, ENABLE Pin

GPO2/ALERT2 Pin

−0.3 V to +25 V

−0.3 V to +25 V

PWRGD Pin −0.3 V to +25 V

FLB Pin −0.3 V to +25 V

VOUT Pin −0.3 V to +25 V

GATE Pin (Internal Supply Only)1 −0.3 V to +36 V

SENSE+ Pin −0.3 V to +25 V

SENSE− Pin −0.3 V to +25 V

V

(V

SENSE

SENSE+

− V

) ±0.3 V

SENSE−

Continuous Current into Any Pin ±10 mA

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +85°C

Lead Temperature, Soldering (10 sec) 300°C

Junction Temperature 150°C

1

The GATE pin has internal clamping circuits to prevent the GATE pin voltage

from exceeding the maximum ratings of a MOSFET with V

internal process limits. Applying a voltage source to this pin externally may

cause irreversible damage.

= 20 V and

GSMAX

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 4. Thermal Resistance

Package Type θJA Unit

16-lead QSOP (RQ-16) 150 °C/W

20-lead QSOP (RQ-20) 126 °C/W

20-lead LFCSP (CP-20-9) 30.4 °C/W

ESD CAUTION

Rev. B | Page 8 of 48

ADM1275

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

UV

OV

VCAP

TIMER

SS

ISET

VCC

SENSE–

GATE

GND

PWRGD

FLB

VOUT

GPO1/ALERT1/CONV

ADR

LATCH

GPO2/ALERT2

SDA

SCL

SENSE+

ADM1275-1

TOP VIEW

(Not to S cale)

08931-006

1OV

2VCAP

3ISET

4SS

5TIMER

NOTES

1. SOLDER THE EXPOSED PADDLE TO

THE BOARD TO IMPROVE THERMAL

DISSIPATION. THE EXPOSED PADDLE

CAN BE CONNECTED TO GROUND.

LATCH

ADR

GPO1/ALERT1/CONV

GPO2/ALERT2

SDA

13

14

15

12

11

FLB

VOUT

GND

PWRGD

SCL

SENSE+

VCC

UV

SENSE–

GATE

6

7

8

01

9

81

91

02

71

61

08931-109

ADM1275-1

TOP VIEW

(Not to S cale)

PIN 1

INDICATOR

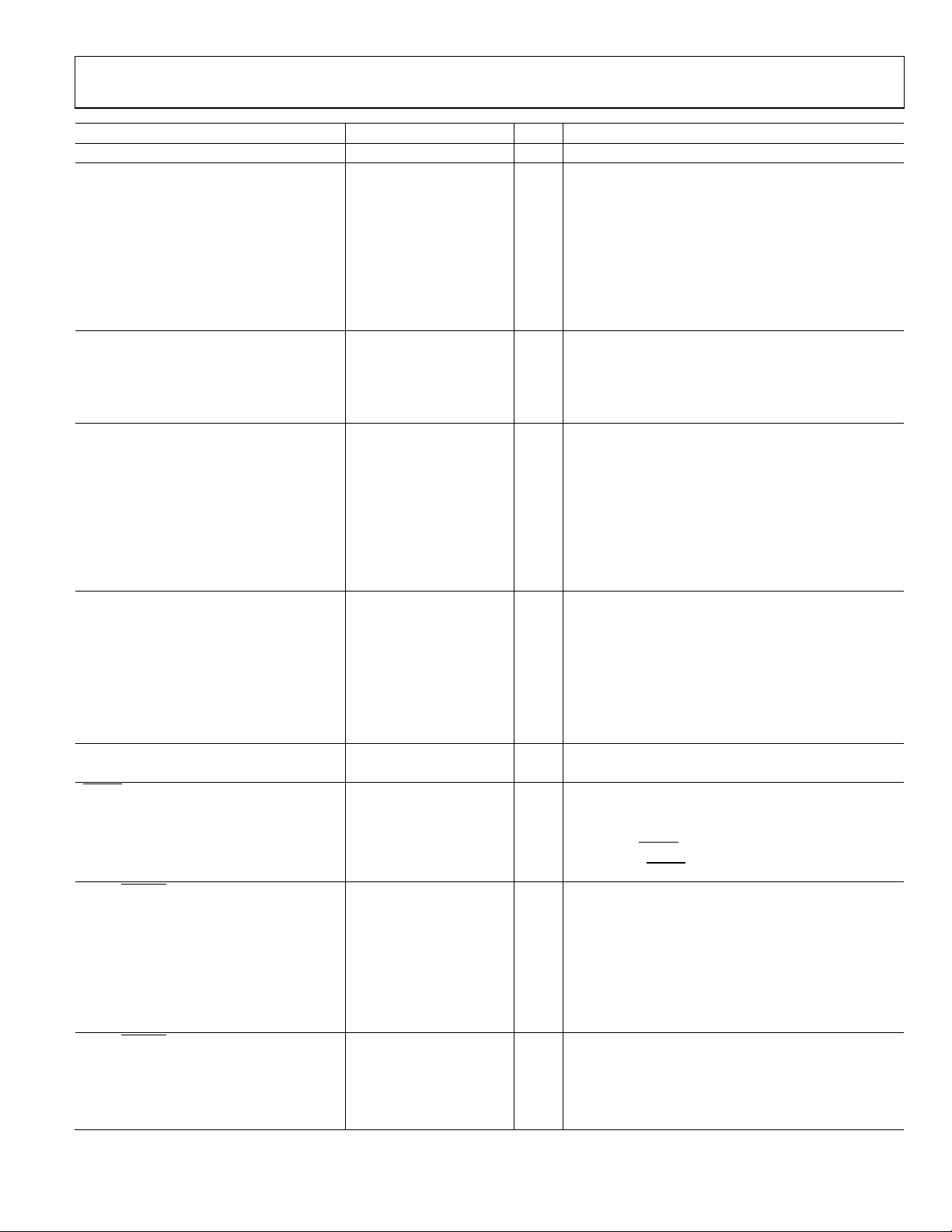

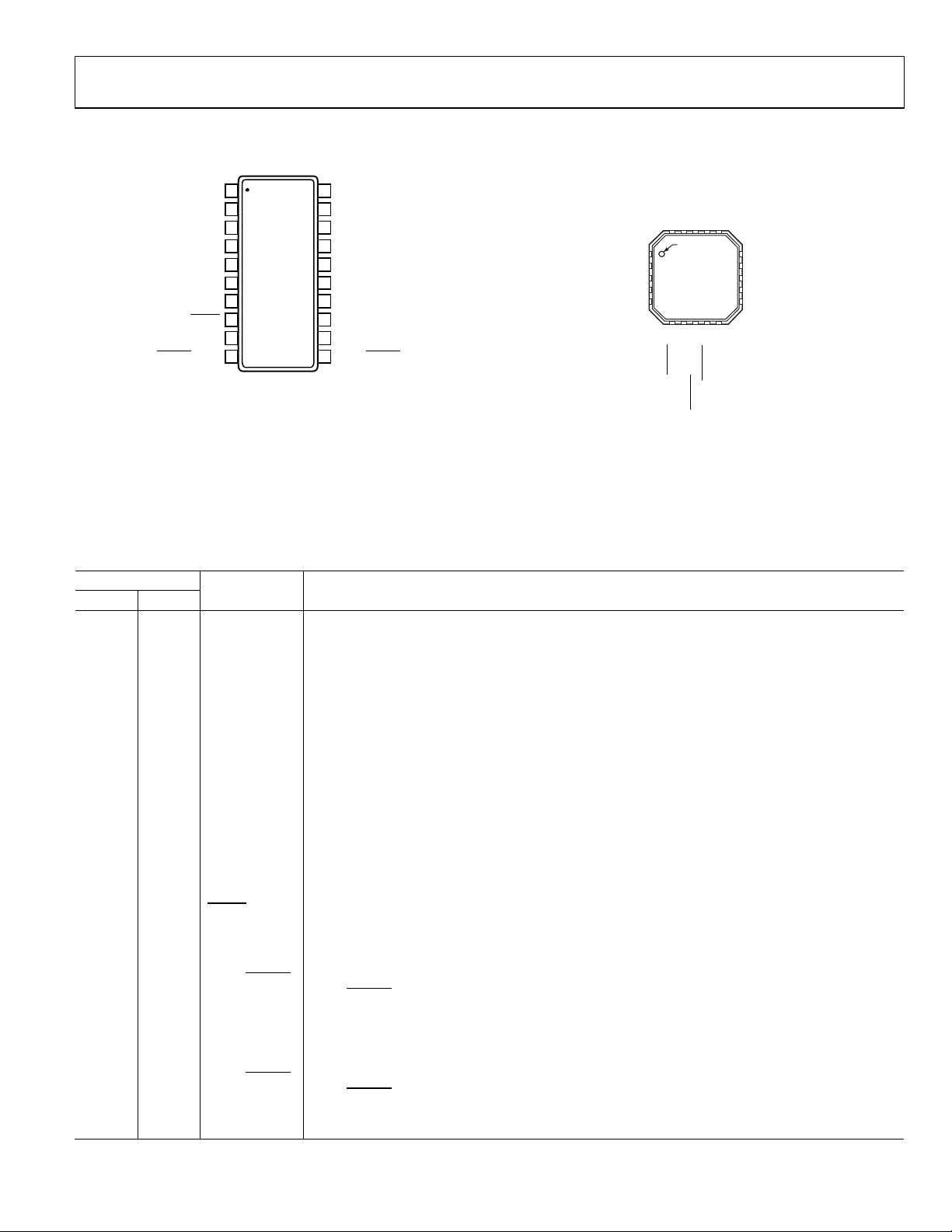

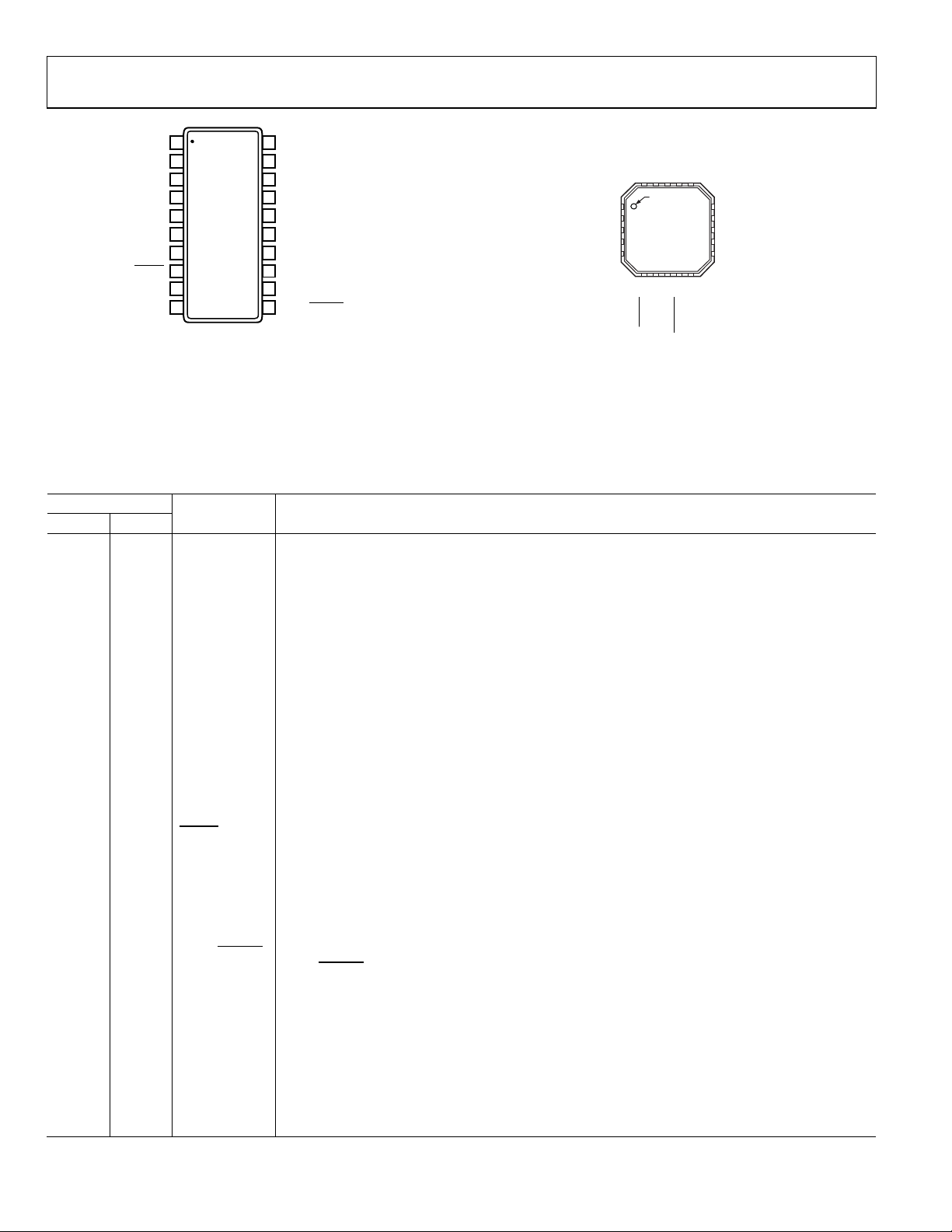

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. ADM1275-1 Pin Configuration, QSOP

Figure 4. ADM1275-1 Pin Configuration, LFCSP

Table 5. ADM1275-1 Pin Function Descriptions

Pin No.

QSOP LFCSP Mnemonic Description

1 19 VCC Positive Supply Input Pin. An undervoltage lockout (UVLO) circuit resets the device when a low

2 20 UV Undervoltage Input Pin. An external resistor divider is used from the supply to this pin to allow an

3 1 OV Overvoltage Input Pin. An external resistor divider is used from the supply to this pin to allow an

4 2 VCAP Internal Regulated Supply. A capacitor with a value of 1 µF or greater should be placed on this pin

5 3 ISET This pin allows the current limit threshold to be programmed. The default limit is set when this pin

6 4 SS Soft Start Pin. A capacitor is used on this pin to set the soft start ramp profile. The voltage on the

7 5 TIMER Timer Pin. An external capacitor, C

8 6

9 7 ADR PMBus Address Pin. This pin can be tied to GND, tied to VCAP, left floating, or tied low through a

10 8 GPO1/

11 9 GPO2/

LATC H

CONV

supply voltage is detected. GATE is held low when the supply is below UVLO. During normal

operation, this pin should remain greater than or equal to SENSE+ to ensure that specifications

are adhered to. No sequencing is required.

internal comparator to detect whether the supply is under the UV limit.

internal comparator to detect whether the supply is above the OV limit.

to maintain good accuracy. This pin can be used as a reference to program the ISET pin voltage.

is connected directly to VCAP. To achieve a user-defined sense voltage, the current limit can be

adjusted using a resistor divider from VCAP. An external reference can also be used.

SS pin controls the current sense voltage limit, which controls the inrush current profile.

, sets an initial timing cycle delay and a fault delay. The GATE

TIMER

pin is pulled low when the voltage on the TIMER pin exceeds the upper threshold.

Signals that the device is latching off after an overcurrent fault. The device can be configured for

automatic retry after latch-off by connecting this pin directly back to the UV pin.

resistor to set four different PMBus addresses (see the Device Addressing section).

/

ALERT1

General-Purpose Digital Output (GPO1).

Alert (

). This pin can be configured to generate an alert signal when one or more fault or

ALERT1

warning conditions are detected.

Conversion (CONV). This pin can be used as an input signal to control when a power monitor ADC

sampling cycle begins.

At power-up, this pin defaults to a high impedance state. There is no internal pull-up on this pin.

General-Purpose Digital Output (GPO2).

ALERT2

Alert (

). This pin can be configured to generate an alert signal when one or more fault or

ALERT2

warning conditions are detected.

At power-up, this pin indicates the FET health mode by default. There is no internal pull-up on this pin.

Rev. B | Page 9 of 48

ADM1275

Pin No.

QSOP LFCSP Mnemonic Description

12 10 SDA Serial Data Input/Output Pin. Open-drain input/output. Requires an external resistive pull-up.

13 11 SCL Serial Clock Pin. Open-drain input. Requires an external resistive pull-up.

14 12 PWRGD Power-Good Signal. Used to indicate that the supply is within tolerance. This signal is based on the

voltage present on the FLB pin.

15 13 FLB Foldback Pin. A foldback resistor divider is placed from the source of the FET to this pin. Foldback is

used to reduce the current limit when the source voltage drops. The foldback feature ensures that

the power through the FET is not increased beyond the SOA limits.

16 14 VOUT This pin is used to read back the output voltage using the internal ADC. A 1 kΩ resistor should be

inserted in series between the source of a FET and the VOUT pin.

17 15 GND Chip Ground Pin.

18 16 GAT E Gate Output Pin. This pin is the high-side gate drive of an external N-channel FET. This pin is driven

by the FET drive controller, which uses a charge pump to provide a pull-up current to charge the FET

gate pin. The FET drive controller regulates to a maximum load current by regulating the GATE pin.

GATE is held low when the supply is below UVLO.

19 17 SENSE− Negative Current Sense Input Pin. A sense resistor between the SENSE+ pin and the SENSE− pin sets

the analog current limit. The hot-swap operation of the ADM1275 controls the external FET gate to

maintain the sense voltage (V

20 18 SENSE+ Positive Current Sense Input Pin. This pin connects to the main supply input. A sense resistor

between the SENSE+ pin and the SENSE− pin sets the analog current limit. The hot-swap operation

of the ADM1275 controls the external FET gate to maintain the sense voltage (V

pin is also used to measure the supply input voltage using the ADC.

N/A EP EPAD Exposed Paddle on Underside of LFCSP. Solder the exposed paddle to the board to improve thermal

dissipation. The exposed paddle can be connected to ground.

SENSE+

− V

). This pin also connects to the FET drain pin.

SENSE−

SENSE+

− V

SENSE−

). This

Rev. B | Page 10 of 48

ADM1275

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

UV

VCAP

ISET

ADR

TIMER

SS

VCC

SENSE–

GATE

GND

SCL

GPO1/ALERT1/CONV SDA

PWRGD

FLB

SENSE+

ADM1275-2

TOP VIEW

(Not to S cale)

08931-007

Foldback Pin. A foldback resistor divider is placed from the source of the FET to this pin. Foldback

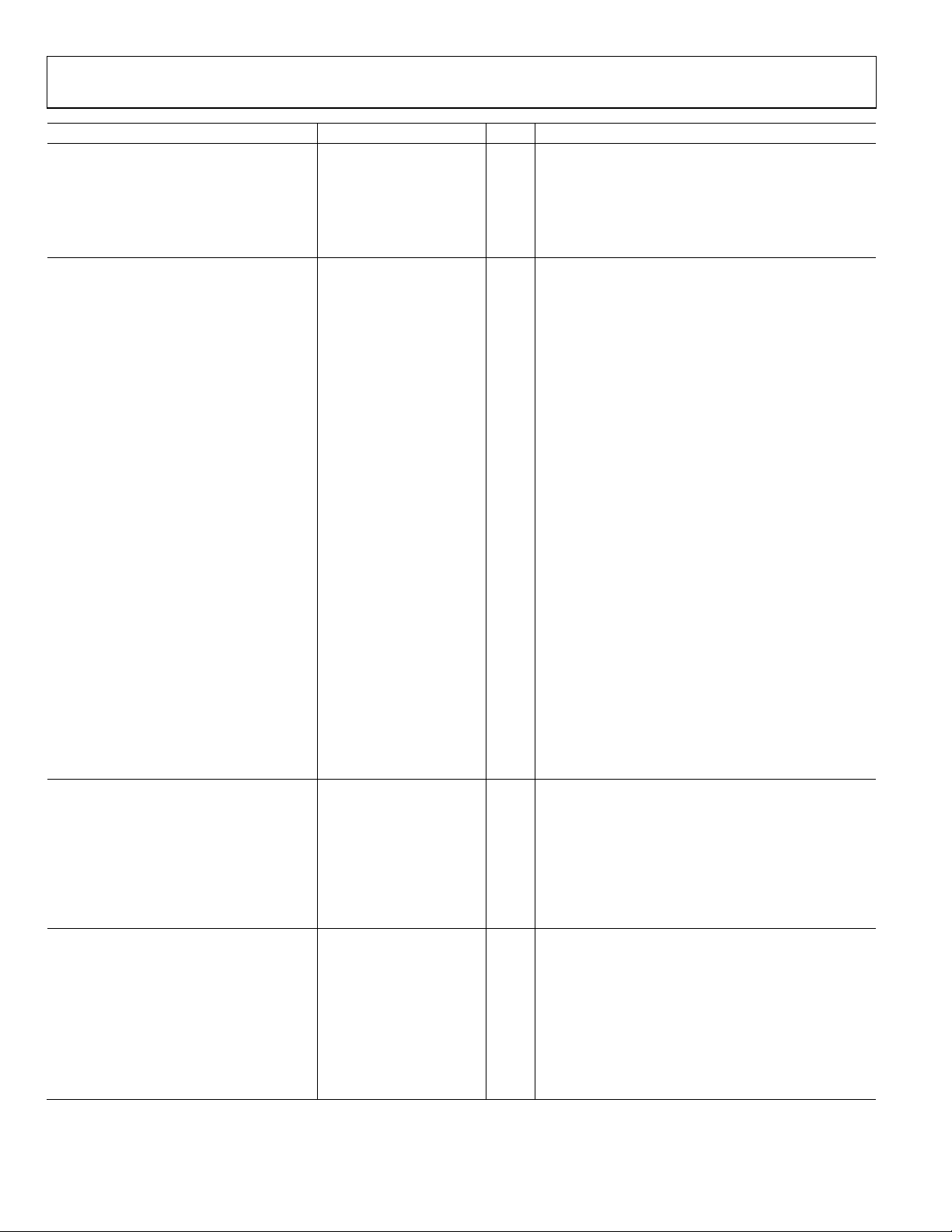

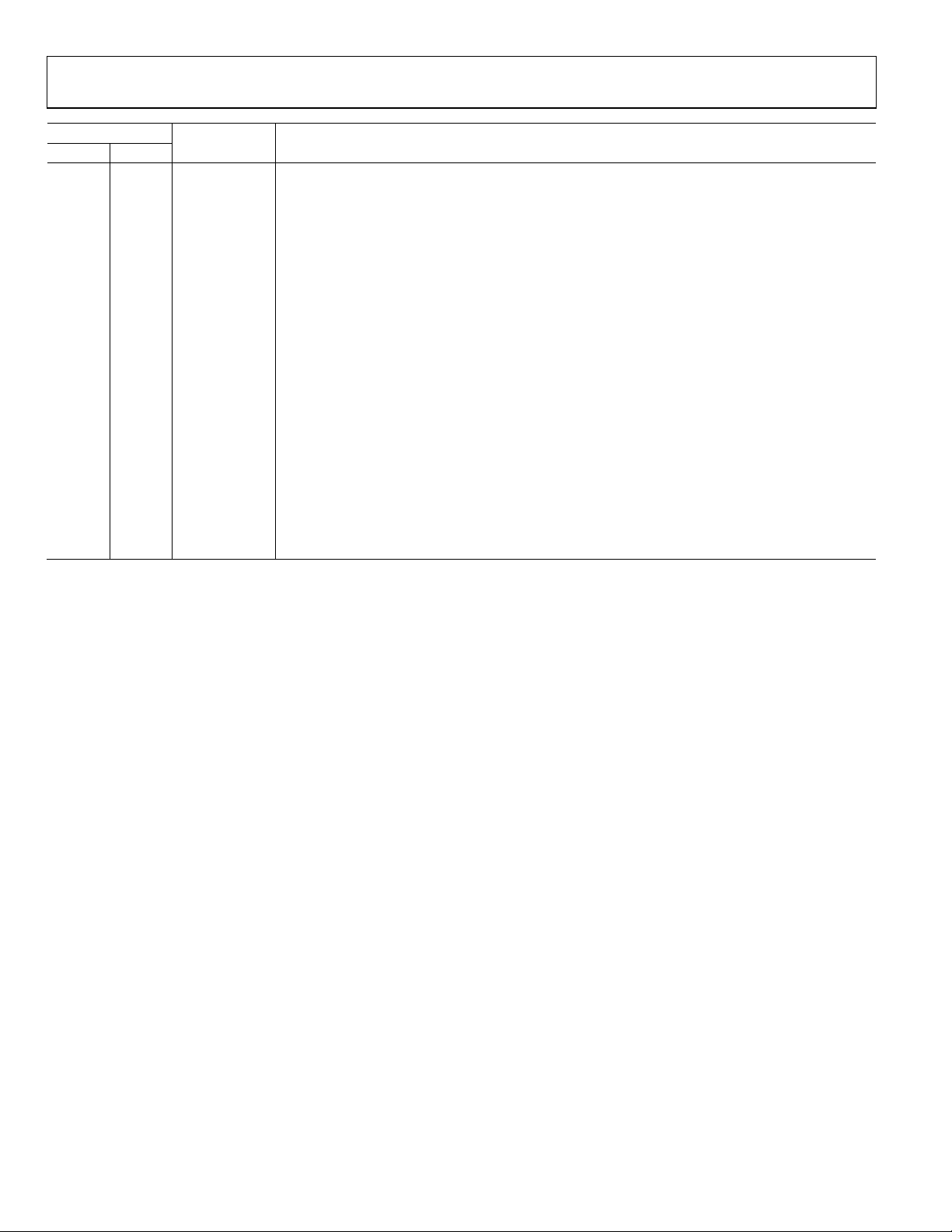

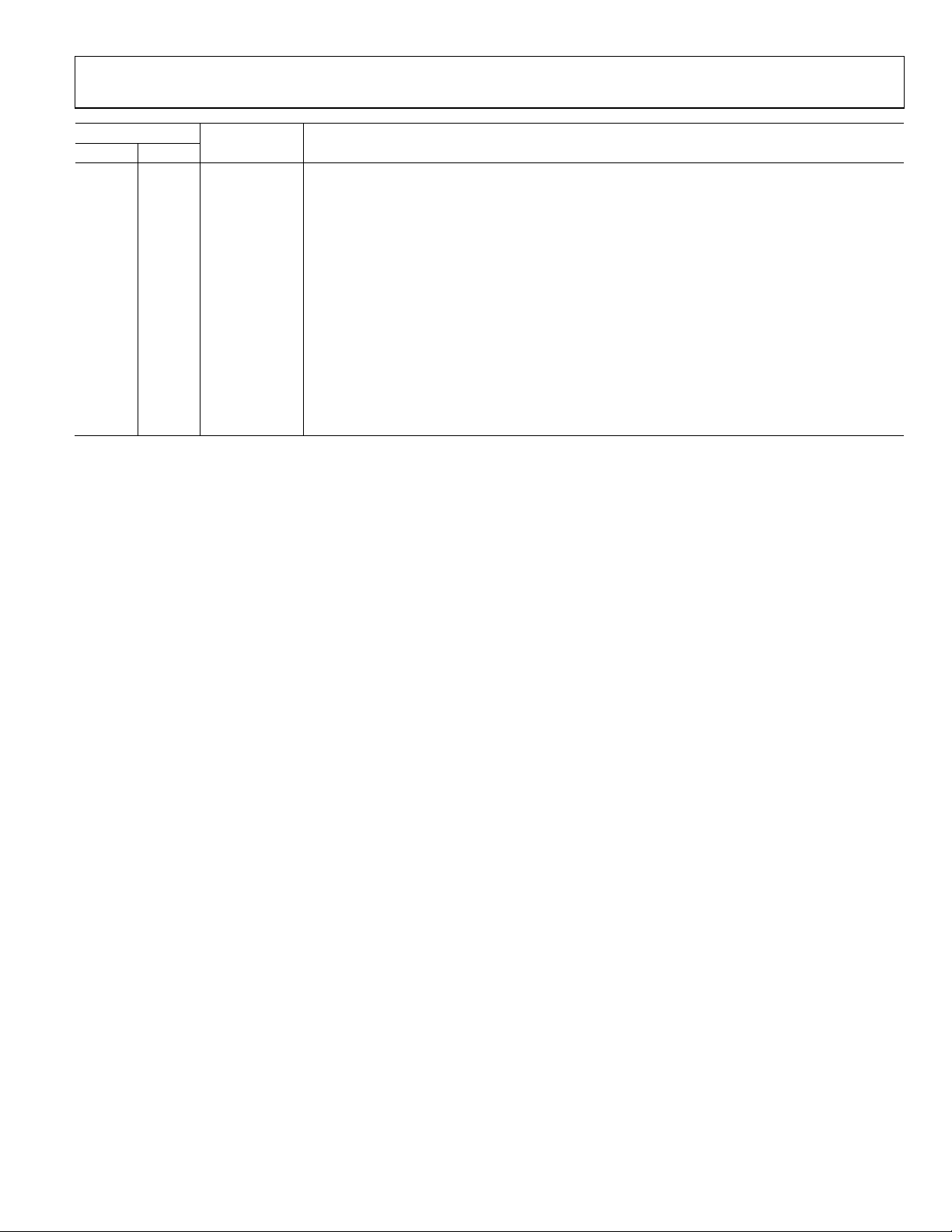

Figure 5. ADM1275-2 Pin Configuration

Table 6. ADM1275-2 Pin Function Descriptions

Pin No. Mnemonic Description

1 VCC Positive Supply Input Pin. An undervoltage lockout (UVLO) circuit resets the device when a low

supply voltage is detected. GATE is held low when the supply is below UVLO. During normal

operation, this pin should remain greater than or equal to SENSE+ to ensure that specifications

are adhered to. No sequencing is required.

2 UV Undervoltage Input Pin. An external resistor divider is used from the supply to this pin to allow

an internal comparator to detect whether the supply is under the UV limit.

3 VCAP Internal Regulated Supply. A capacitor with a value of 1 µF or greater should be placed on this pin

to maintain good accuracy. This pin can be used as a reference to program the ISET pin voltage.

4 ISET This pin allows the current limit threshold to be programmed. The default limit is set when this

pin is connected directly to VCAP. To achieve a user-defined sense voltage, the current limit can

be adjusted using a resistor divider from VCAP. An external reference can also be used.

5 SS Soft Start Pin. A capacitor is used on this pin to set the soft start ramp profile. The voltage on the

SS pin controls the current sense voltage limit, which controls the inrush current profile.

6 TIMER Timer Pin. An external capacitor, C

TIMER

GAT E pin is pulled low when the voltage on the TIMER pin exceeds the upper threshold.

7 ADR PMBus Address Pin. This pin can be tied to GND, tied to VCAP, left floating, or tied low through a

resistor to set four different PMBus addresses (see the Device Addressing section).

8 GPO1/

/CONV General-Purpose Digital Output (GPO1).

ALERT1

Alert (

). This pin can be configured to generate an alert signal when one or more fault or

ALERT1

warning conditions are detected.

Conversion (CONV). This pin can be used as an input signal to control when a power monitor

ADC sampling cycle begins.

At power-up, this pin defaults to a high impedance state. There is no internal pull-up on this pin.

9 SDA Serial Data Input/Output Pin. Open-drain input/output. Requires an external resistive pull-up.

10 SCL Serial Clock Pin. Open-drain input. Requires an external resistive pull-up.

11 PWRGD Power-Good Signal. Used to indicate that the supply is within tolerance. This signal is based on

the voltage present on the FLB pin.

12 FLB

is used to reduce the current limit when the source voltage drops. The foldback feature ensures

that the power through the FET is not increased beyond the SOA limits.

13 GND Chip Ground Pin.

14 GATE Gate Output Pin. This pin is the high-side gate drive of an external N-channel FET. This pin is

driven by the FET drive controller, which uses a charge pump to provide a pull-up current to

charge the FET gate pin. The FET drive controller regulates to a maximum load current by

regulating the GATE pin. GATE is held low when the supply is below UVLO.

15 SENSE− Negative Current Sense Input Pin. A sense resistor between the SENSE+ pin and the SENSE− pin

sets the analog current limit. The hot-swap operation of the ADM1275 controls the external FET

gate to maintain the sense voltage (V

16 SENSE+ Positive Current Sense Input Pin. This pin connects to the main supply input. A sense resistor

between the SENSE+ pin and the SENSE− pin sets the analog current limit. The hot-swap operation

of the ADM1275 controls the external FET gate to maintain the sense voltage (V

This pin is also used to measure the supply input voltage using the ADC.

Rev. B | Page 11 of 48

, sets an initial timing cycle delay and a fault delay. The

SENSE+

− V

). This pin also connects to the FET drain pin.

SENSE−

SENSE+

− V

SENSE−

).

ADM1275

1

2

3

4

5

6

7

8

9

1

0

20

19

18

17

16

15

14

13

12

11

UV

OV

VCAP

TIMER

SS

ISET

VCC

SENSE–

GATE

GND

PWRGD

FLB

VOUT

ENABLE

ADR

LATCH

GPO2/ALERT2

SDA

SCL

SENSE+

ADM1275-3

TOP VIEW

(Not to S cale)

08931-008

1OV

2VCAP

3ISET

4SS

5TIMER

LATCH

ADR

ENABLE

GPO2/ALERT2

SDA

13

14

15

12

11

FLB

VOUT

GND

PWRGD

SCL

SENSE+

VCC

UV

SENSE–

GATE

6

7

8

01

9

81

91

02

71

61

08931-110

ADM1275-3

TOP VIEW

(Not to S cale)

PIN 1

INDICATOR

NOTES

1. SOLDER THE EXPOSED PADDLE TO

THE BOARD TO IMPROVE THERMAL

DISSIPATION. THE EXPOSED PADDLE

CAN BE CONNECTED TO GROUND.

Figure 6. ADM1275-3 Pin Configuration, QSOP

Table 7. ADM1275-3 Pin Function Descriptions

Pin No.

QSOP LFCSP Mnemonic Description

1 19 VCC Positive Supply Input Pin. An undervoltage lockout (UVLO) circuit resets the device when a low

2 20 UV Undervoltage Input Pin. An external resistor divider is used from the supply to this pin to allow an

3 1 OV Overvoltage Input Pin. An external resistor divider is used from the supply to this pin to allow an

4 2 VCAP Internal Regulated Supply. A capacitor with a value of 1 µF or greater should be placed on this pin

5 3 ISET This pin allows the current limit threshold to be programmed. The default limit is set when this pin

6 4 SS Soft Start Pin. A capacitor is used on this pin to set the soft start ramp profile. The voltage on the

7 5 TIMER Timer Pin. An external capacitor, C

8 6

9 7 ADR PMBus Address Pin. This pin can be tied to GND, tied to VCAP, left floating, or tied low through a

10 8 ENABLE Digital Logic Input. This input must be high to allow the ADM1275-3 hot-swap controller to begin a

11 9 GPO2/

12 10 SDA Serial Data Input/Output Pin. Open-drain input/output. Requires an external resistive pull-up.

13 11 SCL Serial Clock Pin. Open-drain input. Requires an external resistive pull-up.

14 12 PWRGD Power-Good Signal. Used to indicate that the supply is within tolerance. This signal is based on the

15 13 FLB Foldback Pin. A foldback resistor divider is placed from the source of the FET to this pin. Foldback is

Figure 7. ADM1275-3 Pin Configuration, LFCSP

supply voltage is detected. GATE is held low when the supply is below UVLO. During normal

operation, this pin should remain greater than or equal to SENSE+ to ensure that specifications are

adhered to. No sequencing is required.

internal comparator to detect whether the supply is under the UV limit.

internal comparator to detect whether the supply is above the OV limit.

to maintain good accuracy. This pin can be used as a reference to program the ISET pin voltage.

is connected directly to VCAP. To achieve a user-defined sense voltage, the current limit can be

adjusted using a resistor divider from VCAP. An external reference can also be used.

SS pin controls the current sense voltage limit, which controls the inrush current profile.

, sets an initial timing cycle delay and a fault delay. The GATE

TIMER

pin is pulled low when the voltage on the TIMER pin exceeds the upper threshold.

Signals that the device is latching off after an overcurrent fault. The device can be configured for

LATC H

automatic retry after latch-off by connecting this pin directly back to the UV pin.

resistor to set four different PMBus addresses (see the Device Addressing section).

power-up sequence. If this pin is held low, the ADM1275-3 is prevented from powering up. There is

no internal pull-up on this pin.

General-Purpose Digital Output (GPO2).

ALERT2

Alert (

). This pin can be configured to generate an alert signal when one or more fault or

ALERT2

warning conditions are detected.

At power-up, this pin indicates the FET health mode by default. There is no internal pull-up on this pin.

voltage present on the FLB pin.

used to reduce the current limit when the source voltage drops. The foldback feature ensures that

the power through the FET is not increased beyond the SOA limits.

Rev. B | Page 12 of 48

ADM1275

Pin No.

QSOP LFCSP Mnemonic Description

16 14 VOUT This pin is used to read back the output voltage using the internal ADC. A 1 kΩ resistor should be

inserted in series between the source of a FET and the VOUT pin.

17 15 GND Chip Ground Pin.

18 16 GATE Gate Output Pin. This pin is the high-side gate drive of an external N-channel FET. This pin is driven

by the FET drive controller, which uses a charge pump to provide a pull-up current to charge the FET

gate pin. The FET drive controller regulates to a maximum load current by regulating the GATE pin.

GATE is held low when the supply is below UVLO.

19 17 SENSE− Negative Current Sense Input Pin. A sense resistor between the SENSE+ pin and the SENSE− pin sets

the analog current limit. The hot-swap operation of the ADM1275 controls the external FET gate to

maintain the sense voltage (V

SENSE+

− V

20 18 SENSE+ Positive Current Sense Input Pin. This pin connects to the main supply input. A sense resistor

between the SENSE+ pin and the SENSE− pin sets the analog current limit. The hot-swap operation

of the ADM1275 controls the external FET gate to maintain the sense voltage (V

pin is also used to measure the supply input voltage using the ADC.

N/A EP EPAD Exposed Paddle on Underside of LFCSP. Solder the exposed paddle to the board to improve thermal

dissipation. The exposed paddle can be connected to ground.

). This pin also connects to the FET drain pin.

SENSE−

SENSE+

− V

SENSE−

). This

Rev. B | Page 13 of 48

ADM1275

0

1

2

3

4

5

I

CC

(mA)

VCC (V)

2 4 6 8 10 12 14 16 18

20

08931-009

+25°C

+85°C

–40°C

0

1

2

3

4

5

–40 –20 0

I

CC

(mA)

TEMPERATURE (°C)

VCC = 20V

VCC = 12V

V

CC

= 2.95V

08931-010

20 40

60 80

0

2

4

6

8

10

12

14

2 4 6 8 1210 14 16 18 20

I

GATEDN_SLOW

(mA)

VCC (V)

08931-011

+25°C

–40°C

+85°C

0

2

4

6

8

10

12

14

I

GATEDN_SLOW

(mA)

TEMPERATURE (°C)

08931-012

V

CC

= 12V

–40

–20 0 20 40 60 80

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0 5 10 15 20 25

I

GATEDN_SLOW

(mA)

V

GATE

(V)

08931-013

–40

–35

–30

–25

–20

–15

–10

–5

0

2 4 6 8 10 12 14 16 18 20

I

GATEUP

(µA)

VCC (V)

08931-014

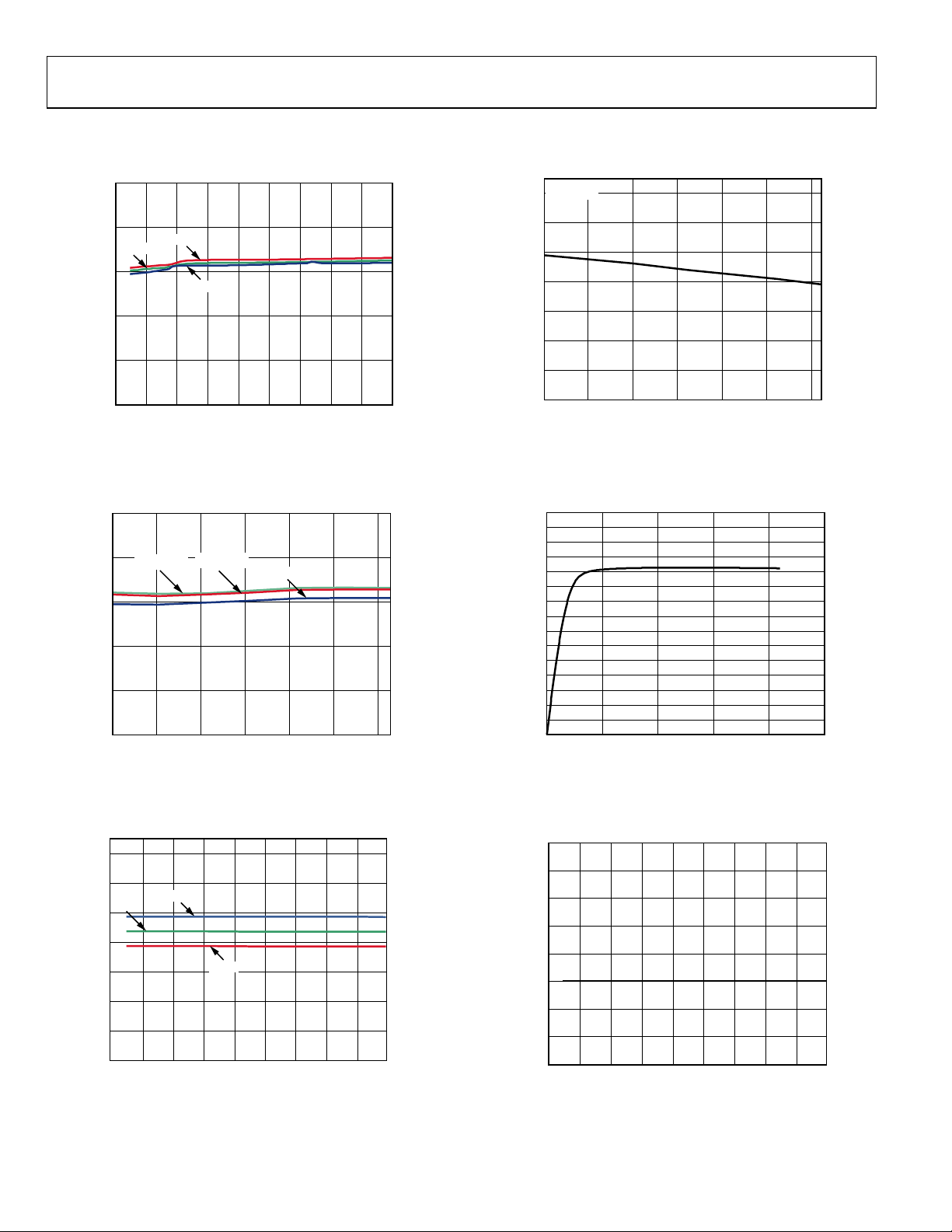

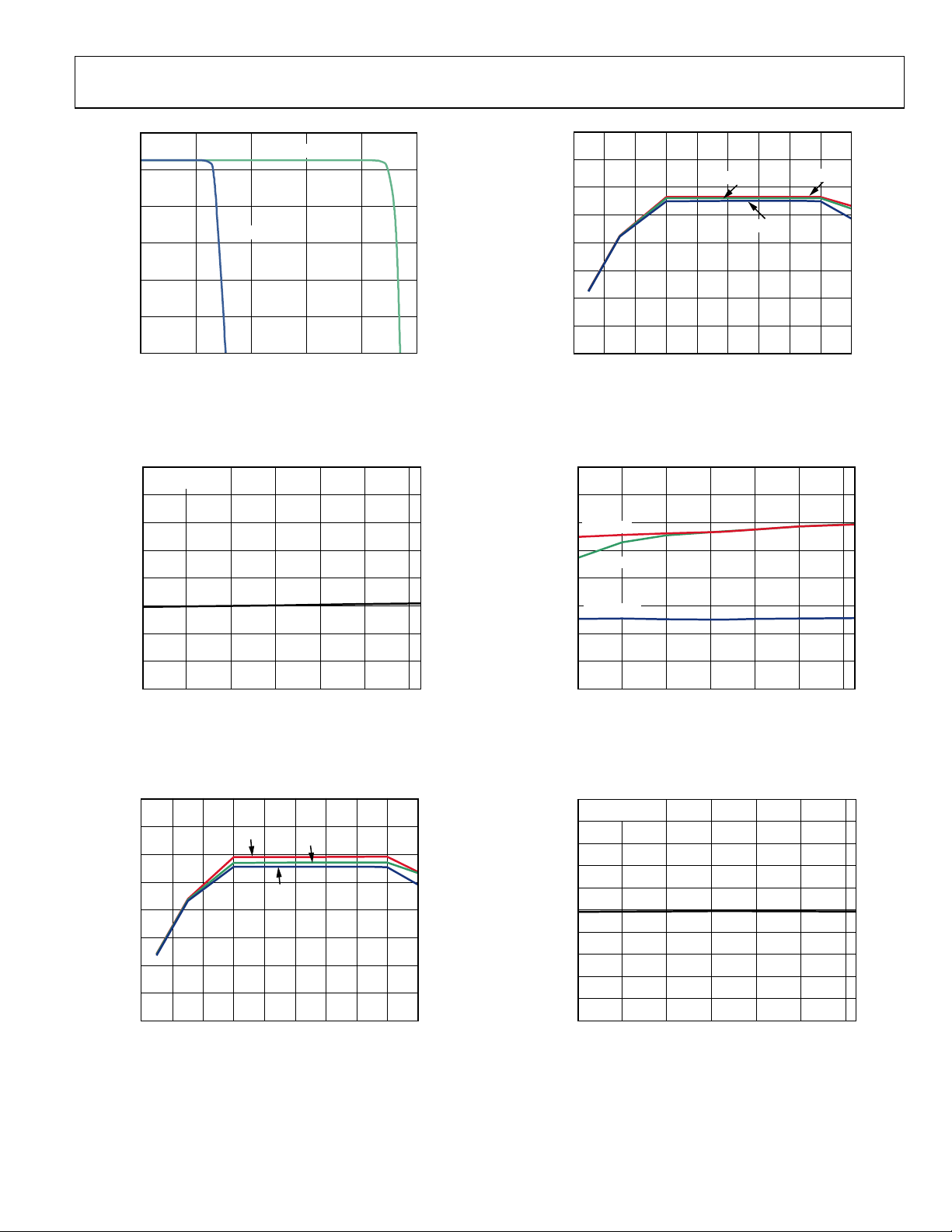

TYPICAL PERFORMANCE CHARACTERISTICS

Figure 8. Supply Current (ICC) vs. Supply Voltage (VCC)

Figure 11. Gate Pull-Down Current (I

GATEDN_SLOW

) vs. Temperature

Figure 9. Supply Current (I

Figure 10. Gate Pull-Down Current (I

GATEDN_SLOW

) vs. Temperature

CC

) vs. Supply Voltage (VCC)

Figure 12. Gate Pull-Down Current (I

GATEDN_S LOW

) vs. Gate Voltage (V

GATE

)

Figure 13. Gate Pull-Up Current (I

) vs. Supply Voltage (VCC)

GATEUP

Rev. B | Page 14 of 48

ADM1275

0

5

10

15

20

25

30

0 5 10 15 20 25

I

GATEUP

(µA)

V

GATE

(V)

VCC = 12V

V

CC

= 2.95V

08931-016

–40

–35

–30

–25

–20

–15

–10

–5

0

I

GATEUP

(µA)

TEMPERATURE (°C)

V

CC

= 12V

08931-015

–40

–20 0 20 40 60 80

0

2

4

6

8

10

12

14

16

2 20

ΔV

GATE

(V)

V

CC

(V)

+85°C

+25°C

–40°C

08931-017

4 6 8 10 12 14 16 18

0

2

4

6

8

10

12

14

16

ΔV

GATE

(V)

V

CC

(V)

08931-018

2 4 6 8 10 12 14 16 18 20

+25°C

+85°C

–40°C

0

2

4

6

8

10

12

14

16

–40 –20 0 20 40 60

ΔV

GATE

(V)

TEMPERATURE (°C)

V

CC

= 12V

V

CC

= 20V

V

CC

= 2.95V

08931-019

80

–20

–18

–16

–14

–12

–10

–8

–6

–4

–2

0

–40

I

SS

PULL-UP (µA)

TEMPERATURE (°C)

V

CC

= 12V

08931-020

–20 0 20 40 60 80

Figure 14. Gate Pull-Up Current (I

Figure 15. Gate Pull-Up Current (I

) vs. Gate Voltage (V

GATEUP

) vs. Temperature

GATEUP

GATE

)

Figure 17. Gate Drive Voltage (ΔV

Figure 18. Gate Drive Voltage (ΔV

) vs. Supply Voltage (VCC), 5 µA Load

GATE

) vs. Temperature, No Load

GATE

Figure 16. Gate Drive Voltage (ΔV

) vs. Supply Voltage (VCC), No Load

GATE

Rev. B | Page 15 of 48

Figure 19. Soft Start Pull-Up Current (I

) vs. Temperature

SS

Loading...

Loading...