Frequency Synthesizer

ADF4193

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

Trademarks and registered trademarks are the property of their respective owners.

Fax: 781.461.3113 ©2005–2012 Analog Devices, Inc. All rights reserved.

05328-001

N COUNTER

SW1

CP

OUT+

CP

OUT–

SW2

REFERENCE

DATA

LE

24-BIT

DATA

REGISTER

CLK

REF

IN

A

GND

1

A

GND

2 D

GND

1 D

GND

2 D

GND

3 SD

GND

SW

GND

V

DD

DGND

LOCK DETE CT

R

DIV

N

DIV

SDVDDDV

DD

1 DVDD2 DV

DD

3 AV

DD

1

V

P

1 V

P

2 V

P

3 R

SET

OUTPUT

MUX

MUX

OUT

–

+

HIGH Z

PHASE

FREQUENCY

DETECTOR

ADF4193

FRACTIONAL

INTERPOLATOR

MODULUS

REG

FRACTION

REG

INTEGER

REG

RF

IN+

RF

IN–

×2

DOUBLER

4-BIT R

COUNTER

÷2

DIVIDER

CHARGE

PUMP

–

+

+

–

DIFFERENTIAL

AMPLIFIER

CMR

AIN–

AIN+

A

OUT

SW3

Data Sheet

FEATURES

New, fast settling, fractional-N PLL architecture

Single PLL replaces ping-pong synthesizers

Frequency hop across GSM band in 5 µs with phase settled

by 20 µs

0.5° rms phase error at 2 GHz RF output

Digitally programmable output phase

RF input range up to 3.5 GHz

3-wire serial interface

On-chip, low noise differential amplifier

Phase noise figure of merit: −216 dBc/Hz

Loop filter design possible using ADI SimPLL

Qualified for automotive applications

APPLICATIONS

GSM/EDGE base stations

PHS base stations

Instrumentation and test equipment

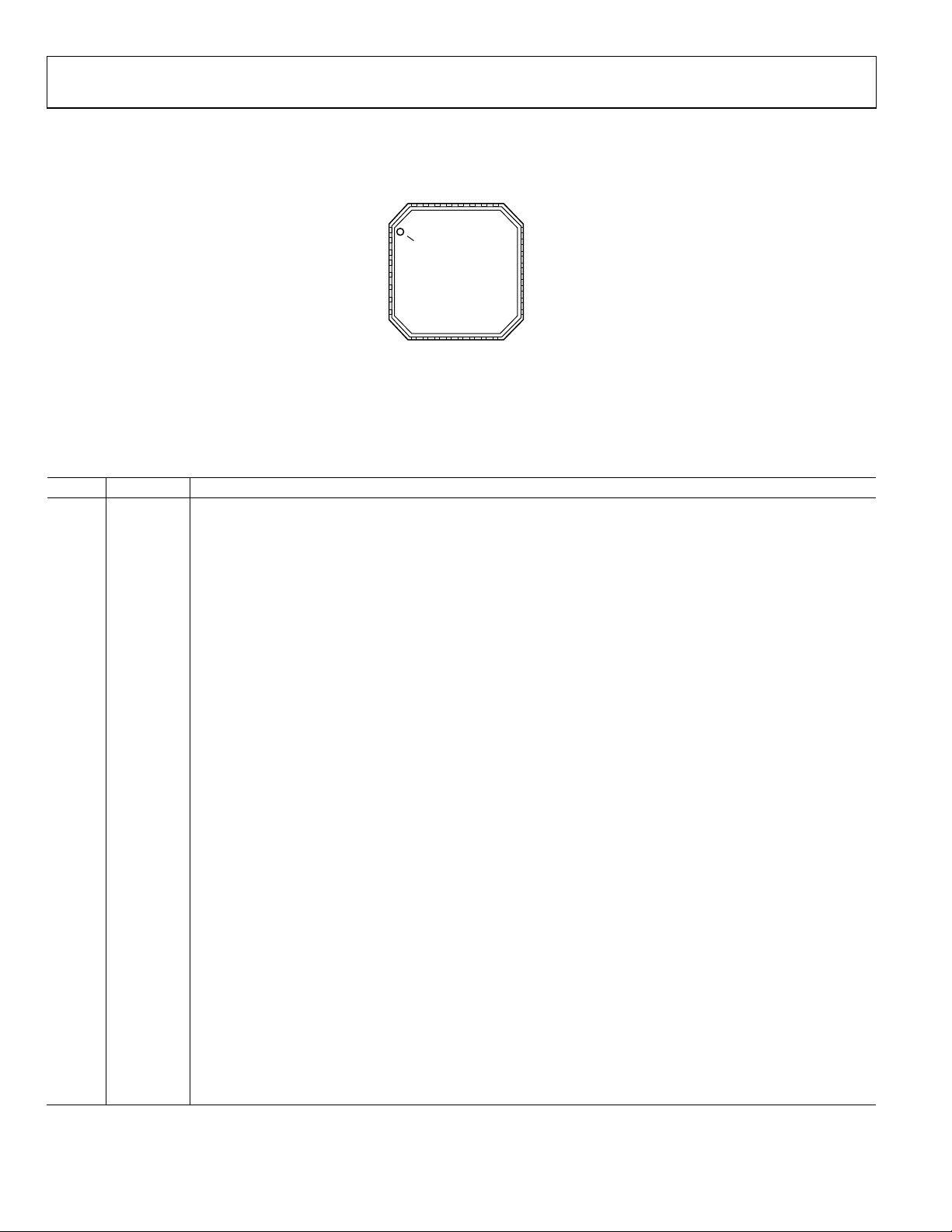

FUNCTIONAL BLOCK DIAGRAM

Low Phase Noise, Fast Settling PLL

GENERAL DESCRIPTION

The ADF4193 frequency synthesizer can be used to implement

local oscillators in the upconversion and downconversion

sections of wireless receivers and transmitters. Its architecture

is specifically designed to meet the GSM/EDGE lock time

requirements for base stations. It consists of a low noise, digital

phase frequency detector (PFD), and a precision differential

charge pump. There is also a differential amplifier to convert

the differential charge pump output to a single-ended voltage

for the external voltage-controlled oscillator (VCO).

The Σ-Δ based fractional interpolator, working with the N

divider, allows programmable modulus fractional-N division.

Additionally, the 4-bit reference (R) counter and on-chip

frequency doubler allow selectable reference signal (REFIN)

frequencies at the PFD input. A complete phase-locked loop

(PLL) can be implemented if the synthesizer is used with an

external loop filter and a VCO. The switching architecture

ensures that the PLL settles inside the GSM time slot guard

period, removing the need for a second PLL and associated

isolation switches. This decreases cost, complexity, PCB area,

shielding, and characterization on previous ping-pong GSM

PLL architectures.

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

ADF4193 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ........................................................................... 2

Specifications ..................................................................................... 3

Timing Characteristics ................................................................ 4

Absolute Maximum Ratings ............................................................ 5

ESD Caution .................................................................................. 5

Pin Configuration and Function Descriptions ............................. 6

Typical Performance Characteristics ............................................. 8

Theory of Operation ...................................................................... 11

Reference Input Section ............................................................. 11

RF Input Stage ............................................................................. 11

Register Map .................................................................................... 14

FRAC/INT Register (R0) ........................................................... 15

MOD/R Register (R1) ................................................................ 16

Phase Register (R2) .................................................................... 17

Function Register (R3) .............................................................. 18

Charge Pump Register (R4) ...................................................... 19

Power-Down Register (R5) ....................................................... 20

Mux Register (R6) ...................................................................... 21

Programming .................................................................................. 22

Worked Example ........................................................................ 22

Spur Mechanisms ....................................................................... 22

Power-Up Initialization ............................................................. 23

Changing the Frequency of the PLL and the Phase Look-Up

Table ............................................................................................. 23

Applications ..................................................................................... 25

Local Oscillator for A GSM Base Station ................................ 25

Interfacing ................................................................................... 27

PCB Design Guidelines for Chip Scale Package .................... 27

Outline Dimensions ....................................................................... 28

Ordering Guide .......................................................................... 28

Automotive Products ................................................................. 28

REVISION HISTORY

3/12—Rev. C to Rev. D

Changes to Noise Characteristics Parameter, Table 1 .................. 4

Change to Table 4 ............................................................................. 6

Updated Outline Dimensions ....................................................... 28

Changes to Ordering Guide .......................................................... 28

1/11—Rev. B to Rev. C

Changes to Features Section............................................................ 1

Changes to Table 1 ............................................................................ 3

Changes to Table 2 ............................................................................ 4

Changes to Ordering Guide .......................................................... 28

Added Automotive Products Paragraph...................................... 28

6/06—Rev A. to Rev. B

Changes to Table 1 ............................................................................ 3

Changes to Figure 32 ...................................................................... 18

Changes to Power-Up Initialization Section ............................... 23

Changes to Timer Values for Tx Section and Timer Values for

Rx Section ........................................................................................ 25

11/05—Rev 0. to Rev. A

Updated Format .................................................................. Universal

Changes to Features Section ............................................................ 1

Changes to Table 1 ............................................................................. 3

Changes to Reference Input Section ............................................ 11

Changes to RF N Divider Section ................................................ 11

Changes to the Lock Detect Section ............................................ 13

Changes to Figure 29 ...................................................................... 15

Changes to the 8-Bit INT Value Section ..................................... 15

Changes to Figure 33 ...................................................................... 19

Replaced Figure 35 ......................................................................... 21

Changes to the Σ-Δ and Lock Detect Modes Section ................ 21

Changes to the Power-Up Initialization Section ........................ 23

Changes to Table 8 .......................................................................... 23

Changes to the Local Oscillator for a GSM

Base Station Section ....................................................................... 25

Changes to the Timer Values for Rx Section .............................. 25

Changes to Figure 36 ...................................................................... 26

Updates to the Outline Dimensions............................................. 28

Changes to the Ordering Guide ................................................... 28

4/05—Revision 0: Initial Version

Rev. D | Page 2 of 28

Data Sheet ADF4193

RF CHARACTERISTICS

10 MHz, use a dc-coupled square wave

VCO Tuning Range

1.8/(VP3 − 0.8)

1.8/(VP3 − 0.8)

V min/max

SPECIFICATIONS

AVDD = DVDD = SDVDD = 3 V ± 10%, VP1, VP2 = 5 V ± 10%, VP3 = 5.35 V ± 5%, AGND = DGND = GND = 0 V, R

referred to 50 Ω, T

= T

A

MIN

to T

, unless otherwise noted.

MAX

Table 1.

Parameter B Version1 C Version2 Unit Test Conditions/Comments

RF Input Frequency (RFIN) 0.4/3.5 0.4/3.5 GHz min/max See Figure 21 for input circuit

RF Input Sensitivity −10/0 −10/0 dBm min/max

Maximum Allowable Prescaler

Output Frequency

3

470 470 MHz max

REFIN CHARACTERISTICS

REFIN Input Frequency 10/300 10/300 MHz min/max For f > 120 MHz, set REF/2 bit = 1. For f <

REFIN Edge Slew Rate 300 300 V/µs min

REFIN Input Sensitivity 0.7/VDD 0.7/VDD V p-p min/max AC-coupled

0 to VDD 0 to VDD V max CMOS-compatible

REFIN Input Capacitance 10 10 pF max

REFIN Input Current ±100 ±100 µA max

PHASE DETECTOR

Phase Detector Frequency 26 26 MHz max

CHARGE PUMP

ICP Up/Down

Hig h Value 6.6 6.6 mA typ With R

Low Value 104 104 µA typ With R

= 2.4 kΩ

SET

= 2.4 kΩ

SET

Absolute Accuracy 5 5 % typ

R

Range 1/4 1/4 kΩ min/max Nominally R

SET

= 2.4 kΩ

SET

ICP Three-State Leakage 1 1 nA typ

ICP Up vs. Down Matching 0.1 0.1 % typ 0.75 V ≤ VCP ≤ VP – 1.5 V

ICP vs. VCP 1 1 % typ 0.75 V ≤ VCP ≤ VP – 1.5 V

ICP vs. Temperature 1 1 % typ 0.75 V ≤ VCP ≤ VP – 1.5 V

DIFFERENTIAL AMPLIFIER

Input Current 1 1 nA typ

Output Voltage Range 1.4/(VP3 − 0.3) 1.4/(VP3 − 0.3) V min/max

= 2.4 kΩ, dBm

SET

Output Noise 7 7 nV/√Hz typ At 20 kHz offset

LOGIC INPUTS

VIH, Input High Voltage 1.4 1.4 V min

VIL, Input Low Voltage 0.7 0.7 V max

I

, I

, Input Current ±1 ±2 µA max

INH

INL

CIN, Input Capacitance 10 10 pF max

LOGIC OUTPUTS

VOH, Output High Voltage VDD − 0.4 VDD − 0.4 V min IOH = 500 µA

VOL, Output Low Voltage 0.4 0.4 V max IOL = 500 µA

POWER SUPPLIES

AVDD 2.7/3.3 2.7/3.3 V min/V max

DVDD AVDD AVDD

VP1, VP2 4.5/5.5 4.5/5.5 V min/V max AVDD ≤ VP1, VP2 ≤ 5.5 V

VP3 5.0/5.65 5.0/5.65 V min/V max VP1, VP2 ≤ VP3 ≤ 5.65 V

IDD (AVDD + DVDD + SDVDD) 27 35 mA max 22 mA typ

IDD (VP1 + VP2) 27 30 mA max 22 mA typ

IDD (VP3) 30 35 mA max 24 mA typ

IDD Power-Down 10 10 µA typ

Rev. D | Page 3 of 28

ADF4193 Data Sheet

Parameter B Version1 C Version2 Unit Test Conditions/Comments

SW1, SW2, and SW3

RON (SW1 and SW2) 65 65 Ω typ

RON SW3 75 75 Ω typ

NOISE CHARACTERISTICS

Output

900 MHz4 −108 −108 dBc/Hz typ At 5 kHz offset and 26 MHz PFD frequency

1800 MHz5 −102 −102 dBc/Hz typ At 5 kHz offset and 13 MHz PFD frequency

Phase Noise

Normalized Phase Noise

Floor (PN

SYNTH

)6

Normalized 1/f Noise (PN

1

Operating temperature range is from −40°C to +85°C.

2

Operating temperature range is from −40°C to +105°C

3

The prescaler value is chosen to ensure that the RF input is divided down to a frequency that is less than this value.

4

f

= 26 MHz; f

REF

IN

5

f

= 13 MHz; f

REF

IN

6

The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 log(N) (where N is the N divider

value) and 10 log(f

7

The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency,

= 200 kHz; fRF = 900 MHz; loop bandwidth = 40 kHz.

STEP

= 200 kHz; fRF = 1800 MHz; loop bandwidth = 60 kHz.

STEP

). PN

SYNTH

= PN

PFD

fRF, and at an offset frequency, f, is given by PN = P1_f + 10 log(10 kHz/f) + 20 log(fRF/1 GHz). Both the normalized phase noise floor and flicker noise are modeled in

ADIsimPLL™.

TIMING CHARACTERISTICS

AVDD = DVDD = 3 V ± 10%, VP1, VP2 = 5 V ± 10%, VP3 = 5.35 V ± 5%, AGND = DGND = GND = 0 V, R

50 Ω, T

= T

A

MIN

to T

, unless otherwise noted.

MAX

−216 −216 dBc/Hz typ

At VCO output with dither off, PLL loop

bandwidth = 500 kHz

)7 −110 −110 dBc/Hz typ Measured at 10 kHz offset, normalized to 1 GHz

1_f

− 10 log(f

TOT

) − 20 log(N).

PFD

= 2.4 kΩ, dBm referred to

SET

Table 2.

Parameter Limit (B Version)1 Limit (C Version) 2 Unit Test Conditions/Comments

t1 10 10 ns min LE setup time

t2 10 10 ns min DATA to CLOCK setup time

t3 10 10 ns min DATA to CLOCK hold time

t4 15 15 ns min CLOCK high duration

t5 15 15 ns min CLOCK low duration

t6 10 10 ns min CLOCK to LE setup time

t7 15 15 ns min LE pulse width

1

Operating temperature is from −40°C to +85°C.

2

Operating temperature is from −40°C to +105°C.

CLK

DATA

t

4

t

2

DB23

(MSB)

LE

t

1

t

3

DB22 DB2

t

5

DB1

(CONTROL BIT C2)

DB0 (LSB)

(CONTROL BIT C1)

t

7

t

6

LE

05238-002

Figure 2. Timing Diagram

Rev. D | Page 4 of 28

Data Sheet ADF4193

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 3.

Parameter Rating

AVDD to GND −0.3 V to +3.6 V

AVDD to DVDD, SDVDD −0.3 V to +0.3 V

VP to GND −0.3 V to +5.8 V

VP to AVDD −0.3 V to +5.8 V

Digital I/O Voltage to GND −0.3 V to VDD + 0.3 V

Analog I/O Voltage to GND −0.3 V to VP + 0.3 V

REFIN, RF

Operating Temperature Range

Industrial (B Version) −40°C to +85°C

Operating Temperature Range

Automotive (W Version)

Storage Temperature Range −65°C to +125°C

Maximum Junction Temperature 150°C

LFCSP θJA Thermal Impedance

(Paddle Soldered)

Reflow Soldering

Peak Temperature 260°C

Time at Peak Temperature 40 sec

, RF

to GND −0.3 V to VDD + 0.3 V

IN+

IN−

−40°C to +105°C

27.3°C/W

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

This device is a high performance RF integrated circuit with an

ESD rating of <2 kV, and it is ESD sensitive. Proper precautions

need to be taken for handling and assembly.

Transistor Count

75,800 (MOS), 545 (BJT).

ESD CAUTION

Rev. D | Page 5 of 28

ADF4193 Data Sheet

05328-003

1

CMR

2

A

OUT

3

SW3

NOTES:

1. THE EXPOSED P

AD MUST BE CONNE CTED TO AGND.

4

A

GND

1

5

RF

IN–

6

RF

IN+

7

AV

DD

1

24

VP2

23

R

SET

22

A

GND

2

21

D

GND

3

20

VP1

19

LE

18

DATA

17

CLK

8

DV

DD

1

ADF4193

TOP VIEW

9

D

GND

1

10

DV

DD

2

11

REF

IN

12

D

GND

2

13

DV

DD

3

14

SD

GND

15

SDV

DD

16

MUX

OUT

32

V

P

3

31

AIN+

30

CP

OUT+

29

SW1

28

SW

GND

27

SW226CP

OUT–

25

AIN–

PIN 1

INDICATOR

21

D

3

Ground Return Pin for VP1.

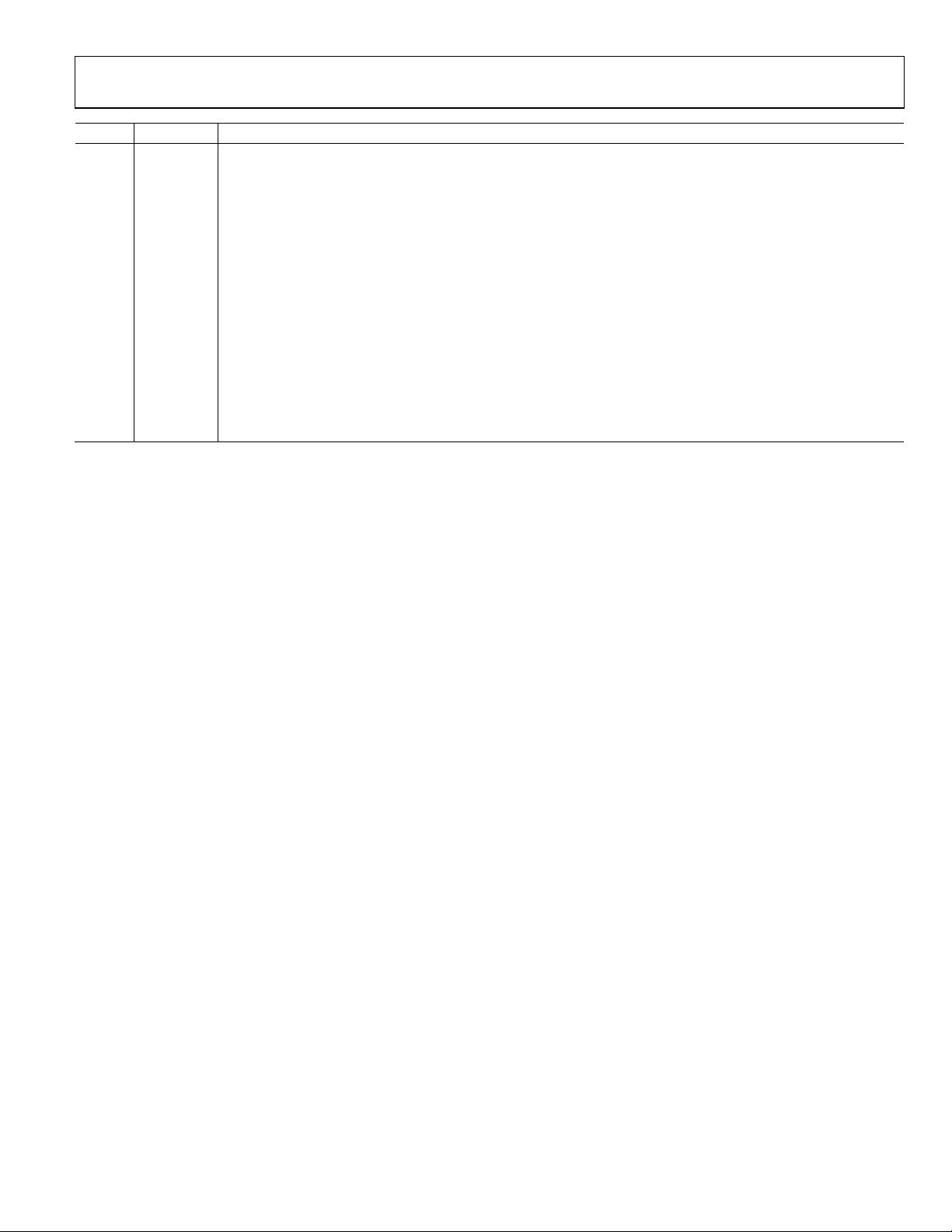

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

Table 4. Pin Function Descriptions

Pin N o. Mnemonic Description

1 CMR Common-Mode Reference Voltage for the Differential Amplifier’s Output Voltage Swing. Internally biased to

2 A

three-fifths of V

Differential Amplifier Output to Tune the External VCO.

OUT

3. Requires a 0.1 µF capacitor to ground.

P

3 SW3 Fast-Lock Switch 3. Closed while SW3 timeout counter is active.

4 A

5 RF

1 Analog Ground. This is the ground return pin for the differential amplifier and the RF section.

GND

Complementary Input to the RF Prescaler. This point must be decoupled to the ground plane with a small bypass

IN−

capacitor, typically 100 pF.

6 RF

Input to the RF Prescaler. This small signal input is ac-coupled to the external VCO.

IN+

7 AVDD1 Power Supply Pin for the RF Section. Nominally 3 V. A 100 pF decoupling capacitor to the ground plane should be

placed as close as possible to this pin.

8 DVDD1 Power Supply Pin for the N Divider. Should be the same voltage as AVDD1. A 0.1 µF decoupling capacitor to ground

should be placed as close as possible to this pin.

9 D

1 Ground Return Pin for DVDD1.

GND

10 DVDD2 Power Supply Pin for the REFIN Buffer and R Divider. Nominally 3 V. A 0.1 µF decoupling capacitor to ground

should be placed as close as possible to this pin.

11 REFIN Reference Input. This is a CMOS input with a nominal threshold of VDD/2 and a dc equivalent input resistance of

100 kΩ (see Figure 15). This input can be driven from a TTL or CMOS crystal oscillator or it can be ac-coupled.

12 D

2 Ground Return Pin for DVDD2 and DVDD3.

GND

13 DVDD3 Power Supply Pin for the Serial Interface Logic. Nominally 3 V.

14 SD

Ground Return Pin for the Σ-Δ Modulator.

GND

15 SDVDD Power Supply Pin for the Digital Σ-Δ Modulator. Nominally 3 V. A 0.1 µF decoupling capacitor to the ground plane

should be placed as close as possible to this pin.

16 MUX

Multiplexer Output. This multiplexer output allows either the lock detect, the scaled RF, or the scaled reference

OUT

frequency to be accessed externally (see Figure 35).

17 CLK Serial Clock Input. Data is clocked into the 24-bit shift register on the CLK rising edge. This input is a high

impedance CMOS input.

18 DATA Serial Data Input. The serial data is loaded MSB first with the three LSBs as the control bits. This input is a high

19 LE Load Enable, CMOS Input. When LE goes high, the data stored in the shift register is loaded into the register that is

20 VP1 Power Supply Pin for the Phase Frequency Detector (PFD). Nominally 5 V, should be at the same voltage at VP2.

22 A

impedance CMOS input.

selected by the three LSBs.

A 0.1 µF decoupling capacitor to ground should be placed as close as possible to this pin.

GND

2 Ground Return Pin for VP2.

GND

Rev. D | Page 6 of 28

Data Sheet ADF4193

29

SW1

Fast Lock Switch 1. This switch is closed to SW

while the SW1/SW2 timeout counter is active.

Pin N o. Mnemonic Description

23 R

24 VP2 Power Supply Pin for the Charge Pump. Nominally 5 V, should be at the same voltage at VP1. A 0.1 µF decoupling

25 AIN− Differential Amplifier’s Negative Input Pin.

26 CP

27 SW2 Fast Lock Switch 2. This switch is closed to SW

28 SW

30 CP

31 AIN+ Differential Amplifier’s Positive Input Pin.

32 VP3 Power Supply Pin for the Differential Amplifier. This can range from 5.0 V to 5.5 V. A 0.1 µF decoupling capacitor to

EP Exposed Pad. The exposed pad must be connected to AGND.

Connecting a resistor between this pin and GND sets the charge pump output current. The nominal voltage bias at

SET

the R

pin is 0.55 V. The relationship between ICP and R

SET

ICP = 0.25/R

So, with R

SET

SET

= 2.4 kΩ, ICP = 104 µA.

SET

is

capacitor to ground should be placed as close as possible to this pin.

Differential Charge Pump’s Negative Output Pin. Should be connected to AIN− and the loop filter.

OUT−

while the SW1/SW2 timeout counter is active.

GND

Common for SW1 and SW2 Switches. Should be connected to the ground plane.

GND

GND

Differential Charge Pump’s Positive Output Pin. Should be connected to AIN+ and the loop filter.

OUT+

ground should be placed as close as possible to this pin. Also requires a 10 µF decoupling capacitor to ground.

Rev. D | Page 7 of 28

ADF4193 Data Sheet

–

–

TYPICAL PERFORMANCE CHARACTERISTICS

FREQ. UNIT GHz KEYWORD R

PARAM TYPE S IMPEDANCE 50

DATA FORMAT MA

FREQ. MAGS11 ANGS11

0.5 0.8897 –16.6691

0.6 0.87693 –19.9279

0.7 0.85834 –23.561

0.8 0.85044 –26.9578

0.9 0.83494 –30.8201

1.0 0.81718 –34.9499

1.1 0.80229 –39.0436

1.2 0.78917 –42.3623

1.3 0.77598 –46.322

1.4 0.75578 –50.3484

1.5 0.74437 –54.3545

1.6 0.73821 –57.3785

1.7 0.7253 –60.695

1.8 0.71365 –63.9152

1.9 0.70699 –66.4365

2.0 0.7038 –68.4453

2.1 0.69284 –70.7986

2.2 0.67717 –73.7038

FREQ. MAGS11 ANGS11

2.3 0.67107 –75.8206

2.4 0.66556 –77.6851

2.5 0.6564 –80.3101

2.6 0.6333 –82.5082

2.7 0.61406 –85.5623

2.8 0.5977 –87.3513

2.9 0.5655 –89.7605

3.0 0.5428 –93.0239

3.1 0.51733 –95.9754

3.2 0.49909 –99.1291

3.3 0.47309 –102.208

3.4 0.45694 –106.794

3.5 0.44698 –111.659

3.6 0.43589 –117.986

3.7 0.42472 –125.62

3.8 0.41175 –133.291

3.9 0.41055 –140.585

4.0 0.40983 –147.97

Figure 4. S Parameter Data for the RF Input

30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

PHASE NOISE (dBc/Hz)

–140

–150

–160

–170

1k 10k 100k 1M 10M

GSM900 Rx SETUP, 40kHz LO OP BW, DITHER OF F

RF = 1092.8MHz, F

N = 42 4/130

INTEGER BO UNDARY SPUR: –103dBc @ 800kHz

= 26MHz, MO D = 130

REF

FREQUENCY (Hz)

100M

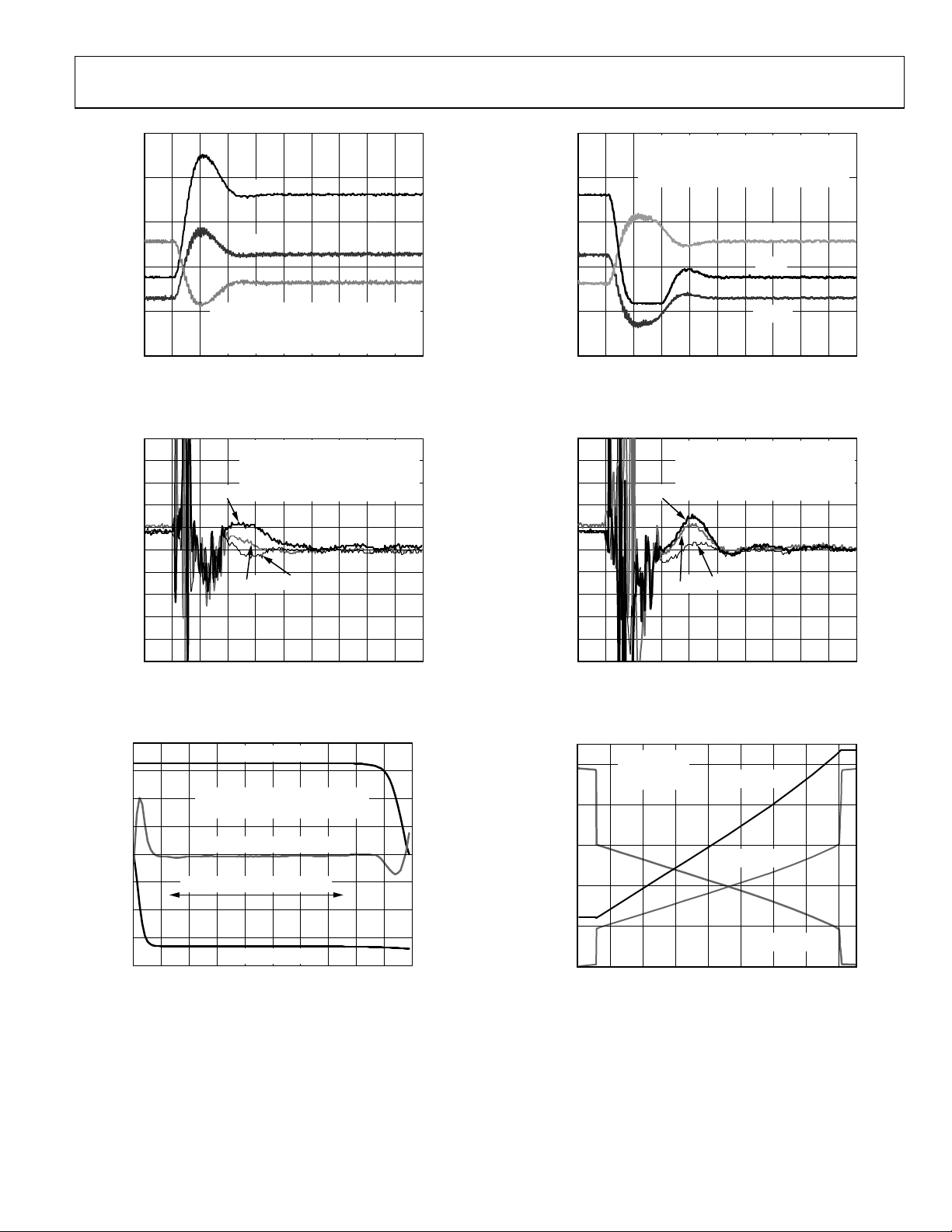

Figure 5. SSB Phase Noise Plot at 1092.8 MHz (GSM900 Rx Setup) vs.

Free Running VCO Noise

–60

DCS1800 Tx SETUP WITH DITHER OFF,

60kHz LOOP BW, 13MHz PFD.

MEASURED ON EVAL-ADF4193-EB1 BOARD

–70

400kHz SPURS @ 25C

05328-038

05328-006

0

–5

–10

–15

–20

LEVEL (dBm)

IN

RF

–25

–30

–35

0 1000 2000 3000 4000

4/5 PRESCALER

8/9 PRESCALER

5000

RFIN FREQUENCY (MHz)

Figure 7. RF Input Sensitivity

30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

PHASE NOISE (dBc/Hz)

–140

–150

–160

–170

1k 10k 100k 1M 10M

DCS1800 Tx SETUP, 60kHz LOO P BW, DIT HER OFF

RF = 1842.6MHz, F

DSB INTEGRATED PHASE ERROR = 0.46° RMS

SIRENZA 1843T VCO

= 13MHz, MOD = 65

REF

FREQUENCY (Hz)

100M

Figure 8. SSB Phase Noise Plot at 1842.6 MHz (DCS1800 Tx Setup)

–60

DCS1800 Tx SETUP WITH DITHER OFF,

60kHz LOOP BW, 13MHz PFD.

MEASURED ON EVAL-ADF4193-EB1 BOARD

–70

05328-005

05328-007

–80

–90

–100

SPUR LEVEL (dBc)

–110

–120

1846 1859

FREQUENCY (MHz)

400kHz SPURS @ 85C

05328-010

1872

Figure 6. 400 kHz Fractional Spur Levels Across All DCS1800 Tx Channels

Over Two-Integer Multiples of the PFD Reference

–80

–90

–100

SPUR LEVEL (dBc)

–110

–120

1846 1859

FREQUENCY (MHz)

600kHz SPURS @ 25C

600kHz SPURS @ 85

C

05328-011

1872

Figure 9. 600 kHz Fractional Spur Levels Across All DCS1800 Tx Channels

Over Two-Integer Multiples of the PFD Reference

Rev. D | Page 8 of 28

Data Sheet ADF4193

05328-040

TIME (µs)

(V)

–1

0

1

2

3

4

5

9876543210

V

TUNE

CP

OUT+

CP

OUT–

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

FREQUENCY LOCK IN WIDE BW MODE @ 4µs.

05328-008

TIME (µs)

PHASE ERROR (Degrees)

–5 0 5 10 15 20 25 30 35 40

–50

50

40

30

20

10

0

–10

–20

–30

–40

45

+25°C

+85°C

–40°C

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD WITH AD8302

PHASE DETECTOR.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

PEAK PHASE ERROR < 5° @ 17.8µs

05328-012

CP

OUT

+ / CP

OUT

– VOLTAGE (V)

I

CP

(mA)

MISMATCH ( %)

0 0.5 1.0 1.5 2.0 2.5

3.0 3.5 4.0 4.5

–8

–6

–4

–2

0

2

4

6

8

–2.0

–1.5

–1.0

–0.5

0

0.5

1.0

1.5

2.0

5.0

ICP

OUT

+ P, ICP

OUT

– P

CHARGE PUMP MISMATCH (%)

NORMAL OP E RATING RANGE

ICP

OUT

+ N, ICP

OUT

– N

IUP= | ICP

OUT

+ P | + | ICP

OUT

– N |

I

DOWN

= | ICP

OUT

– P | + | ICP

OUT

+ N |

05328-041

TIME (µs)

(V)

–1

0

1

2

3

4

5

9876543210

V

TUNE

CP

OUT–

CP

OUT+

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

FREQUENCY LOCK IN WIDE BW MODE @ 5µs.

05328-009

TIME (µs)

PHASE ERROR (Degrees)

–5 0 5 10 15 20 25 30 35 40

–50

50

40

30

20

10

0

–10

–20

–30

–40

45

+25°C

+85°C

–40°C

DCS1800 Tx SETUP, 60kHz LOOP BW.

MEASURED ON EVAL-ADF4193-EB1

EVALUATION BOARD WITH AD8302

PHASE DETECTOR.

TIMERS: ICP = 28, SW1/SW2, SW3 = 35.

PEAK PHASE ERROR < 5° @ 19.2µs

05328-013

FREQUENCY (MHz)

(V)

1780 1800 1820 1840 1860 1880 1900 1920 1940

0

2

1

3

4

5

VP1 = VP2 = 5V

V

P

3 = 5.5V

V

CMR

= 3.3V

CP

OUT–

(= AIN–)

A

OUT

(= V

TUNE

)

CP

OUT+

(= AIN+)

Figure 10. V

Settling Transient for a 75 MHz Jump from 1818 MHz to

TUNE

1893 MHz with Sirenza 1843T VCO

Figure 11. Phase Settling Transient for a 75 MHz Jump from 1818 MHz to

1893 MHz (V

1.8 V to 3.7 V with Sirenza 1843T VCO)

TUNE

Figure 13. V

Settling Transient for a 75 MHz Jump Down from 1893 MHz to

TUNE

1818 MHz, the Bottom of the A llowed Tuning Range with the Sirenza 1843T VCO

Figure 14. Phase Settling Transient for a 75 MHz Jump from 1893 MHz to

1818 MHz (V

= 3.7 V to 1.8 V with Sirenza 1843T VCO)

TUNE

Figure 12. Differential Charge Pump Output Compliance Range and

Charge Pump Mismatch with V

1 = VP2 = 5 V

P

Figure 15. Tuning Range with a Sirenza 1843T VCO and a 5.5 V Differential

Amplifier Power Supply Voltage

Rev. D | Page 9 of 28

Loading...

Loading...