a

PLL Frequency Synthesizer

ADF4106

FEATURES

6.0 GHz Bandwidth

2.7 V to 3.3 V Power Supply

Separate Charge Pump Supply (V

) Allows Extended

P

Tuning Voltage in 3 V Systems

Programmable Dual Modulus Prescaler

8/9, 16/17, 32/33, 64/65

Programmable Charge Pump Currents

Programmable Anti-Backlash Pulsewidth

3-Wire Serial Interface

Analog and Digital Lock Detect

Hardware and Software Power-Down Mode

APPLICATIONS

Broadband Wireless Access

Instrumentation

Wireless LANS

Base Stations For Wireless Radio

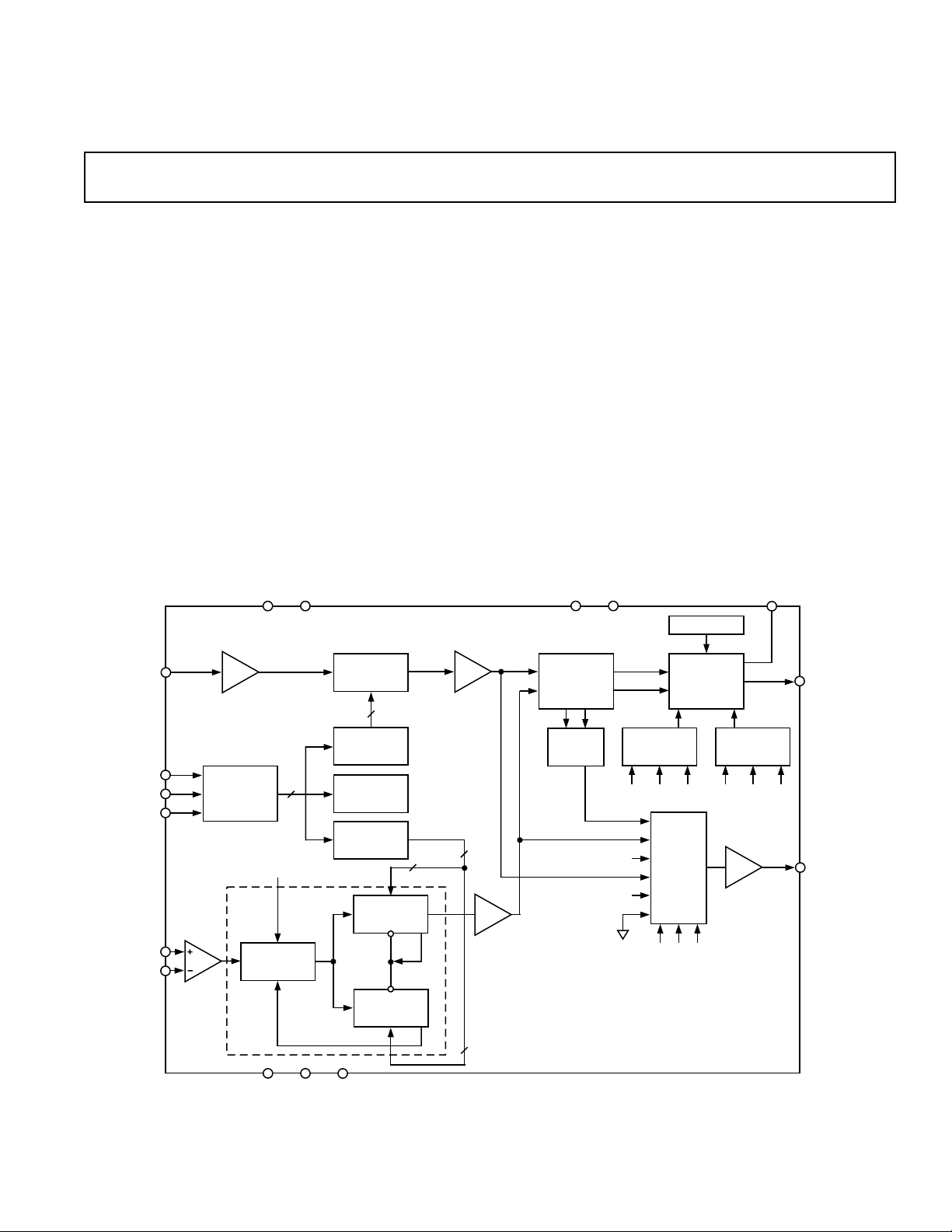

FUNCTIONAL BLOCK DIAGRAM

AV

DV

DD

DD

REF

IN

14-BIT

R COUNTER

14

GENERAL DESCRIPTION

The ADF4106 frequency synthesizer can be used to implement

local oscillators in the up-conversion and down-conversion

sections of wireless receivers and transmitters. It consists of a

low-noise digital PFD (Phase Frequency Detector), a precision

charge pump, a programmable reference divider, programmable

A and B counters and a dual-modulus prescaler (P/P + 1). The

A (6-bit) and B (13-bit) counters, in conjunction with the dual

modulus prescaler (P/P + 1), implement an N divider (N = BP + A).

In addition, the 14-bit reference counter (R Counter), allows

selectable REFIN frequencies at the PFD input. A complete

PLL (Phase-Locked Loop) can be implemented if the synthesizer is used with an external loop filter and VCO (Voltage

Controlled Oscillator). Its very high bandwidth means that

frequency doublers can be eliminated in many high-frequency

systems, simplifying system architecture and lowering cost.

V

P

PHASE

FREQUENCY

DETECTOR

CPGND

REFERENCE

CHARGE

PUMP

R

SET

CP

R COUNTER

LATCH

CLK

DATA

LE

RFINA

RF

B

IN

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

24-BIT INPUT

REGISTER

FUNCTION

PRESCALER

FROM

LATCH

P/P + 1

CE

22

N = BP + A

AGND

FUNCTION

LATCH

AB COUNTER

LATCH

B COUNTER

LOAD

LOAD

A COUNTER

DGND

13

13-BIT

6-BIT

LOCK

DETECT

19

CURRENT

SETTING 1

CPI3 CPI2 CPI1 CPI6 CPI5 CPI4

AV

SD

DD

OUT

MUX

M3 M2 M1

CURRENT

SETTING 2

HIGH Z

MUXOUT

ADF4106

6

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

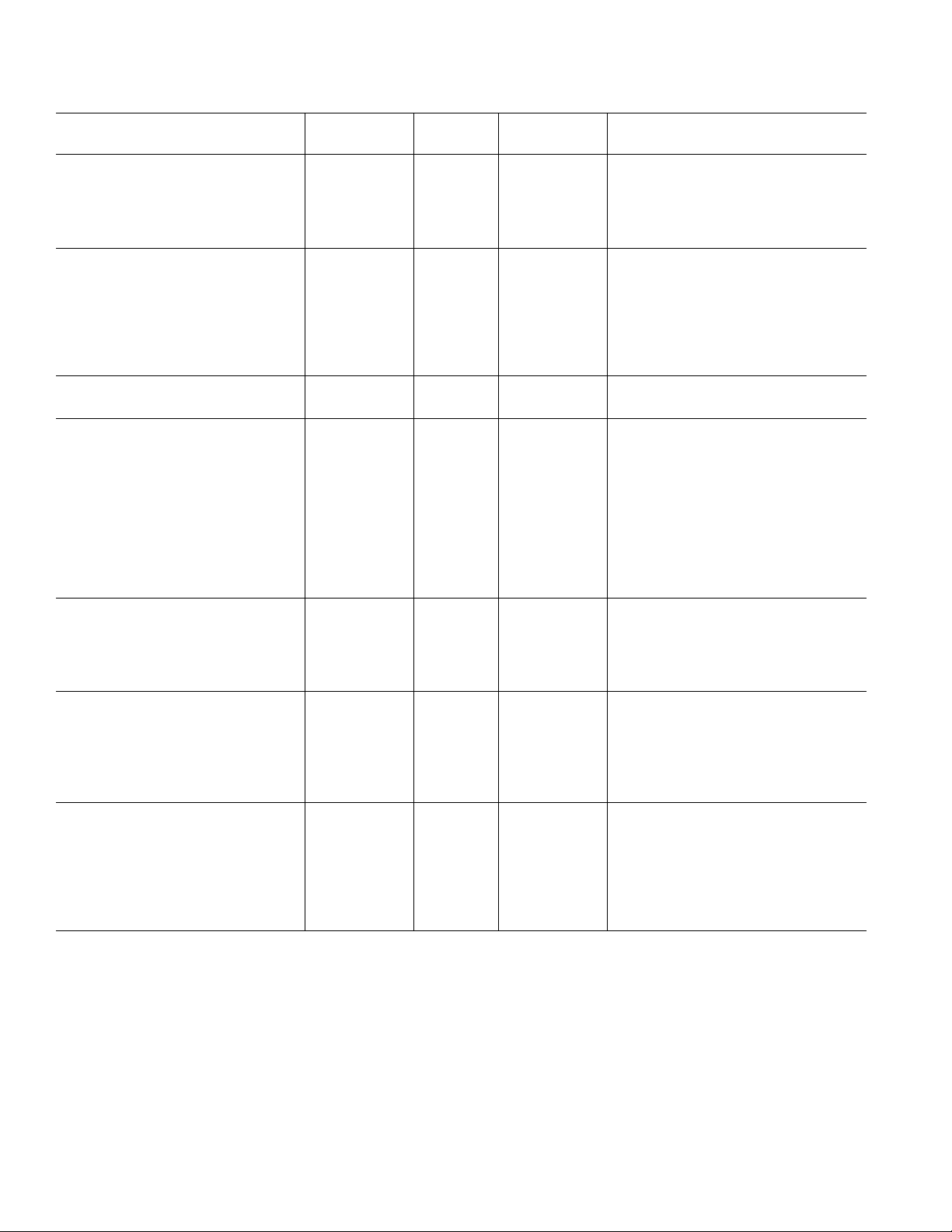

ADF4106–SPECIFICATIONS

(AV

= DVDD = 3 V 10%; AVDD ≤ VP ≤ 5.5 V; AGND = DGND = CPGND = 0 V;

DD

1

R

= 5.1 k; dBm referred to 50 ; TA = T

SET

MIN

to T

unless otherwise noted.)

MAX

Parameter B Version

RF CHARACTERISTICS See Figure 3 for Input Circuit

RF Input Frequency (RF

3

)

IN

0.5/6.0 0.5/6.0 GHz min/max

1

BChips

(typ) Unit Test Conditions/Comments

2

RF Input Sensitivity –10/0 –10/0 dBm min/max

Maximum Allowable

Prescaler Output Frequency

4

300 300 MHz max

REFIN CHARACTERISTICS

REFIN Input Frequency 20/250 20/250 MHz min/max For f < 20 MHz, Use DC-Coupled

REFIN Input Sensitivity

5

0.8/AV

DD

0.8/AV

V p-p min/max AC-Coupled; When DC-Coupled,

DD

Square Wave, (0 to V

0 to V

max (CMOS Compatible)

DD

DD

)

REFIN Input Capacitance 10 10 pF max

REFIN Input Current ± 100 ±100 µA max

PHASE DETECTOR

Phase Detector Frequency

6

56 56 MHz max

CHARGE PUMP

ICP Sink/Source Programmable, See Table V

High Value 5 5 mA typ With R

= 5.1 kΩ

SET

Low Value 625 625 µA typ

Absolute Accuracy 2.5 2.5 % typ With R

Range 2.7/10 2.7/10 kΩ typ See Table V

R

SET

I

Three-State Leakage Current 1 1 nA typ

CP

Sink and Source Current Matching 2 2 % typ 0.5 V ⱕ V

I

CP

vs. V

CP

1.5 1.5 % typ 0.5 V ⱕ VCP ⱕ VP – 0.5 V

= 5.1 kΩ

SET

ⱕ VP – 0.5 V

CP

ICP vs. Temperature 2 2 % typ VCP = VP/2

LOGIC INPUTS

V

, Input High Voltage 1.4 1.4 V min

INH

, Input Low Voltage 0.6 0.6 V max

V

INL

I

, Input Current ± 1 ± 1 µA max

INH/IINL

CIN, Input Capacitance 10 10 pF max

LOGIC OUTPUTS

VOH, Output High Voltage 1.4 1.4 V min Open Drain Output Chosen 1 kΩ

Pull-up to 1.8 V

, Output High Voltage 1.4 1.4 V min CMOS Output Chosen

V

OH

I

OH

100 100 µA max

VOL, Output Low Voltage 0.4 0.4 V max IOL = 500 µA

POWER SUPPLIES

AV

DD

DV

DD

V

P

7

(AIDD + DIDD) 15 13 mA max 13 mA typ

I

DD

I

P

2.7/3.3 2.7/3.3 V min/V max

AV

DD

AV

DD

AVDD/5.5 AVDD/5.5 V min/V max AVDD ⱕ VP ⱕ 5.5 V

0.4 0.4 mA max TA = 25°C

Power-Down Mode8 (AIDD + DIDD)10 10 µA typ

–2–

REV. 0

ADF4106

BChips

2

Parameter B Version1(typ) Unit Test Conditions/Comments

NOISE CHARACTERISTICS

ADF4106 Phase Noise Floor

9

–174 –174 dBc/Hz typ @ 25 kHz PFD Frequency

–166 –166 dBc/Hz typ @ 200 kHz PFD Frequency

Phase Noise Performance

900 MHz Output

5800 MHz Output

5800 MHz Output

Spurious Signals

900 MHz Output

5800 MHz Output

5800 MHz Output

NOTES

1

Operating temperature range (B Version) is –40°C to +85°C.

2

The BChip specifications are given as typical values.

3

Use a square wave for lower frequencies, below the mimimum stated.

4

This is the maximum operating frequency of the CMOS counters. The prescaler value should be chosen to ensure that the RF input is divided down to a frequency

that is less than this value.

5

AVDD = DVDD = 3 V

6

Guaranteed by design. Sample tested to ensure compliance.

7

TA = 25°C; AVDD = DVDD = 3 V; P = 16; RFIN = 6.0 GHz

8

TA = 25°C; AVDD = DVDD = 3.3 V; R = 16383; A = 63; B = 891; P = 32; RFIN = 6.0 GHz

9

The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20logN (where N is the N divider value).

10

The phase noise is measured with the EVAL-ADF4106EB1 Evaluation Board and the HP8562E Spectrum Analyzer. The spectrum analyzer provides the REFIN for

the synthesizer (f

11

f

= 10 MHz; f

REFIN

12

f

= 10 MHz; f

REFIN

13

f

= 10 MHz; f

REFIN

Specifications subject to change without notice.

REFOUT

= 200 kHz; Offset Frequency = 1 kHz; fRF = 900 MHz; N = 4500; Loop B/W = 20 kHz

PFD

= 200 kHz; Offset Frequency = 1 kHz; fRF = 5800 MHz; N = 29000; Loop B/W = 20 kHz

PFD

= 1 MHz; Offset Frequency = 1 kHz; fRF = 5800 MHz; N = 5800; Loop B/W = 100 kHz

PFD

10

11

12

13

11

12

13

= 10 MHz @ 0 dBm).

–159 –159 dBc/Hz typ @ 1 MHz PFD Frequency

@ VCO Output

–93 –93 dBc/Hz typ @ 1 kHz Offset and 200 kHz PFD Frequency

–74 –74 dBc/Hz typ @ 1 kHz Offset and 200 kHz PFD Frequency

–84 –84 dBc/Hz typ @ 1 kHz Offset and 1 MHz PFD Frequency

–90/–92 –90/–92 dBc typ @ 200 kHz/400 kHz and 200 kHz PFD Frequency

–65/–70 –65/–70 dBc typ @ 200 kHz/400 kHz and 200 kHz PFD Frequency

–70/–75 –70/–75 dBc typ @ 1 MHz/2 MHz and 1 MHz PFD Frequency

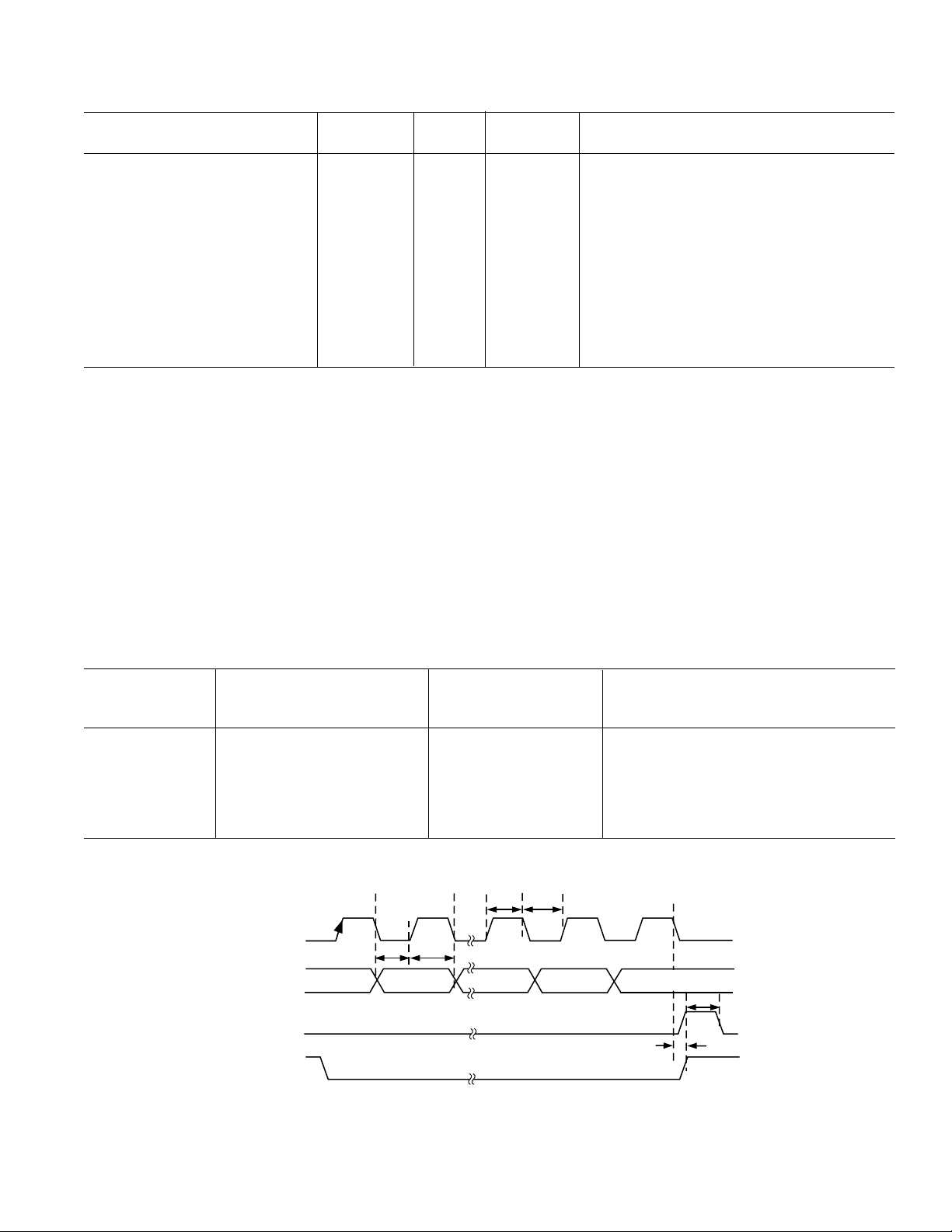

(AV

TIMING CHARACTERISTICS

= DVDD = 3 V 10%; AVDD ≤ VP ≤ 5.5 V; AGND = DGND = CPGND = 0 V; R

DD

TA = T

MIN

to T

unless otherwise noted.)

MAX

= 5.1 k;

SET

Limit at

to T

T

MIN

MAX

Parameter (B Version) Unit Test Conditions/Comments

t

1

t

2

t

3

t

4

t

5

t

6

Guaranteed by design but not production tested.

10 ns min DATA to CLOCK Setup Time

10 ns min DATA to CLOCK Hold Time

25 ns min CLOCK High Duration

25 ns min CLOCK Low Duration

10 ns min CLOCK to LE Setup Time

20 ns min LE Pulsewidth

t

t

3

4

CLOCK

DATA

LE

LE

DB23 (MSB)

t

t

2

1

DB22

DB2

DB1 (CONTROL

BIT C2)

DB0 (LSB)

(CONTROL BIT C1)

t

5

t

6

REV. 0

Figure 1. Timing Diagram

–3–

ADF4106

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

(TA = 25°C unless otherwise noted.)

1, 2

AVDD to GND3 . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +3.6 V

AV

to DVDD . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

DD

to GND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +5.3 V

V

P

V

to AVDD . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +5.5 V

P

Digital I/O Voltage to GND . . . . . . . . –0.3 V to V

Analog I/O Voltage to GND . . . . . . . . . –0.3 V to V

REF

, RFINA, RFINB to GND . . . . . . –0.3 V to VDD + 0.3 V

IN

+ 0.3 V

DD

+ 0.3 V

P

Operating Temperature Range

Industrial (B Version) . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Maximum Junction Temperature . . . . . . . . . . . . . . . . 150°C

TSSOP

CSP

Thermal Impedance . . . . . . . . . . . . . 150.4°C/W

JA

Thermal Impedance . . . . . . . . . . . . . . . . . . 122°C/W

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . 215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

This device is a high-performance RF integrated circuit with an ESD rating of

<2 kV and it is ESD sensitive. Proper precautions should be taken for handling and

assembly.

3

GND = AGND = DGND = 0 V

ORDERING GUIDE

Model Temperature Range Package Option*

ADF4106BRU –40°C to +85°C RU-16

ADF4106BCP –40°C to +85°C CP-20

*RU = Thin Shrink Small Outline Package (TSSOP)

CP = Chip Scale Package

Contact the factory for chip availability.

Note that aluminum bond wire should not be used with the ADF4106 die.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

ADF4106 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

–4–

REV. 0

PIN CONFIGURATIONS

ADF4106

R

SET

CP

CPGND

AGND

RF

IN

RF

IN

AV

REF

B

A

DD

IN

TSSOP

1

2

3

ADF4106

4

TOP VIEW

5

(Not to Scale)

6

7

8

16

V

15

DV

14

MUXOUT

13

LE

12

DATA

11

CLK

10

CE

9

DGND

P

DD

NOTE: TRANSISTOR COUNT 6425 (CMOS), 303 (BIPOLAR)

Chip Scale Package

SET

20 CP

19 R

CPGND 1

AGND 2

AGND 3

RFINB 4

A 5

RF

IN

PIN 1

INDICATOR

ADF4106

TOP VIEW

6

7

DD

DD

AV

AV

18 VP17 DVDD16 DV

8

IN

REF

DGND 9

DD

15 MUXOUT

14 LE

13 DATA

12 CLK

11 CE

DGND 10

PIN FUNCTION DESCRIPTIONS

Mnemonic Function

R

SET

CP Charge Pump Output. When enabled this provides ±I

Connecting a resistor between this pin and CPGND sets the maximum charge pump output current. The nominal

voltage potential at the R

So, with R

= 5.1 kΩ, I

SET

pin is 0.6 V. The relationship between ICP and R

SET

25 5.

=

R

SET

to the external loop filter, which in turn drives the

CP

CPMAX

= 5 mA.

I

CP MAX

SET

is

external VCO.

CPGND Charge Pump Ground. This is the ground return path for the charge pump.

AGND Analog Ground. This is the ground return path of the prescaler.

RF

B Complementary Input to the RF Prescaler. This point must be decoupled to the ground plane with a small bypass

IN

capacitor, typically 100 pF. See Figure 3.

RF

A Input to the RF Prescaler. This small signal input is ac coupled to the external VCO.

IN

AV

REF

DD

IN

Analog Power Supply. This may range from 2.7 V to 3.3 V. Decoupling capacitors to the analog ground plane

should be placed as close as possible to this pin. AV

must be the same value as DVDD.

DD

Reference Input. This is a CMOS input with a nominal threshold of VDD/2 and a dc equivalent input resistance of

100 kΩ. See Figure 2. This input can be driven from a TTL or CMOS crystal oscillator or it can be ac coupled.

DGND Digital Ground

CE Chip Enable. A logic low on this pin powers down the device and puts the charge pump output into three-state

mode. Taking the pin high will power up the device depending on the status of the power-down bit F2.

CLK Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the

24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.

DATA Serial Data Input. The serial data is loaded MSB first with the two LSBs being the control bits. This input is a

high impedance CMOS input.

LE Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four

latches, the latch being selected using the control bits.

MUXOUT This multiplexer output allows either the Lock Detect, the scaled RF or the scaled Reference Frequency to be

accessed externally.

DV

V

P

DD

Digital Power Supply. This may range from 2.7 V to 3.3 V. Decoupling capacitors to the digital ground plane

should be placed as close as possible to this pin. DV

must be the same value as AVDD.

DD

Charge Pump Power Supply. This should be greater than or equal to VDD. In systems where VDD is 3 V, it can be

set to 5 V and used to drive a VCO with a tuning range of up to 5 V.

REV. 0

–5–

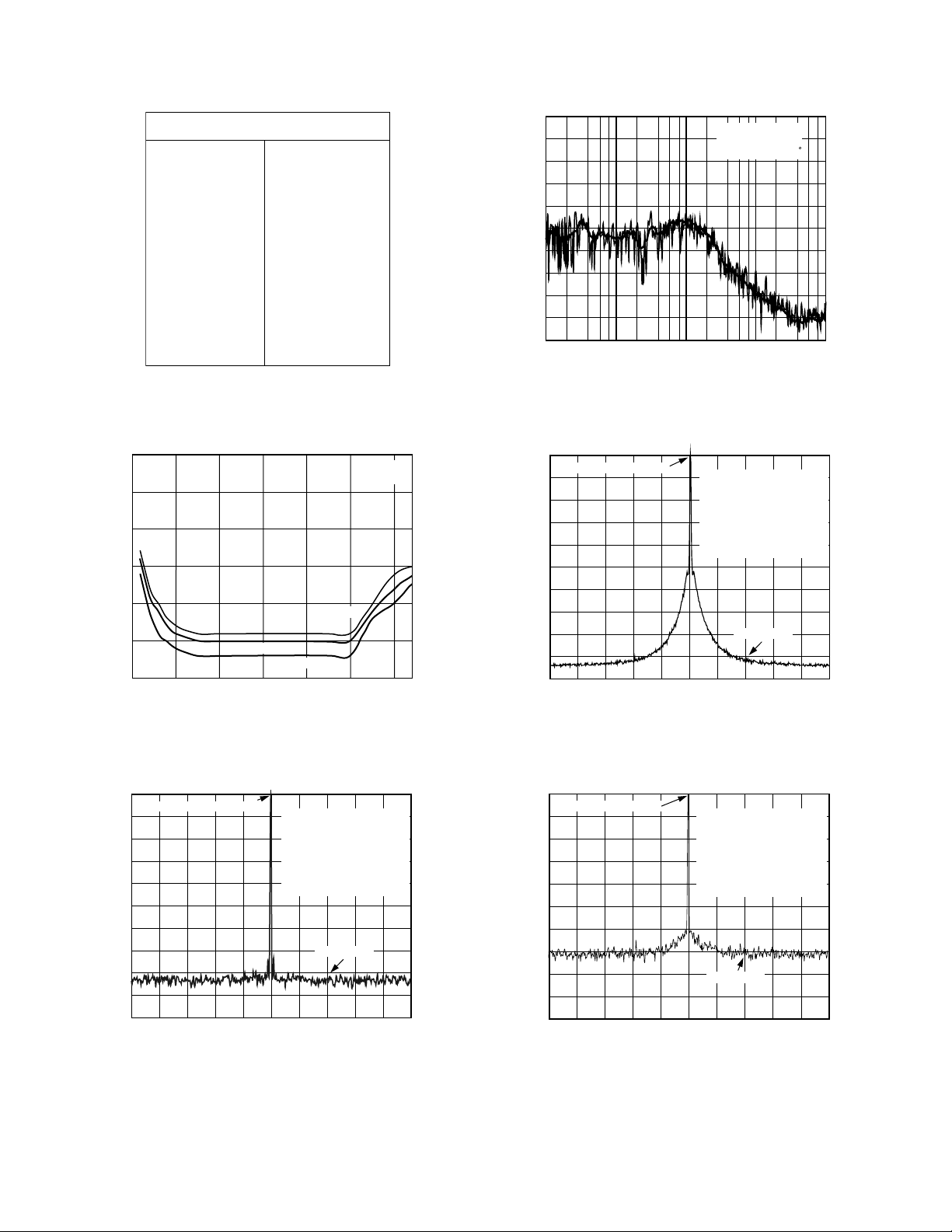

ADF4106–Typical Performance Characteristics

FREQ UNIT – GHz

PARAM TYPE – S

DATA FORMAT – MA

FREQ MAGS11 ANGS11

0.500 0.89148 – 17.2820

0.600 0.88133 – 20.6919

0.700 0.87152 – 24.5386

0.800 0.85855 – 27.3228

0.900 0.84911 – 31.0698

1.000 0.83512 – 34.8623

1.100 0.82374 – 38.5574

1.200 0.80871 – 41.9093

1.300 0.79176 – 45.6990

1.400 0.77205 – 49.4185

1.500 0.75696 – 52.8898

1.600 0.74234 – 56.2923

1.700 0.72239 – 60.2584

1.800 0.69419 – 63.1446

1.900 0.67288 – 65.6464

2.000 0.66227 – 68.0742

2.100 0.64758 – 71.3530

2.200 0.62454 – 75.5658

2.300 0.59466 – 79.6404

2.400 0.55932 – 82.8246

2.500 0.52256 – 85.2795

2.600 0.48754 – 85.6298

2.700 0.46411 – 86.1854

2.800 0.45776 – 86.4997

2.900 0.44859 – 88.8080

3.000 0.44588 – 91.9737

3.100 0.43810 – 95.4087

3.200 0.43269 – 99.1282

KEYWORD – R

IMPEDANCE – 50

FREQ MAGS11 ANGS11

3.300 0.42777 – 102.748

3.400 0.42859 – 107.167

3.500 0.43365 – 111.883

3.600 0.43849 – 117.548

3.700 0.44475 – 123.856

3.800 0.44800 – 130.399

3.900 0.45223 – 136.744

4.000 0.45555 – 142.766

4.100 0.45313 – 149.269

4.200 0.45622 – 154.884

4.300 0.45555 – 159.680

4.400 0.46108 – 164.916

4.500 0.45325 – 168.452

4.600 0.45054 – 173.462

4.700 0.45200 – 176.697

4.800 0.45043 178.824

4.900 0.45282 174.947

5.000 0.44287 170.237

5.100 0.44909 166.617

5.200 0.44294 162.786

5.300 0.44558 158.766

5.400 0.45417 153.195

5.500 0.46038 147.721

5.600 0.47128 139.760

5.700 0.47439 132.657

5.800 0.48604 125.782

5.900 0.50637 121.110

6.000 0.52172 115.400

TPC 1. S-Parameter Data for the RF Input

0

–5

–10

–15

OUTPUT POWER – dB

–20

–25

TA = +25C

TA = +85C

TA = –40C

–30

01

246

3

5

RF INPUT FREQUENCY – GHz

TPC 2. Input Sensitivity

VDD = 3V

V

= 3V

P

–40

–50

–60

10dB/DIV

RL = –40dBc/Hz

RMS NOISE = 0.36

–70

–80

–90

–100

–110

PHASE NOISE – dBc/Hz

–120

–130

–140

100Hz 1MHz

FREQUENCY OFFSET FROM 900MHz CARRIER

TPC 4. Integrated Phase Noise (900 MHz,

200 kHz, and 20 kHz)

0

REF LEVEL = –14.0dBm

–10

–20

–30

–40

VDD = 3V, VP = 5V

I

= 5mA

CP

PFD FREQUENCY = 200kHz

LOOP BANDWIDTH = 20kHz

RES BANDWIDTH = 1kHz

VIDEO BANDWIDTH = 1kHz

SWEEP = 2.5 SECONDS

AVERAGES = 30

–50

–60

–70

OUTPUT POWER – dB

–80

–91.0dBc/Hz

–90

–100

–400kHz

400kHz900MHz–200kHz 200kHz

FREQUENCY

TPC 5. Reference Spurs (900 MHz, 200 kHz, and 20 kHz)

0

REF LEVEL = –14.3dBm

–10

–20

–30

–40

VDD = 3V, VP = 5V

I

= 5mA

CP

PFD FREQUENCY = 200kHz

LOOP BANDWIDTH = 20kHz

RES BANDWIDTH = 10Hz

VIDEO BANDWIDTH = 10Hz

SWEEP = 1.9 SECONDS

AVERAGES = 10

–50

–60

OUTPUT POWER – dB

–70

–93.0dBc/Hz

–80

–90

–100

–2kHz

2kHz900MHz–1kHz 1kHz

FREQUENCY

TPC 3. Phase Noise (900 MHz, 200 kHz, and 20 kHz)

–6–

0

REF LEVEL = –10dBm

–10

–20

–30

–40

VDD = 3V, VP = 5V

I

= 5mA

CP

PFD FREQUENCY = 1MHz

LOOP BANDWIDTH = 100kHz

RES BANDWIDTH = 10Hz

VIDEO BANDWIDTH = 10Hz

SWEEP = 1.9 SECONDS

AVERAGES = 10

–50

–60

–70

OUTPUT POWER – dB

–80

–84.0dBc/Hz

–90

–100

–2kHz

2kHz5800MHz–1kHz 1kHz

FREQUENCY

TPC 6. Phase Noise (5.8 GHz, 1 MHz, and 100 kHz)

REV. 0

Loading...

Loading...