V

Single-Phase Multifunction Metering IC

FEATURES

High accuracy; supports IEC 60687/61036/61268 and

IEC 62053-21/62053-22/62053-23

On-chip digital integrator enables direct interface to current

sensors with di/dt output

Active, reactive, and apparent energy; sampled waveform;

current and voltage rms

Less than 0.1% error in active energy measurement over a

dynamic range of 1000 to 1 at 25°C

Positive-only energy accumulation mode available

On-chip user programmable threshold for line voltage surge

and SAG and PSU supervisory

Digital calibration for power, phase, and input offset

On-chip temperature sensor (±3°C typical)

SPI® compatible serial interface

Pulse output with programmable frequency

Interrupt request pin (

Reference 2.4 V with external overdrive capability

Single 5 V supply, low power (25 mW typical)

GENERAL DESCRIPTION

The ADE7753 features proprietary ADCs and DSP for high

accuracy over large variations in environmental conditions and

time. The ADE7753 incorporates two second-order 16-bit Σ-∆

ADCs, a digital integrator (on CH1), reference circuitry,

temperature sensor, and all the signal processing required to

perform active, reactive, and apparent energy measurements,

line-voltage period measurement, and rms calculation on the

IRQ

) and status register

with di/dt Sensor Interface

ADE7753

voltage and current. The selectable on-chip digital integrator

provides direct interface to di/dt current sensors such as

Rogowski coils, eliminating the need for an external analog

integrator and resulting in excellent long-term stability and precise phase matching between the current and voltage channels.

The ADE7753 provides a serial interface to read data, and a

pulse output frequency (CF), which is proportional to the active

power. Various system calibration features, i.e., channel offset

correction, phase calibration, and power calibration, ensure high

accuracy. The part also detects short duration low or high

voltage variations.

The positive-only accumulation mode gives the option to

accumulate energy only when positive power is detected. An

internal no-load threshold ensures that the part does not exhibit

any creep when there is no load. The zero-crossing output (ZX)

produces a pulse that is synchronized to the zero-crossing point

of the line voltage. This signal is used internally in the line cycle

active and apparent energy accumulation modes, which enables

faster calibration.

The interrupt status register indicates the nature of the interrupt,

and the interrupt enable register controls which event produces

IRQ

an output on the

The ADE7753 is available in a 20-lead SSOP package.

pin, an open-drain, active low logic output.

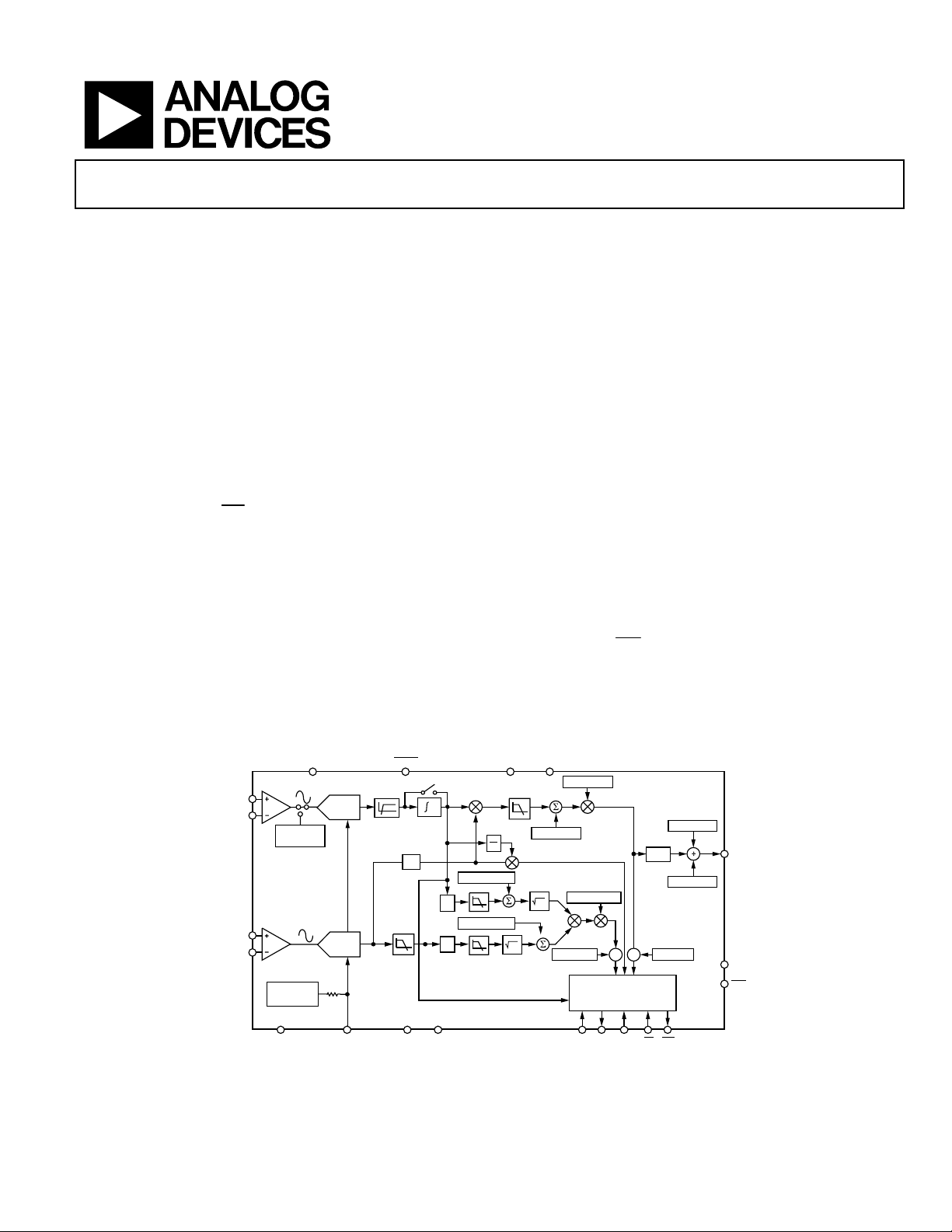

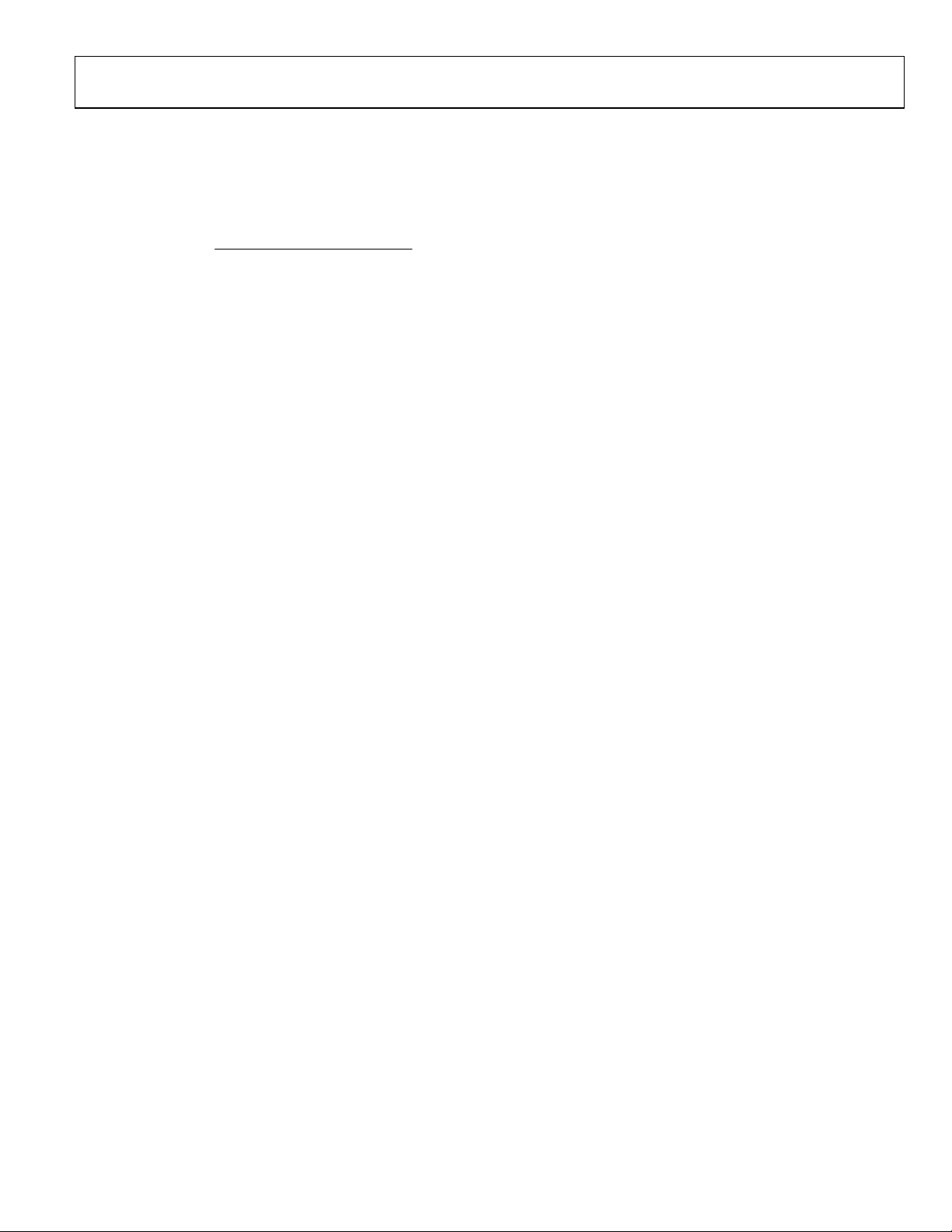

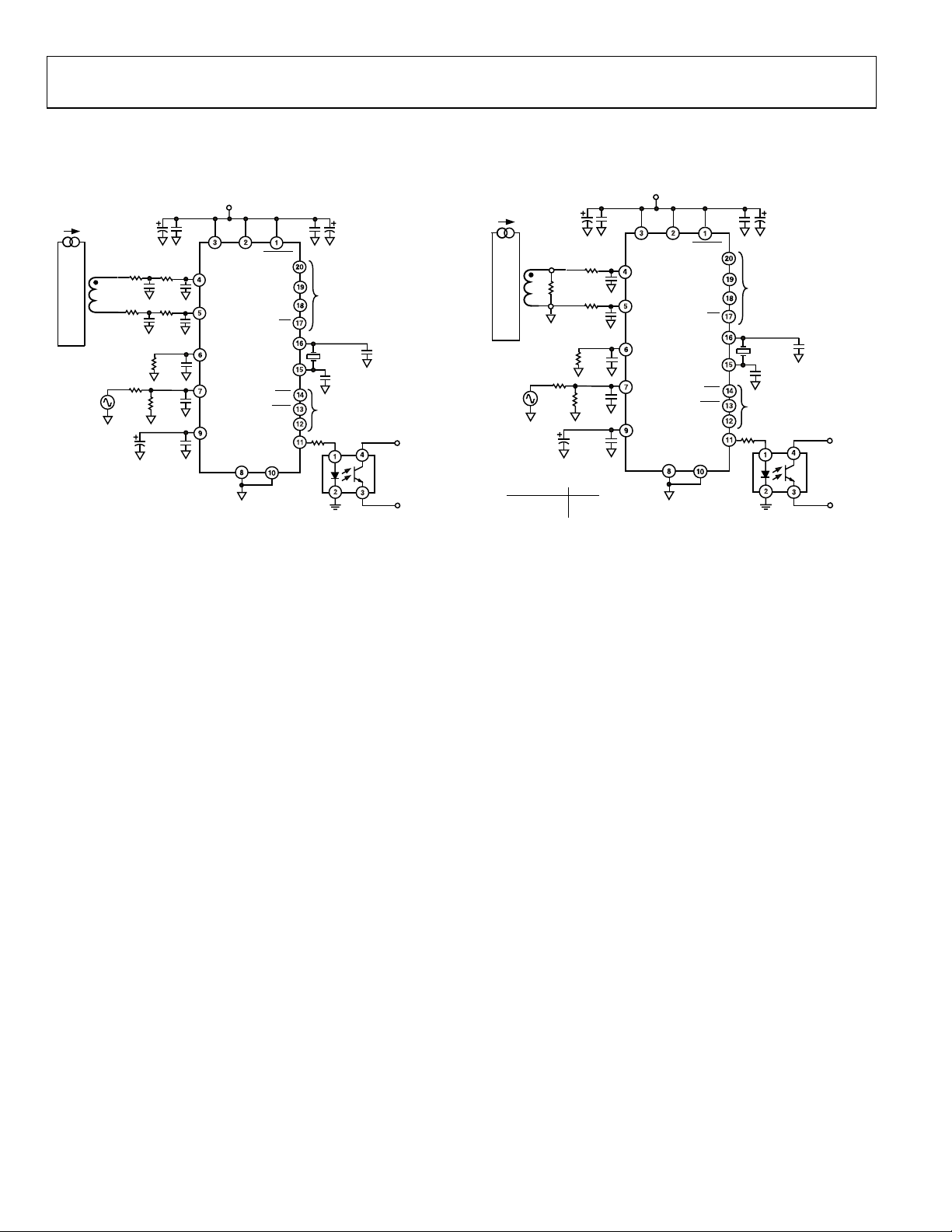

FUNCTIONAL BLOCK DIAGRAM

AVDD

PGA

V1P

V1N

V2P

SENSOR

PGA

2N

2.4V

REFERENCE

AGND

ADC

TEMP

ADC

4k

IN/OUT

*U.S. Patents 5,745,323; 5,760,617; 5,862,069; 5,872,469; others pending.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

RESET

HPF1

PHCAL[5:0]

INTEGRATOR

Φ

LPF1

CLKIN

dt

CLKOUT

2

x

2

x

MULTIPLIER

IRMSOS[11:0]

VRMSOS[11:0]

Figure 1.

DVDD DGND

APOS[15:0]

VADIV[7:0]

WGAIN[11:0]

VAGAIN[11:0]

REGISTERS AND

SERIAL INTERFACE

DIN DOUT SCLKREF

% %

LPF2

π

2

DFC

WDIV[7:0]

CS IRQ

ADE7753

CFNUM[11:0]

CF

CFDEN[11:0]

ZX

SAG

02875-A-001

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

ADE7753

TABLE OF CONTENTS

Specifications..................................................................................... 3

Timing Characteristics..................................................................... 5

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Te r m in o l o g y ...................................................................................... 7

Pin Configuration and Function Descriptions............................. 8

Typical Performance Characteristics........................................... 10

Theory of Operation ...................................................................... 15

Analog Inputs.............................................................................. 15

di/dt Current Sensor and Digital Integrator ...........................16

Zero-Crossing Detection........................................................... 17

Period Measurement.................................................................. 18

Power Supply Monitor ............................................................... 18

Line Voltage Sag Detection........................................................ 18

Peak Detection ............................................................................ 19

ADE7753 Interrupts................................................................... 20

Temperature Measurement ....................................................... 21

ADE7753 Analog-to-Digital Conversion................................ 21

Channel 1 ADC........................................................................... 22

Channel 2 ADC........................................................................... 24

Phase Compensation.................................................................. 26

Active Power Calculation .......................................................... 27

Energy Calculation..................................................................... 28

Power Offset Calibration ........................................................... 30

Energy-to-Frequency Conversion ........................................... 30

Line Cycle Energy Accumulation Mode ................................. 32

Positive-Only Accumulation Mode ......................................... 32

No-Load Threshold.................................................................... 32

Reactive Power Calculation ...................................................... 33

Sign of Reactive Power Calculation......................................... 34

Apparent Power Calculation ..................................................... 34

Apparent Energy Calculation ................................................... 35

Line Apparent Energy Accumulation...................................... 36

Energies Scaling.......................................................................... 37

Calibrating an Energy Meter Based on the ADE7753........... 37

CLKIN Frequency ...................................................................... 47

Suspending ADE7753 Functionality........................................ 47

Checksum Register..................................................................... 47

ADE7753 Serial Interface.......................................................... 48

ADE7753 Registers......................................................................... 51

ADE7753 Register Descriptions................................................... 54

Communications Register......................................................... 54

Mode Register (0x09)................................................................. 54

Interrupt Status Register (0x0B), Reset Interrupt Status

Register (0x0C), Interrupt Enable Register (0x0A)

............... 56

CH1OS Register (0x0D)............................................................ 57

Outline Dimensions....................................................................... 58

Ordering Guide .......................................................................... 58

REVISION HISTORY

6/04—Changed from Rev. 0 to Rev A

Changes IEC Standards ................................................................... 1

Changes to Phase Error Between Channels Definition............... 7

Changes to Figure 24...................................................................... 13

Changes to CH2OS Register ......................................................... 16

Change to the Period Measurement Section............................... 18

Change to Temperature Measurement Section ..........................21

Changes to Figure 69...................................................................... 31

Rev. A | Page 2 of 60

Changes to Figure 71...................................................................... 33

Changes to the Apparent Energy Section.................................... 36

Changes to Energies Scaling Section ........................................... 37

Changes to Calibration Section.................................................... 37

8/03—Revision 0: Initial Version

ADE7753

SPECIFICATIONS

AVDD = DVDD = 5 V ± 5%, AGND = DGND = 0 V, on-chip reference, CLKIN = 3.579545 MHz XTAL, T

MIN

to T

= –40°C to +85°C.

MAX

Table 1.

Parameter

1

Spec Unit Test Conditions/Comments

ENERGY MEASUREMENT ACCURACY

Active Power Measurement Error CLKIN = 3.579545 MHz

Channel 1 Range = 0.5 V Full Scale Channel 2 = 300 mV rms/60 Hz, gain = 2

Gain = 1 0.1 % typ Over a dynamic range 1000 to 1

Gain = 2 0.1 % typ Over a dynamic range 1000 to 1

Gain = 4 0.1 % typ Over a dynamic range 1000 to 1

Gain = 8 0.1 % typ Over a dynamic range 1000 to 1

Channel 1 Range = 0.25 V Full Scale

Gain = 1 0.1 % typ Over a dynamic range 1000 to 1

Gain = 2 0.1 % typ Over a dynamic range 1000 to 1

Gain = 4 0.1 % typ Over a dynamic range 1000 to 1

Gain = 8 0.2 % typ Over a dynamic range 1000 to 1

Channel 1 Range = 0.125 V Full Scale

Gain = 1 0.1 % typ Over a dynamic range 1000 to 1

Gain = 2 0.1 % typ Over a dynamic range 1000 to 1

Gain = 4 0.2 % typ Over a dynamic range 1000 to 1

Gain = 8 0.2 % typ Over a dynamic range 1000 to 1

Active Power Measurement Bandwidth 14 kHz

Phase Error 1 between Channels

AC Power Supply Rejection

2

2

±0.05 max Line Frequency = 45 Hz to 65 Hz, HPF on

AVDD = DVDD = 5 V + 175 mV rms/120 Hz

Output Frequency Variation (CF) 0.2 % typ Channel 1 = 20 mV rms, gain = 16, range = 0.5 V

Channel 2 = 300 mV rms/60 Hz, gain = 1

DC Power Supply Rejection

2

AVDD = DVDD = 5 V ± 250 mV dc

Output Frequency Variation (CF) ±0.3 % typ Channel 1 = 20 mV rms/60 Hz, gain = 16, range = 0.5 V

Channel 2 = 300 mV rms/60 Hz, gain = 1

IRMS Measurement Error 0.5 % typ Over a dynamic range 100 to 1

IRMS Measurement Bandwidth 14 kHz

VRMS Measurement Error 0.5 % typ Over a dynamic range 20 to 1

VRMS Measurement Bandwidth 140 Hz

ANALOG INPUTS

3

See the Analog Inputs section

Maximum Signal Levels ±0.5 V max V1P, V1N, V2N, and V2P to AGND

Input Impedance (dc) 390 k min

Bandwidth 14 kHz CLKIN/256, CLKIN = 3.579545 MHz

Gain Error

2, 3

External 2.5 V reference, gain = 1 on Channels 1 and 2

Channel 1

Range = 0.5 V Full Scale ±4 % typ V1 = 0.5 V dc

Range = 0.25 V Full Scale ±4 % typ V1 = 0.25 V dc

Range = 0.125 V Full Scale ±4 % typ V1 = 0.125 V dc

Channel 2 ±4 % typ V2 = 0.5 V dc

Offset Error

2

±32 mV max Gain 1

Channel 1 ±13 mV max Gain 16

±32 mV max Gain 1

Channel 2 ±13 mV max Gain 16

WAVEFORM SAMPLING Sampling CLKIN/128, 3.579545 MHz/128 = 27.9 kSPS

Channel 1 See the Channel 1 Sampling section

Signal-to-Noise Plus Distortion 62 dB typ 150 mV rms/60 Hz, range = 0.5 V, gain = 2

Bandwidth(–3 dB) 14 kHz CLKIN = 3.579545 MHz

Footnotes on next page.

Rev. A | Page 3 of 60

ADE7753

Parameter Spec Unit Test Conditions/Comments

Channel 2 See the Channel 2 Sampling section

Signal-to-Noise Plus Distortion 60 dB typ 150 mV rms/60 Hz, gain = 2

Bandwidth (–3 dB) 140 Hz CLKIN = 3.579545 MHz

REFERENCE INPUT

REF

2.2 V min 2.4 V – 8%

Input Capacitance 10 pF max

ON-CHIP REFERENCE Nominal 2.4 V at REF

Reference Error ±200 mV max

Current Source 10 µA max

Output Impedance 3.4 kΩ min

Temperature Coefficient 30 ppm/°C typ

CLKIN All specifications CLKIN of 3.579545 MHz

Input Clock Frequency 4 MHz max

1 MHz min

LOGIC INPUTS

RESET

Input High Voltage, V

Input Low Voltage, V

Input Current, I

Input Capacitance, C

LOGIC OUTPUTS

SAG

Output High Voltage, V

Output Low Voltage, V

ZX and DOUT

Output High Voltage, V

Output Low Voltage, V

CF

Output High Voltage, V

Output Low Voltage, V

POWER SUPPLY For specified performance

AVDD 4.75 V min 5 V – 5%

5.25 V max 5 V + 5%

DVDD 4.75 V min 5 V – 5%

5.25 V max 5 V + 5%

AI

DI

_______________________________________________

1

See the plots in the Typical Performance Characteristics section.

2

See the Terminology section for explanation of specifications.

3

See the Analog Inputs section.

Input Voltage Range 2.6 V max 2.4 V + 8%

IN/OUT

, DIN, SCLK, CLKIN, and

IN

IRQ

and

DD

DD

CS

INH

INL

IN

OH

OL

OH

OL

OH

OL

2.4 V min DVDD = 5 V ± 10%

0.8 V max DVDD = 5 V ± 10%

±3 µA max Typically 10 nA, VIN = 0 V to DV

10 pF max

Open-drain outputs, 10 kΩ pull-up resistor

4 V min I

0.4 V max I

4 V min I

0.4 V max I

4 V min I

1 V max I

3 mA max Typically 2.0 mA

4 mA max Typically 3.0 mA

200 µA

SOURCE

= 0.8 mA

SINK

SOURCE

= 0.8 mA

SINK

SOURCE

= 7 mA

SINK

I

Ol

= 5 mA

= 5 mA

= 5 mA

IN/OUT

pin

DD

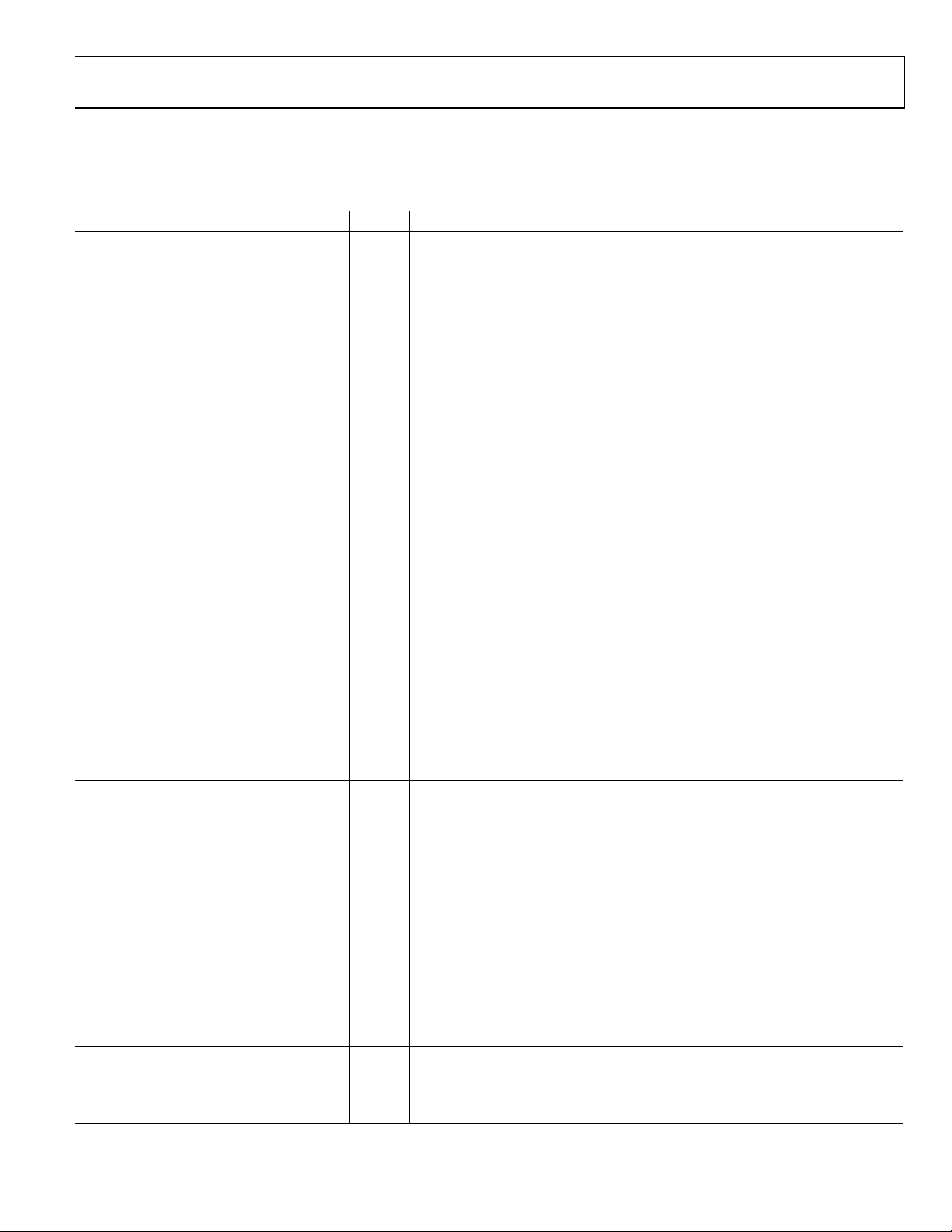

OUTPUT

PIN

TO

50pF

C

L

1.6mA

I

OH

+2.1V

02875-0-002

Figure 2. Load Circuit for Timing Specifications

Rev. A | Page 4 of 60

ADE7753

K

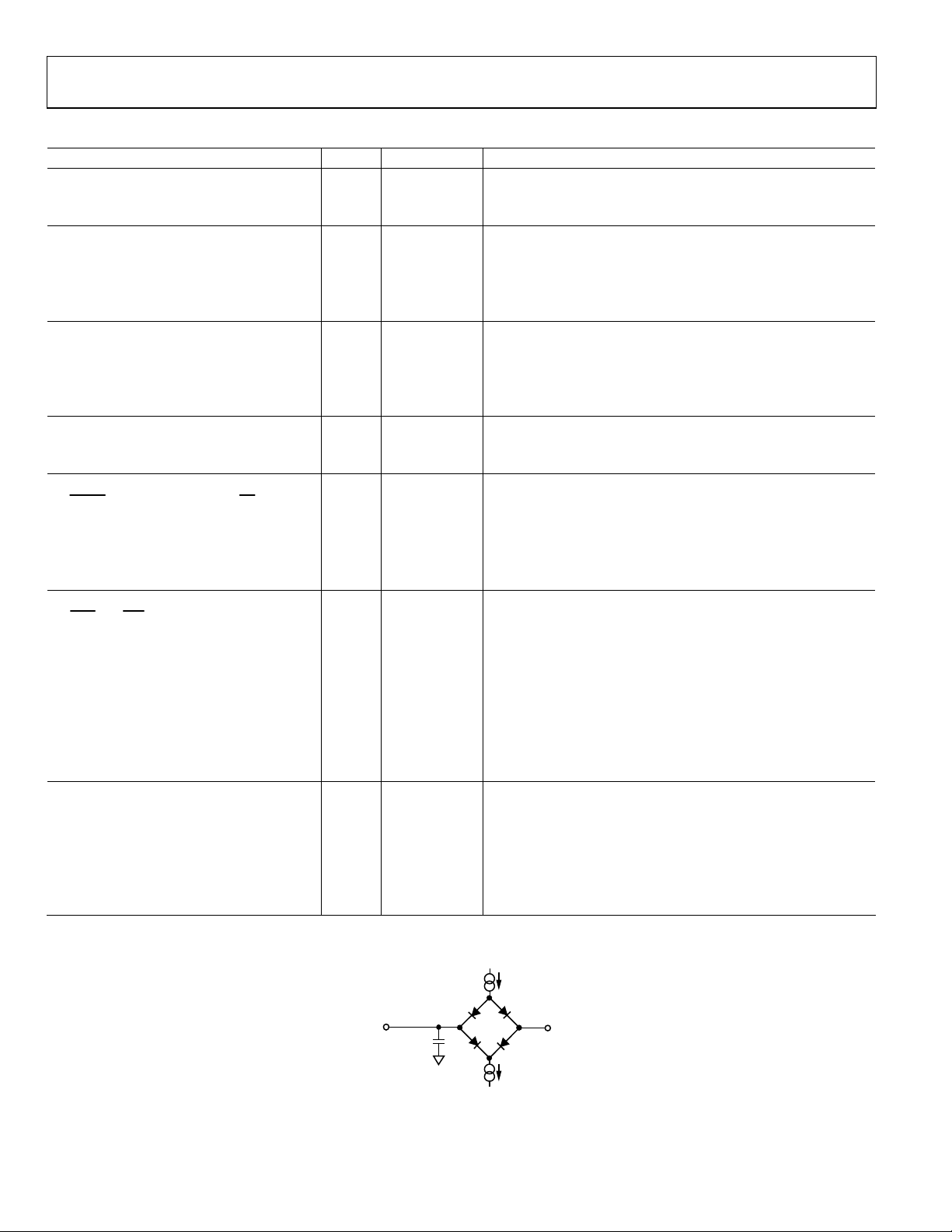

TIMING CHARACTERISTICS

AVDD = DV = 5 V ± 5%, AGND = DGND = 0 V, on-chip reference, CLKIN = 3.579545 MHz XTAL, T

DD MIN

Table 2.

Parameter

1, 2

Spec Unit Test Conditions/Comments

Write Timing

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

50 ns (min)

CS falling edge to first SCLK falling edge.

50 ns (min) SCLK logic high pulse width.

50 ns (min) SCLK logic low pulse width.

10 ns (min) Valid data setup time before falling edge of SCLK.

5 ns (min) Data hold time after SCLK falling edge.

400 ns (min) Minimum time between the end of data byte transfers.

50 ns (min) Minimum time between byte transfers during a serial write.

100 ns (min)

CS hold time after SCLK falling edge.

Read Timing

3

t

9

4 µs (min) Minimum time between read command (i.e., a write to

communication register) and data read.

t

10

t

11

50 ns (min) Minimum time between data byte transfers during a multibyte read.

30 ns (min) Data access time after SCLK rising edge following a write to the

communications register.

4

t

12

100 ns (max) Bus relinquish time after falling edge of SCLK.

10 ns (min)

5

t

13

100 ns (max)

Bus relinquish time after rising edge of

10 ns (min)

___________________________________

1

Sample tested during initial release and after any redesign or process change that could affect this parameter. All input signals are specified with tr = tf = 5 ns

(10% to 90%) and timed from a voltage level of 1.6 V.

2

See Figure 3, Figure 4, and the ADE7753 Serial Interface section.

3

Minimum time between read command and data read for all registers except waveform register, which is t9 = 500 ns min.

4

Measured with the load circuit in Figure 2 and defined as the time required for the output to cross 0.8 V or 2.4 V.

5

Derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit in Figure 2. The measured number is then extrapolated back

to remove the effects of charging or discharging the 50 pF capacitor. This means that the time quoted in the timing characteristics is the true bus relinquish time of

the part and is independent of the bus loading.

CS

SCL

DIN

t

1

1

t

3

t

A4A5 A3

4

t

5

A2

A1

t

2

0

t

7

A0

DB7

DB0

t

7

DB7

to T

t

6

= –40°C to +85°C.

MAX

CS

.

t

8

DB0

COMMAND BYTE

MOST SIGNIFICANT BYTE

LEAST SIGNIFICANT BYTE

02875-0-081

Figure 3. Serial Write Timing

CS

SCLK

DIN

DOUT

t

1

t

9

0

0

A4A5 A3

COMMAND BYTE

A2

A0

A1

t

11

DB7

MOST SIGNIFICANT BYTE

t

10

t

11

DB0

LEAST SIGNIFICANT BYTE

t

13

t

12

DB0DB7

02875-0-083

Figure 4. Serial Read Timing

Rev. A | Page 5 of 60

ADE7753

ABSOLUTE MAXIMUM RATINGS

T = 25°C, unless otherwise noted.

A

Table 3.

Parameter Rating

AVDD to AGND –0.3 V to +7 V

DVDD to DGND –0.3 V to +7 V

DVDD to AVDD –0.3 V to +0.3 V

Analog Input Voltage to AGND

V1P, V1N, V2P, and V2N

Reference Input Voltage to AGND –0.3 V to AVDD + 0.3 V

Digital Input Voltage to DGND –0.3 V to DVDD + 0.3 V

Digital Output Voltage to DGND –0.3 V to DVDD + 0.3 V

Operating Temperature Range

Industrial –40°C to +85°C

Storage Temperature Range –65°C to +150°C

Junction Temperature 150°C

20-Lead SSOP, Power Dissipation 450 mW

θJA Thermal Impedance 112°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

–6 V to +6 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. A | Page 6 of 60

ADE7753

TERMINOLOGY

Measurement Error

The error associated with the energy measurement made by the

ADE7753 is defined by the following formula:

⎛

⎜

ErrorPercentage

=

⎜

⎝

EnergyTrue

7753

−

⎞

EnergyTrueADERegisterEnergy

⎟

%100

×

⎟

⎠

supplies. Any error introduced by this ac signal is expressed as

a percentage of reading—see the Measurement Error definition.

For the dc PSR measurement, a reading at nominal supplies

(5 V) is taken. A second reading is obtained with the same input

signal levels when the supplies are varied ±5%. Any error

introduced is again expressed as a percentage of the reading.

Phase Error between Channels

The digital integrator and the high-pass filter (HPF) in Channel 1

have a non-ideal phase response. To offset this phase response

and equalize the phase response between channels, two phasecorrection networks are placed in Channel 1: one for the digital

integrator and the other for the HPF. The phase correction

networks correct the phase response of the corresponding

component and ensure a phase match between Channel 1

(current) and Channel 2 (voltage) to within ±0.1° over a range

of 45 Hz to 65 Hz with the digital integrator off. With the

digital integrator on, the phase is corrected to within ±0.4°

over a range of 45 Hz to 65 Hz.

Power Supply Rejection

This quantifies the ADE7753 measurement error as a percentage

of reading when the power supplies are varied. For the ac PSR

measurement, a reading at nominal supplies (5 V) is taken. A

second reading is obtained with the same input signal levels

when an ac (175 mV rms/120 Hz) signal is introduced onto the

ADC Offset Error

The dc offset associated with the analog inputs to the ADCs. It

means that with the analog inputs connected to AGND, the

ADCs still see a dc analog input signal. The magnitude of the

offset depends on the gain and input range selection—see the

Typical Performance Characteristics section. However, when

HPF1 is switched on, the offset is removed from Channel 1

(current) and the power calculation is not affected by this

offset. The offsets can be removed by performing an offset

calibration—see the Analog Inputs section.

Gain Error

The difference between the measured ADC output code (minus

the offset) and the ideal output code—see the Channel 1 ADC

and Channel 2 ADC sections. It is measured for each of the

input ranges on Channel 1 (0.5 V, 0.25 V, and 0.125 V). The

difference is expressed as a percentage of the ideal code.

Rev. A | Page 7 of 60

ADE7753

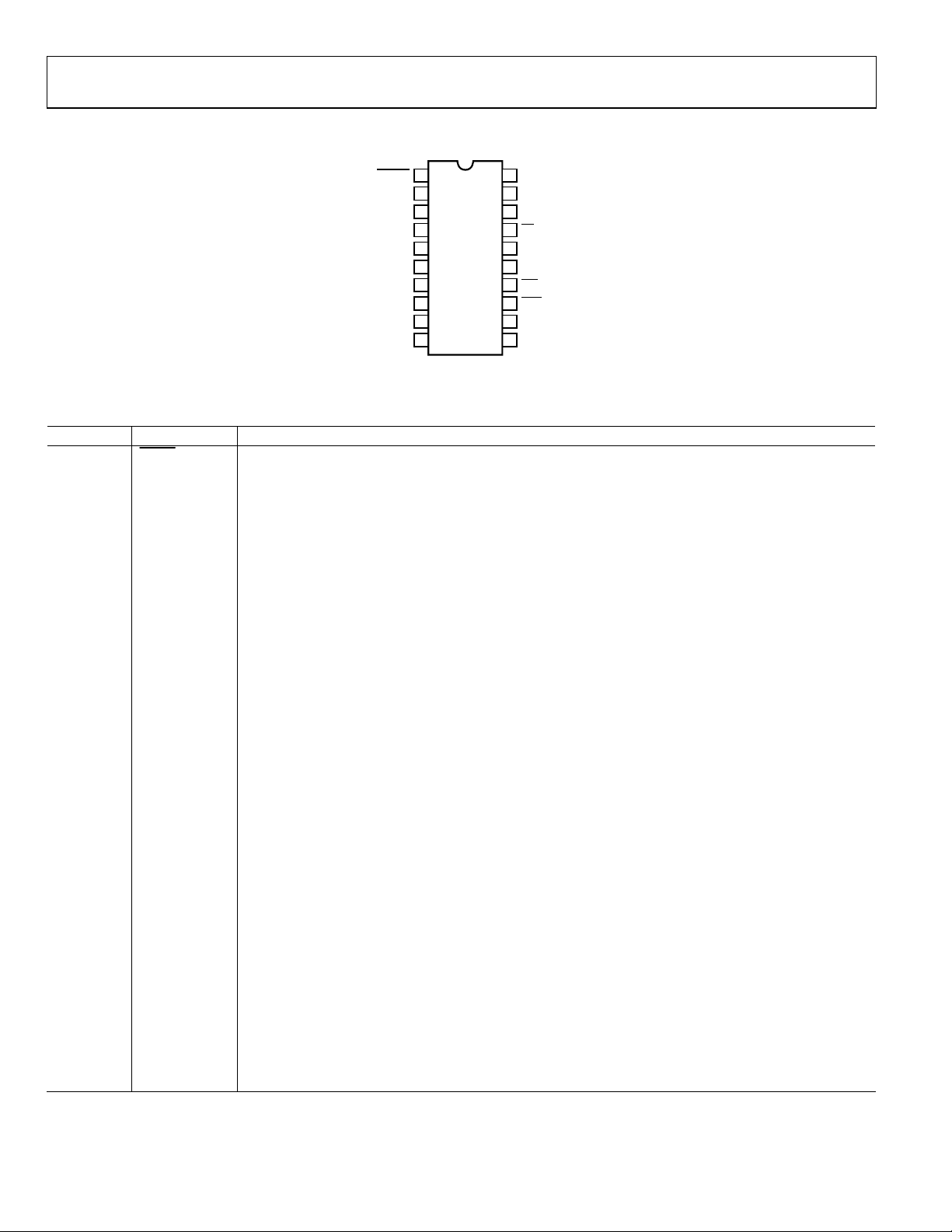

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

RESET

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1

RESET

Reset Pin for the ADE7753. A logic low on this pin holds the ADCs and digital circuitry (including the serial

interface) in a reset condition.

2 DVDD

Digital Power Supply. This pin provides the supply voltage for the digital circuitry in the ADE7753. The

supply voltage should be maintained at 5 V ± 5% for specified operation. This pin should be decoupled to

DGND with a 10 µF capacitor in parallel with a ceramic 100 nF capacitor.

3 AVDD

Analog Power Supply. This pin provides the supply voltage for the analog circuitry in the ADE7753. The

supply should be maintained at 5 V ± 5% for specified operation. Every effort should be made to minimize

power supply ripple and noise at this pin by the use of proper decoupling. The typical performance graphs

show the power supply rejection performance. This pin should be decoupled to AGND with a 10 µF

capacitor in parallel with a ceramic 100 nF capacitor.

4, 5 V1P, V1N

Analog Inputs for Channel 1. This channel is intended for use with a di/dt current transducer such as a

Rogowski coil or another current sensor such as a shunt or current transformer (CT). These inputs are fully

differential voltage inputs with maximum differential input signal levels of ±0.5 V, ±0.25 V, and ±0.125 V,

depending on the full-scale selection—see the Analog Inputs section. Channel 1 also has a PGA with gain

selections of 1, 2, 4, 8, or 16. The maximum signal level at these pins with respect to AGND is ±0.5 V. Both

inputs have internal ESD protection circuitry, and, in addition, an overvoltage of ±6 V can be sustained on

these inputs without risk of permanent damage.

6, 7 V2N, V2P

Analog Inputs for Channel 2. This channel is intended for use with the voltage transducer. These inputs are

fully differential voltage inputs with a maximum differential signal level of ±0.5 V. Channel 2 also has a PGA

with gain selections of 1, 2, 4, 8, or 16. The maximum signal level at these pins with respect to AGND is

±0.5 V. Both inputs have internal ESD protection circuitry, and an overvoltage of ±6 V can be sustained on

these inputs without risk of permanent damage.

8 AGND

Analog Ground Reference. This pin provides the ground reference for the analog circuitry in the ADE7753,

i.e., ADCs and reference. This pin should be tied to the analog ground plane or the quietest ground

reference in the system. This quiet ground reference should be used for all analog circuitry, for example,

anti-aliasing filters, current and voltage transducers, etc. To keep ground noise around the ADE7753 to a

minimum, the quiet ground plane should connected to the digital ground plane at only one point. It is

acceptable to place the entire device on the analog ground plane.

9 REF

IN/OUT

Access to the On-Chip Voltage Reference. The on-chip reference has a nominal value of 2.4 V ± 8% and a

typical temperature coefficient of 30 ppm/°C. An external reference source can also be connected at this

pin. In either case, this pin should be decoupled to AGND with a 1 µF ceramic capacitor.

10 DGND

Digital Ground Reference. This pin provides the ground reference for the digital circuitry in the ADE7753,

i.e., multiplier, filters, and digital-to-frequency converter. Because the digital return currents in the

ADE7753 are small, it is acceptable to connect this pin to the analog ground plane of the system. However,

high bus capacitance on the DOUT pin could result in noisy digital current, which could affect

performance.

11 CF

Calibration Frequency Logic Output. The CF logic output gives active power information. This output is

intended to be used for operational and calibration purposes. The full-scale output frequency can be

adjusted by writing to the CFDEN and CFNUM registers—see the Energy-to-Frequency Conversion section.

1

2

DVDD

AVDD

3

4

V1P

ADE7753

V1N

5

TOP VIEW

6

(Not to Scale)

7

8

9

10

02875-0-005

REF

V2N

V2P

AGND

IN/OUT

DGND

Figure 5. Pin Configuration (SSOP Package)

DIN

20

19

DOUT

SCLK

18

17

CS

CLKOUT

16

CLKIN

15

14

IRQ

SAG

13

ZX

12

CF

11

Rev. A | Page 8 of 60

ADE7753

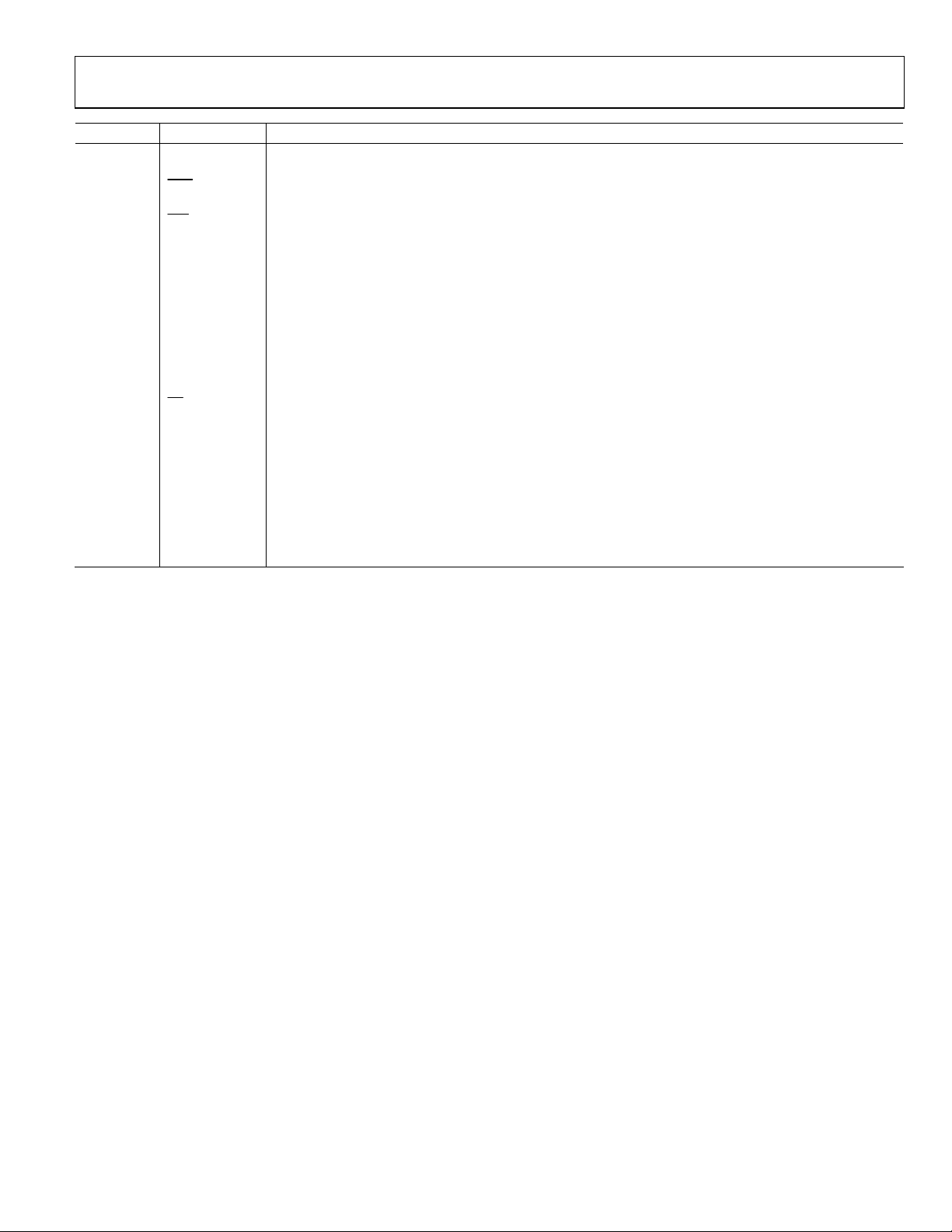

Pin No. Mnemonic Description

12 ZX

13

14

SAG This open-drain logic output goes active low when either no zero crossings are detected or a low voltage

IRQ Interrupt Request Output. This is an active low open-drain logic output. Maskable interrupts include active

15 CLKIN

16 CLKOUT

17

CS Chip Select. Part of the 4-wire SPI serial interface. This active low logic input allows the ADE7753 to share

18 SCLK

19 DOUT

20 DIN

Voltage Waveform (Channel 2) Zero-Crossing Output. This output toggles logic high and logic low at the

zero crossing of the differential signal on Channel 2—see the Zero-Crossing Detection section.

threshold (Channel 2) is crossed for a specified duration—see the Line Voltage Sag Detection section.

energy register rollover, active energy register at half level, and arrivals of new waveform samples—see the

ADE7753 Interrupts section.

Master Clock for ADCs and Digital Signal Processing. An external clock can be provided at this logic input.

Alternatively, a parallel resonant AT crystal can be connected across CLKIN and CLKOUT to provide a clock

source for the ADE7753. The clock frequency for specified operation is 3.579545 MHz. Ceramic load

capacitors of between 22 pF and 33 pF should be used with the gate oscillator circuit. Refer to the crystal

manufacturer’s data sheet for load capacitance requirements.

A crystal can be connected across this pin and CLKIN as described for Pin 15 to provide a clock source for

the ADE7753. The CLKOUT pin can drive one CMOS load when either an external clock is supplied at CLKIN

or a crystal is being used.

the serial bus with several other devices—see the ADE7753 Serial Interface section.

Serial Clock Input for the Synchronous Serial Interface. All serial data transfers are synchronized to this

clock—see the ADE7753 Serial Interface section. The SCLK has a Schmitt-trigger input for use with a clock

source that has a slow edge transition time, for example, opto-isolator output.

Data Output for the Serial Interface. Data is shifted out at this pin on the rising edge of SCLK. This logic

output is normally in a high impedance state unless it is driving data onto the serial data bus—see the

ADE7753 Serial Interface section.

Data Input for the Serial Interface. Data is shifted in at this pin on the falling edge of SCLK—see the

ADE7753 Serial Interface section.

Rev. A | Page 9 of 60

ADE7753

TYPICAL PERFORMANCE CHARACTERISTICS

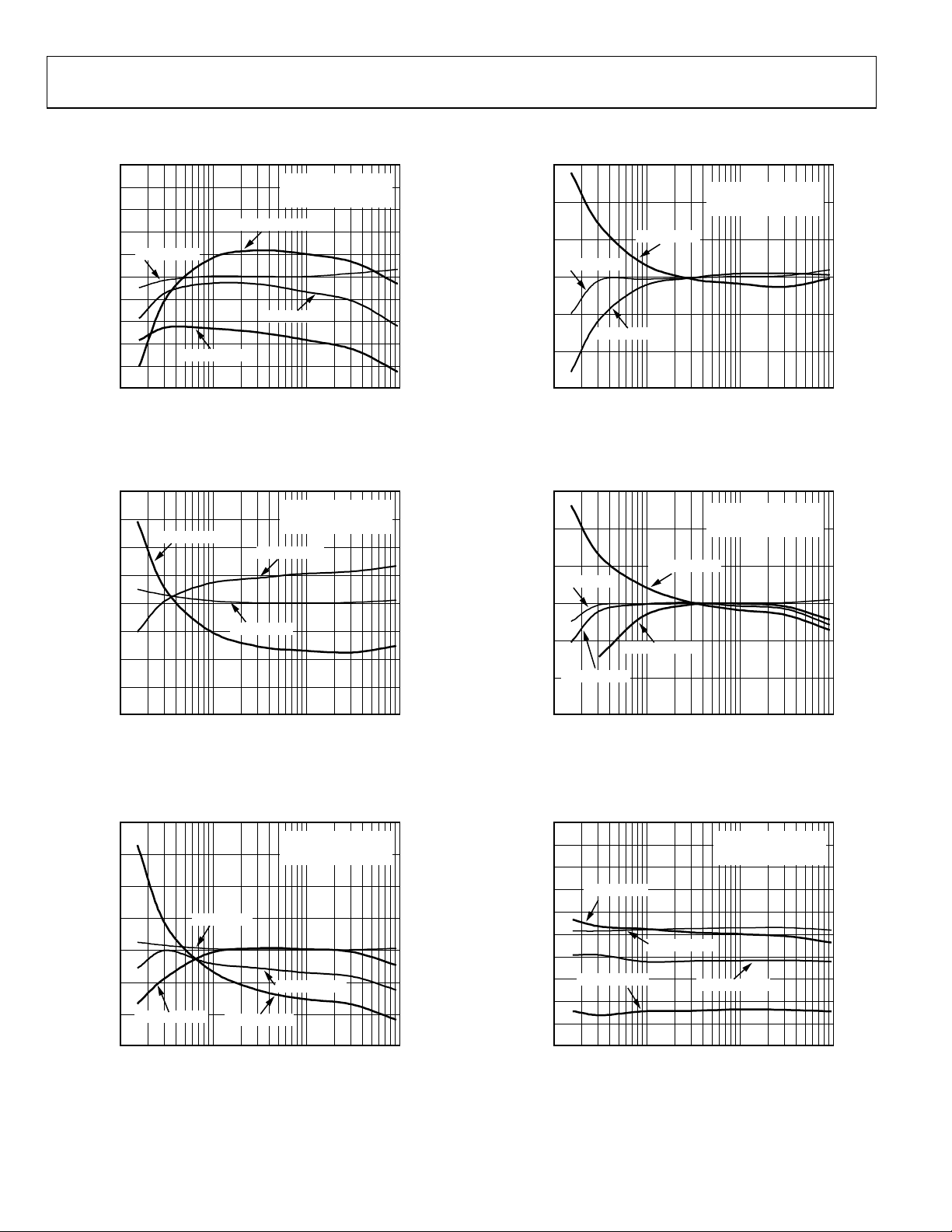

0.5

0.4

0.3

0.2

+25°C, PF = 1

0.1

0

–0.1

ERROR (%)

–0.2

–0.3

–0.4

–0.5

0.1

+85°C, PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

Figure 6. Active Energy Error as a Percentage of Reading (Gain = 1) over

Power Factor with Internal Reference and Integrator Off

GAIN = 1

INTEGRATOR OFF

INTERNAL REFERENCE

–40°C, PF = 0.5

+25°C, PF = 0.5

02875-0-006

0.3

GAIN = 8

0.2

0.1

0

ERROR (%)

–0.1

–0.2

–0.3

0.1

+85°C, PF = 1

+25°C, PF = 1

–40°C, PF = 1

1 10 100

FULL-SCALE CURRENT (%)

INTEGRATOR OFF

EXTERNAL REFERENCE

02875-0-010

Figure 9. Active Energy Error as a Percentage of Reading (Gain = 8) over

Temperature with External Reference and Integrator Off

0.4

0.3

0.2

0.1

0

ERROR (%)

–0.1

–0.2

–0.3

–0.4

0.1

+85°C, PF = 1

+25°C, PF = 1

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR OFF

INTERNAL REFERENCE

–40°C, PF = 1

02875-0-008

Figure 7. Active Energy as a Percentage of Reading (Gain = 8) over

Temperature with Internal Reference and Integrator Off

0.8

0.6

0.4

0.2

0

ERROR (%)

–0.2

–0.4

–0.6

0.1

+25°C, PF = 1

–40°C, PF = 0.5

+85°C, PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR OFF

INTERNAL REFERENCE

+25°C, PF = 0.5

02875-0-009

Figure 8. Active Energy Error as a Percentage of Reading (Gain = 8) over

Power Factor with Internal Reference and Integrator Off

0.6

GAIN = 8

0.4

0.2

0

ERROR (%)

–0.2

–0.4

–0.6

0.1

+25°C, PF = 1

+25°C, PF = 0.5

+85°C, PF = 0.5

–40°C, PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

INTEGRATOR OFF

EXTERNAL REFERENCE

02875-0-011

Figure 10. Active Energy Error as a Percentage of Reading (Gain = 8) over

Power Factor with External Reference and Integrator Off

0.5

0.4

0.3

0.2

0.1

–0.1

ERROR (%)

–0.2

–0.3

–0.4

–0.5

0

0.1

+25°C, PF = 0

–40°C, PF = 0.5

+85°C, PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 1

INTEGRATOR OFF

INTERNAL REFERENCE

+25°C, PF = 0.5

02875-0-012

Figure 11. Reactive Energy Error as a Percentage of Reading (Gain = 1) over

Power Factor with Internal Reference and Integrator Off

Rev. A | Page 10 of 60

ADE7753

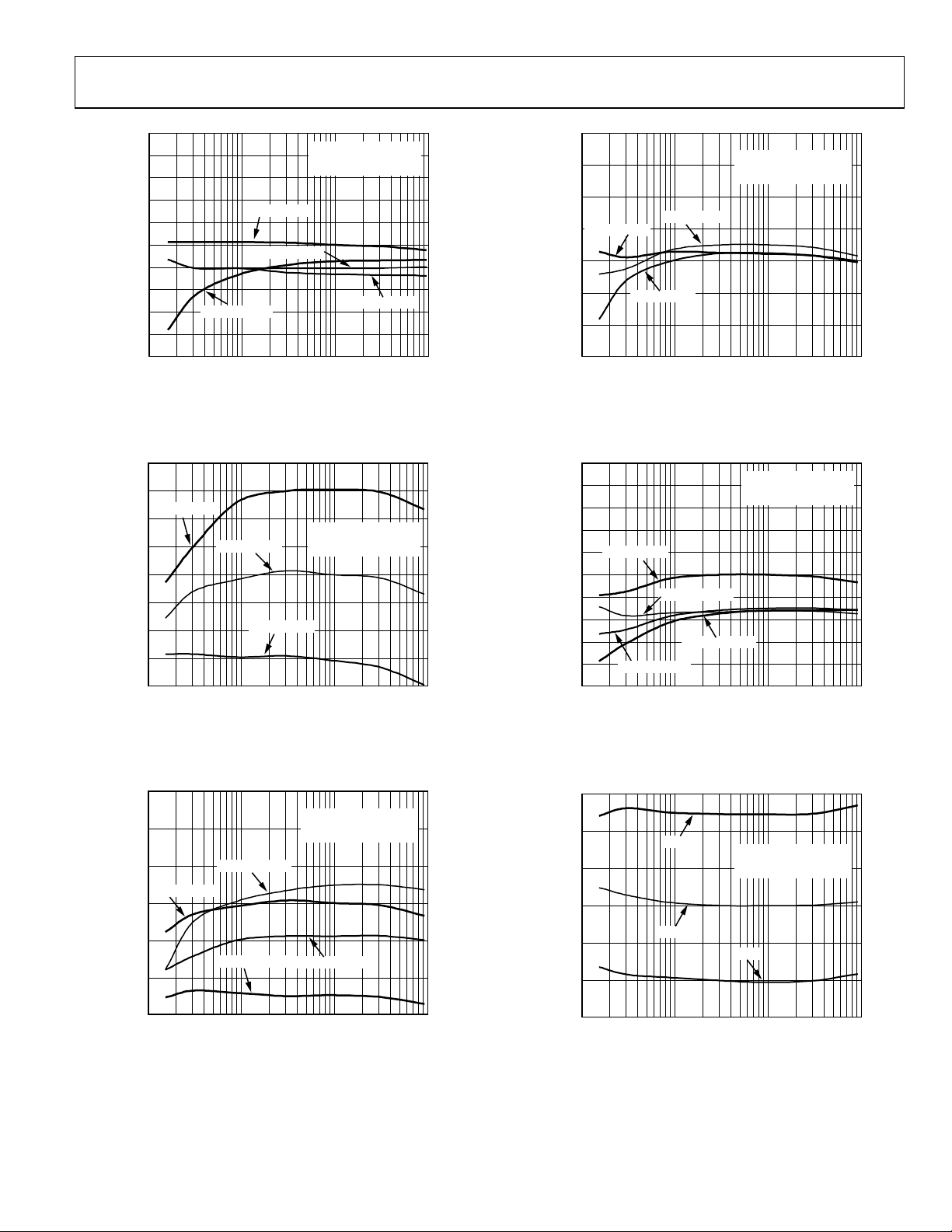

0.5

0.4

0.3

0.2

0.1

0

–0.1

ERROR (%)

–0.2

–0.3

–0.4

–0.5

0.1

+25°C, PF = 0

+25°C, PF = 0.5

–40°C, PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 1

INTEGRATOR OFF

EXTERNAL REFERENCE

+85°C, PF = 0.5

02875-0-013

Figure 12. Reactive Energy Error as a Percentage of Reading (Gain = 1) over

Power Factor with External Reference and Integrator Off

0.35

0.25

0.15

0.05

–0.05

ERROR (%)

–0.15

–0.25

–0.35

0.1

+85°C, PF = 0

+25°C, PF = 0

–40°C, PF = 0

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR OFF

EXTERNAL REFERENCE

02875-0-016

Figure 15. Reactive Energy Error as a Percentage of Reading (Gain = 8) over

Temperature with External Reference and Integrator Off

0.20

0.15

–40°C, PF = 0

0.10

0.05

0

ERROR (%)

–0.05

–0.10

–0.15

–0.20

0.1

+25°C, PF = 0

+85°C, PF = 0

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR OFF

INTERNAL REFERENCE

02875-0-014

Figure 13. Reactive Energy Error as a Percentage of Reading (Gain = 8) over

Temperature with Internal Reference and Integrator Off

0.3

GAIN = 8

0.2

0.1

0

ERROR (%)

–0.1

–0.2

–40°C, PF = 0.5

+25°C, PF = 0

+85°C, PF = 0.5

INTEGRATOR OFF

INTERNAL REFERENCE

+25°C, PF = 0.5

0.5

0.4

0.3

0.2

0.1

0

–0.1

ERROR (%)

–0.2

–0.3

–0.4

–0.5

0.1

+25°C, PF = 0

+85°C, PF = 0.5

–40°C, PF = 0.5

+25°C, PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR OFF

EXTERNAL REFERENCE

02875-0-017

Figure 16. Reactive Energy Error as a Percentage of Reading (Gain = 8) over

Power Factor with External Reference and Integrator Off

0.3

0.2

0.1

0

ERROR (%)

–0.1

–0.2

5.25V

5.0V

GAIN = 8

INTEGRATOR OFF

INTERNAL REFERENCE

4.75V

–0.3

0.1

1 10 100

FULL-SCALE CURRENT (%)

02875-0-015

Figure 14. Reactive Energy Error as a Percentage of Reading (Gain = 8) over

Power Factor with Internal Reference and Integrator Off

Rev. A | Page 11 of 60

–0.3

0.1

1 10 100

FULL-SCALE CURRENT (%)

02875-0-018

Figure 17. Active Energy Error as a Percentage of Reading (Gain = 8) over

Power Supply with Internal Reference and Integrator O ff

ADE7753

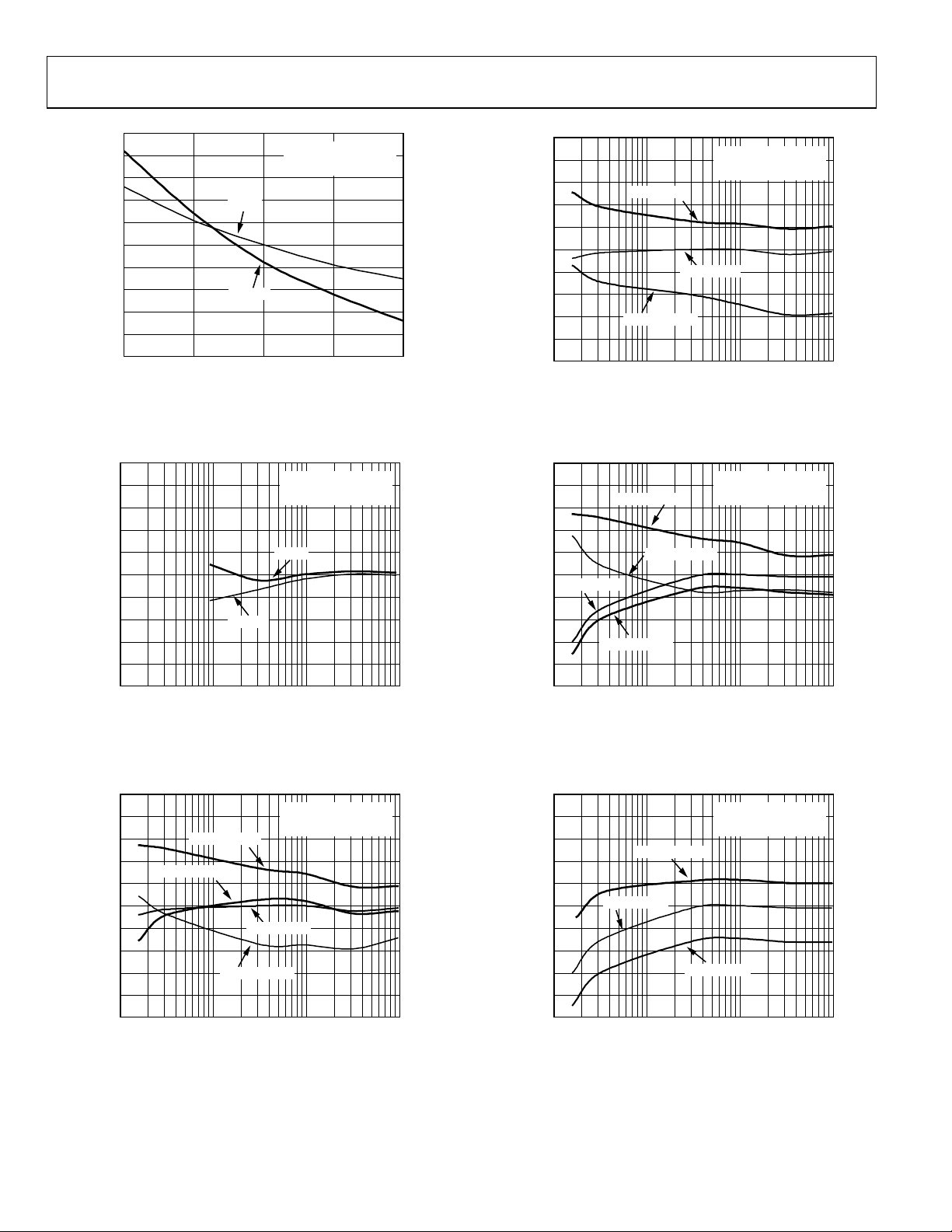

5

d

0.1

0.8

0.6

0.4

0.2

0

–0.2

ERROR (%)

–0.4

–0.6

–0.8

–0.1

45

50 55 60 6

PF = 1

PF = 0.5

LINE FREQUENCY (Hz)

Figure 18. Active Energy Error as a Percentage of Reading (Gain = 8) over

Frequency with External Reference and Integrator O ff

GAIN = 8

INTEGRATOR OFF

EXTERNAL REFERENCE

02875-0-019

1.0

0.8

0.6

0.4

0.2

0

–0.2

ERROR (%)

–0.4

–0.6

–0.8

–1.0

0.1

–40°C, PF = 1

85°C, PF = 1

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR ON

INTERNAL REFERENCE

25°C, PF = 1

02875-0-023

Figure 21. Active Energy Error as a Percentage of Reading (Gain = 8) over

Temperature with Internal Reference and Integrator On

0.5

0.4

0.3

0.2

0.1

0

–0.1

ERROR (%)

–0.2

–0.3

–0.4

–0.5

0.1

PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR OFF

INTERNAL REFERENCE

PF = 1

02875-0-020

Figure 19. IRMS Error as a Percentage of Reading (Gain = 8) with

Internal Reference and Integrator Off

1.0

0.8

0.6

0.4

0.2

0

–0.2

ERROR (%)

–0.4

–0.6

–0.8

–1.0

0.1

–40°C, PF = 0.5

+25°C, PF = 0.5

+85°C, PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR ON

INTERNAL REFERENCE

+25°C, PF = 1

02875-0-022

Figure 20. Active Energy Error as a Percentage of Reading (Gain = 8) over

Power Factor with Internal Reference an

Integrator On

1.0

0.8

0.6

0.4

0.2

0

–0.2

ERROR (%)

–0.4

–0.6

–0.8

–1.0

0.1

+25°C, PF = 0

–40°C, PF = 0.5

+85°C, PF = 0.5

+25°C, PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR ON

INTERNAL REFERENCE

02875-0-024

Figure 22. Reactive Energy Error as a Percentage of Reading (Gain = 8) over

Power Factor with Internal Reference and Integrator On

1.0

0.8

0.6

0.4

0.2

0

–0.2

ERROR (%)

–0.4

–0.6

–0.8

–1.0

0.1

–40°C, PF = 0

+25°C, PF = 0

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR ON

INTERNAL REFERENCE

+85°C, PF = 0

02875-0-025

Figure 23. Reactive Energy Error as a Percentage of Reading (Gain = 8) over

Temperature with Internal Reference and Integrator On

Rev. A | Page 12 of 60

ADE7753

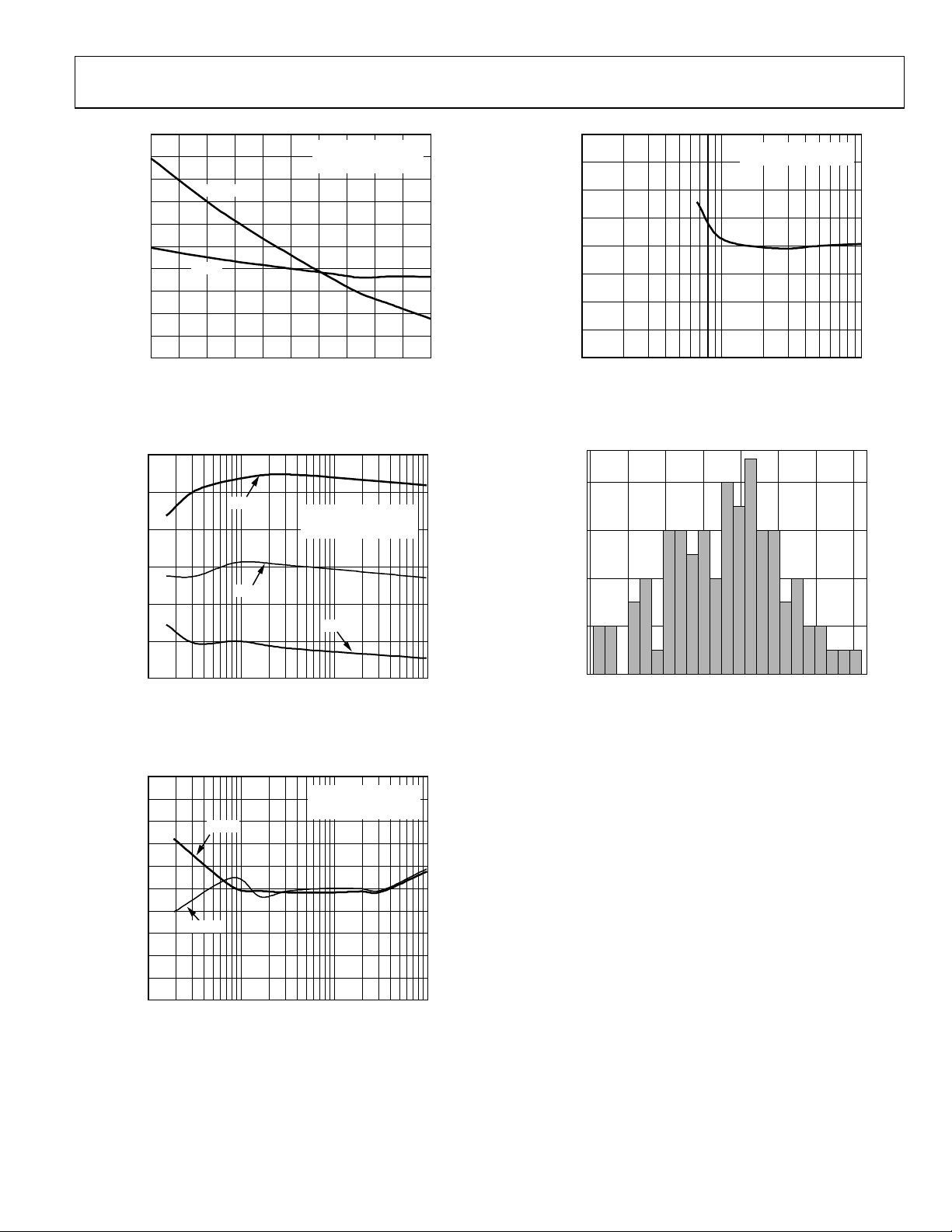

3.0

2.5

2.0

1.5

1.0

0.5

0

ERROR (%)

–0.5

–1.0

–1.5

–2.0

45 47 49 51 53 55 57 59 61 63 65

PF = 0.5

PF = 1

FREQUENCY (Hz)

GAIN = 8

INTEGRATOR ON

INTERNAL REFERENCE

02875-0-026

Figure 24. Active Energy Error as a Percentage of Reading (Gain = 8) over

Power Factor with Internal Reference and Integrator On

0.3

0.8

0.6

0.4

0.2

0

ERROR (%)

–0.2

–0.4

–0.6

–0.8

1

FULL-SCALE VOLTAGE

GAIN = 1

EXTERNAL REFERENCE

10 100

02875-0-029

Figure 27. VRMS Error as a Percentage of Reading (Gain = 1) with

External Reference

0.2

0.1

0

ERROR (%)

–0.1

–0.2

–0.3

0.1

5.25V

5.0V

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR ON

INTERNAL REFERENCE

4.75V

02875-0-027

Figure 25. Active Energy Error as a Percentage of Reading (Gain = 8) over

Power Supply with Internal Reference and Integrator On

0.5

0.4

0.3

0.2

0.1

0

–0.1

ERROR (%)

–0.2

–0.3

–0.4

–0.5

0.1

PF = 1

PF = 0.5

1 10 100

FULL-SCALE CURRENT (%)

GAIN = 8

INTEGRATOR ON

INTERNAL REFERENCE

02875-0-028

Figure 26. IRMS Error as a Percentage of Reading (Gain = 8) with

Internal Reference and Integrator On

8

6

HITS

4

2

0

–15 –12 –9 –6 –3

CH1 OFFSET (0p5V_1X) (mV)

036

02875-0-087

Figure 28. Channel 1 Offset (Gain = 1)

Rev. A | Page 13 of 60

ADE7753

V

DD

I

di/dt CURRENT

SENSOR

110V

CHANNEL 1 GAIN = 8

CHANNEL 2 GAIN = 1

10µF

100Ω 1kΩ

33nF 33nF

100Ω 1kΩ

33nF

1kΩ

600kΩ

1kΩ

10µF

100nF 100nF

AVDD DVDD

V1P

33nF

33nF

33nF

100nF

V1N

ADE7753

V2N

V2P

REF

IN/OUT

AGND DGND

U1

RESET

DIN

DOUT

SCLK

CS

CLKOUT

CLKIN

IRQ

SAG

ZX

CF

TOSPI BUS

(USED ONLY FOR

CALIBRATION)

Y1

3.58MHz

NOT CONNECTED

Figure 29. Test Circuit for Performance Curves with Integrator On

10µF

22pF

U3

PS2501-1

22pF

TO

FREQUENCY

COUNTER

02875-A-012

V

DD

I

110V

CT TURN RATIO = 1800:1

CHANNEL 2 GAIN = 1

GAIN 1 (CH1)

10µF1µF

CURRENT

TRANSFORMER

RB

1kΩ

600kΩ

1kΩ

10µF

1

8

100nF 100nF

1kΩ

33nF

1kΩ

33nF

33nF

33nF

100nF

RB

10Ω

1.21Ω

AVDD DVDD

V1P

V1N

V2N

V2P

REF

U1

ADE7753

CLKOUT

IN/OUT

AGND DGND

RESET

DIN

DOUT

SCLK

CS

CLKIN

IRQ

SAG

ZX

CF

0

TOSPI BUS

(USED ONLY FOR

CALIBRATION)

22pF

U3

PS2501-1

22pF

TO

FREQUENCY

COUNTER

02875-0-030

Y1

3.58MHz

NOT CONNECTED

Figure 30. Test Circuit for Performance Curves with Integrator Off

Rev. A | Page 14 of 60

ADE7753

T

THEORY OF OPERATION

ANALOG INPUTS

The ADE7753 has two fully differential voltage input channels.

The maximum differential input voltage for input pairs V1P/V1N

and V2P/V2N is ±0.5 V. In addition, the maximum signal level

on analog inputs for V1P/V1N and V2P/ V2N is ±0.5 V with

respect to AGND.

Each analog input channel has a programmable gain amplifier

(PGA) with possible gain selections of 1, 2, 4, 8, and 16. The gain

selections are made by writing to the gain register—see Figure 32.

Bits 0 to 2 select the gain for the PGA in Channel 1, and the gain

selection for the PGA in Channel 2 is made via Bits 5 to 7.

Figure 31 shows how a gain selection for Channel 1 is made

using the gain register.

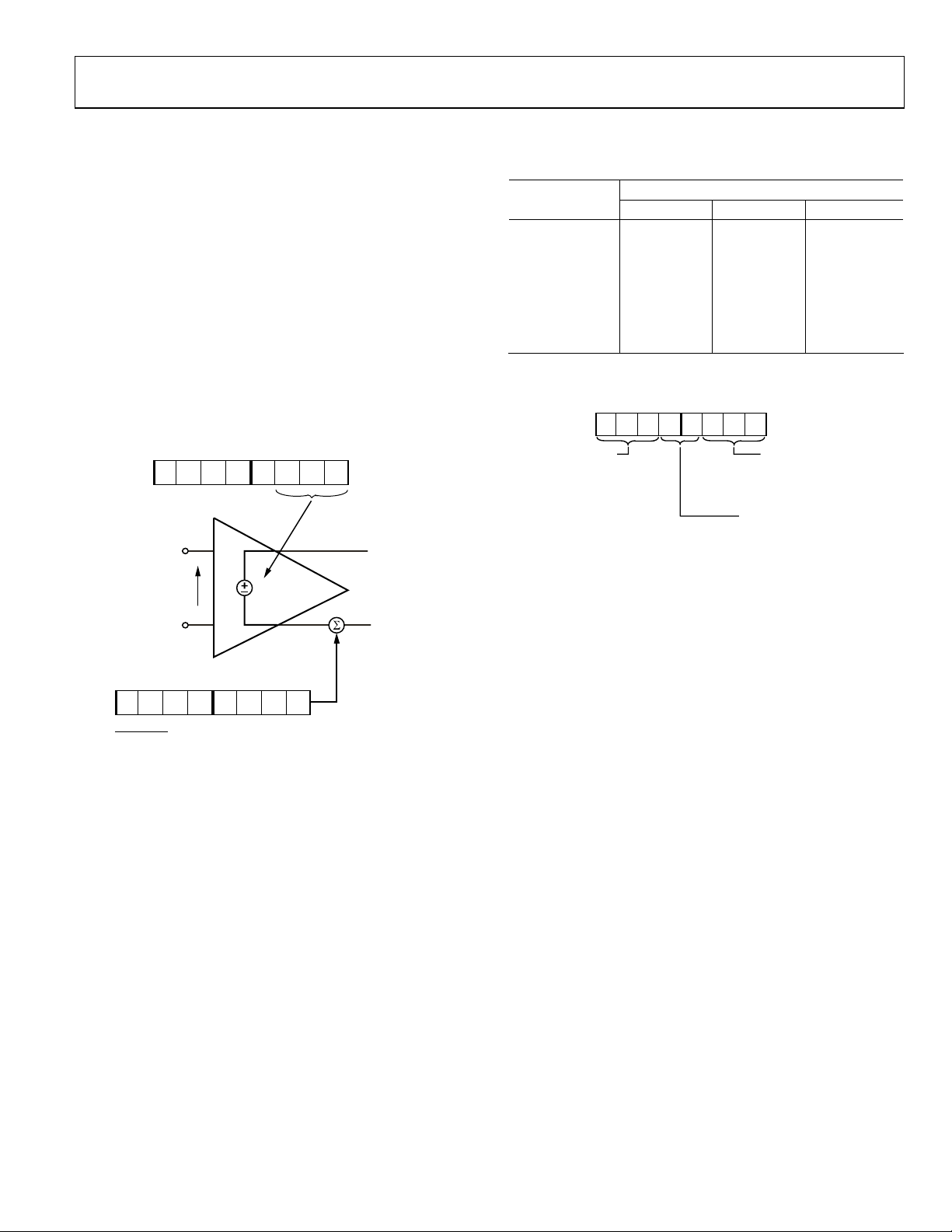

76 5 4 3 2 1 0

00 0 0 0 0 0 0

V1P

V

IN

V1N

7654 3210

0000 0000

CH1OS[7:0]

BITS 0 to 5: SIGN MAGNITUDE CODED OFFSET CORRECTION

BIT 6: NOT USED

BIT 7: DIGITAL INTEGRATOR (ON = 1, OFF = 0; DEFAULT OFF)

In addition to the PGA, Channel 1 also has a full-scale input

range selection for the ADC. The ADC analog input range

selection is also made using the gain register—see Figure 32. As

mentioned previously, the maximum differential input voltage is

0.5 V. However, by using Bits 3 and 4 in the gain register, the

maximum ADC input voltage can be set to 0.5 V, 0.25 V, or

0.125 V. This is achieved by adjusting the ADC reference—see

the ADE7753 Reference Circuit section. Table 5 summarizes the

maximum differential input signal level on Channel 1 for the

various ADC range and gain selections.

GAIN[7:0]

GAIN (K)

SELECTION

K × V

IN

Figure 31. PGA in Channel 1

+

OFFSET ADJUST

(±50mV)

02875-0-031

Table 5. Maximum Input Signal Levels for Channel 1

Max Signal ADC Input Range Selection

Channel 1 0.5 V 0.25 V 0.125 V

0.5 V Gain = 1 − −

0.25 V Gain = 2 Gain = 1 −

0.125 V Gain = 4 Gain = 2 Gain = 1

0.0625 V Gain = 8 Gain = 4 Gain = 2

0.0313 V Gain = 16 Gain = 8 Gain = 4

0.0156 V − Gain = 16 Gain = 8

0.00781 V − − Gain = 16

CHANNEL 1 AND CHANNEL 2 PGA CONTROL

PGA 2 GAIN SELEC

000 =× 1

×

2

001 =

×

4

010 =

×

8

011 =

×

16

100 =

*REGISTER CONTENTS

GAIN REGISTER*

7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0

SHOW POWER-ON DEFAULTS

ADDR:

0AH

PGA 1 GAIN SELECT

×

000 =

×

001 =

×

010 =

×

011 =

×

100 =

CHANNEL 1 FULL-SCALE SELECT

00 = 0.5V

01 = 0.25V

10 = 0.125V

Figure 32. ADE7753 Analog Gain Register

1

2

4

8

16

02875-0-032

It is also possible to adjust offset errors on Channel 1 and

Channel 2 by writing to the offset correction registers, CH1OS

and CH2OS, respectively. These registers allow channel offsets

in the range ±20 mV to ±50 mV (depending on the gain setting)

to be removed. Channel 1 and 2 offset registers are sign magnitude coded. A negative number is applied to the Channel 1

offset register, CH1OS, for a negative offset adjustment. Note

that the Channel 2 offset register is inverted. A negative number

is applied to CH2OS for a positive offset adjustment. It is not

necessary to perform an offset correction in an energy measurement application if HPF in Channel 1 is switched on. Figure 33

shows the effect of offsets on the real power calculation. As seen

from Figure 33, an offset on Channel 1 and Channel 2 contributes

a dc component after multiplication. Because this dc component

is extracted by LPF2 to generate the active (real) power information, the offsets contribute an error to the active power

calculation. This problem is easily avoided by enabling HPF in

Channel 1. By removing the offset from at least one channel, no

error component is generated at dc by the multiplication. Error

terms at cos(ωt) are removed by LPF2 and by integration of the

active power signal in the active energy register (AENERGY[23:0])

—see the Energy Calculation section.

Rev. A | Page 15 of 60

ADE7753

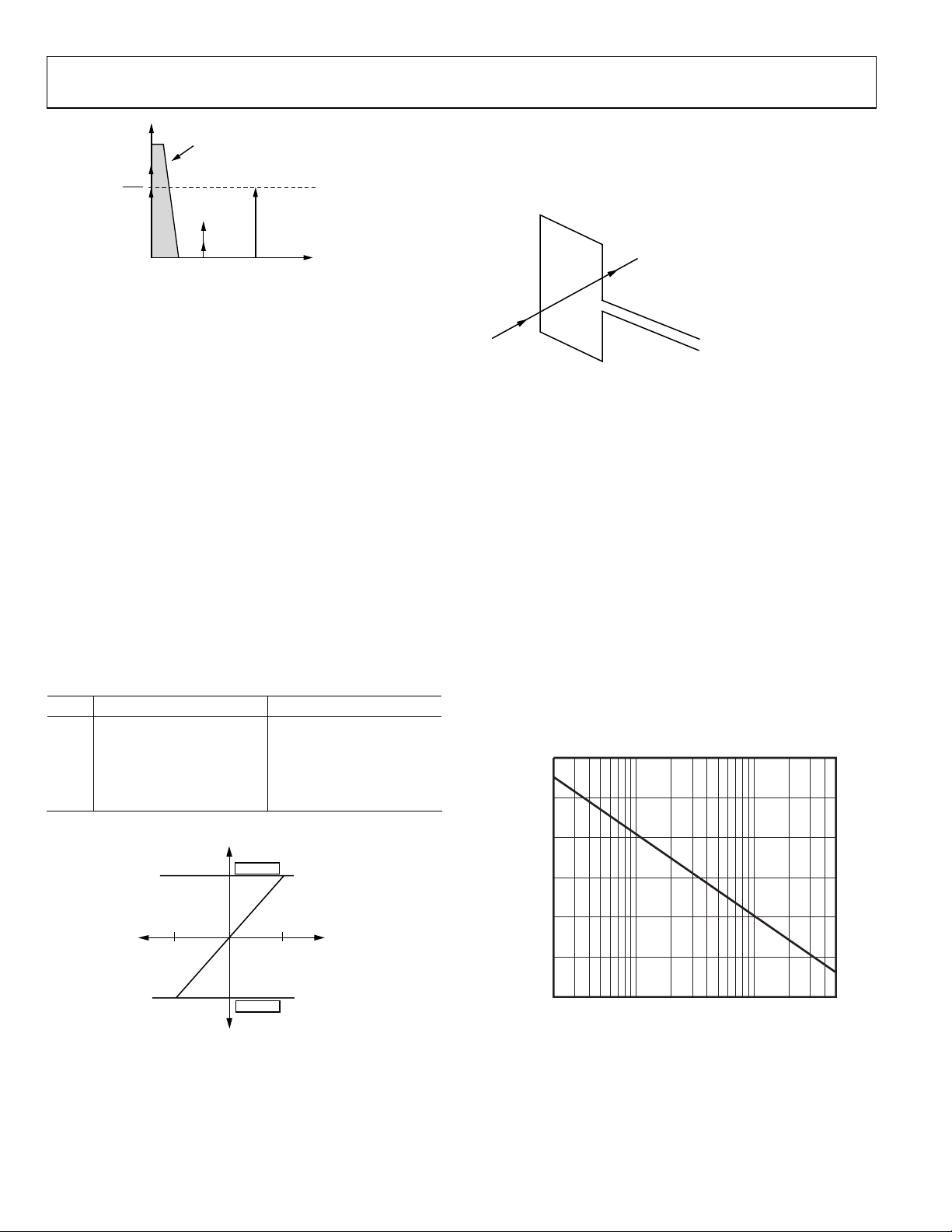

V

DC COMPONENT (INCLUDING ERROR TERM)

IS EXTRACTED BY THE LPF FOR REAL

× I

OS

OS

V × I

2

0

Figure 33. Effect of Channel Offsets on the Real Power Calculation

POWER CALCULATION

× V

I

OS

× I

V

OS

2ωω

FREQUENCY (RAD/S)

02875-0-033

di/dt CURRENT SENSOR AND DIGITAL INTEGRATOR

A di/dt sensor detects changes in magnetic field caused by ac

current. Figure 35 shows the principle of a di/dt current sensor.

MAGNETIC FIELD CREATED BY CURRENT

(DIRECTLY PROPORTIONAL TO CURRENT)

The contents of the offset correction registers are 6-bit, sign and

magnitude coded. The weight of the LSB depends on the gain

setting, i.e., 1, 2, 4, 8, or 16. Table 6 shows the correctable offset

span for each of the gain settings and the LSB weight (mV) for

the offset correction registers. The maximum value that can be

written to the offset correction registers is ±31d—see Figure 34.

Figure 34 shows the relationship between the offset correction

register contents and the offset (mV) on the analog inputs for a

gain setting of 1. In order to perform an offset adjustment, the

analog inputs should be first connected to AGND, and there

should be no signal on either Channel 1 or Channel 2. A read

from Channel 1 or Channel 2 using the waveform register

indicates the offset in the channel. This offset can be canceled

by writing an equal and opposite offset value to the Channel 1

offset register, or an equal value to the Channel 2 offset register.

The offset correction can be confirmed by performing another

read. Note when adjusting the offset of Channel 1, one should

disable the digital integrator and the HPF.

Table 6. Offset Correction Range—Channels 1 and 2

Gain Correctable Span LSB Size

1 ±50 mV 1.61 mV/LSB

2 ±37 mV 1.19 mV/LSB

4 ±30 mV 0.97 mV/LSB

8 ±26 mV 0.84 mV/LSB

16 ±24 mV 0.77 mV/LSB

CH1OS[5:0]

+ EMF (ELECTROMOTIVE FORCE)

– INDUCED BY CHANGES IN

MAGNETIC FLUX DENSITY (di/dt)

02875-0-035

Figure 35. Principle of a di/dt Current Sensor

The flux density of a magnetic field induced by a current is

directly proportional to the magnitude of the current. The

changes in the magnetic flux density passing through a

conductor loop generate an electromotive force (EMF) between

the two ends of the loop. The EMF is a voltage signal, which is

proportional to the di/dt of the current. The voltage output

from the di/dt current sensor is determined by the mutual

inductance between the current-carrying conductor and the

di/dt sensor. The current signal needs to be recovered from the

di/dt signal before it can be used. An integrator is therefore

necessary to restore the signal to its original form. The ADE7753

has a built-in digital integrator to recover the current signal

from the di/dt sensor. The digital integrator on Channel 1 is

switched off by default when the ADE7753 is powered up.

Setting the MSB of CH1OS register turns on the integrator.

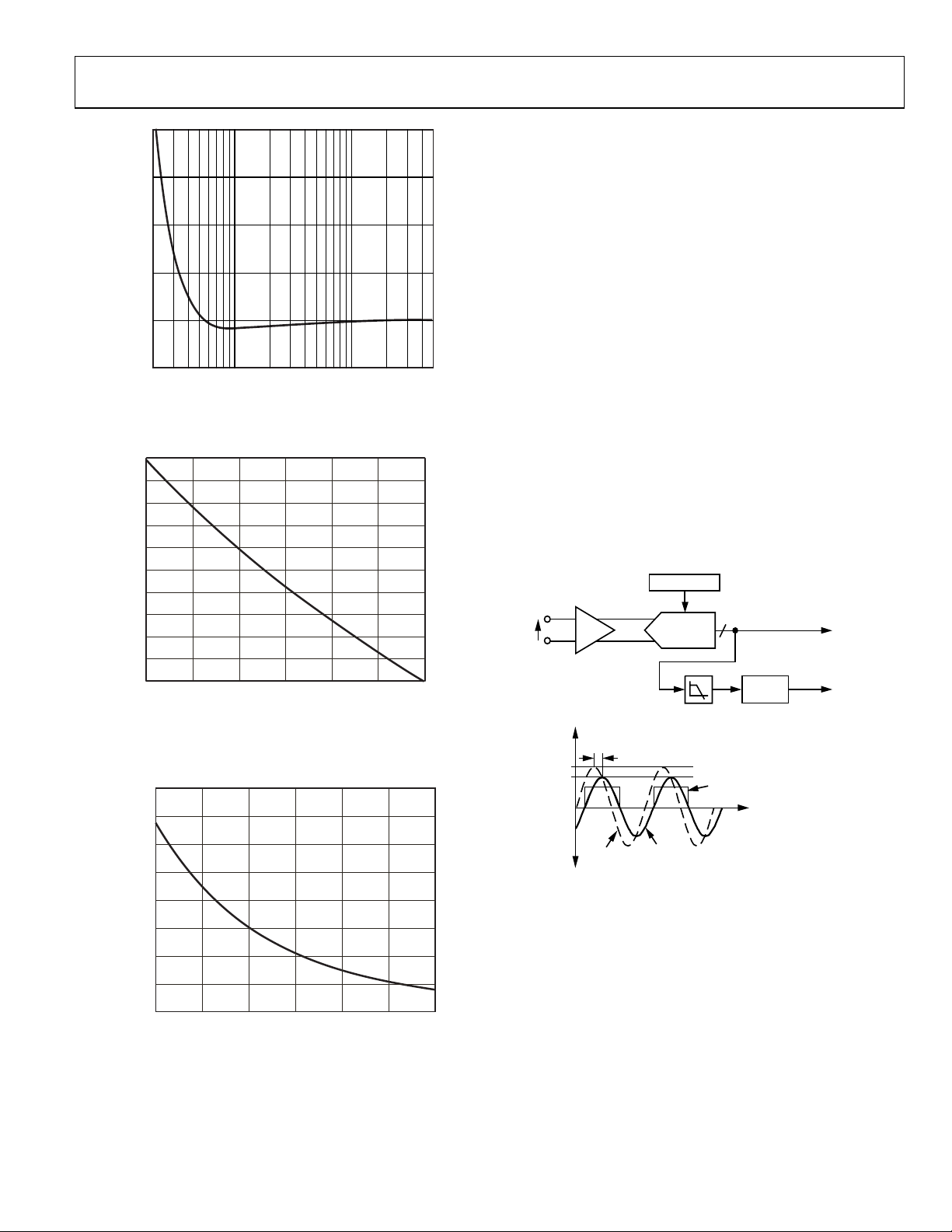

Figure 36 to Figure 39 show the magnitude and phase response

of the digital integrator.

10

0

–10

01,1111b

0x1F

0x00

0x3F

0mV

11,1111b

–50mV

Figure 34. Channel 1 Offset Correction Range (Gain = 1)

SIGN + 5 BITS

+50mV

OFFSET

ADJUST

SIGN + 5 BITS

02875-0-034

–20

GAIN (dB)

–30

–40

–50

2

10

FREQUENCY (Hz)

3

10

02875-0-036

Figure 36. Combined Gain Response of the

Digital Integrator and Phase Compensator

The current and voltage rms offsets can be adjusted with the

IRMSOS and VRMSOS registers—see Channel 1 RMS Offset

Compensation and Channel 2 RMS Offset Compensation

sections.

Rev. A | Page 16 of 60

ADE7753

×

V

–88.0

–88.5

–89.0

–89.5

PHASE (Degrees)

–90.0

Note that the integrator has a –20 dB/dec attenuation and an

approximately –90° phase shift. When combined with a di/dt

sensor, the resulting magnitude and phase response should be a

flat gain over the frequency band of interest. The di/dt sensor

has a 20 dB/dec gain associated with it. It also generates significant high frequency noise, therefore a more effective antialiasing filter is needed to avoid noise due to aliasing—see the

Antialias Filter section.

When the digital integrator is switched off, the ADE7753 can be

used directly with a conventional current sensor such as a current

transformer (CT) or with a low resistance current shunt.

–90.5

2

10

FREQUENCY (Hz)

FREQ

3

10

Figure 37. Combined Phase Response of the

Digital Integrator and Phase Compensator

–1.0

–1.5

–2.0

–2.5

–3.0

–3.5

GAIN (dB)

–4.0

–4.5

–5.0

–5.5

–6.0

40 7045

50 55 60 65

FREQUENCY (Hz)

Figure 38. Combined Gain Response of the

Digital Integrator and Phase Compensator (40 Hz to 70 Hz)

–89.70

–89.75

02875-0-037

02875-0-038

ZERO-CROSSING DETECTION

The ADE7753 has a zero-crossing detection circuit on

Channel 2. This zero crossing is used to produce an external

zero-crossing signal (ZX), and it is also used in the calibration

mode—see the Calibrating an Energy Meter Based on the

ADE7753 section. The zero-crossing signal is also used to

initiate a temperature measurement on the ADE7753—see the

Temperature Measurement section.

Figure 40 shows how the zero-crossing signal is generated from

the output of LPF1.

1,×2,×1,

×8,×

V2P

2

V2N

1.0

0.93

16

{GAIN [7:5]}

PGA2

REFERENCE

ADC 2

f

–

2.32° @ 60Hz

LPF1

= 140Hz

3dB

–63%TO +63% FS

1

ZERO

CROSS

ZX

TO

MULTIPL IER

ZX

–89.80

–89.85

–89.90

–89.95

PHASE (Degrees)

–90.00

–90.05

40 45 7050 55 60 65

FREQUENCY (Hz)

Figure 39. Combined Phase Response of the

Digital Integrator and Phase Compensator (40 Hz to 70 Hz)

02875-0-039

V2

Figure 40. Zero-Crossing Detection on Channel 2

The ZX signal goes logic high on a positive-going zero crossing

and logic low on a negative-going zero crossing on Channel 2.

The zero-crossing signal ZX is generated from the output of

LPF1. LPF1 has a single pole at 140 Hz (at CLKIN = 3.579545

MHz). As a result, there is a phase lag between the analog input

signal V2 and the output of LPF1. The phase response of this

filter is shown in the Channel 2 Sampling section. The phase lag

response of LPF1 results in a time delay of approximately

1.14 ms (@ 60 Hz) between the zero crossing on the analog

inputs of Channel 2 and the rising or falling edge of ZX.

LPF1

02875-0-040

Rev. A | Page 17 of 60

ADE7753

The zero-crossing detection also drives the ZX flag in the

IRQ

interrupt status register. An active low in the

appears if the corresponding bit in the interrupt enable register

is set to Logic 1.

The flag in the interrupt status register as well as the

are reset to their default values when the interrupt status register with reset (RSTSTATUS) is read.

Zero-Crossing Timeout

The zero-crossing detection also has an associated timeout

register, ZXTOUT. This unsigned, 12-bit register is decremented

(1 LSB) every 128/CLKIN seconds. The register is reset to its

user programmed full-scale value every time a zero crossing is

detected on Channel 2. The default power on value in this

register is 0xFFF. If the internal register decrements to 0 before a

zero crossing is detected and the DISSAG bit in the mode

SAG

register is Logic 0, the

zero crossing is also indicated on the

pin goes active low. The absence of a

IRQ

enable bit in the interrupt enable register is set to Logic 1.

Irrespective of the enable bit setting, the ZXTO flag in the

interrupt status register is always set when the internal

ZXTOUT register is decremented to 0—see the ADE7753

Interrupts section.

The ZXOUT register can be written/read by the user and has an

address of 1Dh—see the ADE7753 Serial Interface section. The

resolution of the register is 128/CLKIN seconds per LSB. Thus

the maximum delay for an interrupt is 0.15 second (128/CLKIN

12

).

× 2

Figure 41 shows the mechanism of the zero-crossing timeout

detection when the line voltage stays at a fixed dc level for more

than CLKIN/128 × ZXTOUT seconds.

output also

IRQ

pin if the ZXTO

output

The resolution of this register is 2.2 ms/LSB when CLKIN =

3.579545 MHz, which represents 0.013% when the line frequency is 60 Hz. When the line frequency is 60 Hz, the value of

the period register is approximately 7576d. The length of the

register enables the measurement of line frequencies as low as

13.9 Hz.

The period register is stable at ±1 LSB when the line is

established and the measurement does not change. A settling

time of 1.8 seconds is associated with this filter before the

measurement is stable.

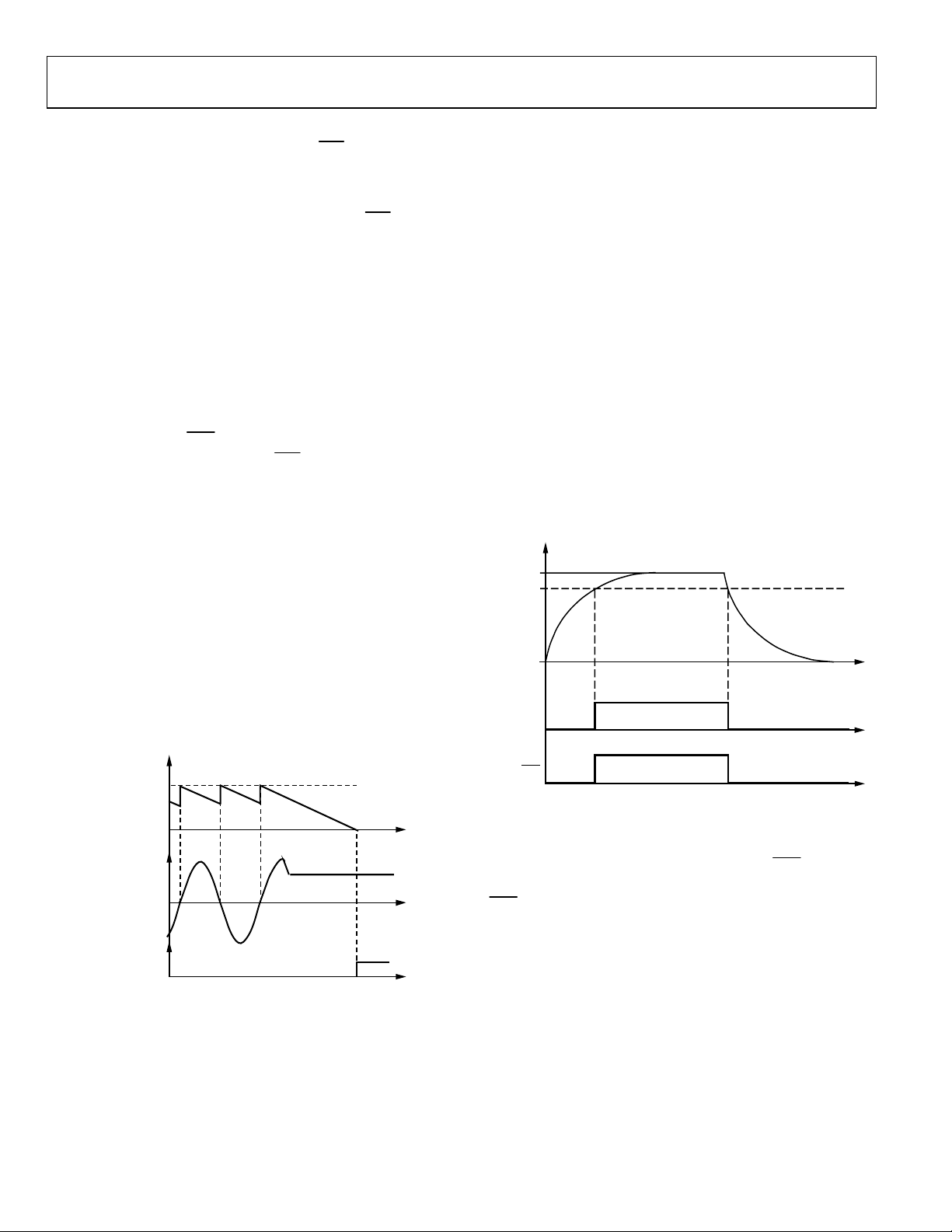

POWER SUPPLY MONITOR

The ADE7753 also contains an on-chip power supply monitor.

The analog supply (AVDD) is continuously monitored by the

ADE7753. If the supply is less than 4 V ± 5%, then the ADE7753

goes into an inactive state, that is, no energy is accumulated

when the supply voltage is below 4 V. This is useful to ensure

correct device operation at power-up and during power-down.

The power supply monitor has built-in hysteresis and filtering,

which give a high degree of immunity to false triggering due to

noisy supplies.

AV

DD

5V

4V

0V

ADE7753

POWER-ON

INACTIVE

STATE

INACTIVE

TIME

ACTIVE INACTIVE

12-BIT INTERNAL

REGISTER VALUE

ZXTOUT

CHANNEL 2

ZXTO

DETECTION

BIT

Figure 41. Zero-Crossing Timeout Detection

02875-0-041

PERIOD MEASUREMENT

The ADE7753 also provides the period measurement of the line.

The period register is an unsigned 16-bit register and is updated

every period. The MSB of this register is always zero.

Rev. A | Page 18 of 60

SAG

02875-0-042

Figure 42. On-Chip Power Supply Monitor

As seen in Figure 42, the trigger level is nominally set at 4 V. The

SAG

tolerance on this trigger level is about ±5%. The

pin can

also be used as a power supply monitor input to the MCU. The

SAG

pin goes logic low when the ADE7753 is in its inactive

state. The power supply and decoupling for the part should be

such that the ripple at AVDD does not exceed 5 V ±5%, as

specified for normal operation.

LINE VOLTAGE SAG DETECTION

In addition to the detection of the loss of the line voltage signal

(zero crossing), the ADE7753 can also be programmed to detect

when the absolute value of the line voltage drops below a

certain peak value for a number of line cycles. This condition is

illustrated in Figure 43.

Loading...

Loading...