T

查询ADAU1702供应商

SigmaDSP® 28/56-Bit Audio

Preliminary Technical Data

FEATURES

28/56-bit, 25 MHz digital audio processor

Stereo ADC: 102 dB dynamic range and -90 dB THD+N

4-channel DAC: 103 dB dynamic range and -90 dB THD+N

Complete stand-alone operation

• Self-boot from serial EEPROM

• Auxiliary ADC with four-input mux for analog

control

• GPIOs for digital controls and outputs

Fully programable with SigmaStudio™ graphical tool

Sampling rates up to 192 kHz supported

28-bit × 28-bit multiplier with 56-bit accumulator

Double precision mode for full 56-bit processing

Clock Oscillator for generating master clock from crystal

PLL for generating master clock from 64 × f

, or 512 × fS clocks

f

S

Flexible serial data I/O ports with I

2

S compatible, left-

justified, right-justified, and TDM serial port modes

On-chip voltage regulator for compatibility with 3.3 V

systems

48-lead LQFP plastic package

GENERAL DESCRIPTION

The ADAU1702 is a stand-alone 28/56-bit audio DSP which

handles all system processing and control tasks. Processing

includes equalization, crossover, bass enhancement, multiband

dynamics processing, delay compensation, speaker

compensation, and stereo image widening. These algorithms

can be used to compensate for the real-world limitations of

speakers, amplifiers, and listening environments, resulting in a

dramatic improvement of perceived audio quality.

The signal processing used in the ADAU1702 is comparable to

that found in high end studio equipment. Most of the

processing is done in full 56-bit double-precision mode,

resulting in very good low level signal performance. The

ADAU1702 is a fully-programmable DSP. The easy-to-use

SigmaStudio software allows the user to graphically configure a

custom signal processing flow using blocks such as biquad

, 256 × fS, 384 ×

S

Processor with 2ADC/4DAC

ADAU1702

APPLICATIONS

Multimedia audio speaker systems

MP3 player speaker docks

Automotive head units

Mini-component stereos

Digital televisions

Studio monitors

Speaker crossover

Musical instrument effects boxes

In-seat sound systems (aircrafts/motor coaches)

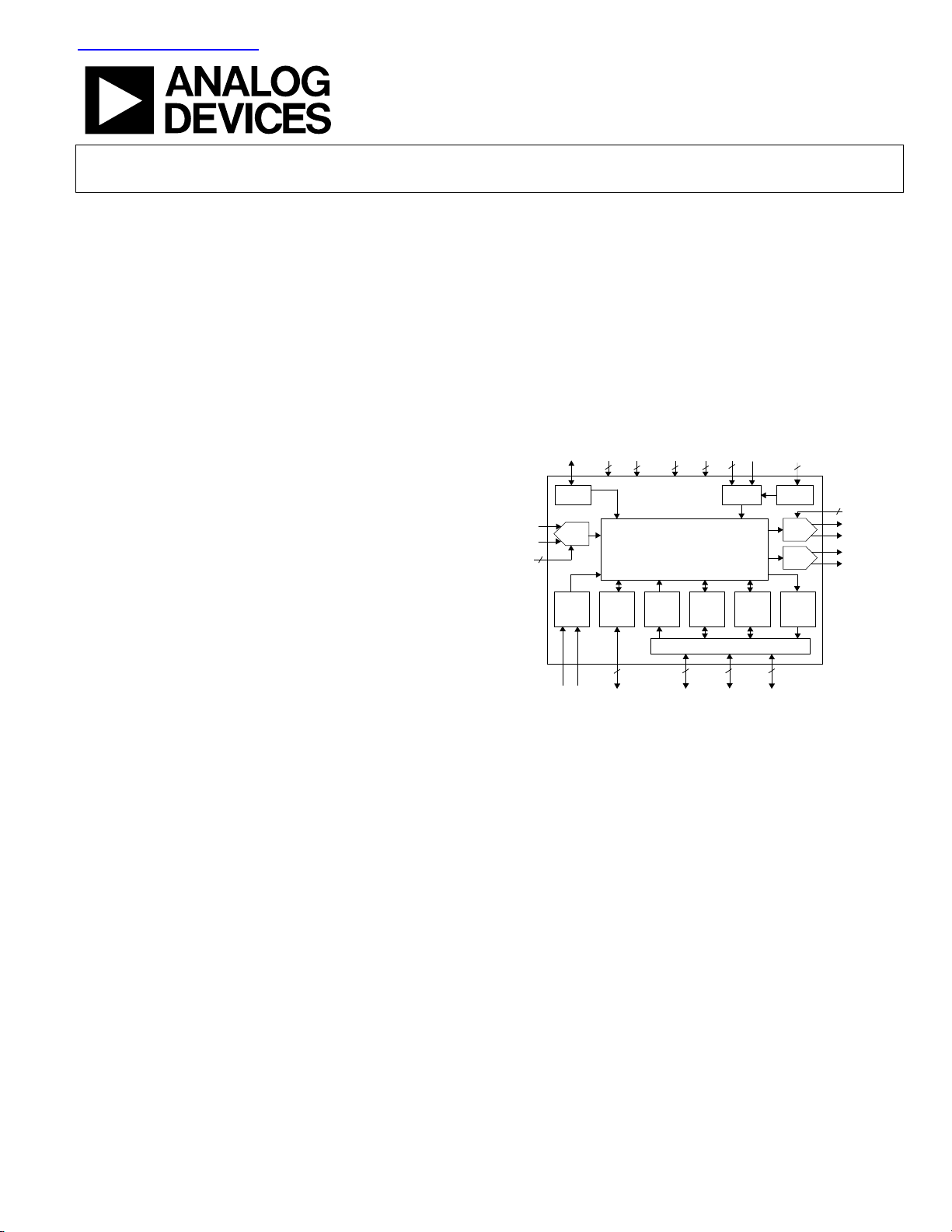

FUNCTIONAL BLOCK DIAGRAM

ANALOG

DIGITAL

DIGITAL

2-CHANNEL

ANALOG

INPU

FILTA /

ADC_RES

2

3.3 V

1.8 V

REGULATOR

STEREO

ADC

RESET/

MODE

SELECT

RESET

SELF

BOOT

VDD

3

CONTROL

INTERFACE

AND

SELFBOOT

I2C/SPI &

WRITEBACK

5

GROUND

3 3 3

filters, dynamics processors, level controls, and GPIO interface

controls.

ADAU1702 programs can be loaded on power-up either from a

serial EEPROM though its own self-boot mechanism or from

an external microcontroller. On power-down, the current state

of the parameters can be written back to the EEPROM from the

ADAU1702 to be recalled the next time the program is run.

The ADAU1702’s two ADCs and four DACs provide an analogin to analog-out dynamic range greater than 98 dB and THD+N

better than -92 dB. Digital input and output ports allow a

glueless connection to additional ADCs and DACs. The

ADAU1702 operates with either an I

ANALOG

VDD

GROUND

S

28/56-BIT, 25 MHz

AUDIO PROCESSOR CORE

10 ms DELAY MEMORY

8-CH

DIGITAL

INPUT

8-BIT

AUX

ADC

INPUT/OUTPUT MATRIX

4 4 4

DIGITAL IN

OR

GPIO

Figure 1.

PLL

LOOP

PLL

FILTER

MODE

3

PLL

AUX ADC

OR

GPIO

2

C bus or a 4-wire SPI port.

GPIO

CLOCK

OSCILLATOR

DIGITAL OUT

OR

GPIO

CRYSTAL

DAC

DAC

8-CH

DIGITAL

OUTPUT

2

FILTD / CM

2

4-CHANNEL

ANALOG

OUTPUT

Rev. PrC

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

ADAU1702 Preliminary Technical Data

TABLE OF CONTENTS

Introduction ...................................................................................... 3

Recommended Program/Parameter Loading Procedure ..... 22

Specifications..................................................................................... 4

Analog Performance .................................................................... 4

Digital I/O ..................................................................................... 5

Power.............................................................................................. 5

Temperature Range ...................................................................... 5

Digital Timing............................................................................... 5

PLL ................................................................................................. 6

Regulator........................................................................................ 6

Absolute Maximum Ratings............................................................ 7

ESD Caution.................................................................................. 7

Digital Timing Diagrams................................................................. 8

Pin Configuration and Function Descriptions........................... 10

Pin Functions .................................................................................. 12

Signal Processing ............................................................................ 14

Overview...................................................................................... 14

Safeload Registers....................................................................... 22

Data Capture Registers.............................................................. 22

DSP Core Control Register....................................................... 23

Interface Registers...................................................................... 23

Control Port Read/Write Data Formats .................................. 23

Multipurpose Pins.......................................................................... 26

GPIO pin Setting Register......................................................... 26

Multi-Purpose pin Configuration Registers........................... 26

Auxiliary ADC............................................................................ 26

General Purpose Input/Outputs .............................................. 27

Serial Data Input/Output Ports ................................................ 27

Serial Output Control Registers ............................................... 28

Serial Input Control Register.................................................... 29

Two-Channel Audio ADC ............................................................ 31

Four-Channel DAC........................................................................ 32

Numeric Formats........................................................................ 14

Programming.............................................................................. 14

Control Port.....................................................................................15

Overview...................................................................................... 15

SPI Port........................................................................................ 15

I2C Port ........................................................................................ 15

Self boot ....................................................................................... 18

RAMs and Registers ....................................................................... 21

Control Port Addressing............................................................ 21

Parameter RAM.......................................................................... 21

REVISION HISTORY

9/05—Preliminary Version PrC1

Initialization.................................................................................... 33

Power-Up Sequence................................................................... 33

Setting Master Clock/PLL Mode.............................................. 33

Voltage Regulator....................................................................... 33

Layout Recommendations............................................................. 34

Parts Placement .......................................................................... 34

Grounding................................................................................... 34

Outline Dimensions....................................................................... 35

Ordering Guide .......................................................................... 35

Rev. PrC | Page 2 of 37

Preliminary Technical Data ADAU1702

INTRODUCTION

, 384 × fS, or 512 × fS to generate the core’s internal

256 × f

The core of the ADAU1702 is a 28-bit DSP (56-bit with double

precision) optimized for audio processing. The part’s program

and parameter RAMs can be loaded with a custom audio

processing signal flow built with ADI’s SigmaStudio graphical

programming software. The values stored in the parameter

RAM control individual signal processing blocks, such as IIR

equalization filters, dynamics processors, audio delays, and

mixer levels. A safeload feature allows parameters to be

transparently updated without causing clicks on the output

signals.

The program RAM, parameter RAM, and register contents can

be saved in an external EEPROM, from which the ADAU1702

can self-boot on start-up. In this stand-alone mode, parameters

can be controlled through the on-board multipurpose pins.

The ADAU1702 can accept controls from switches,

potentiometers, rotary encoders, and IR receivers. Parameters

such as volume and tone settings can be saved to the EEPROM

on power-down and recalled when it is powered up again.

The ADAU1702 can operate with either digital or analog I/Os,

or a mix of both. The stereo ADC and four-channel DAC have

an analog-to-analog SNR of 97 dB. … The flexible serial data

input/output ports allow for glueless interconnection to a

variety of ADCs, DACs, general-purpose DSPs, S/PDIF

receivers & transmitters, and sample rate converters. The

2

ADAU1702 can be configured in I

S, left-justified, right-

justified, or TDM serial port compatible modes.

Twelve multi-purpose (MP) pins allow for the ADAU1702 to

input external control signals and output flags or controls to

other devices in the system. These MP pins can be configured

as digital I/Os, inputs to the 4-channel auxiliary ADC, or set up

as the serial data I/O ports. As inputs, these can be connected

to buttons, switches, rotary encoders, potentiometers, IR

receivers, or other external control circuitry to control the

internal signal processing program. When configured as

outputs, these pins can be used to drive LEDs (with a buffer),

control other ICs, or connect to other external circuitry in an

application.

The ADAU1702 has a sophisticated control port that supports

complete read/write capability of all memory locations. Control

registers are provided to offer complete control of the chip’s

configuration and serial modes. Handshaking is included for

ease of memory uploads/downloads. The ADAU1702 can be

2

configured for either SPI or I

C control.

An on-board oscillator can be connected to an external crystal

to generate the master clock. Also, a master clock phase-locked

loop (PLL) allows the ADAU1702 to be clocked from a variety

of different clock speeds. The PLL can accept inputs of 64 × f

,

S

S

master clock.

The SigmaStudio software is used to program and control the

SigmaDSP through the control port. Along with designing and

tuning a signal flow, the tools can configure the all registers and

burn a new program into the external EEPROM. SigmaStudio’s

graphical interface allows anyone with digital or analog audio

processing knowledge to easily design a DSP signal flow and

port it to a target application. It also provides enough flexibility

and programmability for an experienced DSP programmer to

have in-depth control of the design. In SigmaStudio, the user

can simply connect graphical blocks such as biquad filters,

dynamics processors, mixers, and delays, compile the design,

and load the program and parameter files into the ADAU1702’s

memory through the control port. Signal processing blocks

available in the provided libraries include

• Single- and double-precision biquad filters

• Mono and multichannel dynamics processors with peak or

RMS detection

• Mixers and splitters

• Tone and noise generators

• Fixed and variable gain

• Loudness

• Delay

• Stereo enhancement

• Dynamic bass boost

• Noise and tone sources

• Level detectors

• GPIO control & conditioning

More processing blocks are always in development. Analog

Devices also provides proprietary and third-party algorithms

for applications such as matrix decoding, bass enhancement,

and surround virtualizers. Please contact ADI for information

about licensing these algorithms.

The ADAU1702 operates from a 1.8 V digital power supply, and

a 3.3 V analog supply. An on-board voltage regulator can be

used to operate the digital circuitry from a 3.3 supply. It is

fabricated on a single monolithic integrated circuit and is

housed in a 48-lead LQFP package for operation over the –0°C

to +70°C temperature range.

Rev. PrC | Page 3 of 37

ADAU1702 Preliminary Technical Data

SPECIFICATIONS

Test conditions, unless otherwise noted.

Table 1.

Parameter Conditions

Analog Supply Voltage (AVDD)

Digital Supply Voltage (DVDD)

PLL Voltage (PVDD)

Output Voltage (IOVDD)

Ambient Temperature

Master Clock Input

Load Capacitance

Load Current

Input Voltage, HI

Input Voltage, LO

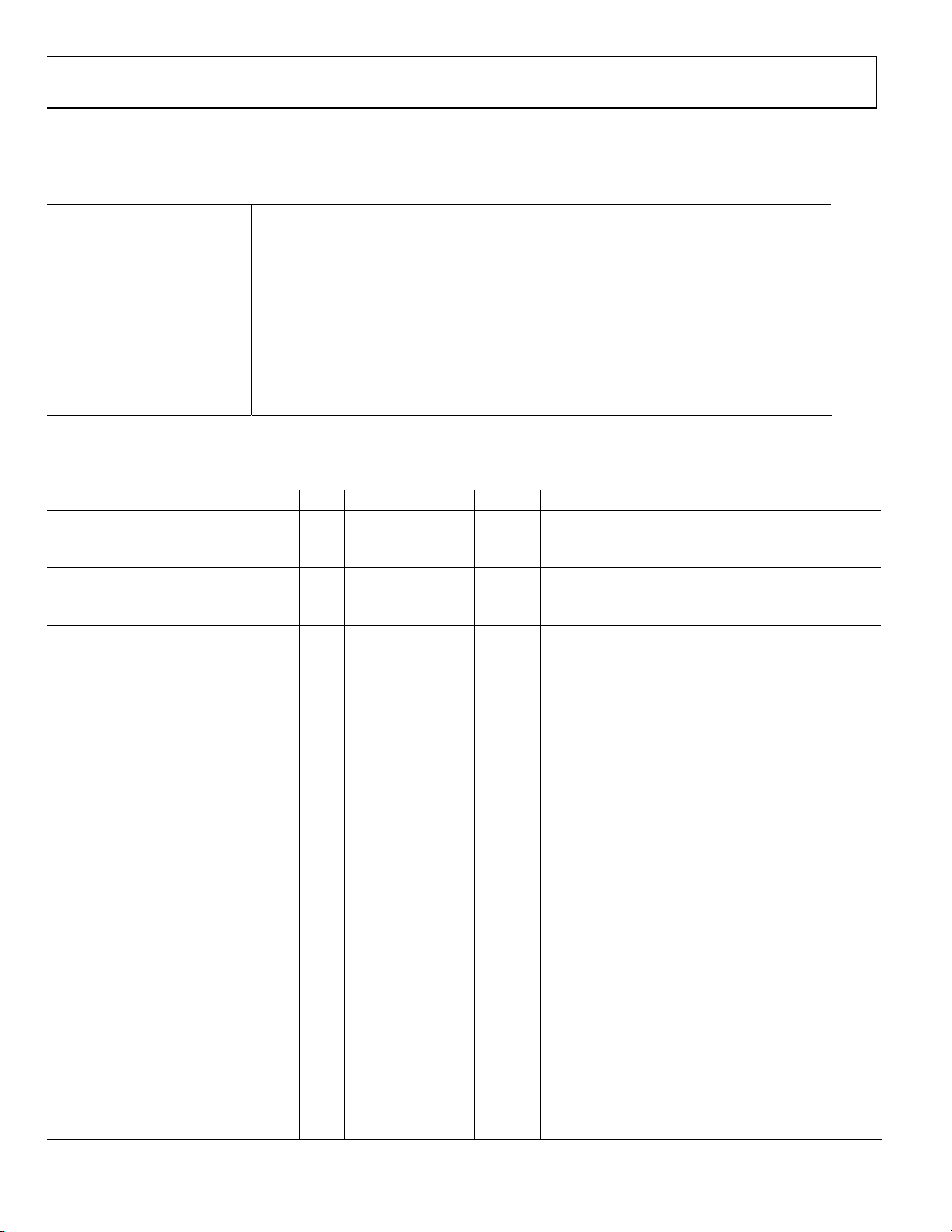

ANALOG PERFORMANCE

Table 2. Analog Performance

Parameter Min Typical Max Units Test Conditions/Comments

REFERENCE SECTION

Absolute Voltage V

V

Temperature Coefficient TBD ppm/°C

REF

AUX ANALOG INPUTS

Full Scale Analog Input 3.3 V

Step size 13 mV

ADC INPUTS

Number of channels 2 Stereo ADC

Resolution 24 Bits

Full Scale Analog Input

Signal-to-Noise Ratio

A-Weighted 100 dB

Dynamic Range -60dB with respect to full scale Analog input

A-Weighted TBD dB

Total Harmonic Distortion + Noise -95 dB -xxdB with respect to full scale Analog input

Interchannel Gain Mismatch TBD dB Left and Right channel Gain Mismatch

Crosstalk TBD dB Analog Channel Crosstalk

DC Bias TBD V

Gain Error TBD dB

Power Supply Rejection TBD dB 1kHz, 300mV

DAC OUTPUTS

Number of channels 4 2 stereo output channels

Resolution 24 Bits

Full Scale Analog Output 1 Vrms

Signal-to-Noise Ratio

A-Weighted 105 dB

Dynamic Range -60dB with respect to full scale Analog input

A-Weighted TBD dB

Total Harmonic Distortion + Noise -95 dB -xxdB with respect to full scale Analog input

Crosstalk TBD dB Analog Channel Crosstalk

Interchannel Gain Mismatch TBD dB Left and Right channel Gain Mismatch

DC Bias 1.5 V

Power Supply Rejection TBD dB 1kHz, 300mV

1.5 V

REF

100

μArms

2Vrms input with 20kΩ series resistor

Signal at AVDD

P-P

Signal at AVDD

P-P

Rev. PrC | Page 4 of 37

Preliminary Technical Data ADAU1702

DIGITAL I/O

Table 3. Digital I/O

Parameter Min Max Unit

Input Voltage, HI (VIH) V

Input Voltage, LO (VIL) V

Input Leakage (IIH) μA

Input Leakage (IIL) μA

Low Level Output Voltage (VOL) IOVDD = x.x V, IOL = xx mA V

Low Level Output Voltage (VOL) IOVDD = x.x V, IOL = xx mA V

Input Capacitance pF

POWER

Table 4.

Parameter Comments Min Typ Max1 Unit

Supplies

Analog Voltage 3.3 V

Digital Voltage 1.8 V

PLL Voltage 3.3 V

Analog Current TBD mA

Digital Current TBD mA

PLL Current TBD mA

Analog Current, Reset TBD mA

Digital Current, Reset TBD mA

PLL Current, Reset TBD mA

Dissipation

Operation, all supplies TBD mW

Reset, all supplies TBD mW

1

Maximum specifications are measured across −xx°C to xx°C (case) and across VDD = xxx V to xxx V.

TEMPERATURE RANGE

Table 5.

Parameter Min Typ Max Unit

Functionality Guaranteed xx°C xx°C °C Ambient

xx°C xx°C °C Case

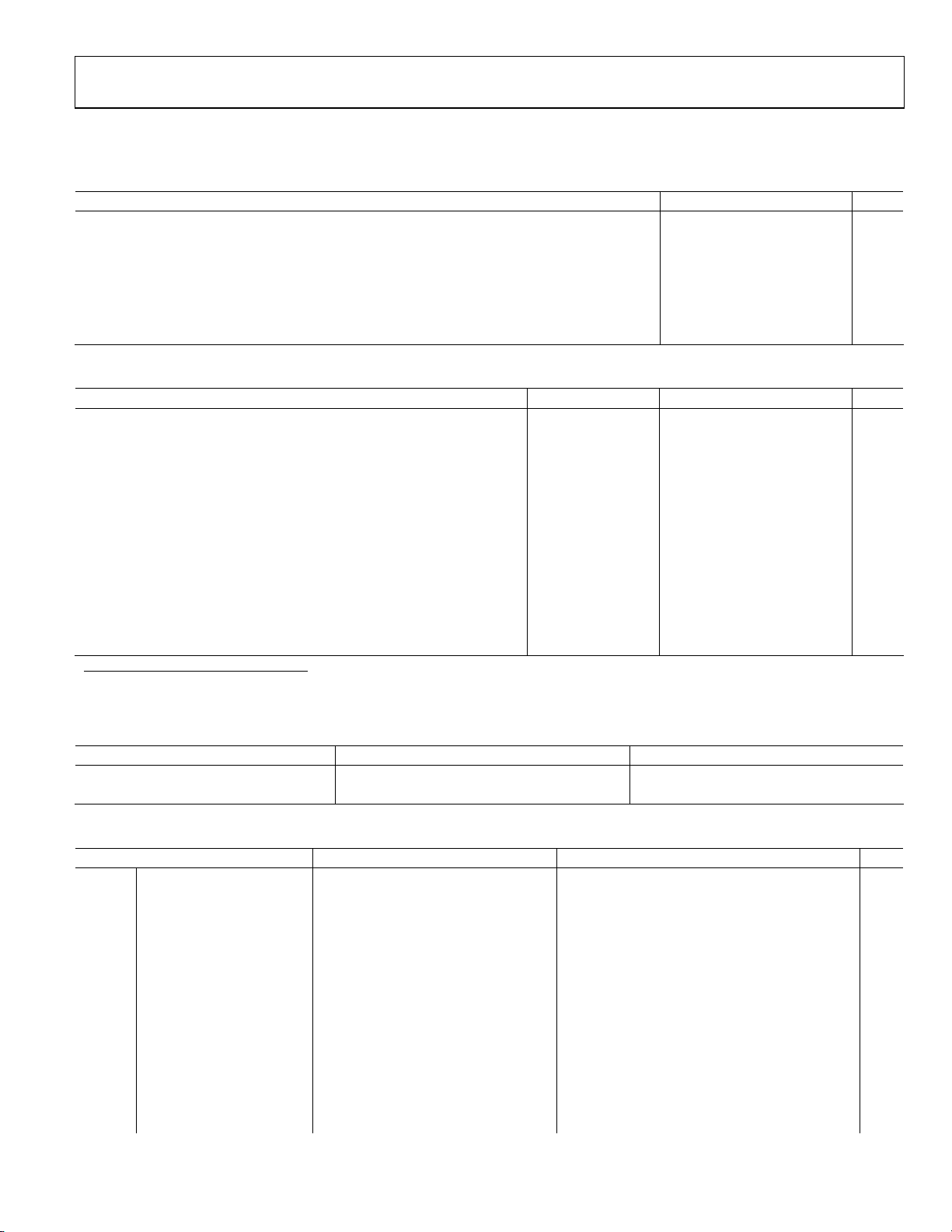

DIGITAL TIMING

Table 6 Digital Timing1

Parameter Comments Min Max Unit

tMP MCLK Period 512 fS mode ns

tMP MCLK Period 384 fS mode ns

tMP MCLK Period 256 fS mode ns

tMP MCLK Period 64 fS mode ns

tMP MCLK Period Bypass mode ns

t

MCLK Duty Cycle Bypass mode %

MDC

t

BCLK_IN LO Pulse Width ns

BIL

t

BCLK_IN HI Pulse Width ns

BIH

t

LRCLK_IN Setup To BCLK_IN rising ns

LIS

t

LRCLK_IN Hold From BCLK_IN rising ns

LIH

t

SDATA_INx Setup To BCLK_IN rising ns

SIS

t

SDATA_INx Hold From BCLK_IN rising ns

SIH

t

LRCLK_OUTx Setup Slave mode ns

LOS

t

LRCLK_OUTx Hold Slave mode ns

LOH

Rev. PrC | Page 5 of 37

ADAU1702 Preliminary Technical Data

tTS

t

SODS

t

SODM

t

CCPL

t

CCPH

t

CLS

t

CLH

t

CLPH

t

CDS

t

CDH

t

COD

t

RLPW

f

SCL

t

t

t

t

SCLH

SCLL

SCS

SCH

BCLK_OUTx Falling to

LRCLK_OUTx Timing Skew

SDATA_OUTx Delay Slave mode, from BCLK_OUTx falling ns

SDATA_OUTx Delay Master mode, from BCLK_OUTx falling ns

CCLK Pulse Width LO

CCLK Pulse Width HI

CLATCH Setup To CCLK rising ns

CLATCH Hold From CCLK rising

CLATCH Pulse Width HI

CDATA Setup To CCLK rising ns

CDATA Hold From CCLK rising

COUT Delay From CCLK rising

RESETB LO Pulse Width ns

SCL Clock Frequency TBD kHz

SCL High TBD μS

SCL Low TBD μS

Setup Time Relevant for Repeated Start Condition TBD μS

Hold Time

tDS Data Setup Time TBD ns

t

SCL Rise Time TBD ns

SCR

t

SCL Fall Time TBD ns

SCF

t

SDA Rise Time TBD ns

SDR

t

SDA Fall Time TBD ns

SDF

1

All timing specifications are given for the default (I2S) states of the serial input control port and the serial output control ports. See Table 40.

After this period the 1st clock is

generated

ns

ns

ns

ns

ns

ns

ns

TBD μS

PLL

Table 7.

Parameter Min Typ Max Unit

Lock Time TBD ms

REGULATOR

Table 8.

Parameter Min Typ Max Unit

DVDD Voltage 1.8 V

Rev. PrC | Page 6 of 37

Preliminary Technical Data ADAU1702

ABSOLUTE MAXIMUM RATINGS

Table 9.

Parameter Min Max Unit

DVDD to GND V

AVDD to GND V

IOVDD to GND V

Digital Inputs V

Maximum Junction Temperature 135 °C

Storage Temperature Range –65 +150 °C

Soldering (10 sec) 300 °C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only;

functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is

not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 10. Package Characteristics

Parameter Min Typ Max Unit

θJA Thermal Resistance (Junction-to-Ambient) 72 °C/W

θJC Thermal Resistance (Junction-to-Case) 19.5 °C/W

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. PrC | Page 7 of 37

ADAU1702 Preliminary Technical Data

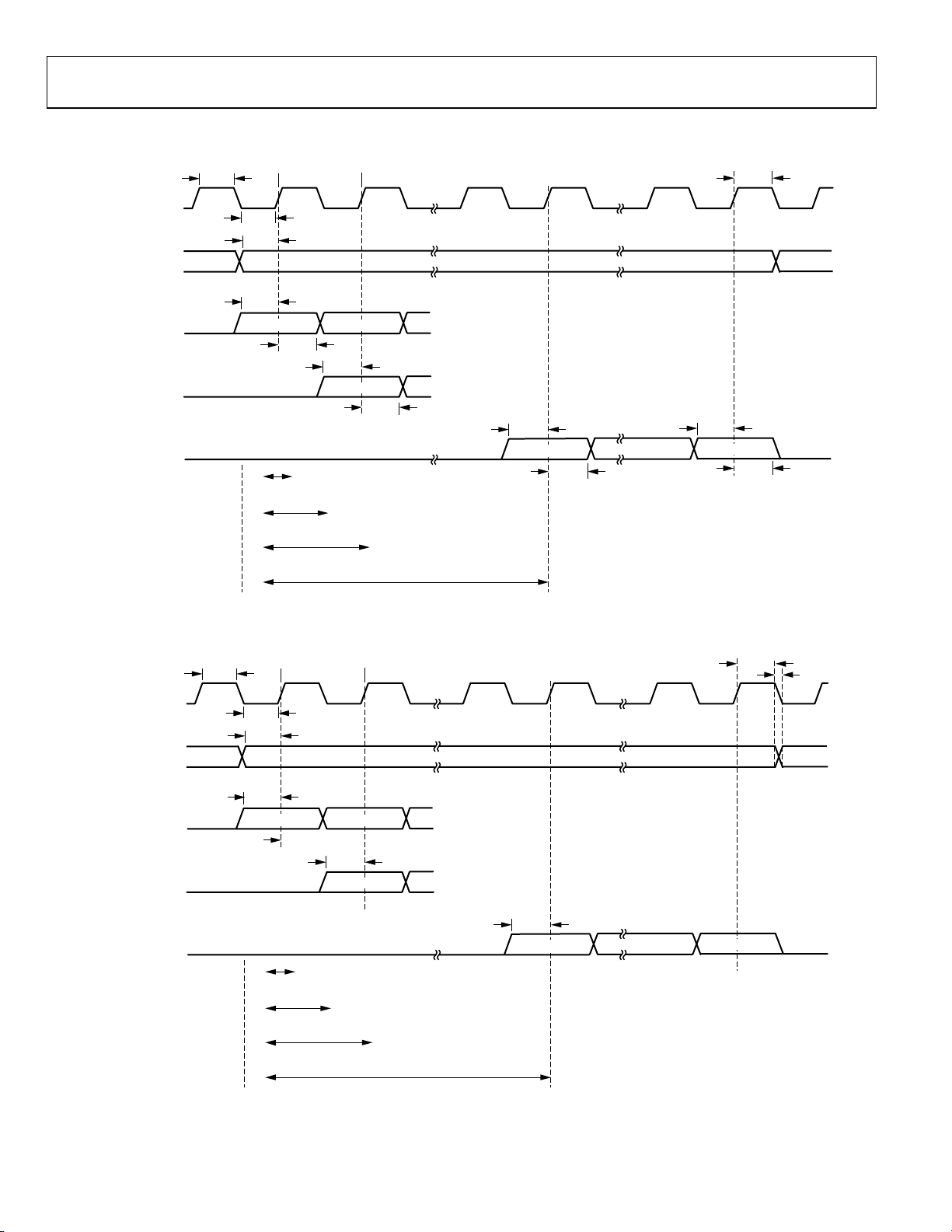

DIGITAL TIMING DIAGRAMS

BCLK_IN

LRCLK_IN

SDATA_INX

LEFT-JUSTIFIED

MODE

SDATA_INX

2

I

S-JUSTIFIED

MODE

SDATA_INX

RIGHT-JUSTIFIED

MODE

BCLK_OUTX

LRCLK_OUTX

t

BIH

t

BIL

t

LIS

t

SIS

MSB

t

SIH

8-BIT CLOCKS

(24-BIT DATA)

12-BIT CLOCKS

(20-BIT DATA)

14-BIT CLOCKS

(18-BIT DATA)

16-BIT CLOCKS

(16-BIT DATA)

t

SIS

MSB-1

MSB

t

SIH

t

SIS

MSB

t

SIH

Figure 2. Serial Input Port Timing

t

BIH

t

BIL

t

LOS

t

LCH

t

LIH

t

SIS

LSB

t

SIH

04607-0-013

t

TS

SDATA_OUTX

LEFT-JUSTIFIED

MODE

SDATA_OUTX

2

I

S-JUSTIFIED

MODE

SDATA_OUTX

RIGHT-JUSTIFIED

MODE

t

SDDS

t

SDDM

MSB

8-BIT CLOCKS

(24-BIT DATA)

12-BIT CLOCKS

(20-BIT DATA)

14-BIT CLOCKS

(18-BIT DATA)

16-BIT CLOCKS

(16-BIT DATA)

t

SDDS

t

SDDM

MSB-1

MSB

Figure 3. Serial Output Port Timing

Rev. PrC | Page 8 of 37

t

SDDS

t

SDDM

MSB

LSB

04607-0-014

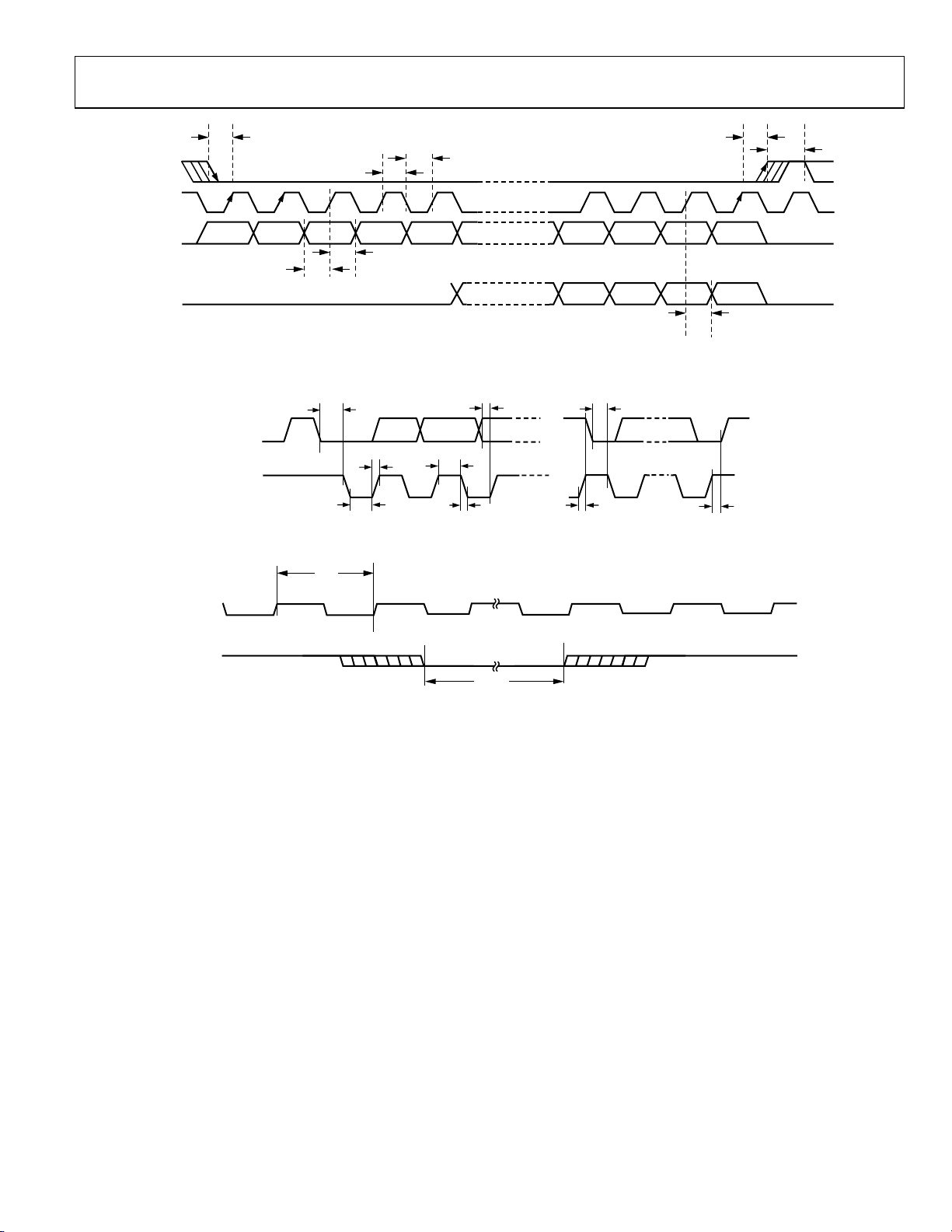

Preliminary Technical Data ADAU1702

t

CLS

t

CCPL

CLATCH

CCLK

CDATA

COUT

t

CDS

t

CCPH

t

CDH

Figure 4. SPI Port Timing

t

TSCH

SDA

t

SR

SCLK

t

SCLL

t

MP

t

DS

t

SCLH

t

ST

Figure 5. I

2

C Port Timing

t

SCS

t

TSCH

t

CLH

t

COD

t

SSH

04607-026

t

CLPH

04607-0-015

MCLK

RESETB

t

RLPW

Figure 6. Master Clock and Reset Timing

04607-0-016

Rev. PrC | Page 9 of 37

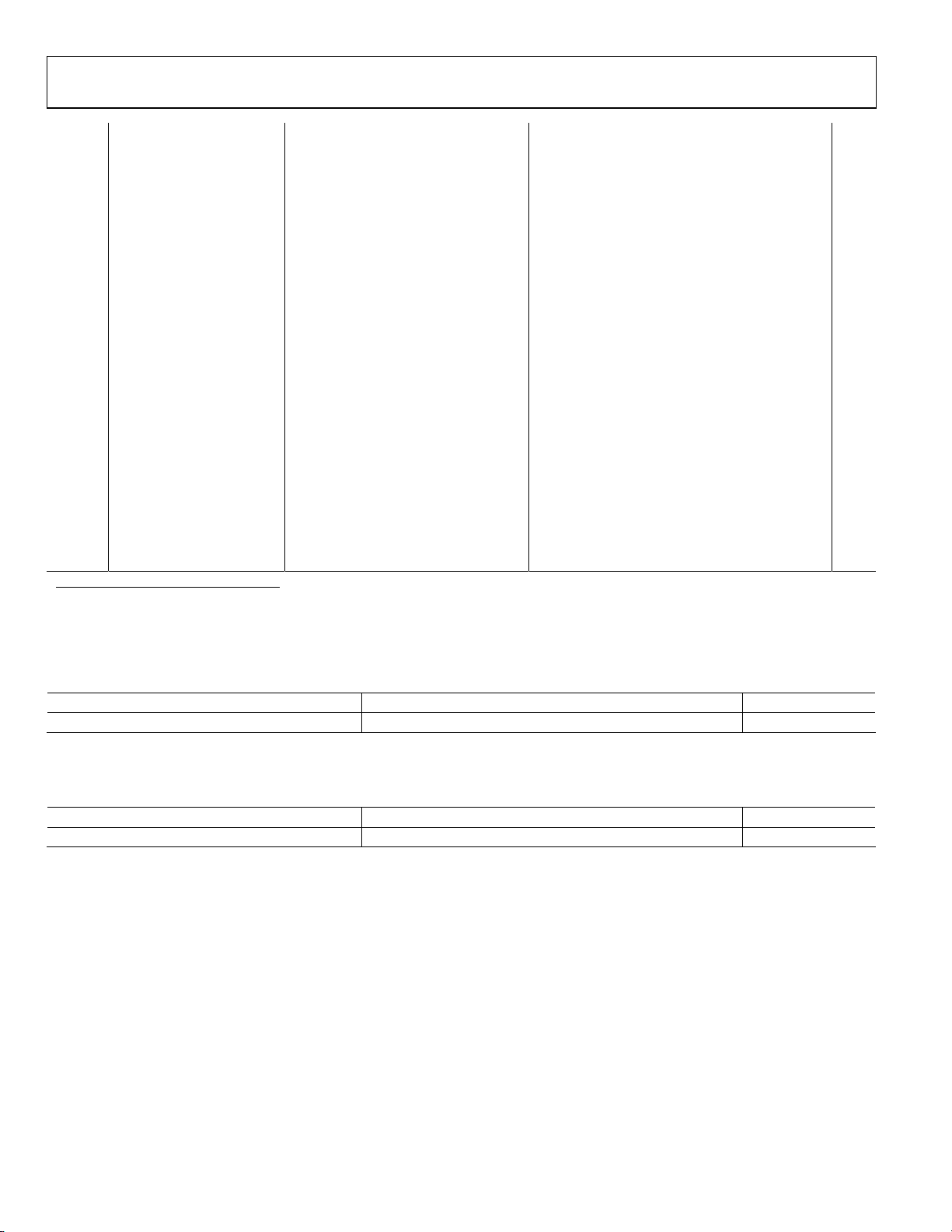

ADAU1702 Preliminary Technical Data

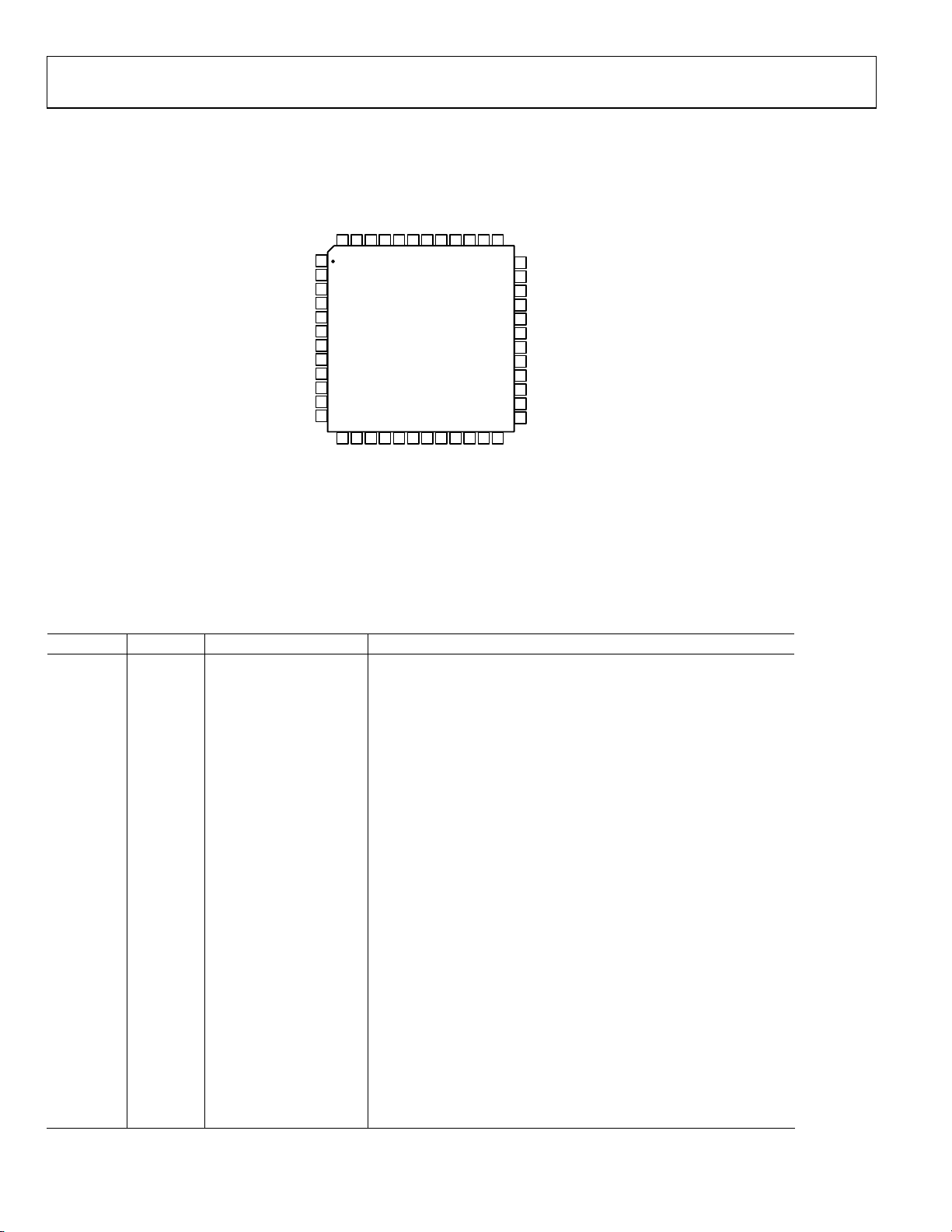

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

0

E

E

D

D

O

3

2

0

1

T

T

T

T

D

U

U

U

N

O

O

O

G

V

V

V

A

ADAU1702

TOP VIEW

(Not to Scal e)

0

1

E

D

1

1

V

D

I

P

P

V

R

M

M

O

D

I

V

AGND

ADC1

ADC_RES

ADC0

RESETB

SELFBOOT

ADDR0

MP4

MP5

MP1

MP0

DGND

D

A

U

T

D

L

O

V

I

V

A

F

48 47 46 45 44 39 38 3743 42 41 40

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

6

7

D

P

P

D

M

M

V

D

Figure 7. 48-Lead LQFP Pin Configuration

Table 11. Pin Function Descriptions

Pin No. I/O Mnemonic Description

1 AGND Analog Ground

2 IN ADC1 Analog input 1

3 ADC_RES Reference current – connect resistor

4 IN ADC0 Analog Input 0

5 IN RESETB Reset, Active Low

6 IN SELFBOOT Select Host or Self-boot mode

7 IN ADDR0 I2C and SPI Address 0

8 IN/OUT MP4 Multi-Purpose – GPIO or Serial input port LRCLK

9 IN/OUT MP5 Multi-Purpose – GPIO or Serial input port BCLK

10 IN/OUT MP1 Multi-Purpose – GPIO or Serial Input port data 1

11 IN/OUT MP0 Multi-Purpose – GPIO or Serial Input port data 0

12 DGND Digital Ground

13 DVDD 1.8 V Digital Supply

14 IN/OUT MP7 Multi-Purpose – GPIO or Serial output port data 1

15 IN/OUT MP6 Multi-Purpose – GPIO, Serial output port data 0, or TDM data output

16 IN/OUT MP10 Multi-Purpose – GPIO or Serial output port LRCLK

17 OUT VDRIVE Drive for external PNP Transistor for 1.8 V regulator

18 IOVDD Input and Output Pin Supply

19 IN/OUT MP11 Multi-Purpose – GPIO or Serial output port BCLK

20 IN ADDR1/CDATA/WB_TRIG I2C Address 1 / SPI Data Input / Self-boot Write-back trigger

21 IN/OUT CLATCH / WP SPI Latch / Self-boot EEPROM write protect

22 IN/OUT SDA/COUT I2C Data / SPI Data Out

23 IN/OUT SCL/CCLK I2C Clock / SPI Clock

24 DVDD 1.8 V Digital Supply

25 DGND Digital Ground

O

M

M

D

T

L

I

F

G

I

R

T

_

B

W

/

A

T

A

D

C

/

1

R

D

D

A

D

_

_

N

L

L

M

G

L

L

C

A

P

P

36

AVDD

35

PLL_LF

34

PVDD

33

PGND

32

MCLKI

31

OSCO

30

RSVD

29

MP2

28

MP3

27

MP8

26

MP9

25

DGND

T

K

P

D

L

U

D

W

C

/

V

O

C

H

D

C

/

/

C

L

A

T

C

D

A

S

S

L

C

Rev. PrC | Page 10 of 37

Preliminary Technical Data ADAU1702

26 IN/OUT MP9 Multi-Purpose – GPIO or Aux ADC input 0

27 IN/OUT MP8 Multi-Purpose – GPIO or Aux ADC input 3

28 IN/OUT MP3 Multi-Purpose – GPIO or Aux ADC input 2

29 IN/OUT MP2 Multi-Purpose – GPIO or Aux ADC input 1

30 RSVD Reserved, tie to ground

31 OUT OSCO Oscillator Output

32 IN MCLKI Master Clock or Crystal Input

33 PGND PLL Ground

34 PVDD 3.3 V PLL Power

35 PLL_LF PLL Loop Filter connection

36 AVDD 3.3 V Analog Supply

37 AGND Analog Ground

38 IN PLL_MODE0 PLL Mode select 0

39 IN PLL_MODE1 PLL Mode select 1

40 CM Common Mode Decoupling Capacitor

41 FILTD Decoupling Capacitor

42 AGND Analog Ground

43 OUT VOUT3 Channel 3 DAC output

44 OUT VOUT2 Channel 2 DAC output

45 OUT VOUT1 Channel 1 DAC output

46 OUT VOUT0 Channel 0 DAC output

47 FILTA Decoupling capacitor

48 AVDD 3.3 V Analog Supply

Rev. PrC1 | Page 1 of 37

ADAU1702 Preliminary Technical Data

PIN FUNCTIONS

Table 11 shows the ADAU1702’s pin numbers, names, and

functions. Input pins have a logic threshold compatible with

TTL input levels and may be used in systems with 3.3 V logic.

ADC0

ADC1

Stereo ADC inputs.

IDAC

Bias current pin for ADC. A resistor with the same value as

those on the ADC0 & ADC1 should be connected between this

pin and ground.

FILTA

ADC decoupling pin. A 10 μF capacitor should be placed

between this pin and ground.

VOUT0

VOUT1

VOUT2

VOUT3

Four-channel DAC outputs

CM

Reference. A 47 μF capacitor should be placed between this pin

and ground to reduce crosstalk.

FILTD

DAC decoupling pin. A 10 μF capacitor should be placed

between this pin and ground.

PLL_MODE0

PLL_MODE1

PLL_MODE2

PLL Mode Control Pins. The functionality of these pins is

described in the Setting Master Clock/PLL Mode section.

MCLKI

Master clock or crystal oscillator input.

OSCO

Crystal oscillator output.

PLL_LF

PLL loop filter connection.

SCL

2

I

C Clock. This pin is always an input when in I2C control

mode. In self-boot mode this pin will be an output (I

2

C

master). The line connected to this pin should have a 2 kΩ

pull-up resistor on it.

SDA

2

C Serial Data. The data line is bidirectional. The line

I

connected to this pin should have a 2 kΩ pull-up resistor on it.

CDATA

Serial Data Input for the SPI Control Port.

COUT

Serial Data Output for the SPI Port. This is used for reading

back registers and memory locations. It is three-stated when an

SPI read is not active.

CCLK

SPI Bit Clock. This clock may either run continuously or be

gated off in between SPI transactions.

CLATCH

SPI Latch Signal. This must go low at the beginning of an SPI

transaction and high at the end of a transaction. Each SPI

transaction may take a different number of CCLKs to complete,

depending on the address and read/write bit that are sent at the

beginning of the SPI transaction.

ADDR0

ADDR1

Address Select. These pins select the address for the

ADAU1702’s communication with the control port. This allows

two ADAU1702s to be used on the same control port.

WP

EEPROM write protect.

WB_TRIG

EEPROM Writeback trigger.

RESETB

Active-Low Reset Signal. After RESETB goes high, the

ADAU1702 goes through an initialization sequence where the

program and parameter RAMs are initialized with the contents

of the on-board boot ROMs. All registers are set to 0, and the

data RAMs are also set to 0. The initialization is complete after

xxxx internal MCLK cycles (referenced to the rising edge of

RESETB), which corresponds to xxxx external MCLK cycles if

the part is in 256 × f

mode. New values should not be written

S

to the control port until the initialization is complete.

SELFBOOT

Selfboot or external program load select.

MP0

MP1

MP2

MP3

MP4

MP5

MP6

MP7

MP8

MP9

MP10

MP11

Multi-purpose input/output pins. These pins can be configured

as serial data inputs/outputs, auxiliary ADC inputs, or general

purpose switch and button inputs/outputs.

Rev. PrC | Page 12 of 37

Loading...

Loading...