Analog Devices AD9821 Datasheet

Complete 12-Bit 40 MSPS

Imaging Signal Processor

AD9821

FEATURES

Differential Sensor Input with 1 V p-p Input Range

0 dB to 36 dB 10-Bit Variable Gain Amplifier (VGA)

Low Noise Optical Black Clamp Circuit

Analog Preblanking Function

12-Bit 40 MSPS A/D Converter (ADC)

3-Wire Serial Digital Interface

3 V Single-Supply Operation

Low Power: 150 mW @ 3 V Supply

48-Lead LQFP Package

APPLICATIONS

Digital Still Cameras Using CMOS Imagers

Industrial/Scientific Imaging

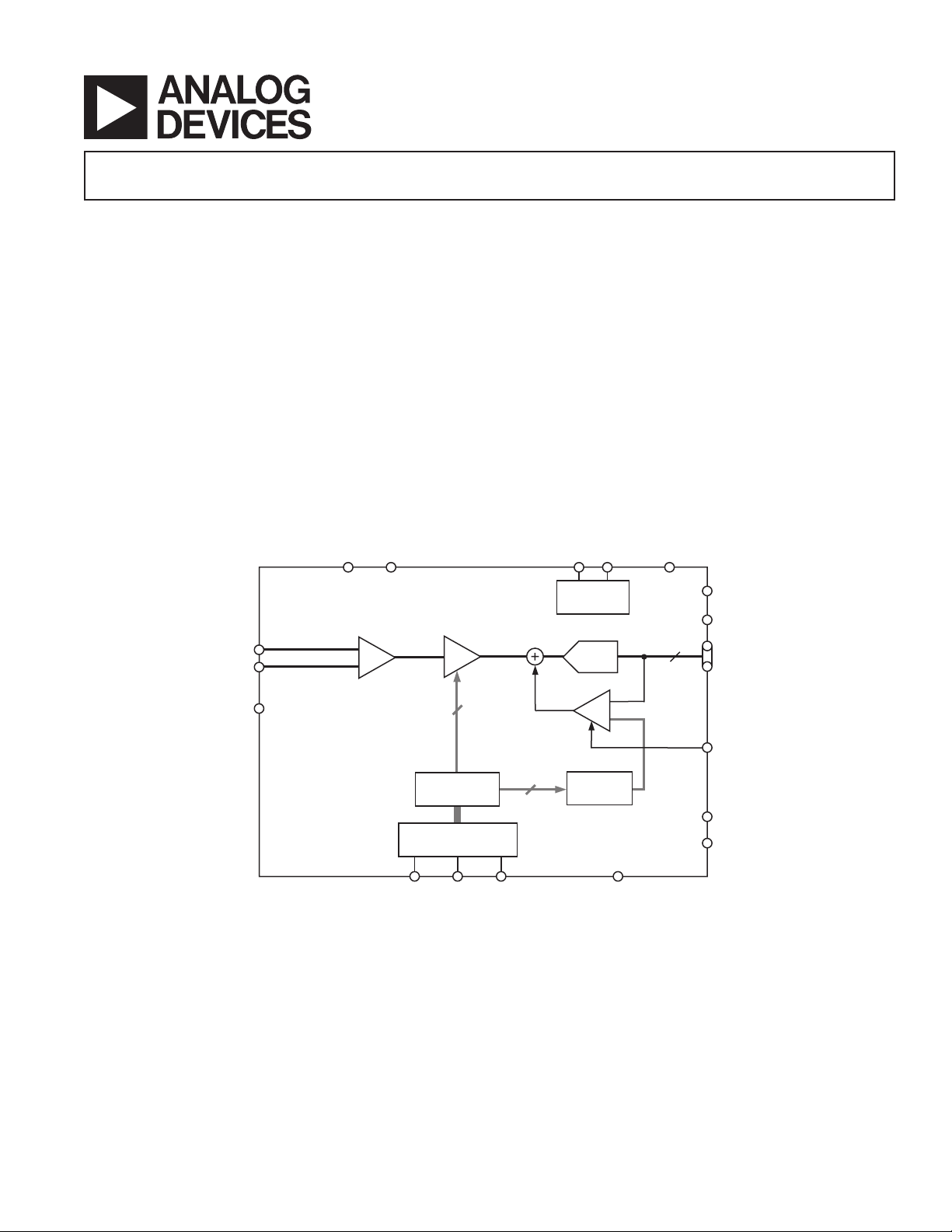

FUNCTIONAL BLOCK DIAGRAM

AV DD

AVSS

AD9821

0dB ~ 36dB

VIN+

VIN–

+

SHA

–

VGA

GENERAL DESCRIPTION

The AD9821 is a complete analog signal processor for imaging

applications that do not require Correlated Double Sampling

(CDS). It features a 40 MHz single-channel architecture designed

to sample and condition the outputs of CMOS imagers and CCD

arrays already containing on-chip CDS. The AD9821’s signal

chain consists of a differential input sample-and-hold amplifier

(SHA), digitally controlled variable gain amplifier (VGA), black

level clamp, and a 12-bit ADC.

The internal registers are programmed through a 3-wire serial

digital interface. Programmable features include gain adjustment, black level adjustment, and power-down modes.

The AD9821 operates from a single 3 V power supply, typically

dissipates 150 mW, and is packaged in a 48-lead LQFP.

PBLKVRT VRB

BAND GAP

REFERENCE

12-BIT

ADC

DRVDD

DRVSS

12

DOUT

BYP1

SL

10

INTERNAL

REGISTERS

DIGITAL

INTERFACE

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

CLP

CLPOB

8

BLK CLAMP

LEVEL

DVD D

DVSS

SDATASCK

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

DATACLK

AD9821–SPECIFICATIONS

to T

GENERAL SPECIFICATIONS

(T

MIN

, AVDD = DVDD = 3.0 V, f

MAX

Parameter Min Typ Max Unit

TEMPERATURE RANGE

Operating –20 +85 °C

Storage –65 +150 °C

POWER SUPPLY VOLTAGE

Analog, Digital, Digital Driver 2.7 3.6 V

POWER CONSUMPTION

Normal Operation (Specified under Each Mode of Operation)

Power-Down Modes

Standby 5 mW

Total Power-Down 1 mW

MAXIMUM CLOCK RATE 40 MHz

A/D CONVERTER

Resolution 12 Bits

Differential Nonlinearity (DNL) ± 0.5 LSB

No Missing Codes 12 Bits Guaranteed

Full-Scale Input Voltage 2.0 V

Data Output Coding Straight Binary

VOLTAGE REFERENCE

Reference Top Voltage (VRT) 2.0 V

Reference Bottom Voltage (VRB) 1.0 V

Specifications subject to change without notice.

= 40 MHz, unless otherwise noted.)

DATACLK

DIGITAL SPECIFICATIONS

(DRVDD = 2.7 V, CL = 20 pF, unless otherwise noted.)

Parameter Symbol Min Typ Max Unit

LOGIC INPUTS

High Level Input Voltage V

Low Level Input Voltage V

High Level Input Current I

Low Level Input Current I

Input Capacitance C

IH

IL

IH

IL

IN

2.1 V

0.6 V

10 µA

10 µA

10 pF

LOGIC OUTPUTS

High Level Output Voltage, IOH = 2 mA V

Low Level Output Voltage, IOL = 2 mA V

Specifications subject to change without notice.

OH

OL

2.2 V

0.5 V

REV. 0–2–

AD9821

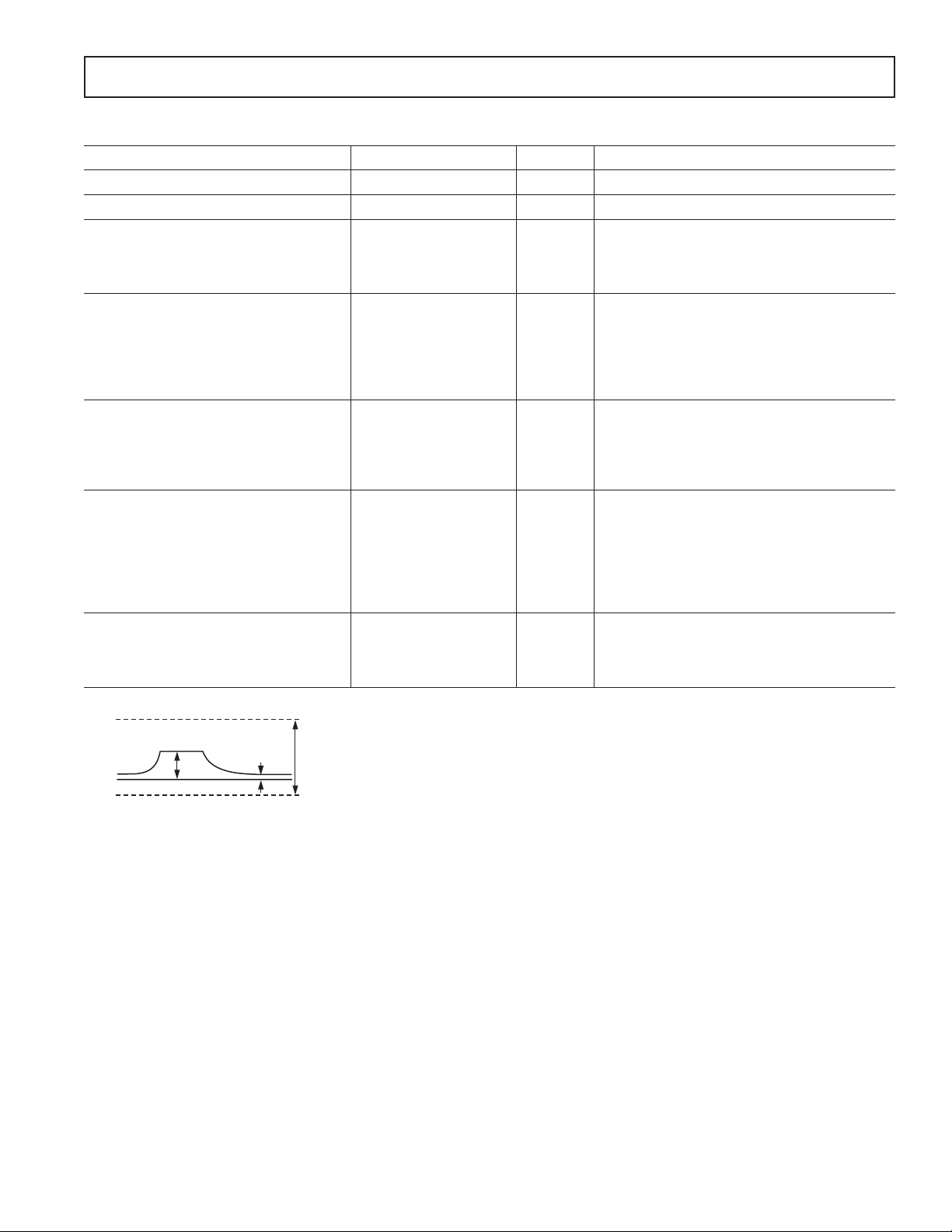

IMAGER-MODE SPECIFICATIONS

(T

to T

MIN

, AVDD = DVDD = 3.0 V, f

MAX

= 40 MHz, unless otherwise noted.)

DATACLK

Parameter Min Typ Max Unit Notes

P

OWER CONSUMPTION 150 mW See TPC 1 for Power vs. Sample Rate

MAXIMUM CLOCK RATE 40 MHz

ANALOG INPUTS (VIN+, VIN–)

Input Common-Mode Range* 0 1.8 V Linear operating range for VIN+, VIN–

Max Input Amplitude* 1.0 V p-p Defined as VIN+ minus VIN–

Max Optical Black Pixel Amplitude* ± 30 mV For stable Clamp at max VGA gain

VARIABLE GAIN AMPLIFIER (VGA)

Gain Control Resolution 1024 Steps

Gain Monotonicity Guaranteed

Gain Range See Figure 11 for VGA Gain Curve

Min Gain (VGA Gain Code 00) 0 dB

Max Gain (VGA Gain Code 1023) 36 dB

BLACK LEVEL CLAMP

Clamp Level Resolution 256 Steps

Clamp Level Measured at ADC Output

Min Clamp Level 0 LSB

Max Clamp Level 255 LSB

SYSTEM PERFORMANCE Specifications Include Entire Signal Chain

Gain Accuracy

Min Gain –1 0 +1 dB

Max Gain 34.5 35.5 36.5 dB

Peak Nonlinearity, 500 mV Input 0.3 % 12 dB Gain Applied

Total Output Noise 0.5 LSB rms AC Grounded Input, 6 dB Gain Applied

Power Supply Rejection (PSR) 40 dB Measured with Step Change on Supply

POWER-UP RECOVERY TIME Normal Clock Signals Applied

Reference Standby Mode 1 ms

Total Power-Down Mode 3 ms

Power-Off Condition 10 ms

*Input Signal Characteristics defined as follows:

+1.8V

VIN+

VIN–

GND

Specifications subject to change without notice.

1V p-p MAX

INPUT SIGNAL RANGE

ⴞ30mV MAX

OB PIXEL

INPUT

CM RANGE

REV. 0

–3–

AD9821

TIMING SPECIFICATIONS

(CL = 20 pF, f

= 40 MHz, Imager-Mode Timing in Figures 5 and 6, Serial Timing in Figures 7–9)

SAMP

Parameter Symbol Min Typ Max Unit

SAMPLE CLOCKS

DATACLK Clock Period t

DATACLK Hi/Low Pulsewidth t

CLPOB Pulsewidth* t

Internal Clock Delay t

CONV

ADC

COB

ID

25 25 ns

11 12.5 ns

220 Pixels

3.0 ns

DATA OUTPUTS

Output Delay t

Output Hold Time t

OD

H

7.0 7.6 ns

13 16 ns

Pipeline Delay 9 Cycles

SERIAL INTERFACE

Maximum SCK Frequency f

SL to SCK Setup Time t

SCK to SL Hold Time t

SDATA Valid to SCK Rising Edge Setup t

SCK Falling Edge to SDATA Valid Hold t

SCK Falling Edge to SDATA Valid Read t

*Minimum CLPOB pulsewidth is for functional operation only. Wider typical pulses are recommended to achieve low noise clamp performance.

Specifications subject to change without notice.

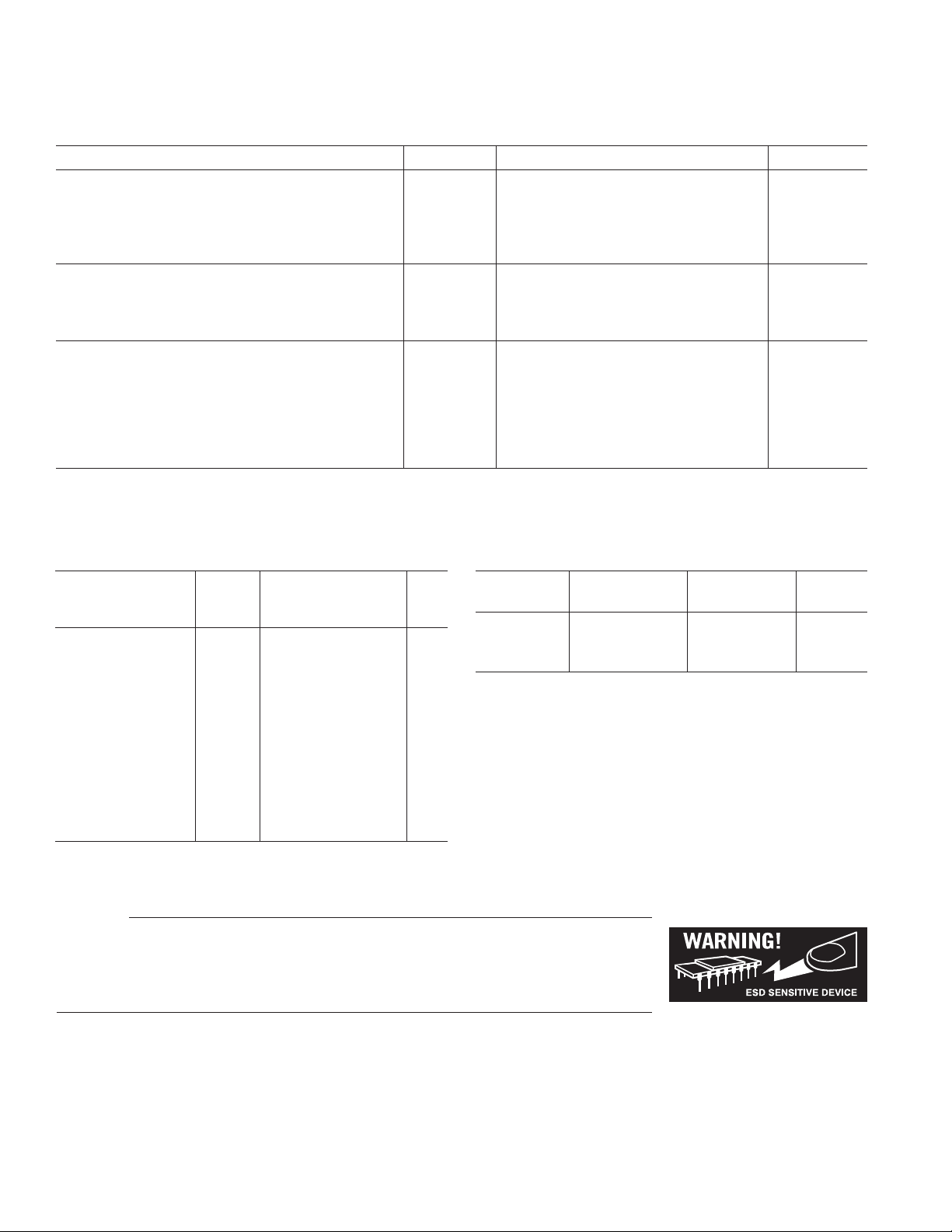

ABSOLUTE MAXIMUM RATINGS

With

Respect

Parameter To Min Max Unit

SCLK

LS

LH

DS

DH

DV

AVDD1, AVDD2 AVSS –0.3 +3.9 V

DVDD1, DVDD2 DVSS –0.3 +3.9 V

10 MHz

10 ns

10 ns

10 ns

10 ns

10 ns

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD9821KST –20°C to +85°CThin Plastic ST-48

Quad Flatpack

(LQFP)

DRVDD DRVSS –0.3 +3.9 V

Digital Outputs DRVSS –0.3 DRVDD + 0.3 V

DATACLK DVSS –0.3 DVDD + 0.3 V

CLPOB, PBLK DVSS –0.3 DVDD + 0.3 V

SCK, SL, SDATA DVSS –0.3 DVDD + 0.3 V

VRT, VRB AVSS –0.3 AVDD + 0.3 V

THERMAL CHARACTERISTICS

Thermal Resistance

48-Lead LQFP Package

= 56°C/W

θ

JA

BYP1, VIN AVSS –0.3 AVDD + 0.3 V

Junction Temperature 150 °C

Lead Temperature 300 °C

(10 sec)

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD9821 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

REV. 0–4–

AD9821

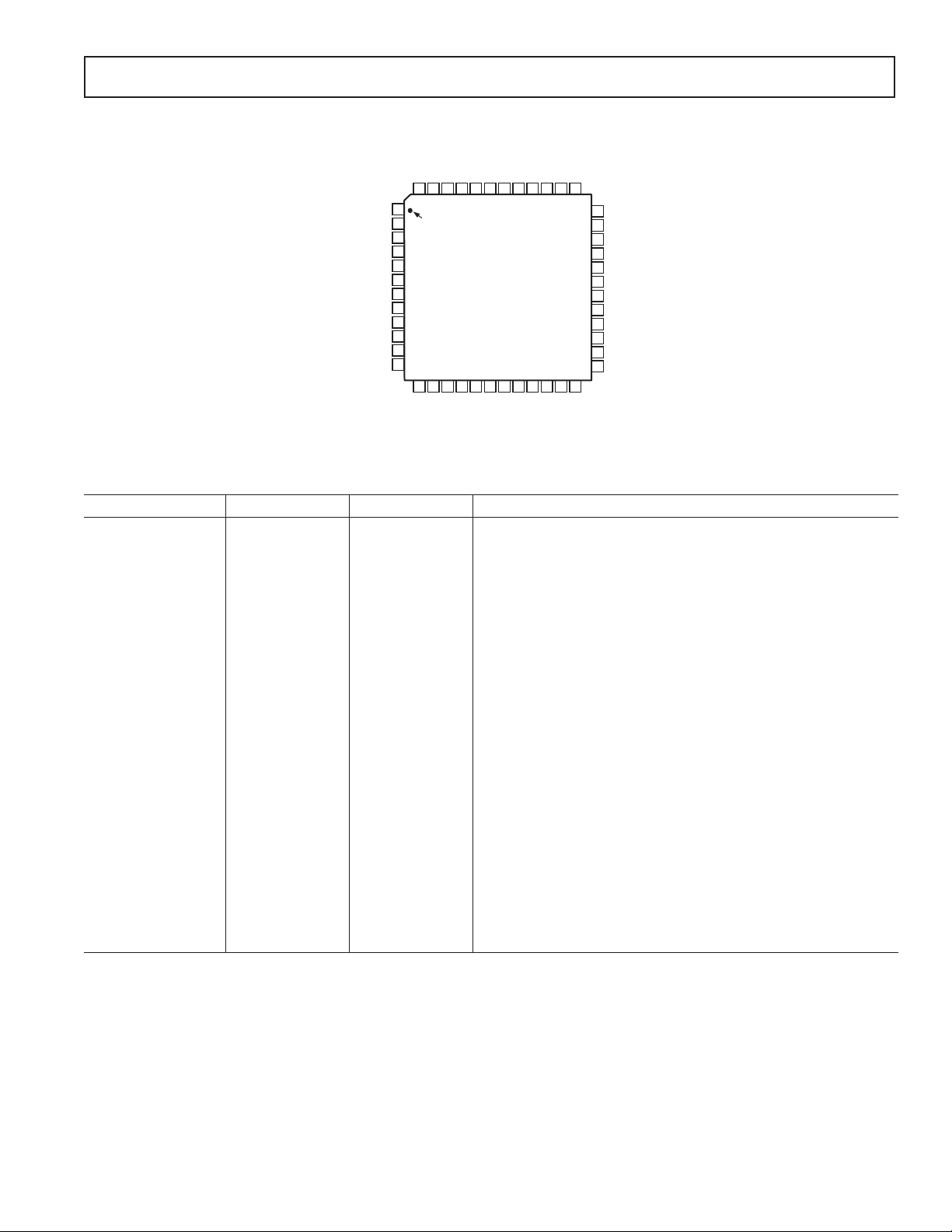

PIN CONFIGURATION

NCNCSCK

(LSB) D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

(MSB) D11

NC = NO CONNECT

48 47 46 4 5 44 39 38 3743 4 2 41 40

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

PIN 1

IDENTIFIER

DVSS

DRVSS

DRVDD

SDATASLSTBYNCDVSS

AD9821

TOP VIEW

(Not to Scale)

DVDD1

DATACLK

PIN FUNCTION DESCRIPTIONS

Pin Number Mnemonic Type Description

1–12 D0–D11 DO Digital Data Outputs

13 DRVDD P Digital Output Driver Supply

14 DRVSS P Digital Output Driver Ground

15, 41 DVSS P Digital Ground

16 DATACLK DI Digital Data Output Latch Clock

17 DVDD1 P Digital Supply

18, 24, 37, 42, 47, 48 NC NC Internally Not Connected. May be Tied High or Low.

19 PBLK DI Preblanking Clock Input

20 CLPOB DI Black Level Clamp Clock Input

21–23 TEST DI Test Use Only. Tie to VDD or VSS.

25, 26, 35 AVSS P Analog Ground

27 AVDD1 P Analog Supply

28, 29 TEST AO Test Use Only. Tie to VDD or VSS.

30 VIN+ AI Positive Analog Input for Imager Signal

31 VIN– AI Negative Analog Input for Imager Signal

32 BYP1 AO Internal Bias Level Decoupling

33 AVDD2 P Analog Supply

34, 36 TEST AI Test Use Only. Tie to VDD or VSS.

38 VRT AO ADC Top Reference Voltage Decoupling

39 VRB AO ADC Bottom Reference Voltage Decoupling

40 DVDD2 P Digital Supply

43 STBY DI Standby Mode, Active High. Same as Total Power-Down Mode.

44 SL DI Serial Digital Interface Load Pulse

45 SDATA DI Serial Digital Interface Data

46 SCK DI Serial Digital Interface Clock

TYPE: AI = Analog Input, AO = Analog Output, DI = Digital Input, DO = Digital Output, P = Power.

NC

PBLK

DVDD2

TEST

CLPOB

VRB

TEST

VRT

TEST

NC

NC

36

35

34

33

32

31

30

29

28

27

26

25

TEST

AVSS

TEST

AVDD2

BYP1

VIN–

VIN+

TEST

TEST

AVDD1

AVSS

AVSS

REV. 0

–5–

Loading...

Loading...