CCD Signal Processor

a

FEATURES

3-Wire Serial I/F for Digital Control

18 MHz Correlated Double Sampler

Low Noise PGA with 0 dB–30 dB Range

Analog Pre-Blanking Function

AUX Input with Input Clamp and PGA

10-Bit 18 MSPS A/D Converter

Direct ADC Input with Input Clamp

Internal Voltage Reference

Two Auxiliary 8-Bit DACs

+3 V Single Supply Operation

Low Power: 150 mW at 2.7 V Supply

48-Lead LQFP Package

PBLK PGACONT1-2 CLPOB

for Electronic Cameras

AD9803

PRODUCT DESCRIPTION

The AD9803 is a complete CCD and video signal processor

developed for electronic cameras. It is well suited for video

camera and still-camera applications.

The 18 MHz CCD signal processing chain consists of a CDS,

low noise PGA, and 10-bit ADC. Required clamping circuitry

and a voltage reference are also provided. The AUX input

features a wideband PGA and input clamp, and can be used to

sample analog video signals.

The AD9803 nominally operates from a single 3 V power supply, typically dissipating 170 mW. The AD9803 is packaged in a

space-saving 48-lead LQFP and is specified over an operating

temperature range of –20°C to +70°C.

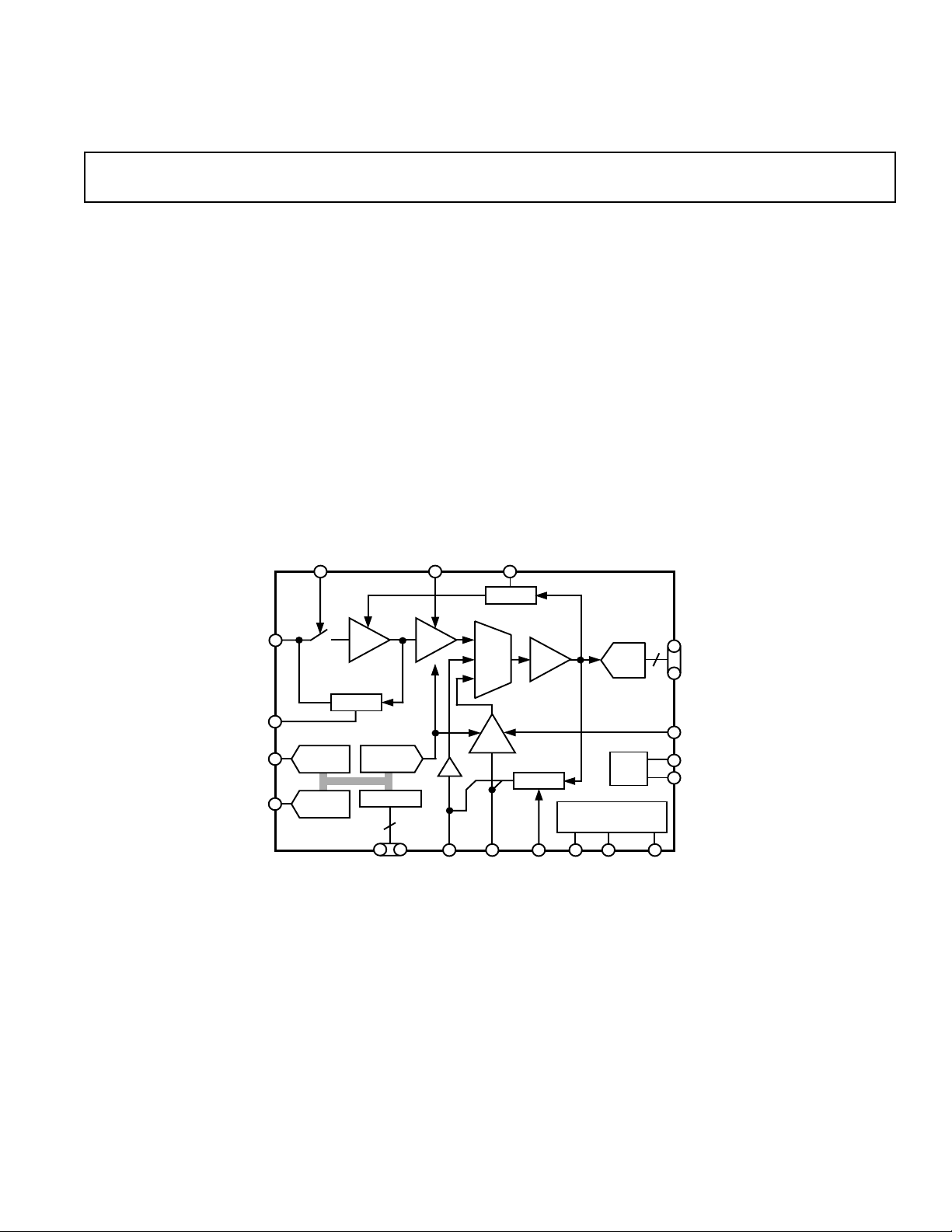

FUNCTIONAL BLOCK DIAGRAM

CCDIN

CLPDM

DAC1

DAC2

8-BIT

DAC

8-BIT

DAC

0–30dB

10-BIT

DAC

INTF

PGA

3

CDS

CLAMP

3-W INTF ADCIN AUXIN ACLP SHP SHD ADCCLK

CLAMP

MUX S/H

0–10dB

PGA

CLAMP

AD9803

TIMING

GENERATOR

ADC

REF

10

DOUT

AUXCONT

VRT

VRB

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

AD9803–SPECIFICATIONS

(T

to T

GENERAL SPECIFICATIONS

MIN

, ACVDD = ADVDD = DVDD = +2.8 V, f

MAX

Parameter Min Typ Max Units

TEMPERATURE RANGE

Operating –20 70 °C

Storage –65 150 °C

POWER SUPPLY VOLTAGE

(For Functional Operation)

Analog 2.7 3.0 3.6 V

Digital 2.7 3.0 3.6 V

Digital Driver 2.7 3.0 3.6 V

POWER CONSUMPTION

(Power-Down Modes Selected Through Serial I/F)

Normal Operation (D-Reg 00) (Specified Under Each Mode of Operation)

High Speed AUX-MODE (D-Reg 01) (Specified Under AUX-MODE)

Reference Standby (D-Reg 10 or STBY Pin Hi) 10 mW

Shutdown Mode (D-Reg 11) 10 mW

MAXIMUM CLOCK RATE (Specified Under Each Mode of Operation)

S/H AMPLIFIER

Gain 0dB

Clock Rate 27 MHz

A/D CONVERTER

Resolution 10 Bits

Differential Nonlinearity

0–255 Code ±0.5 ±0.8 LSBs

256–1023 Code ±0.5 ±1.0 LSBs

No Missing Codes GUARANTEED

Full-Scale Input Range 1.0 V p-p

Clock Rate 0.01 18 MHz

REFERENCE

Reference Top Voltage 1.75 V

Reference Bottom Voltage 1.25 V

Specifications subject to change without notice.

= 18 MHz unless otherwise noted)

ADCCLK

(T

to T

DIGITAL SPECIFICATIONS

MIN

, DRVDD = +2.7 V, CL = 20 pF unless otherwise noted)

MAX

Parameter Symbol Min Typ Max Units

LOGIC INPUTS

High Level Input Voltage V

Low Level Input Voltage V

High Level Input Current I

Low Level Input Current I

Input Capacitance C

IH

IL

IH

IL

IN

2.1 V

0.6 V

10 µA

10 µA

10 pF

LOGIC OUTPUTS

High Level Output Voltage V

Low Level Output Voltage V

High Level Output Current I

Low Level Output Current I

OH

OL

OH

OL

2.1 V

0.6 V

50 µA

50 µA

SERIAL INTERFACE TIMING (Figure 35)

Maximum SCLK Frequency 10 MHz

SDATA to SCLK Setup t

SCLK to SDATA Hold t

SLOAD to SCLK Setup t

SCLK to SLOAD Hold t

Specifications subject to change without notice.

DS

DH

LS

LH

–2–

10 ns

10 ns

10 ns

10 ns

REV. 0

AD9803

(T

to T

MIN

CCD-MODE SPECIFICATIONS

P

arameter Min Typ Max Units

noted)

, ACVDD = ADVDD = DVDD = +2.8 V, f

MAX

POWER CONSUMPTION

VDD = 2.7 150 mW

VDD = 2.8 170 mW

VDD = 3.0 185 mW

MAXIMUM CLOCK RATE 18 MHz

CDS

Gain 0dB

Allowable CCD Reset Transient

Max Input Range Before Saturation

1

1

1000 mV p-p

PGA

Max Input Range 1000 mV p-p

Max Output Range 1000 mV p-p

Digital Gain Control (See Figure 26)

Gain Control Resolution 10 (Fixed) Bits

Minimum Gain (Code 0) –3.5 –1.5 0 dB

Low Gain (Code 207) 0 4 8 dB

Medium Gain (Code 437) 15 dB

High Gain (Code 688) 22 26 30 dB

Max Gain (Code 1023) 32 dB

Analog Gain Control (See Figure 25)

PGACONT1 = 0.7 V, PGACONT2 = 1.5 V 4.5 dB

PGACONT1 = 1.8 V, PGACONT2 = 1.5 V 26 dB

BLACK-LEVEL CLAMP

Clamp Level (Selected by the Serial I/F)

CLP(0) (E-Reg 00) 34 LSB

CLP(1) (E-Reg 01) 50 LSB

CLP(2) (E-Reg 10) 66 LSB

CLP(3) (E-Reg 11) 18 LSB

Even-Odd Offset

2

SIGNAL-TO-NOISE RATIO3 (@ Minimum PGA Gain) 61 dB

TIMING SPECIFICATIONS

4

Pipeline Delay

Even-Odd Offset Correction Disabled 5 Cycles

Even-Odd Offset Correction Enabled 7 Cycles

Internal Clock Delay

Inhibited Clock Period (t

Output Delay (t

Output Hold Time (t

5

(tID)3ns

)15 ns

INHIBIT

) 20 ns

OD

)2 ns

HOLD

ADCCLK, SHP, SHD, Clock Period 47 55.6 ns

ADCCLK Hi-Level, Or Low Level 20 28 ns

SHP, SHD Minimum Pulsewidth

6

10 14 ns

SHP Rising Edge to SHD Rising Edge 20 28

NOTES

1

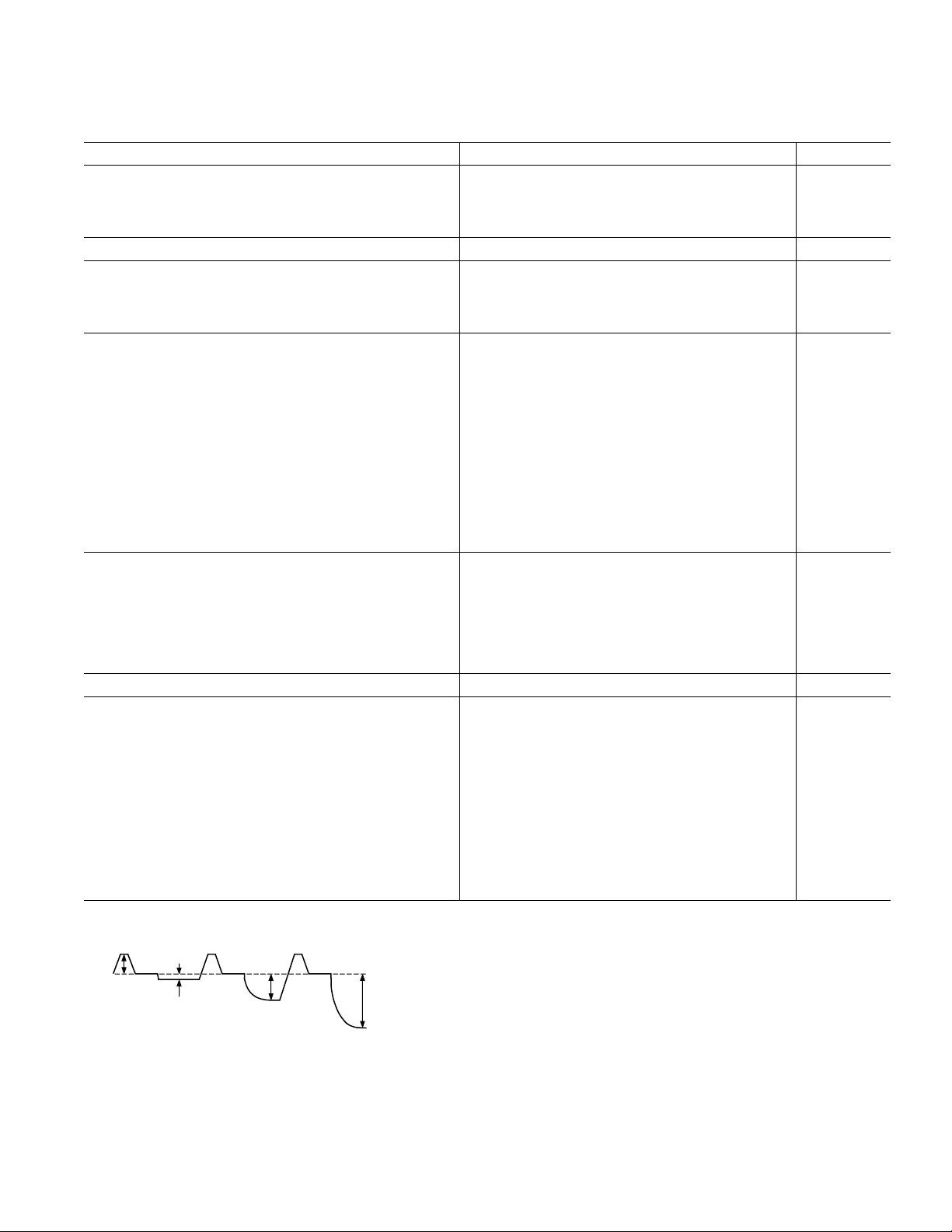

Input Signal Characteristics defined as shown:

= f

SHP

SHD

= f

= 18 MHz unless otherwise

ADCCLK

500 mV

±0.5 LSB

ns

500mV TYP

RESET TRANSIENT

2

Even-Odd Offset is described under the Theory of Operation section. The Even-Odd Offset is measured with the Even-Off Offset correction enabled.

3

SNR = 20 log

4

20 pF loading; timing shown in Figure 1.

5

Internal aperture delay for actual sampling edge.

6

Active Low Clock Pulse Mode (C-Reg 00).

Specifications subject to change without notice.

650mV MAX

OPTICAL BLACK PIXEL

(Full-Scale Voltage/RMS Output Noise).

10

1V MAX

INPUT SIGNAL

RANGE

2V MAX

INPUT SIGNAL

W/PBLK

ENABLED

–3–REV. 0

AD9803–SPECIFICATIONS

(T

to T

AUX-MODE SPECIFICATIONS

Parameter Min Typ Max Units

POWER CONSUMPTION

Normal (D-Reg 00) 80 mW

High Speed (D-Reg 01) 110 mW

MAXIMUM CLOCK RATE 18 MHz

PGA

Max Input Range 700 mV p-p

Max Output Range 1000 mV p-p

Digital Gain Control

Gain Control Resolution 8 (Fixed) Bits

Gain (Selected by the Serial I/F)

Gain(0) –3.5 dB

Gain(255) 10.5 dB

ACTIVE CLAMP (CLAMP ON)

Clamp Level (Selectable by the Serial I/F)

CLP(0) (E-Reg 00) 34 LSB

CLP(1) (E-Reg 01) 50 LSB

CLP(2) (E-Reg 10) 66 LSB

CLP(3) (E-Reg 11) 18 LSB

TIMING SPECIFICATIONS

Pipeline Delay 4 (Fixed) Cycles

Internal Clock Delay (t

Output Delay (tOD) 20 ns

Output Hold Time (t

NOTES

1

20 pF loading; timing shown in Figure 2.

Specifications subject to change without notice.

1

) 5ns

ID

)2 ns

HOLD

MIN

, ACVDD = ADVDD = DVDD = +2.8 V, f

MAX

= 18 MHz unless otherwise noted)

ADCCLK

(T

to T

ADC-MODE SPECIFICATIONS

Parameter Min Typ Max Units

POWER CONSUMPTION (Normal D-Reg 00) 65 mW

MAXIMUM CLOCK RATE 18 MHz

ACTIVE CLAMP (Same as AUX-MODE)

TIMING SPECIFICATIONS (Same as AUX-MODE)

Specifications subject to change without notice.

MIN

, ACVDD = ADVDD = DVDD = +2.8 V, f

MAX

= 18 MHz unless otherwise noted)

ADCCLK

DAC SPECIFICATIONS (DAC1 and DAC2)

Parameter Min Typ Max Units

RESOLUTION 8 (Fixed) Bits

MIN OUTPUT 0.1 V

MAX OUTPUT VDD – 0.1 V

MAX CURRENT LOAD 1 mA

MAX CAPACITIVE LOAD 500 pF

Specifications subject to change without notice.

–4–

REV. 0

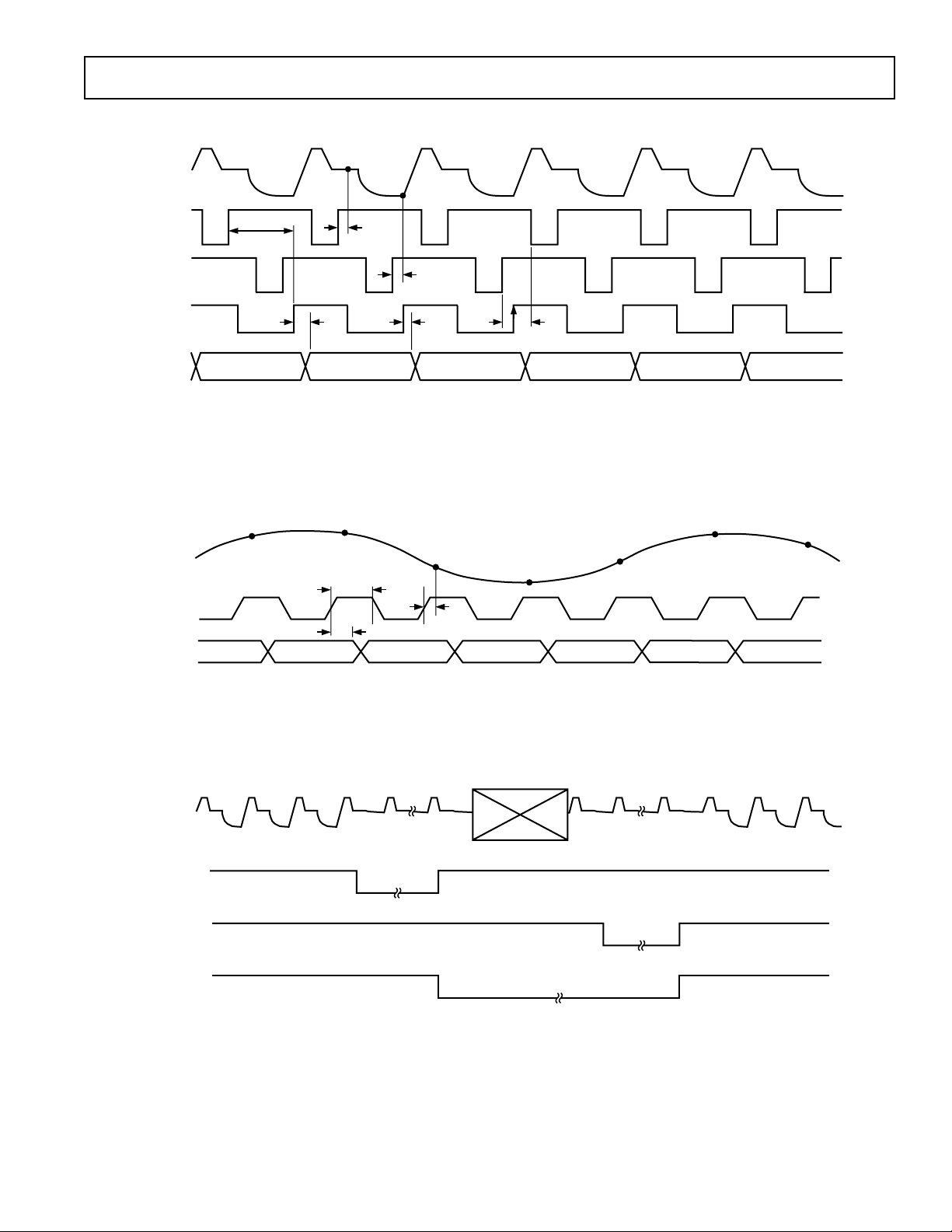

TIMING SPECIFICATIONS

AD9803

CCD

SHP

SHD

ADCCLK

D0–D9

VIDEO

INPUT

ADCCLK

D0–D9

N N+1 N+2 N+3 N+4

t

t

INHIBIT

t

OD

N–8 N–7 N–6 N–5 N–4 N–3

NOTES:

1. SHP AND SHD SHOULD BE OPTIMALLY ALIGNED WITH THE CCD SIGNAL. SAMPLES ARE TAKEN AT THE

2. ADCCLK RISING EDGE MUST OCCUR AT LEAST 15ns AFTER THE RISING EDGE OF SHP (

3. RECOMMENDED PLACEMENT FOR ADCCLK RISING EDGE IS BETWEEN THE RISING EDGE OF SHD AND FALLING EDGE OF SHP.

4. OUTPUT LATENCY (7 CYCLES) SHOWN WITH EVEN-ODD OFFSET CORRECTION ENABLED.

5. ACTIVE LOW CLOCK PULSE MODE IS SHOWN.

ID

t

ID

t

OLD

H

ADCCLK RISING EDGE PLACEMENT

RISING

t

INHIBIT

).

EDGES.

Figure 1. CCD-MODE Timing

N

t

N+1

t

OD

HOLD

N–4 N–3 N–2

N+2

t

ID

N+4

N+3

N–1 N

N+5

CCD

SIGNAL

CLPOB

CLPDM

PBLK

NOTE:

EXAMPLE OF OUTPUT DATA LATCHED BY ADCCLK RISING EDGE.

Figure 2. AUX-MODE and ADC-MODE Timing

EFFECTIVE

PIXELS

NOTES:

1. CLPOB PULSEWIDTH SHOULD BE A MINIMUM OF 10 OB PIXELS WIDE, 20 OB PIXELS ARE RECOMMENDED.

2. CLPDM PULSEWIDTH SHOULD BE AT LEAST 1 ms WIDE.

3. PBLK IS NOT REQUIRED, BUT RECOMMENDED IF THE CCD SIGNAL AMPLITUDE EXCEEDS 1V p-p.

4. CLPDM OVERWRITES PBLK.

5. ACTIVE LOW CLAMP PULSE MODE IS SHOWN.

OPTICAL BLACK

BLANKING

INTERVAL

DUMMY BLACK

Figure 3. CCD-MODE Clamp Timing

EFFECTIVE

PIXELS

–5–REV. 0

AD9803

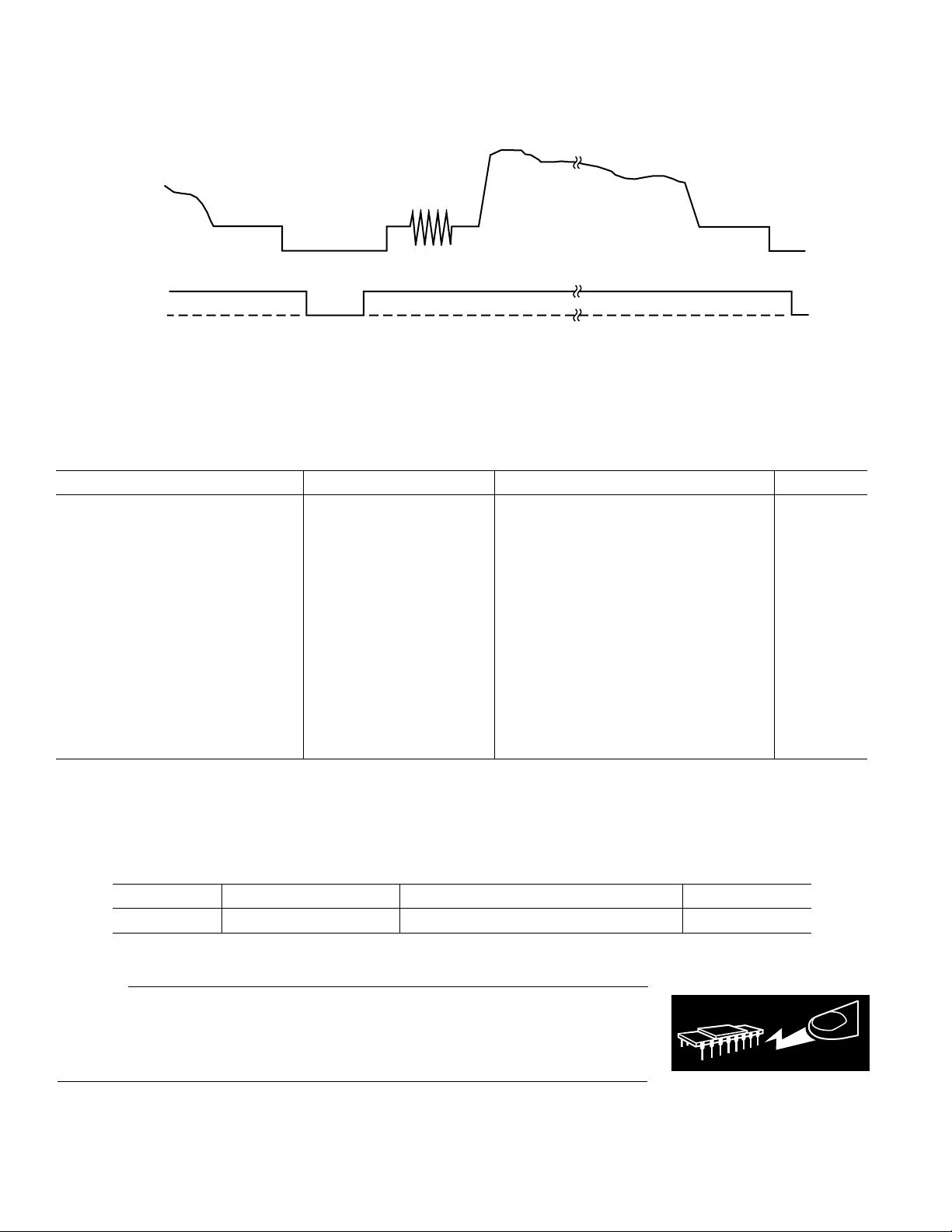

TIMING SPECIFICATIONS (CONTINUED)

VIDEO

SIGNAL

ACLP

H

SYNC

Figure 4. AUX-MODE Clamp Timing

MANUAL CLAMPING

AUTOMATIC CLAMPING

NOTE: ACLP can be used two different ways. To control the

exact time of the clamp, an active low pulse is used to specify

the clamp interval. Alternatively, ACLP may be tied to ground.

In this configuration, the clamp circuitry will sense the most

negative portion of the signal and use this level to set the clamp

voltage. For the video waveform in Figure 4, the SYNC level

will be clamped to the black level specified in the E-Register.

Active low clamp pulse mode is shown.

ABSOLUTE MAXIMUM RATINGS*

Parameter With Respect To Min Max Units

ADVDD ADVSS, SUBST –0.3 6.5 V

ACVDD ACVSS, SUBST –0.3 6.5 V

DVDD DVSS –0.3 6.5 V

DRVDD DRVSS –0.3 6.5 V

CLOCK INPUTS DVSS –0.3 DVDD + 0.3 V

PGACONT1, PGACONT2 SUBST –0.3 ACVDD + 0.3 V

PIN, DIN SUBST –0.3 ACVDD + 0.3 V

DOUT DRVSS –0.3 DRVDD + 0.3 V

VRT, VRB SUBST –0.3 ADVDD + 0.3 V

CCDBYP1, CCDBYP2 SUBST –0.3 ACVDD + 0.3 V

DAC1, DAC2 SUBST –0.3 ACVDD + 0.3 V

DRVSS, DVSS, ACVSS, ADVSS SUBST –0.3 +0.3 V

Junction Temperature +150 °C

Storage Temperature –65 +150 °C

Lead Temperature (10 sec) +300 °C

*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device

at these or other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods

may affect device reliability.

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD9803JST 0°C to +70°C 48-Lead Plastic Thin Quad Flatpack ST-48

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9803 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–6–

WARNING!

ESD SENSITIVE DEVICE

REV. 0

Loading...

Loading...