Dual 12-/14-/16-Bit,

1 GSPS, Digital-to-Analog Converters

FEATURES

Low power: 1.0 W @ 1 GSPS, 600 mW @ 500 MSPS,

full operating conditions

SFDR = 78 dBc to f

Single carrier WCDMA ACLR = 79 dBc @ 80 MHz IF

Analog output: adjustable 8.7 mA to 31.7 mA,

= 25 Ω to 50 Ω

R

L

Novel 2×, 4×, and 8× interpolator/coarse complex modulator

allows carrier placement anywhere in DAC bandwidth

Auxiliary DACs allow control of external VGA and offset control

Multiple chip synchronization interface

High performance, low noise PLL clock multiplier

Digital inverse sinc filter

100-lead, exposed paddle TQFP package

APPLICATIONS

Wireless infrastructure

WCDMA, CDMA2000, TD-SCDMA, WiMax, GSM

Digital high or low IF synthesis

Internal digital upconversion capability

Transmit diversity

Wideband communications: LMDS/MMDS, point-to-point

= 100 MHz

OUT

AD9776/AD9778/AD9779

GENERAL DESCRIPTION

The AD9776/AD9778/AD9779 are dual, 12-/14-/16-bit, high

dynamic range, digital-to-analog converters (DACs) that provide a sample rate of 1 GSPS, permitting multicarrier generation

up to the Nyquist frequency. They include features optimized

for direct conversion transmit applications, including complex

digital modulation, and gain and offset compensation. The DAC

outputs are optimized to interface seamlessly with analog quadrature modulators such as the AD8349. A serial peripheral interface

(SPI®) provides for programming/readback of many internal

parameters. Full-scale output current can be programmed over a

range of 10 mA to 30 mA. The devices are manufactured on an

advanced 0.18 m CMOS process and operate on 1.8 V and

3.3 V supplies for a total power consumption of 1.0 W. They are

enclosed in 100-lead TQFP packages.

PRODUCT HIGHLIGHTS

1. Ultralow noise and intermodulation distortion (IMD)

enable high quality synthesis of wideband signals from

baseband to high intermediate frequencies.

2. A proprietary DAC output switching technique enhances

dynamic performance.

3. The current outputs are easily configured for various

single-ended or differential circuit topologies.

4. CMOS data input interface with adjustable set up and hold.

5. Novel 2×, 4×, and 8× interpolator/coarse complex

modulator allows carrier placement anywhere in DAC

bandwidth.

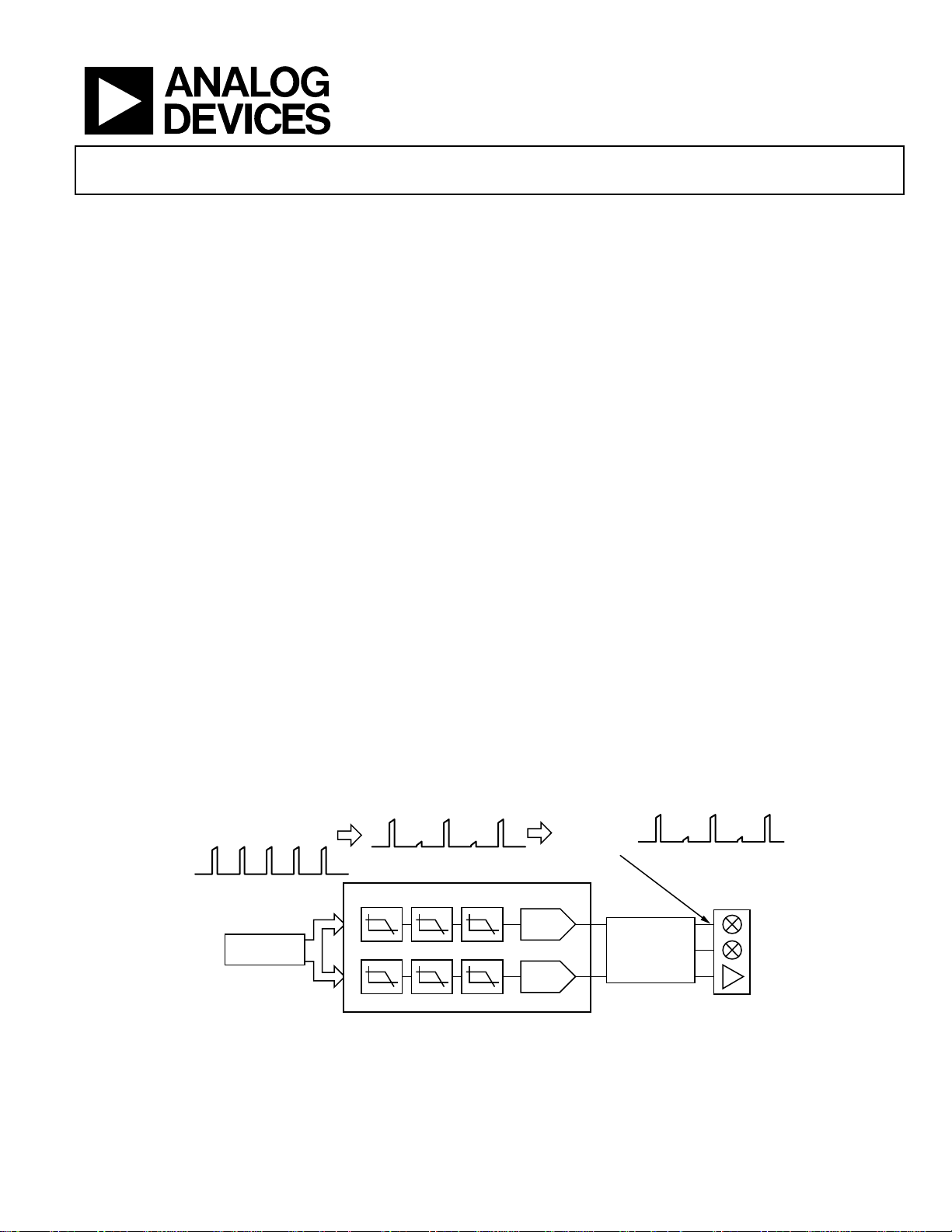

TYPICAL SIGNAL CHAIN

COMPLEX I AND Q

DC

DC

FPGA/ASIC/DSP

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

DIGITAL INTERPOLATION FILTERS

AD9779

QUADRATURE

MODULATOR/

MIXER/

AMPLIFIER

I DAC

POST DAC

ANALOG FILTER

Q DAC

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2005–2007 Analog Devices, Inc. All rights reserved.

LO

A

05361-114

AD9776/AD9778/AD9779

TABLE OF CONTENTS

Features .............................................................................................. 1

SPI Register Map ............................................................................ 27

Applications....................................................................................... 1

General Description......................................................................... 1

Product Highlights........................................................................... 1

Typical S i g nal C h a i n ......................................................................... 1

Revision History ............................................................................... 2

Functional Block Diagram .............................................................. 3

Specifications..................................................................................... 4

DC Specifications ......................................................................... 4

Digital Specifications ................................................................... 6

Digital Input Data Timing Specifications ................................. 7

AC Specifications.......................................................................... 7

Absolute Maximum Ratings............................................................ 8

Thermal Resistance ...................................................................... 8

ESD Caution.................................................................................. 8

Pin Configurations and Function Descriptions ........................... 9

Typical Performance Characteristics ........................................... 15

Te r mi n ol o g y .................................................................................... 24

Theory of Operation ...................................................................... 25

Serial Peripheral Interface......................................................... 25

Interpolation Filter Architecture .................................................. 31

Interpolation Filter Minimum and Maximum Bandwidth

Specifications .............................................................................. 35

Driving the REFCLK Input....................................................... 35

Internal PLL Clock Multiplier/Clock Distribution................ 36

Full-Scale Current Generation ................................................. 38

Power Dissipation....................................................................... 39

Power-Down and Sleep Modes................................................. 41

Interleaved Data Mode .............................................................. 41

Timing Information ................................................................... 41

Synchronization of Input Data to DATACLK

Output (Pin 37)........................................................................... 43

Synchronization of Input Data to the REFCLK Input (Pin 5

and Pin 6) with PLL Enabled or Disabled............................... 43

Evaluation Board Operation ......................................................... 46

Modifying the Evaluation Board to Use the AD8349 On-

Board Quadrature Modulator................................................... 48

Evaluation Board Schematics ................................................... 49

Outline Dimensions ....................................................................... 56

Ordering Guide .......................................................................... 56

MSB/LSB Transfers.....................................................................26

REVISION HISTORY

3/07—Rev. 0 to Rev. A

Changes to Features.......................................................................... 1

Changes to Applications .................................................................. 1

Changes to General Product Highlights........................................ 1

Added Figure 1, Renumbered Figures Sequentially..................... 1

Changes to Table 1............................................................................ 4

Changes to Table 2............................................................................ 5

Changes to Table 3............................................................................ 5

Changes to Figure 53 and Figure 54............................................. 26

Changes to Table 12........................................................................ 29

Changes to Power Dissipation Section ........................................39

Rev. A | Page 2 of 56

Added Table 19, Renumbered Tables Sequentially.................... 41

Changes to Figure 92 and Figure 93............................................. 42

Changes to Figure 94...................................................................... 42

Added New Figure 95, Renumbered Figures Sequentially ....... 42

Changes to Synchronization of Input Data to the REFCLK Input

(Pin 5 and Pin 6) with PLL Enabled or Disabled Section ......... 43

Added New Figure 96, Renumbered Figures Sequentially ....... 43

Changes to Figure 106 ................................................................... 51

7/05—Revision 0: Initial Version

AD9776/AD9778/AD9779

K

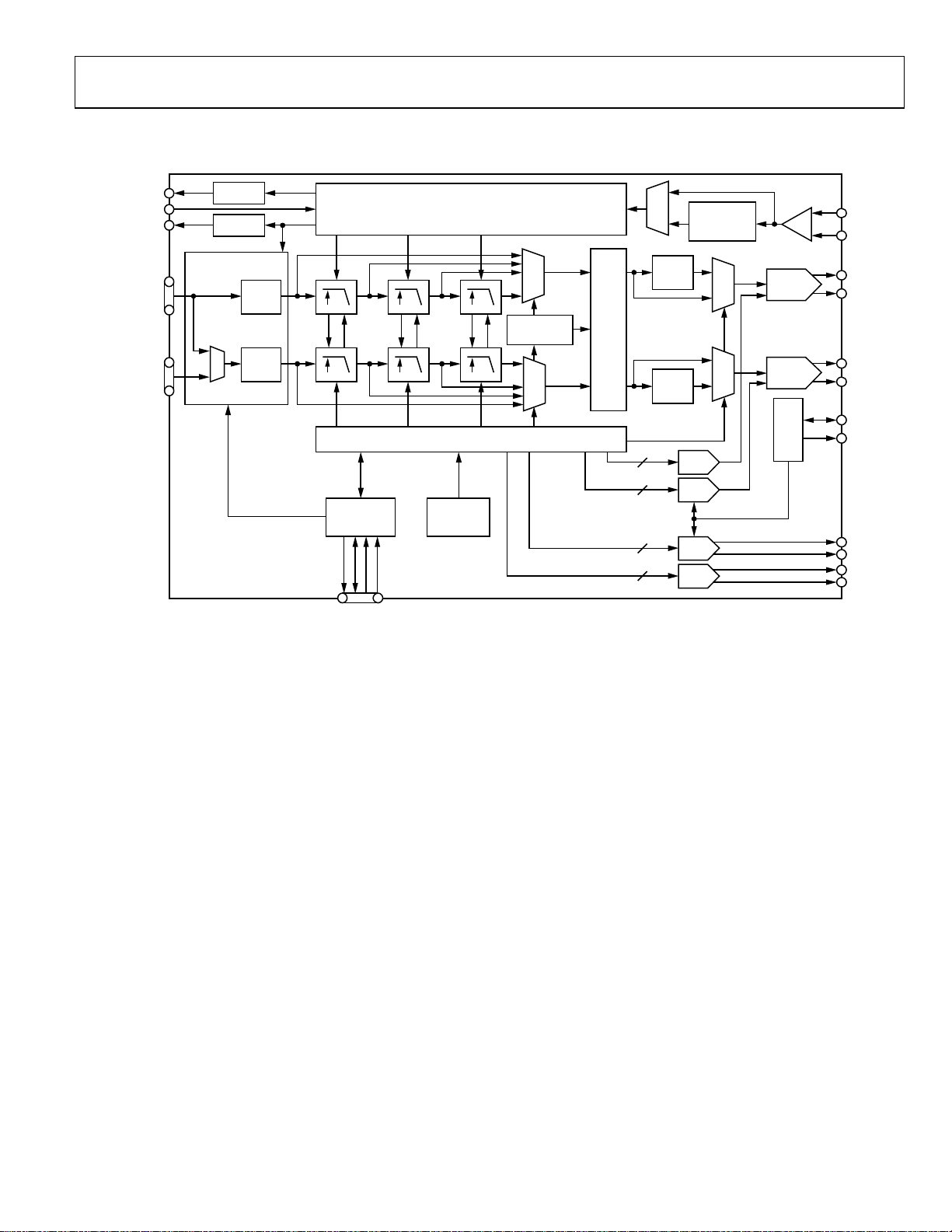

FUNCTIONAL BLOCK DIAGRAM

SYNC_O

SYNC_I

DATACLK_OUT

P1D(15:0)

P2D(15:0)

DELAY

LINE

DELAY

LINE

DATA

ASSEMBLER

LATCH

LATCH

CLOCK GENERAT ION/DISTRIBUTIO N

SYNC

I

Q

2× 2×

2× 2× 2×

DIGITAL CONTROLLER

SERIAL

PERIPHERAL

INTERFACE

SDO

SDIO

SCL

CSB

POWER-ON

RESET

2×

n ×

f

/8

DAC

n = 0, 1, 2 ... 7

COMPLEX

MODULATOR

SYNC

10

10

10

10

CLOCK

MULTIPLIER

2×/4×/8×

1

1

GAIN

GAIN

GAIN

GAIN

16-BIT

IDAC

16-BIT

QDAC

REFERENCE

AND BIAS

CLK+

CLK–

IOUT1_P

IOUT1_N

IOUT2_P

IOUT2_N

VREF

I120

AUX1_P

AUX1_N

AUX2_P

AUX2_N

5361-001

Figure 2. Functional Block Diagram

Rev. A | Page 3 of 56

AD9776/AD9778/AD9779

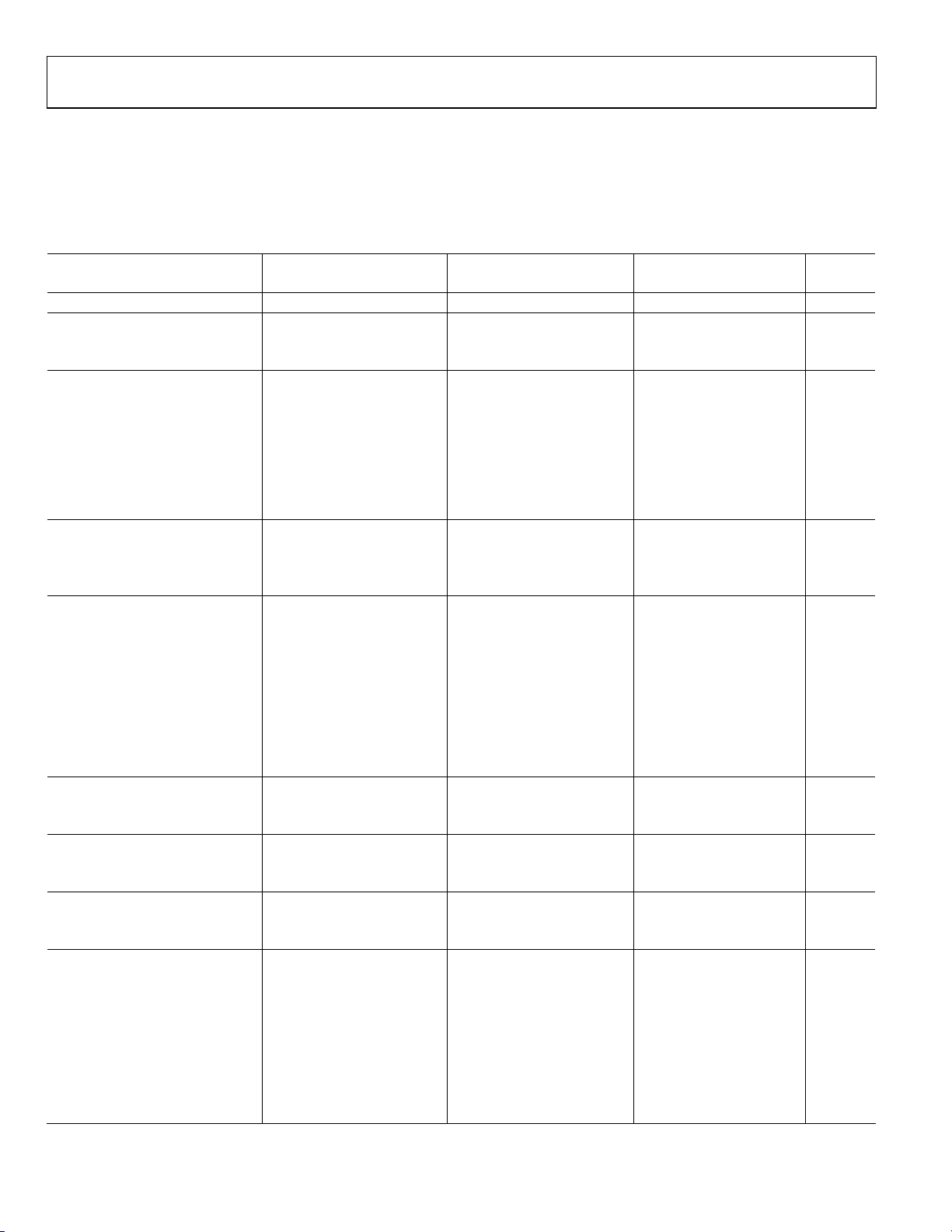

SPECIFICATIONS

DC SPECIFICATIONS

T

to T

MIN

otherwise noted.

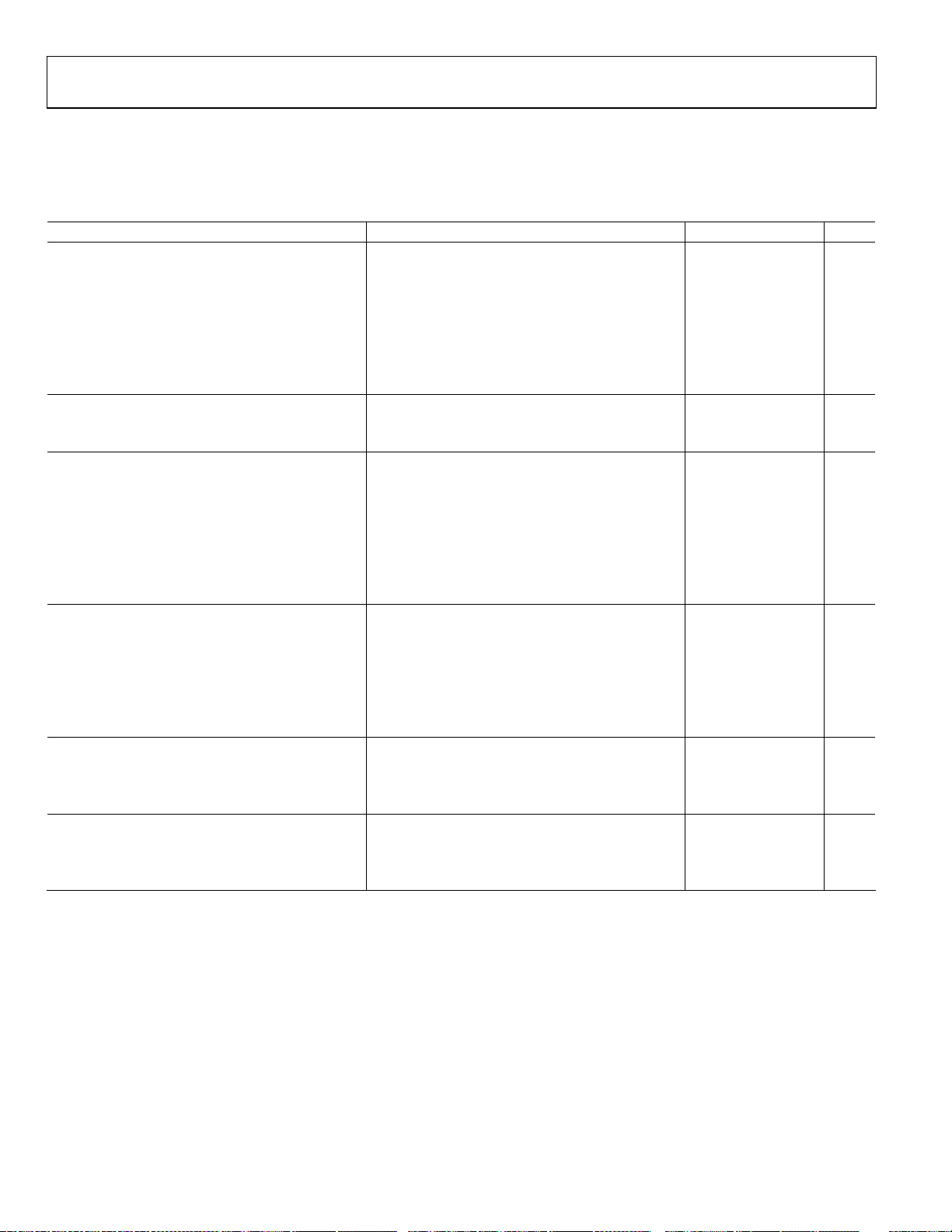

Table 1. AD9776, AD9778, and AD9779 DC Specifications

AD9776 AD9778 AD9779

Parameter Min Typ Max Min Typ Max Min Typ Max Unit

RESOLUTION 12 14 16 Bits

ACCURACY

Differential Nonlinearity (DNL) ±0.1 ±0.65 ±2.1 LSB

Integral Nonlinearity (INL) ±0.6 ±1 ±3.7 LSB

MAIN DAC OUTPUTS

Offset Error −0.001 0 +0.001 −0.001 0 +0.001 −0.001 0 +0.001 % FSR

Gain Error (with Internal

Reference)

Full-Scale Output Current

Output Compliance Range −1.0 +1.0 −1.0 +1.0 −1.0 +1.0 V

Output Resistance 10 10 10 MΩ

Gain DAC Monotonicity Guaranteed Guaranteed Guaranteed

MAIN DAC TEMPERATURE DRIFT

Offset 0.04 0.04 0.04 ppm/°C

Gain 100 100 100 ppm/°C

Reference Voltage 30 30 30 ppm/°C

AUX DAC OUTPUTS

Resolution 10 10 10 Bits

Full-Scale Output Current

Output Compliance Range

(Source)

Output Compliance Range

(Sink)

Output Resistance 1 1 1 MΩ

Aux DAC Monotonicity

Guaranteed

REFERENCE

Internal Reference Voltage 1.2 1.2 1.2 V

Output Resistance 5 5 5 kΩ

ANALOG SUPPLY VOLTAGES

AVDD33 3.13 3.3 3.47 3.13 3.3 3.47 3.13 3.3 3.47 V

CVDD18 1.70 1.8 1.90 1.70 1.8 1.90 1.70 1.8 1.90 V

DIGITAL SUPPLY VOLTAGES

DVDD33 3.13 3.3 3.47 3.13 3.3 3.47 3.13 3.3 3.47 V

DVDD18 1.70 1.8 1.90 1.70 1.8 1.90 1.70 1.8 1.90 V

POWER CONSUMPTION

1× Mode, f

IF = 1 MHz

2× Mode, f

IF = 16 MHz, PLL Off

2× Mode, f

IF = 16 MHz, PLL On

4× Mode, f

f

DAC

IF = 137.5 MHz, Q DAC Off

, AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 =1.8 V, = 20 mA, maximum sample rate, unless

MAX

I

OUTF

S

±2 ±2 ±2 % FSR

1

1

8.66 20.2 31.66 8.66 20.2 31.66 8.66 20.2 31.66 mA

−1.998 +1.998 −1.998 +1.998 −1.998 +1.998 mA

0 1.6 0 1.6 0 1.6 V

0.8 1.6 0.8 1.6 0.8 1.6 V

= 100 MSPS,

DAC

= 320 MSPS,

DAC

= 320 MSPS,

DAC

/4 Modulation,

DAC

250 300 250 300 250 300 mW

498 498 498 mW

588 588 588 mW

572 572 572 mW

= 500 MSPS,

Rev. A | Page 4 of 56

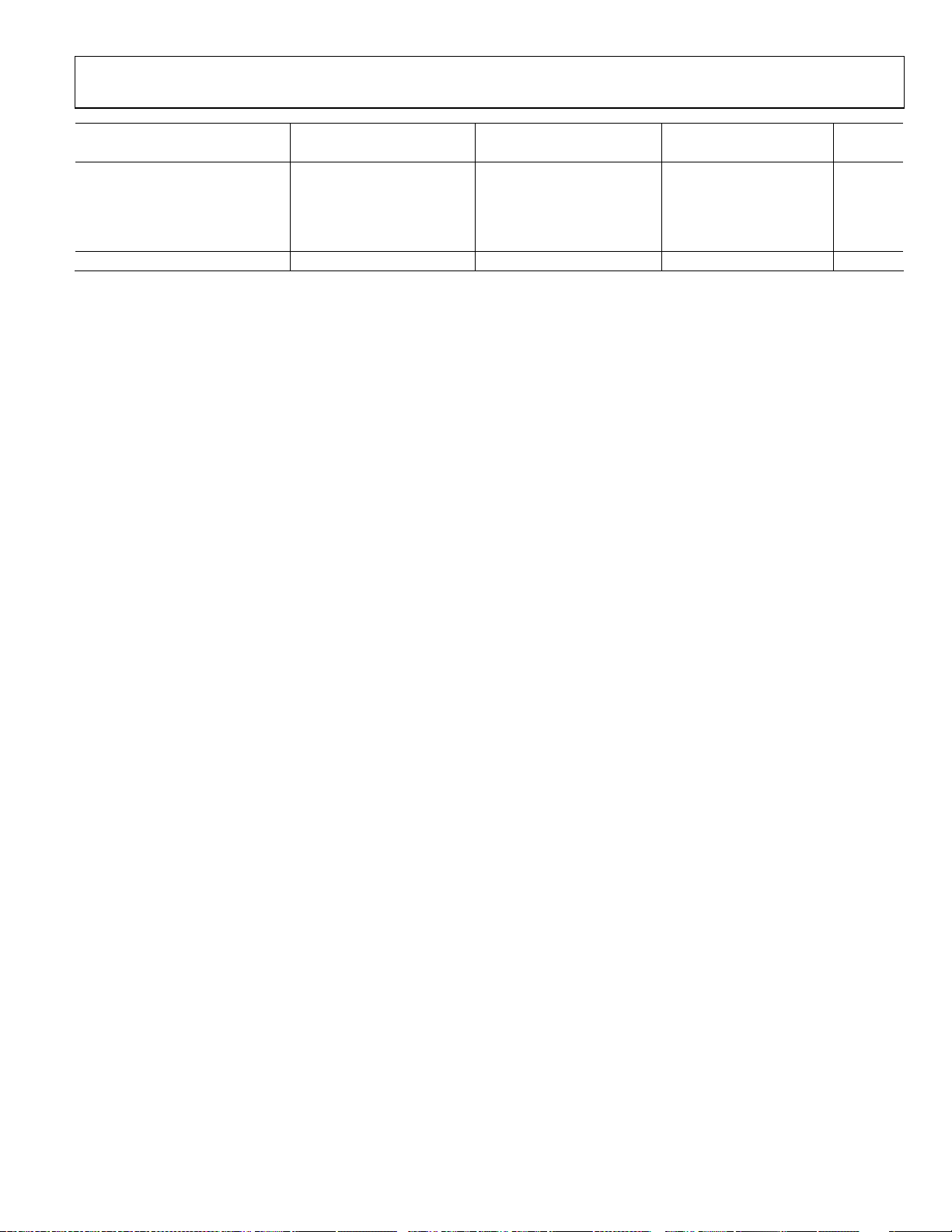

AD9776/AD9778/AD9779

AD9776 AD9778 AD9779

Parameter Min Typ Max Min Typ Max Min Typ Max Unit

8× Mode, f

= 1 GSPS, IF = 262.5 MHz

f

DAC

/4 Modulation,

DAC

Power-Down Mode 2 3.7 2 3.7 2 3.7 mW

Power Supply Rejection Ratio,

AVDD33

OPERATING RANGE −40 +25 +85 −40 +25 +85 −40 +25 +85 °C

1

Based on a 10 k external resistor.

980 980 980 mW

−0.3 +0.3 −0.3 +0.3 −0.3 +0.3 % FSR/V

Rev. A | Page 5 of 56

AD9776/AD9778/AD9779

DIGITAL SPECIFICATIONS

T

to T

MIN

, AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, = 20 mA, maximum sample rate, unless

MAX

otherwise noted. LVDS driver and receiver are compliant to the IEEE-1596 reduced range link, unless otherwise noted.

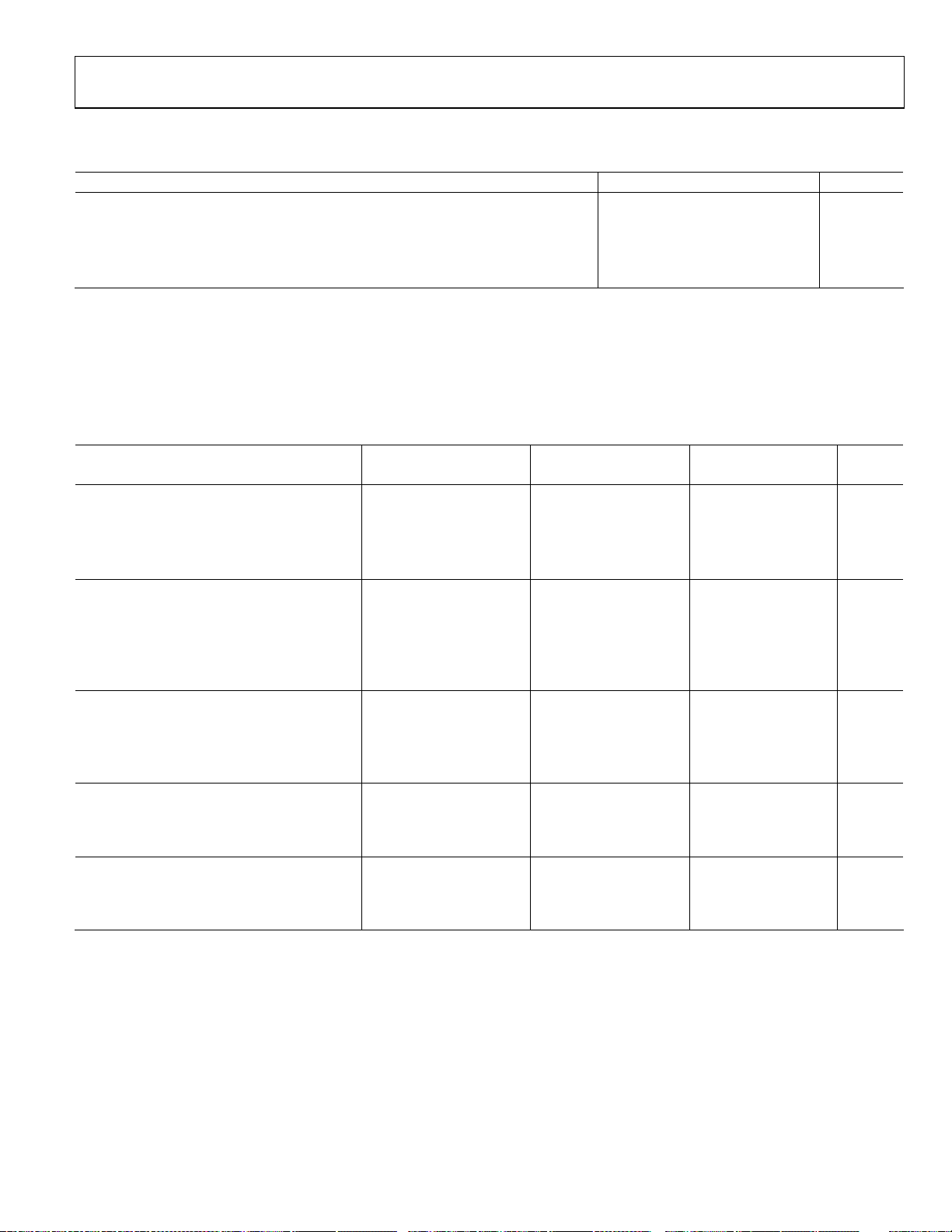

Table 2. AD9776, AD9778, and AD9779 Digital Specifications

Parameter Conditions Min Typ Max Unit

CMOS INPUT LOGIC LEVEL

Input V

Input V

Logic High 2.0 V

IN

Logic Low 0.8 V

IN

Maximum Input Data Rate at Interpolation

1× 300 MSPS

2× 250 MSPS

4× 200 MSPS

8× 125 MSPS

CMOS OUTPUT LOGIC LEVEL (DATACLK, PIN 37)

Output V

Output V

Logic High 2.4 V

OUT

Logic Low 0.4 V

OUT

1

LVDS RECEIVER INPUTS (SYNC_I+, SYNC_I−) SYNC_I+ = VIA, SYNC_I− = V

Input Voltage Range, VIA or V

Input Differential Threshold, V

Input Differential Hysteresis, V

IB

−100 +100 mV

IDTH

− V

IDTHH

IDTHL

Receiver Differential Input Impedance, R

2

IN

825 1575 mV

20 mV

80 120 Ω

LVDS Input Rate 125 MSPS

Set-Up Time, SYNC_I to DAC Clock −0.2 ns

Hold Time, SYNC_I to DAC Clock 1 ns

LVDS DRIVER OUTPUTS (SYNC_O+, SYNC_O−) SYNC_O+ = VOA, SYNC_O− = VOB, 100 Ω termination

Output Voltage High, VOA or V

Output Voltage Low, VOA or V

OB

OB

825 1575 mV

1025 mV

Output Differential Voltage, |VOD| 150 200 250 mV

Output Offset Voltage, V

Output Impedance, R

O

OS

1150 1250 mV

Single-ended 80 100 120 Ω

Maximum Clock Rate 1 GHz

DAC CLOCK INPUT (CLK+, CLK−)

Differential Peak-to-Peak Voltage (CLK+, CLK−)

3

400 800 2000 mV

Common-Mode Voltage 300 400 500 mV

Maximum Clock Rate

4

1 GSPS

SERIAL PERIPHERAL INTERFACE

Maximum Clock Rate (SCLK) 40 MHz

Minimum Pulse Width High 12.5 ns

Minimum Pulse Width Low 12.5 ns

1

Specification is at a DATACLK frequency of 100 MHz into a 1 kΩ load; maximum drive capability of 8 mA. At higher speeds or greater loads, best practice suggests

using an external buffer for this signal.

2

Guaranteed at 25°C. Can drift above 120 Ω at temperatures above 25°C.

3

When using the PLL, a differential swing of 2 V p-p is recommended.

4

Typical maximum clock rate when DVDD18 = CVDD18 = 1.9 V.

I

OUTF

S

IB

Rev. A | Page 6 of 56

AD9776/AD9778/AD9779

DIGITAL INPUT DATA TIMING SPECIFICATIONS

Table 3. AD9776, AD9778, and AD9779 Digital Input Data Timing Specifications

Parameter Min Typ Max Unit

INPUT DATA (ALL MODES, −40°C to +85°C)1

Set-Up Time, Input Data to DATACLK +2.5 ns

Hold Time, Input Data to DATACLK −0.4 ns

Set-Up Time, Input Data to REFCLK −0.8 ns

Hold Time, Input Data to REFCLK +2.9 ns

1

Timing vs. temperature and data valid keep out windows are delineated in Table 19.

AC SPECIFICATIONS

T

to T

MIN

otherwise noted.

Table 4. AD9776, AD9778, and AD9779 AC Specifications

Parameter Min Typ Max Min Typ Max Min Typ Max Unit

SPURIOUS FREE DYNAMIC RANGE (SFDR)

f

DAC

f

DAC

f

DAC

f

DAC

TWO-TONE INTERMODULATION DISTORTION

(IMD)

f

DAC

f

DAC

f

DAC

f

DAC

NOISE SPECTRAL DENSITY (NSD) EIGHT-TONE,

500 kHz TONE SPACING

f

DAC

f

DAC

f

DAC

WCDMA ADJACENT CHANNEL LEAKAGE

RATIO (ACLR), SINGLE CARRIER

f

DAC

f

DAC

WCDMA SECOND ADJACENT CHANNEL

LEAKAGE RATIO (ACLR), SINGLE CARRIER

f

DAC

f

DAC

, AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, = 20 mA, maximum sample rate, unless

MAX

I

OUTF

S

AD9776 AD9778 AD9779

= 100 MSPS, f

= 200 MSPS, f

= 400 MSPS, f

= 800 MSPS, f

= 20 MHz 82 82 82 dBc

OUT

= 50 MHz 81 81 82 dBc

OUT

= 70 MHz 80 80 80 dBc

OUT

= 70 MHz 85 85 87 dBc

OUT

= 200 MSPS, f

= 400 MSPS, f

= 400 MSPS, f

= 800 MSPS, f

= 50 MHz 87 87 91 dBc

OUT

= 60 MHz 80 85 85 dBc

OUT

= 80 MHz 75 81 81 dBc

OUT

= 100 MHz 75 80 81 dBc

OUT

= 200 MSPS, f

= 400 MSPS, f

= 800 MSPS, f

= 80 MHz −152 −155 −158 dBm/Hz

OUT

= 80 MHz −155 −159 −160 dBm/Hz

OUT

= 80 MHz −157.5 −160 −161 dBm/Hz

OUT

= 491.52 MSPS, f

= 491.52 MSPS, f

= 100 MHz 76 78 79 dBc

OUT

= 200 MHz 69 73 74 dBc

OUT

= 491.52 MSPS, f

= 491.52 MSPS, f

= 100 MHz 77.5 80 81 dBc

OUT

= 200 MHz 76 78 78 dBc

OUT

Rev. A | Page 7 of 56

AD9776/AD9778/AD9779

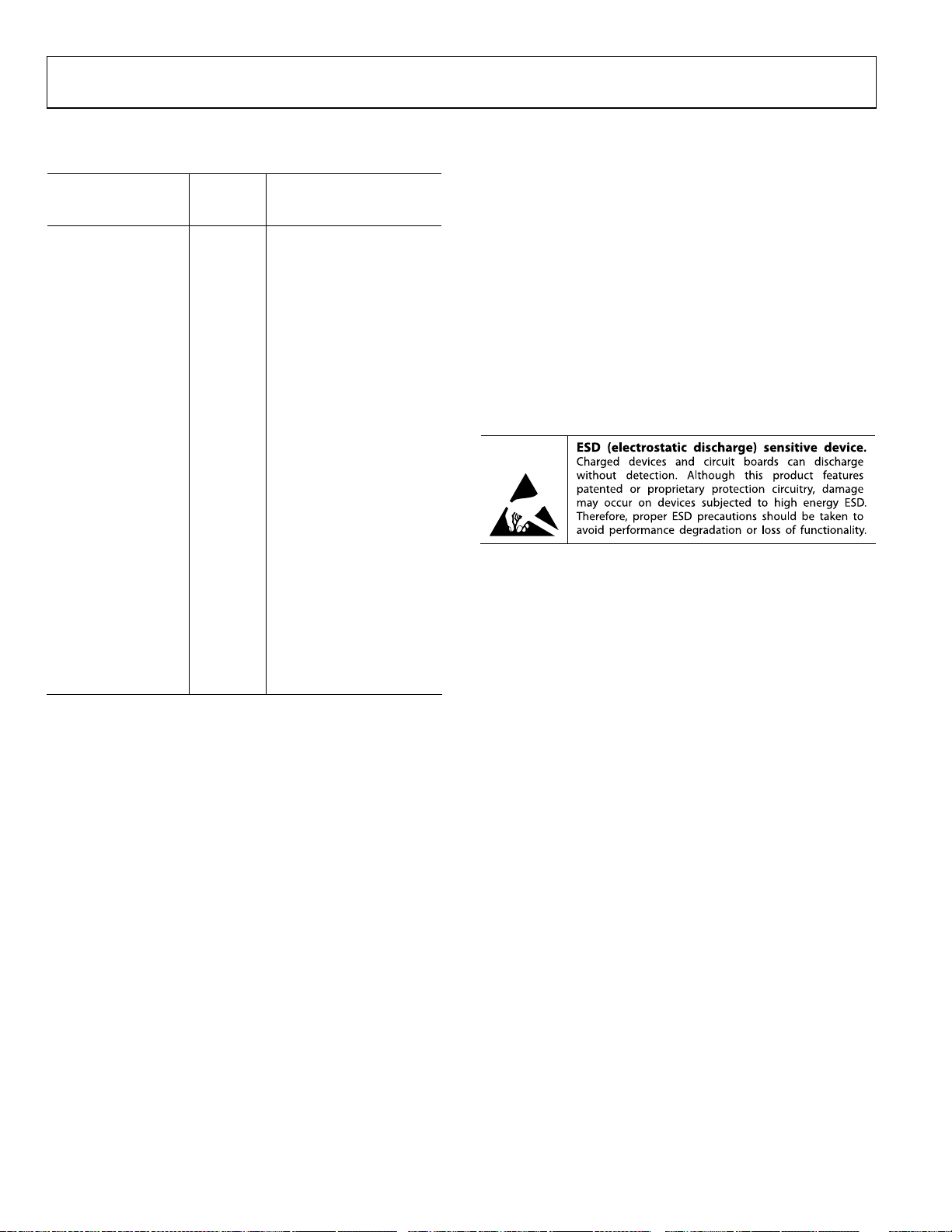

ABSOLUTE MAXIMUM RATINGS

Table 5.

With

Respect

Parameter

AVDD33, DVDD33

DVDD18, CVDD18

AGND

DGND

CGND

I120, VREF, IPTAT AGND −0.3 V to AVDD33 + 0.3 V

I

, I

2-P

OUT1-N

, Aux

, Aux

1-P

2-N

, I

OUT2-P

, Aux

OUT1-P

I

OUT2-N

Aux

P1D15 to P1D0,

P2D15 to P2D0

DATACLK, TXENABLE DGND −0.3 V to DVDD33 + 0.3 V

CLK+, CLK− CGND −0.3 V to CVDD18 + 0.3 V

RESET, IRQ, PLL_LOCK,

SYNC_O+, SYNC_O−,

SYNC_I+, SYNC_I−,

CSB, SCLK, SDIO, SDO

Junction Temperature +125°C

Storage Temperature

Range

To

AGND,

Rating

−0.3 V to +3.6 V

DGND,

CGND

AGND,

−0.3 V to +1.98 V

DGND,

CGND

DGND,

−0.3 V to +0.3 V

CGND

AGND,

−0.3 V to +0.3 V

CGND

AGND,

−0.3 V to +0.3 V

DGND

AGND −1.0 V to AVDD33 + 0.3 V

,

,

1-N

DGND −0.3 V to DVDD33 + 0.3 V

DGND −0.3 V to DVDD33 + 0.3 V

−65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

100-lead, thermally enhanced TQFP_EP package, θJA = 19.1°C/W

with the bottom EPAD soldered to the PCB. With the bottom

EPAD not soldered to the PCB, θ

= 27.4°C/W. These

JA

specifications are valid with no airflow movement.

ESD CAUTION

Rev. A | Page 8 of 56

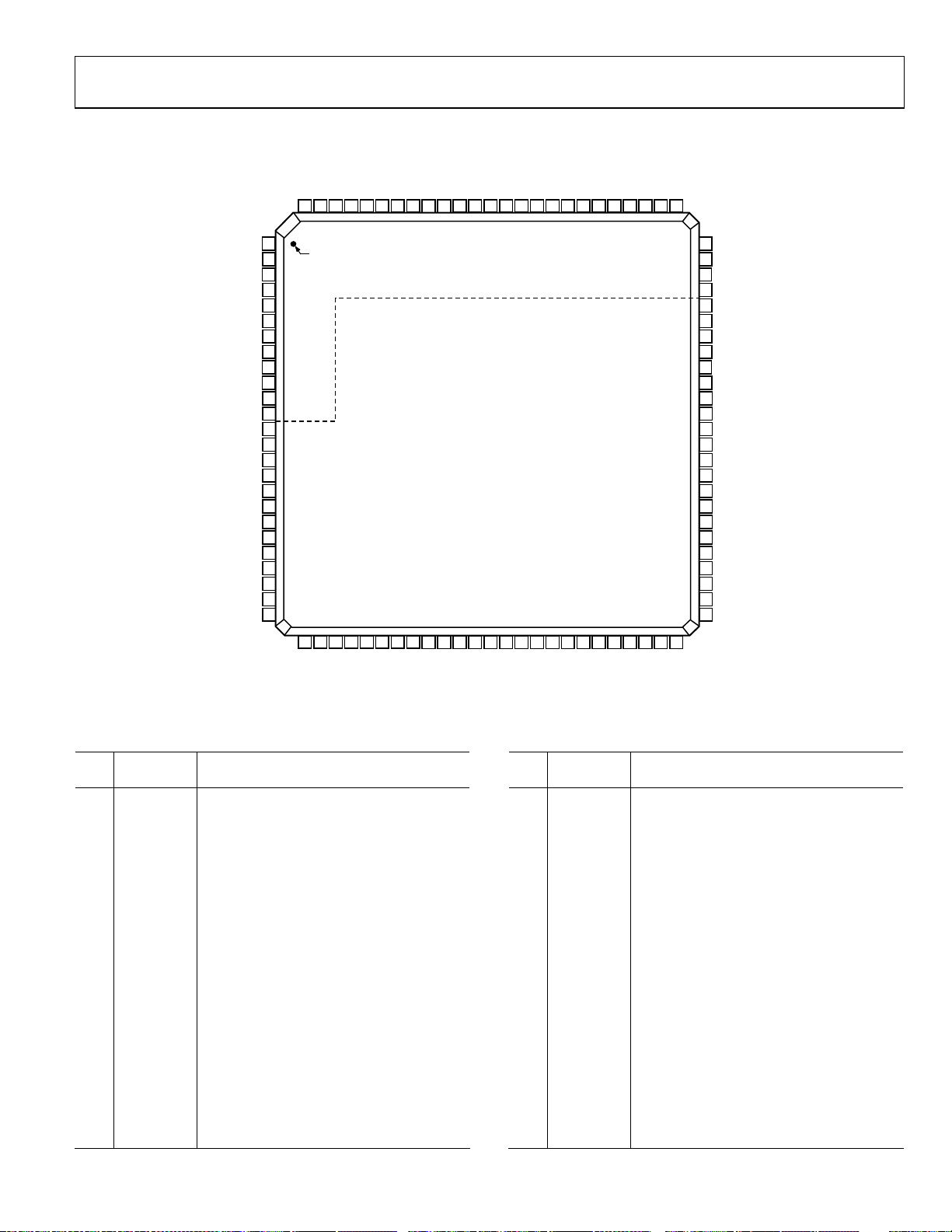

AD9776/AD9778/AD9779

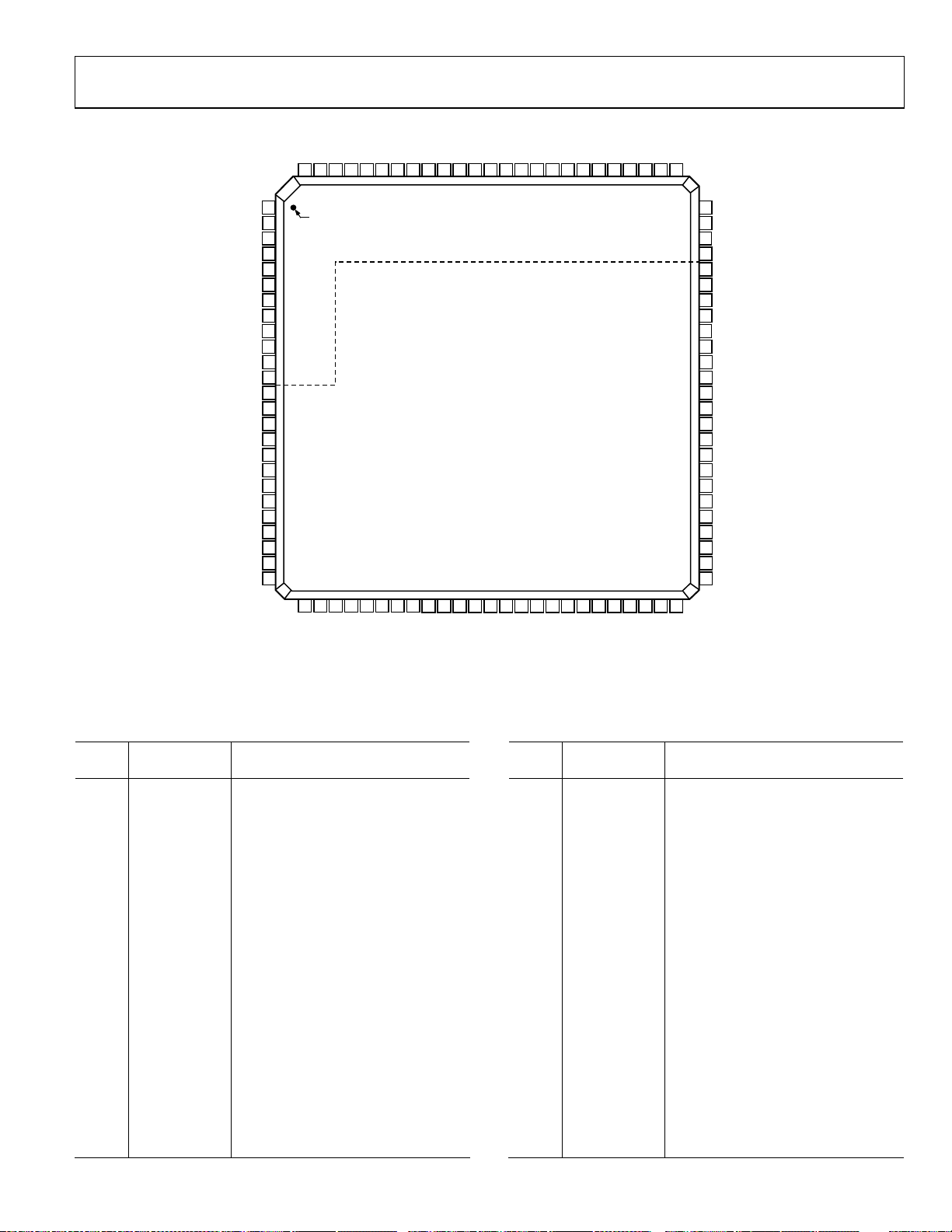

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

AVDD3399AGND98AVDD3397AGND96AVDD3395AGND94AGND93OUT1_P92OUT1_N91AGND90AUX1_P89AUX1_N88AGND87AUX2_N86AUX2_P85AGND84OUT2_N83OUT2_P82AGND81AGND80AVDD3379AGND78AVDD3377AGND76AVDD33

100

CGND

CGND

CLK+

CLK–

CGND

CGND

CGND

AGND

DGND

P1D<9>

P1D<8>

P1D<7>

DGND

P1D<6>

P1D<5>

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

PIN 1

26

P1D<4>27P1D<3>28P1D<2>29P1D<1>30P1D<0>

31NC32

CVDD18

CVDD18

CVDD18

CVDD18

SYNC_I+

SYNC_I–

DVDD18

P1D<11>

P1D<10>

DVDD18

NC = NO CONNECT

Table 6. AD9776 Pin Function Descriptions

Pin

No.

Mnemonic Description

1 CVDD18 1.8 V Clock Supply.

2 CVDD18 1.8 V Clock Supply.

3 CGND Clock Common.

4 CGND Clock Common.

5 CLK+

6 CLK−

1

1

Differential Clock Input.

Differential Clock Input.

7 CGND Clock Common.

8 CGND Clock Common.

9 CVDD18 1.8 V Clock Supply.

10 CVDD18 1.8 V Clock Supply.

11 CGND Clock Common.

12 AGND Analog Common.

13 SYNC_I+ Differential Synchronization Input.

14 SYNC_I− Differential Synchronization Input.

15 DGND Digital Common.

16 DVDD18 1.8 V Digital Supply.

17 P1D<11> Port 1, Data Input D11 (MSB).

18 P1D<10> Port 1, Data Input D10.

19 P1D<9> Port 1, Data Input D9.

ANALOG DOMAIN

DIGITAL DOMAIN

AD9776

TOP VIEW

(Not to Scale)

33

DGND

DVDD18

34NC35NC36NC37

38

39

DVDD33

DATACLK

TXENABLE

40

P2D<11>41P2D<10>

42

P2D<9>

Figure 3. AD9776 Pin Configuration

Pin

No.

Mnemonic Description

20 P1D<8> Port 1, Data Input D8.

21 P1D<7> Port 1, Data Input D7.

22 DGND Digital Common.

23 DVDD18 1.8 V Digital Supply.

24 P1D<6> Port 1, Data Input D6.

25 P1D<5> Port 1, Data Input D5.

26 P1D<4> Port 1, Data Input D4.

27 P1D<3> Port 1, Data Input D3.

28 P1D<2> Port 1, Data Input D2.

29 P1D<1> Port 1, Data Input D1.

30 P1D<0> Port 1, Data Input D0 (LSB).

31 NC No Connect.

32 DGND Digital Common.

33 DVDD18 1.8 V Digital Supply.

34 NC No Connect.

35 NC No Connect.

36 NC No Connect.

DATACLK

37

38 DVDD33 3.3 V Digital Supply.

43

44

45

DGND

DVDD18

P2D<8>46P2D<7>47P2D<6>48P2D<5>49P2D<4>50P2D<3>

Data Clock Output.

75

I120

74

VREF

73

IPTAT

72

AGND

71

IRQ

70

RESET

69

CSB

68

SCLK

67

SDIO

66

SDO

65

PLL_LOCK

64

DGND

63

SYNC_O+

62

SYNC_O–

61

DVDD33

60

DVDD18

59

NC

58

NC

57

NC

56

NC

55

P2D<0>

54

DGND

53

DVDD18

52

P2D<1>

51

P2D<2>

05361-002

Rev. A | Page 9 of 56

AD9776/AD9778/AD9779

Pin

No. Mnemonic

39 TXENABLE Transmit Enable.

40 P2D<11> Port 2, Data Input D11 (MSB).

41 P2D<10> Port 2, Data Input D10.

42 P2D<9> Port 2, Data Input D9.

43 DVDD18 1.8 V Digital Supply.

44 DGND Digital Common.

45 P2D<8> Port 2, Data Input D8.

46 P2D<7> Port 2, Data Input D7.

47 P2D<6> Port 2, Data Input D6.

48 P2D<5> Port 2, Data Input D5.

49 P2D<4> Port 2, Data Input D4.

50 P2D<3> Port 2, Data Input D3.

51 P2D<2> Port 2, Data Input D2.

52 P2D<1> Port 2, Data Input D1.

53 DVDD18 1.8 V Digital Supply.

54 DGND Digital Common.

55 P2D<0> Port 2, Data Input D0 (LSB).

56 NC No Connect.

57 NC No Connect.

58 NC No Connect.

59 NC No Connect.

60 DVDD18 1.8 V Digital Supply.

61 DVDD33 3.3 V Digital Supply.

62 SYNC_O− Differential Synchronization Output.

63 SYNC_O+ Differential Synchronization Output

64 DGND Digital Common

65 PLL_LOCK PLL Lock Indicator

66 SDO SPI Port Data Output

67 SDIO SPI Port Data Input/Output

68 SCLK SPI Port Clock

69 CSB SPI Port Chip Select Bar.

70 RESET Reset, Active High.

71 IRQ Interrupt Request.

72 AGND Analog Common.

Description

Pin

No. Mnemonic

73 IPTAT

Description

Factory Test Pin. Output current is

proportional to absolute temperature,

approximately 10 μA at 25°C with

approximately 20 nA/°C slope. This pin

should remain floating.

74 VREF Voltage Reference Output.

75 I120 120 μA Reference Current.

76 AVDD33 3.3 V Analog Supply.

77 AGND Analog Common.

78 AVDD33 3.3 V Analog Supply.

79 AGND Analog Common.

80 AVDD33 3.3 V Analog Supply.

81 AGND Analog Common.

82 AGND Analog Common.

83 OUT2_P Differential DAC Current Output, Channel 2.

84 OUT2_N Differential DAC Current Output, Channel 2.

85 AGND Analog Common.

86 AUX2_P Auxiliary DAC Current Output, Channel 2.

87 AUX2_N Auxiliary DAC Current Output, Channel 2.

88 AGND Analog Common.

89 AUX1_N Auxiliary DAC Current Output, Channel 1.

90 AUX1_P Auxiliary DAC Current Output, Channel 1.

91 AGND Analog Common.

92 OUT1_N Differential DAC Current Output, Channel 1.

93 OUT1_P Differential DAC Current Output, Channel 1.

94 AGND Analog Common.

95 AGND Analog Common.

96 AVDD33 3.3 V Analog Supply.

97 AGND Analog Common.

98 AVDD33 3.3 V Analog Supply.

99 AGND Analog Common.

100 AVDD33 3.3 V Analog Supply.

1

The combined differential clock input at the CLK+ and CLK– pins are referred

to as REFCLK.

Rev. A | Page 10 of 56

AD9776/AD9778/AD9779

AVDD3399AGND98AVDD3397AGND96AVDD3395AGND94AGND93OUT1_P92OUT1_N91AGND90AUX1_P89AUX1_N88AGND87AUX2_N86AUX2_P85AGND84OUT2_N83OUT2_P82AGND81AGND80AVDD3379AGND78AVDD3377AGND76AVDD33

100

CGND

CGND

CLK+

CLK–

CGND

CGND

CGND

AGND

DGND

P1D<9>

DGND

P1D<8>

P1D<7>

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

CVDD18

CVDD18

CVDD18

CVDD18

SYNC_I+

SYNC_I–

DVDD18

P1D<13>

P1D<12>

P1D<11>

P1D<10>

DVDD18

NC = NO CONNECT

PIN 1

26

P1D<6>27P1D<5>28P1D<4>29P1D<3>30P1D<2>31P1D<1>

ANALOG DOMAIN

DIGITAL DOMAIN

AD9778

TOP VIEW

(Not to Scale)

32

33

34

35NC36NC37

38

39

40

DGND

P1D<0>

DVDD18

Figure 4. AD9778 Pin Configuration

DVDD33

DATACLK

TXENABLE

P2D<13>41P2D<12>42P2D<11>

75

I120

74

VREF

73

IPTAT

72

AGND

71

IRQ

70

RESET

69

CSB

68

SCLK

67

SDIO

66

SDO

65

PLL_LOCK

64

DGND

63

SYNC_O+

62

SYNC_O–

61

DVDD33

60

DVDD18

59

NC

58

NC

57

P2D<0>

56

P2D<1>

55

P2D<2>

54

DGND

53

DVDD18

52

P2D<3>

51

P2D<4>

43

44

45

46

DGND

DVDD18

P2D<9>47P2D<8>48P2D<7>49P2D<6>50P2D<5>

P2D<10>

05361-003

Table 7. AD9778 Pin Function Description

Pin

No.

Mnemonic Description

1 CVDD18 1.8 V Clock Supply.

2 CVDD18 1.8 V Clock Supply.

3 CGND Clock Common.

4 CGND Clock Common.

5 CLK+

6 CLK−

1

1

Differential Clock Input.

Differential Clock Input.

7 CGND Clock Common.

8 CGND Clock Common.

9 CVDD18 1.8 V Clock Supply.

10 CVDD18 1.8 V Clock Supply.

11 CGND Clock Common.

12 AGND Analog Common.

13 SYNC_I+ Differential Synchronization Input.

14 SYNC_I− Differential Synchronization Input.

15 DGND Digital Common.

16 DVDD18 1.8 V Digital Supply.

17 P1D<13> Port 1, Data Input D13 (MSB).

18 P1D<12> Port 1, Data Input D12.

19 P1D<11> Port 1, Data Input D11.

20 P1D<10> Port 1, Data Input D10.

Pin

No.

21 P1D<9> Port 1, Data Input D9.

22 DGND Digital Common.

23 DVDD18 1.8 V Digital Supply.

24 P1D<8> Port 1, Data Input D8.

25 P1D<7> Port 1, Data Input D7.

26 P1D<6> Port 1, Data Input D6.

27 P1D<5> Port 1, Data Input D5.

28 P1D<4> Port 1, Data Input D4.

29 P1D<3> Port 1, Data Input D3.

30 P1D<2> Port 1, Data Input D2.

31 P1D<1> Port 1, Data Input D1.

32 DGND Digital Common.

33 DVDD18 1.8 V Digital Supply.

34 P1D<0> Port 1, Data Input D0 (LSB).

35 NC No Connect.

36 NC No Connect.

37

38 DVDD33 3.3 V Digital Supply.

39 TXENABLE Transmit Enable.

40 P2D<13> Port 2, Data Input D13 (MSB).

Rev. A | Page 11 of 56

Mnemonic Description

DATACLK

Data Clock Output.

AD9776/AD9778/AD9779

Pin

No.

41 P2D<12> Port 2, Data Input D12.

42 P2D<11> Port 2, Data Input D11.

43 DVDD18 1.8 V Digital Supply.

44 DGND Digital Common.

45 P2D<10> Port 2, Data Input D10.

46 P2D<9> Port 2, Data Input D9.

47 P2D<8> Port 2, Data Input D8.

48 P2D<7> Port 2, Data Input D7.

49 P2D<6> Port 2, Data Input D6.

50 P2D<5> Port 2, Data Input D5.

51 P2D<4> Port 2, Data Input D4.

52 P2D<3> Port 2, Data Input D3.

53 DVDD18 1.8 V Digital Supply.

54 DGND Digital Common.

55 P2D<2> Port 2, Data Input D2.

56 P2D<1> Port 2, Data Input D1.

57 P2D<0> Port 2, Data Input D0 (LSB).

58 NC No Connect.

59 NC No Connect.

60 DVDD18 1.8 V Digital Supply.

61 DVDD33 3.3 V Digital Supply.

62 SYNC_O− Differential Synchronization Output.

63 SYNC_O+ Differential Synchronization Output.

64 DGND Digital Common.

65 PLL_LOCK PLL Lock Indicator.

66 SDO SPI Port Data Output.

67 SDIO SPI Port Data Input/Output.

68 SCLK SPI Port Clock.

69 CSB SPI Port Chip Select Bar.

70 RESET Reset, Active High.

71 IRQ Interrupt Request.

72 AGND Analog Common.

73 IPTAT

Mnemonic Description

Factory Test Pin. Output current is

proportional to absolute temperature,

approximately 10 μA at 25°C with

approximately 20 nA/°C slope. This

pin should remain floating.

Pin

No.

Mnemonic Description

74 VREF Voltage Reference Output.

75 I120 120 μA Reference Current.

76 AVDD33 3.3 V Analog Supply.

77 AGND Analog Common.

78 AVDD33 3.3 V Analog Supply.

79 AGND Analog Common.

80 AVDD33 3.3 V Analog Supply.

81 AGND Analog Common.

82 AGND Analog Common.

83 OUT2_P

Differential DAC Current Output,

Channel 2.

84 OUT2_N

Differential DAC Current Output,

Channel 2.

85 AGND Analog Common.

86 AUX2_P

Auxiliary DAC Current Output,

Channel 2.

87 AUX2_N

Auxiliary DAC Current Output,

Channel 2.

88 AGND Analog Common.

89 AUX1_N

Auxiliary DAC Current Output,

Channel 1.

90 AUX1_P

Auxiliary DAC Current Output,

Channel 1.

91 AGND Analog Common.

92 OUT1_N

Differential DAC Current Output,

Channel 1.

93 OUT1_P

Differential DAC Current Output,

Channel 1.

94 AGND Analog Common.

95 AGND Analog Common.

96 AVDD33 3.3 V Analog Supply.

97 AGND Analog Common.

98 AVDD33 3.3 V Analog Supply.

99 AGND Analog Common.

100 AVDD33 3.3 V Analog Supply.

1

The combined differential clock input at the CLK+ and CLK– pins are referred

to as REFCLK.

Rev. A | Page 12 of 56

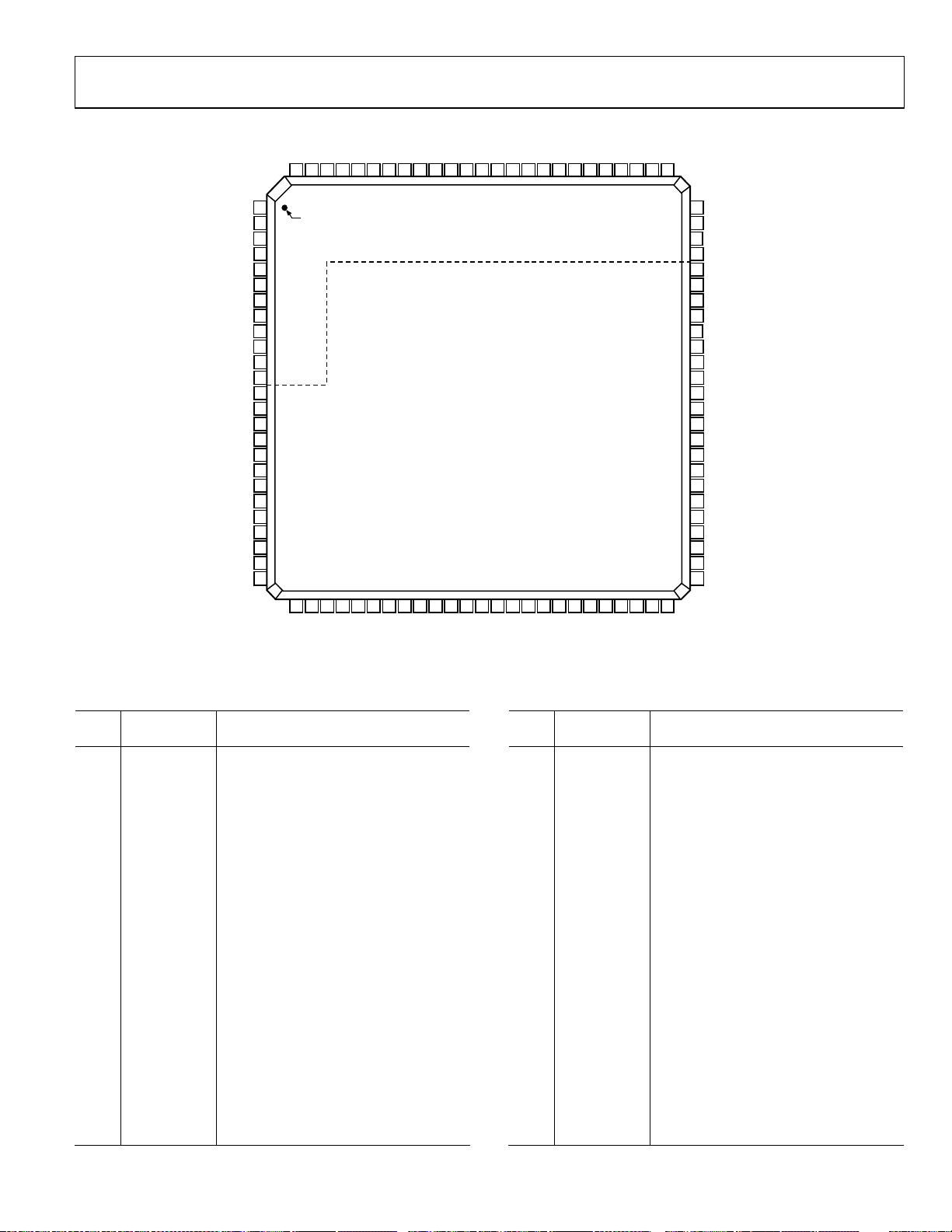

AD9776/AD9778/AD9779

AVDD3399AGND98AVDD3397AGND96AVDD3395AGND94AGND93OUT1_P92OUT1_N91AGND90AUX1_P89AUX1_N88AGND87AUX2_N86AUX2_P85AGND84OUT2_N83OUT2_P82AGND81AGND80AVDD3379AGND78AVDD3377AGND76AVDD33

100

CGND

CGND

CLK+

CLK–

CGND

CGND

CGND

AGND

DGND

DGND

P1D<9>

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

PIN 1

26

P1D<8>27P1D<7>28P1D<6>29P1D<5>30P1D<4>31P1D<3>

32

33

DGND

DVDD18

CVDD18

CVDD18

CVDD18

CVDD18

SYNC_I+

SYNC_I–

DVDD18

P1D<15>

P1D<14>

P1D<13>

P1D<12>

P1D<11>

DVDD18

P1D<10>

Figure 5. AD9779 Pin Configuration

Table 8. AD9779 Pin Function Descriptions

Pin

No.

Mnemonic Description

1 CVDD18 1.8 V Clock Supply.

2 CVDD18 1.8 V Clock Supply.

3 CGND Clock Common.

4 CGND Clock Common.

5 CLK+

6 CLK−

1

1

Differential Clock Input.

Differential Clock Input.

7 CGND Clock Common.

8 CGND Clock Common.

9 CVDD18 1.8 V Clock Supply.

10 CVDD18 1.8 V Clock Supply.

11 CGND Clock Common.

12 AGND Analog Common.

13 SYNC_I+ Differential Synchronization Input.

14 SYNC_I− Differential Synchronization Input.

15 DGND Digital Common.

16 DVDD18 1.8 V Digital Supply.

17 P1D<15> Port 1, Data Input D15 (MSB).

18 P1D<14> Port 1, Data Input D14.

19 P1D<13> Port 1, Data Input D13.

20 P1D<12> Port 1, Data Input D12.

21 P1D<11> Port 1, Data Input D11.

34

P1D<2>35P1D<1>36P1D<0>

ANALOG DOMAIN

DIGITAL DOMAIN

AD9779

TOP VIEW

(Not to Scale)

37

38

39

DVDD33

DATACLK

TXENABLE

75

I120

74

VREF

73

IPTAT

72

AGND

71

IRQ

70

RESET

69

CSB

68

SCLK

67

SDIO

66

SDO

65

PLL_LOCK

64

DGND

63

SYNC_O+

62

SYNC_O–

61

DVDD33

60

DVDD18

59

P2D<0>

58

P2D<1>

57

P2D<2>

56

P2D<3>

55

P2D<4>

54

DGND

53

DVDD18

52

P2D<5>

51

P2D<6>

40

43

44

45

48

P2D<15>41P2D<14>42P2D<13>

DVDD18

DGND

P2D<12>46P2D<11>47P2D<10>

P2D<9>49P2D<8>50P2D<7>

05361-004

Pin

No.

Mnemonic Description

22 DGND Digital Common.

23 DVDD18 1.8 V Digital Supply.

24 P1D<10> Port 1, Data Input D10.

25 P1D<9> Port 1, Data Input D9.

26 P1D<8> Port 1, Data Input D8.

27 P1D<7> Port 1, Data Input D7.

28 P1D<6> Port 1, Data Input D6.

29 P1D<5> Port 1, Data Input D5.

30 P1D<4> Port 1, Data Input D4.

31 P1D<3> Port 1, Data Input D3.

32 DGND Digital Common.

33 DVDD18 1.8 V Digital Supply.

34 P1D<2> Port 1, Data Input D2.

35 P1D<1> Port 1, Data Input D1.

36 P1D<0> Port 1, Data Input D0 (LSB).

DATACLK

37

Data Clock Output.

38 DVDD33 3.3 V Digital Supply.

39 TXENABLE Transmit Enable.

40 P2D<15> Port 2, Data Input D15 (MSB).

41 P2D<14> Port 2, Data Input D14.

42 P2D<13> Port 2, Data Input D13.

Rev. A | Page 13 of 56

AD9776/AD9778/AD9779

Pin

Mnemonic Description

No.

43 DVDD18 1.8 V Digital Supply.

44 DGND Digital Common.

45 P2D<12> Port 2, Data Input D12.

46 P2D<11> Port 2, Data Input D11.

47 P2D<10> Port 2, Data Input D10.

48 P2D<9> Port 2, Data Input D9.

49 P2D<8> Port 2, Data Input D8.

50 P2D<7> Port 2, Data Input D7.

51 P2D<6> Port 2, Data Input D6.

52 P2D<5> Port 2, Data Input D5.

53 DVDD18 1.8 V Digital Supply.

54 DGND Digital Common.

55 P2D<4> Port 2, Data Input D4.

56 P2D<3> Port 2, Data Input D3.

57 P2D<2> Port 2, Data Input D2.

58 P2D<1> Port 2, Data Input D1.

59 P2D<0> Port 2, Data Input D0 (LSB).

60 DVDD18 1.8 V Digital Supply.

61 DVDD33 3.3 V Digital Supply.

62 SYNC_O− Differential Synchronization Output.

63 SYNC_O+ Differential Synchronization Output.

64 DGND Digital Common.

65 PLL_LOCK PLL Lock Indicator.

66 SPI_SDO SPI Port Data Output.

67 SPI_SDIO SPI Port Data Input/Output.

68 SCLK SPI Port Clock.

69 SPI_CSB SPI Port Chip Select Bar.

70 RESET Reset, Active High.

71 IRQ Interrupt Request.

72 AGND Analog Common.

73 IPTAT

Factory Test Pin. Output current is

proportional to absolute temperature,

approximately 10 μA at 25°C with

approximately 20 nA/°C slope. This pin

should remain floating.

Pin

Mnemonic Description

No.

74 VREF Voltage Reference Output.

75 I120 120 μA Reference Current.

76 AVDD33 3.3 V Analog Supply.

77 AGND Analog Common.

78 AVDD33 3.3 V Analog Supply.

79 AGND Analog Common.

80 AVDD33 3.3 V Analog Supply.

81 AGND Analog Common.

82 AGND Analog Common.

83 OUT2_P

Differential DAC Current Output,

Channel 2.

84 OUT2_N

Differential DAC Current Output,

Channel 2.

85 AGND Analog Common.

86 AUX2_P Auxiliary DAC Current Output, Channel 2.

87 AUX2_N Auxiliary DAC Current Output, Channel 2.

88 AGND Analog Common.

89 AUX1_N Auxiliary DAC Current Output, Channel 1.

90 AUX1_P Auxiliary DAC Current Output, Channel 1.

91 AGND Analog Common.

92 OUT1_N

Differential DAC Current Output,

Channel 1.

93 OUT1_P

Differential DAC Current Output,

Channel 1.

94 AGND Analog Common.

95 AGND Analog Common.

96 AVDD33 3.3 V Analog Supply.

97 AGND Analog Common.

98 AVDD33 3.3 V Analog Supply.

99 AGND Analog Common.

100 AVDD33 3.3 V Analog Supply.

1

The combined differential clock input at the CLK+ and CLK– pins are referred

to as REFCLK.

Rev. A | Page 14 of 56

AD9776/AD9778/AD9779

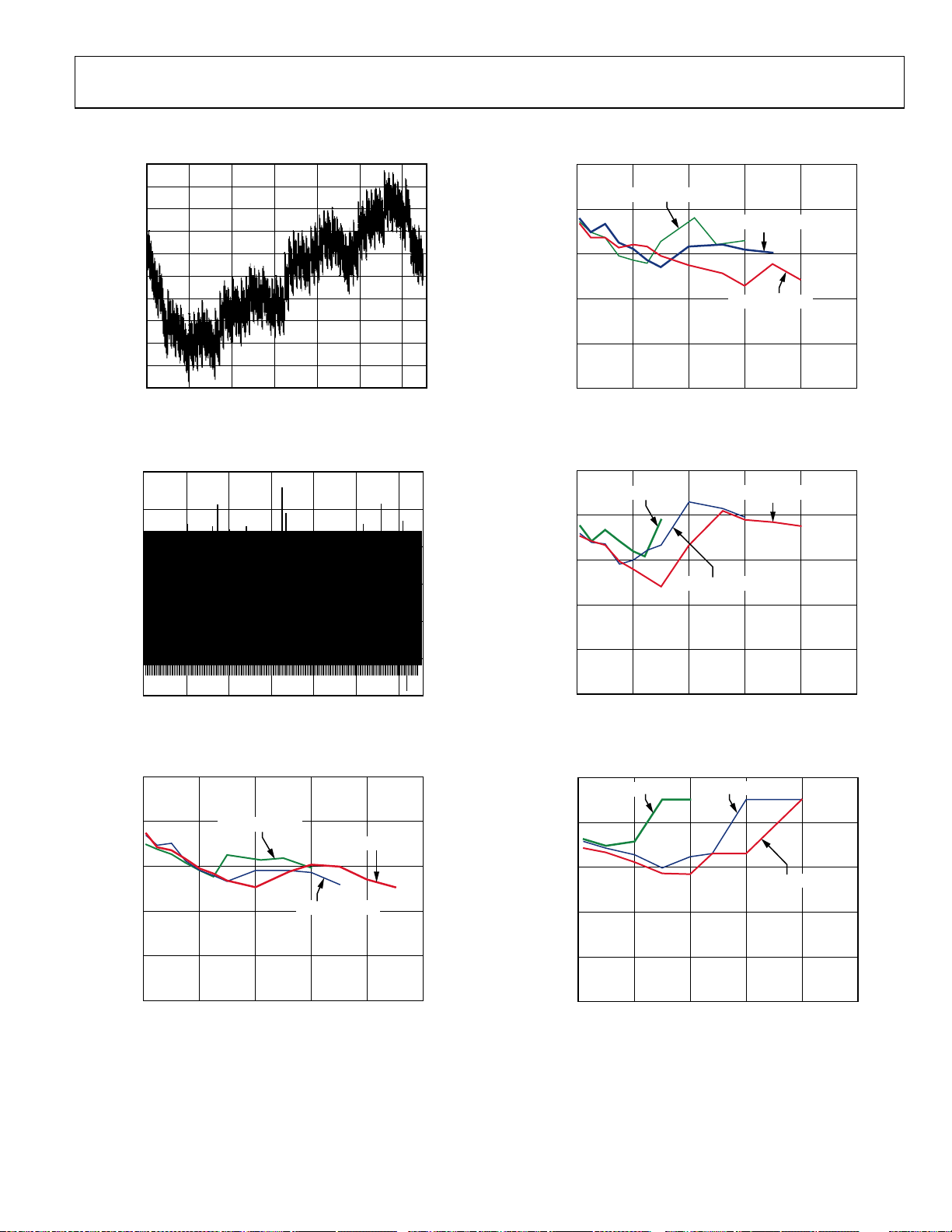

TYPICAL PERFORMANCE CHARACTERISTICS

4

3

2

1

0

–1

–2

INL (16-BIT LSB)

–3

–4

–5

–6

0

10k 20k 30k 60k50k40k

CODE

Figure 6. AD9779 Typical INL

05361-005

100

f

= 160MSPS

90

80

70

SFDR (dBc)

60

50

0 100

Figure 9. AD9779 In-Band SFDR vs. f

DATA

f

= 200MSPS

DATA

f

= 250MSPS

DATA

20 40 60 80

f

OUT

(MHz)

, 2× Interpolation

OUT

05361-008

1.5

1.0

0.5

0

–0.5

DNL (16-BIT LSB)

–1.0

–1.5

–2.0

0

100

90

80

70

SFDR (dBc)

CODE

Figure 7. AD9779 Typical DNL

f

= 160MSPS

DATA

f

f

= 200MSPS

DATA

DATA

60k50k40k30k20k10k

= 250MSPS

05361-006

100

f

f

= 100MSPS

DATA

90

80

f

= 150MSPS

DATA

70

SFDR (dBc)

60

50

0 100

20 40 60 80

f

OUT

(MHz)

Figure 10. AD9779 In-Band SFDR vs. f

100

f

= 50MSPS

DATA

90

80

70

SFDR (dBc)

f

DATA

= 200MSPS

DATA

, 4× Interpolation

OUT

= 100MSPS

f

DATA

= 125MSPS

05361-009

60

50

0 100

Figure 8. AD9779 In-Band SFDR vs. f

20 40 60 80

f

(MHz)

OUT

, 1x Interpolation

OUT

05361-007

Rev. A | Page 15 of 56

60

50

0

10 20 30 40

f

OUT

(MHz)

Figure 11. AD9779 In-Band SFDR vs. f

, 8× Interpolation

OUT

50

05361-010

AD9776/AD9778/AD9779

100

100

90

f

= 160MSPS

DATA

80

70

SFDR (dBc)

60

50

0

20 40 60 80

f

OUT

f

DATA

(MHz)

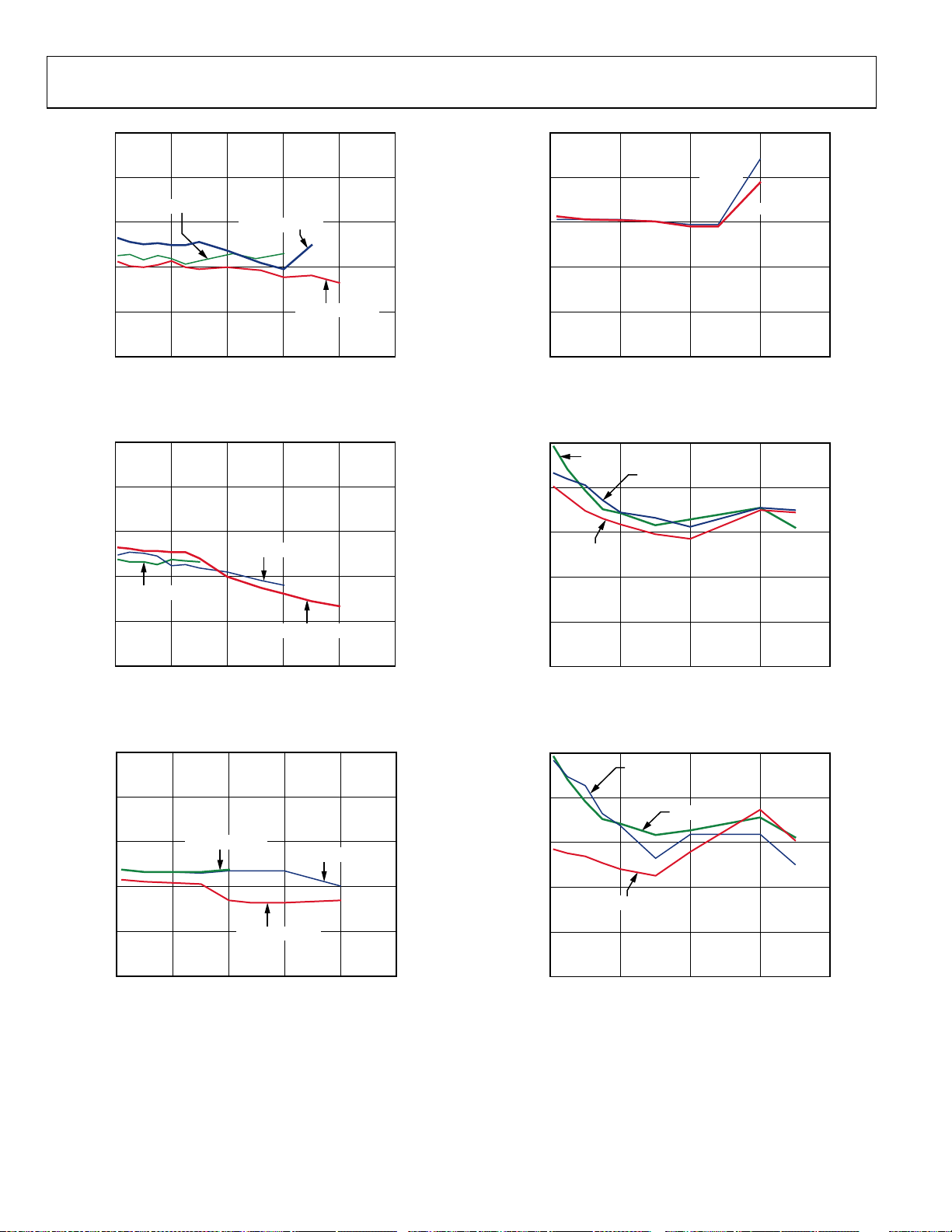

Figure 12. AD9779 Out-of-Band SFDR vs. f

100

90

80

f

= 150MSPS

DATA

70

SFDR (dBc)

f

= 100MSPS

DATA

60

= 200MSPS

f

DATA

OUT

f

= 200MSPS

DATA

= 250MSPS

, 2× Interpolation

100

05361-011

90

80

70

SFDR (dBc)

60

50

04

10 20 30

f

OUT

PLL OFF

(MHz)

PLL ON

0

05361-014

Figure 15. AD9779 In-Band SFDR, 4× Interpolation,

= 100 MSPS, PLL On/Off

f

DATA

100

90

80

70

SFDR (dBc)

60

0dBFS

–3dBFS

–6dBFS

50

0

20 40 60 80

f

OUT

(MHz)

Figure 13. AD9779 Out-of-Band SFDR vs. f

100

90

f

80

70

SFDR (dBc)

60

50

0

10 20 30 40

DATA

= 50MSPS

f

DATA

f

OUT

= 125MSPS

(MHz)

Figure 14. AD9779 Out-of-Band SFDR vs. f

, 4× Interpolation

OUT

f

= 100MSPS

DATA

, 8× Interpolation

OUT

100

50

05361-012

08

20 40 60

f

OUT

(MHz)

0

05361-015

Figure 16. AD9779 In-Band SFDR vs. Digital Full-Scale Input

100

90

80

70

SFDR (dBc)

60

50

05361-013

50

08

10mA

20mA

30mA

20 40 60

f

OUT

(MHz)

0

05361-016

Figure 17. AD9779 In-Band SFDR vs. Output Full-Scale Current

Rev. A | Page 16 of 56

AD9776/AD9778/AD9779

100

f

= 160MSPS

DATA

f

= 200MSPS

(MHz)

DATA

, 1× Interpolation

OUT

90

f

80

IMD (dBc)

70

60

50

0 120

= 250MSPS

DATA

20 40 60 80 100

f

OUT

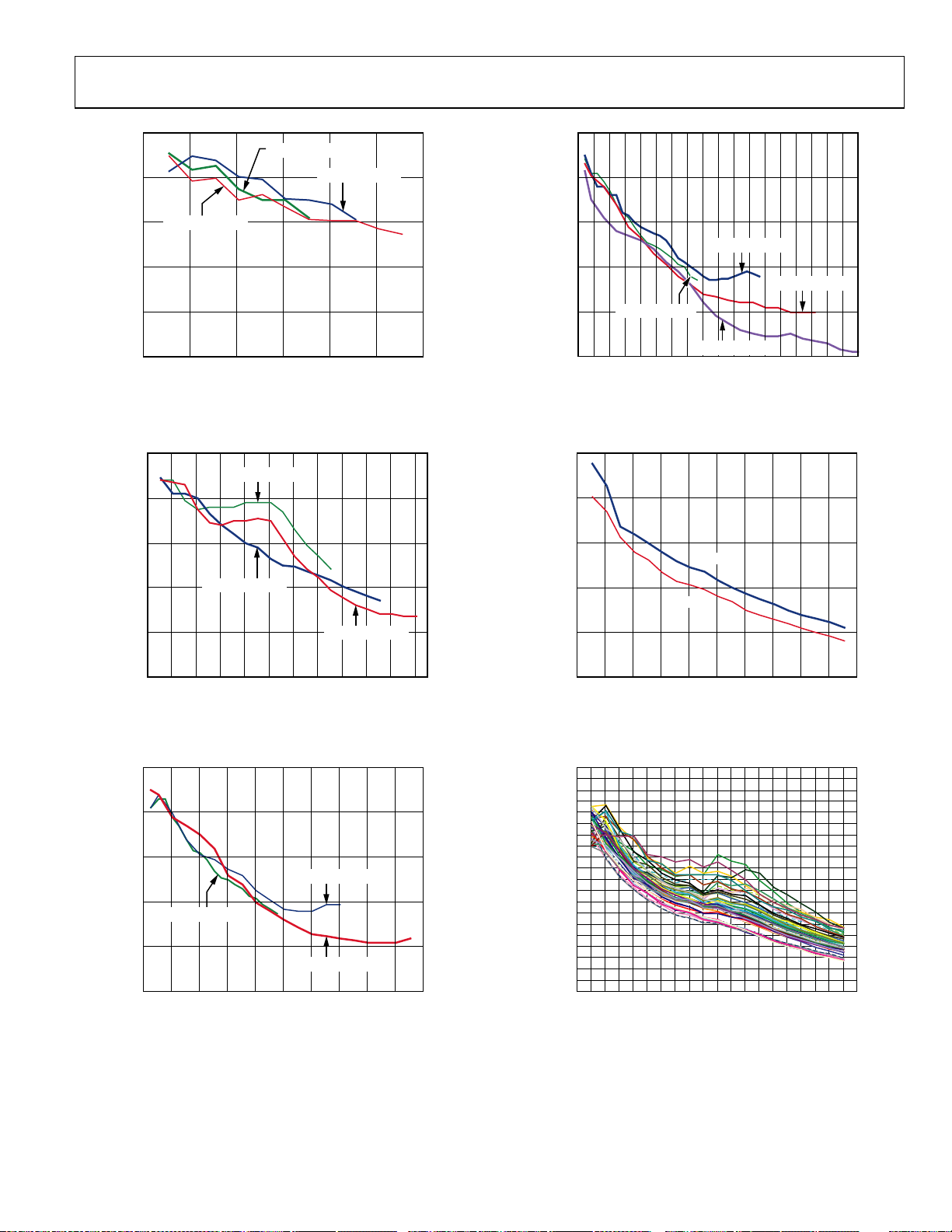

Figure 18. AD9779 Third-Order IMD vs. f

05361-017

100

90

80

f

IMD (dBc)

70

f

50

DATA

75

= 50MSPS

150

125

100

175

f

DATA

f

OUT

200

60

50

0

25

Figure 21. AD9779 Third-Order IMD vs. f

= 75MSPS

DATA

= 125MSPS

250

225

(MHz)

f

= 100MSPS

DATA

350

325

300

275

, 8× Interpolation

OUT

375

400

425

450

05361-020

100

f

= 160MSPS

DATA

90

80

IMD (dBc)

70

60

50

0 20 40 60 80 100 120 140 160 180 200 220

Figure 19. AD9779 Third-Order IMD vs. f

100

90

80

IMD (dBc)

70

60

50

0 400

Figure 20. AD9779 Third-Order IMD vs. f

f

= 200MSPS

DATA

f

= 250MSPS

DATA

f

(MHz)

OUT

, 2× Interpolation

OUT

f

= 150MSPS

DATA

f

= 100MSPS

DATA

f

= 200MSPS

DATA

40 80 120 160 200 240 280 320 360

f

(MHz)

OUT

, 4× Interpolation

OUT

05361-018

05361-019

100

90

80

PLL OFF

IMD (dBc)

70

60

50

0 200

20 40 60 80 120 140 160 180

PLL ON

f

OUT

Figure 22. AD9779 Third-Order IMD vs. f

= 100 MSPS, PLL On vs. PLL Off

f

DATA

100

95

90

85

80

75

IMD (dBc)

70

65

60

55

50

40 80 120 160 200 240 280 320

0 400360

f

OUT

Figure 23. AD9779 Third-Order IMD vs. f

= 200 MSPS

f

DATA

100

(MHz)

, 4× Interpolation,

OUT

(MHz)

, over 50 Parts,4× Interpolation,

OUT

05361-021

05361-022

Rev. A | Page 17 of 56

Loading...

Loading...