Analog Devices AD9776 pra Datasheet

Dual 12-Bit, 1.0 GSPS

D/A Converter

Preliminary Technical Data AD9776

FEATURES

• 1.8/3.3 V Single Supply Operation

• Low power: 560 mW (I

= 20 mA; f

OUTFS

= 1 GSPS, 4×

DAC

Interpolation

• DNL = TBD LSB, INL = TBD LSB

• SFDR = TBD dBc to f

= 100 MHz

OUT

• ACLR = 78 dBc @ 80 MHz IF

• CMOS data interface with Autotracking Input Timing

• Analog Output: Adjustable 10-30mA (RL=25 Ω to 50 Ω)

• 100-lead Exposed Paddle TQFP Package

• Multiple Chip Synchronization Interface

• 84dB Digital Interpolation Filter Stopband Attenuation

• Digital Inverse Sinc Filter

APPLICATIONS

• Wireless Infrastructure

Direct Conversion

Transmit Diversity

• Wideband Communications Systems:

Point-to-Point Wireless, LMDS

PRODUCT DESCRIPTION

The AD9776 is a dual 12-bit high performance, high frequency

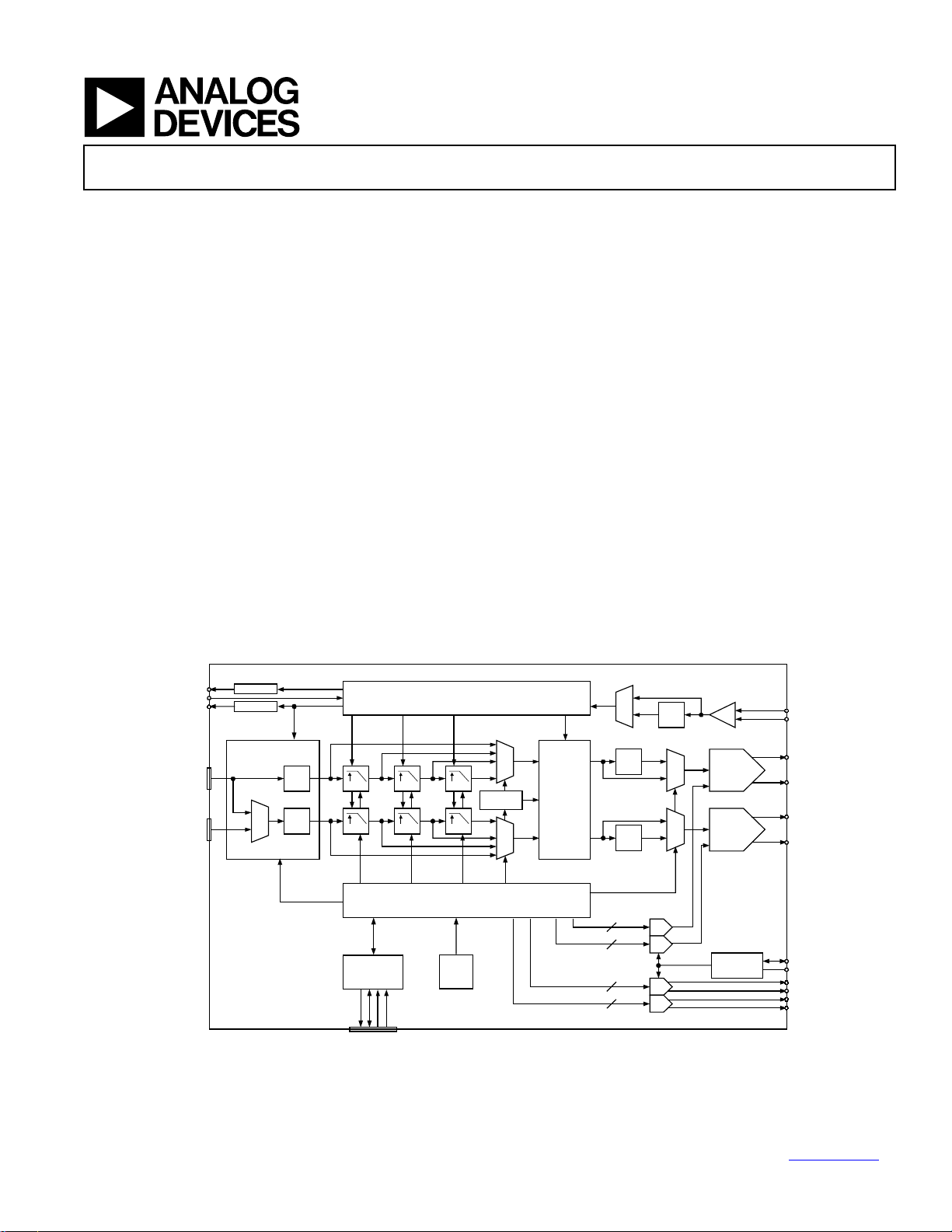

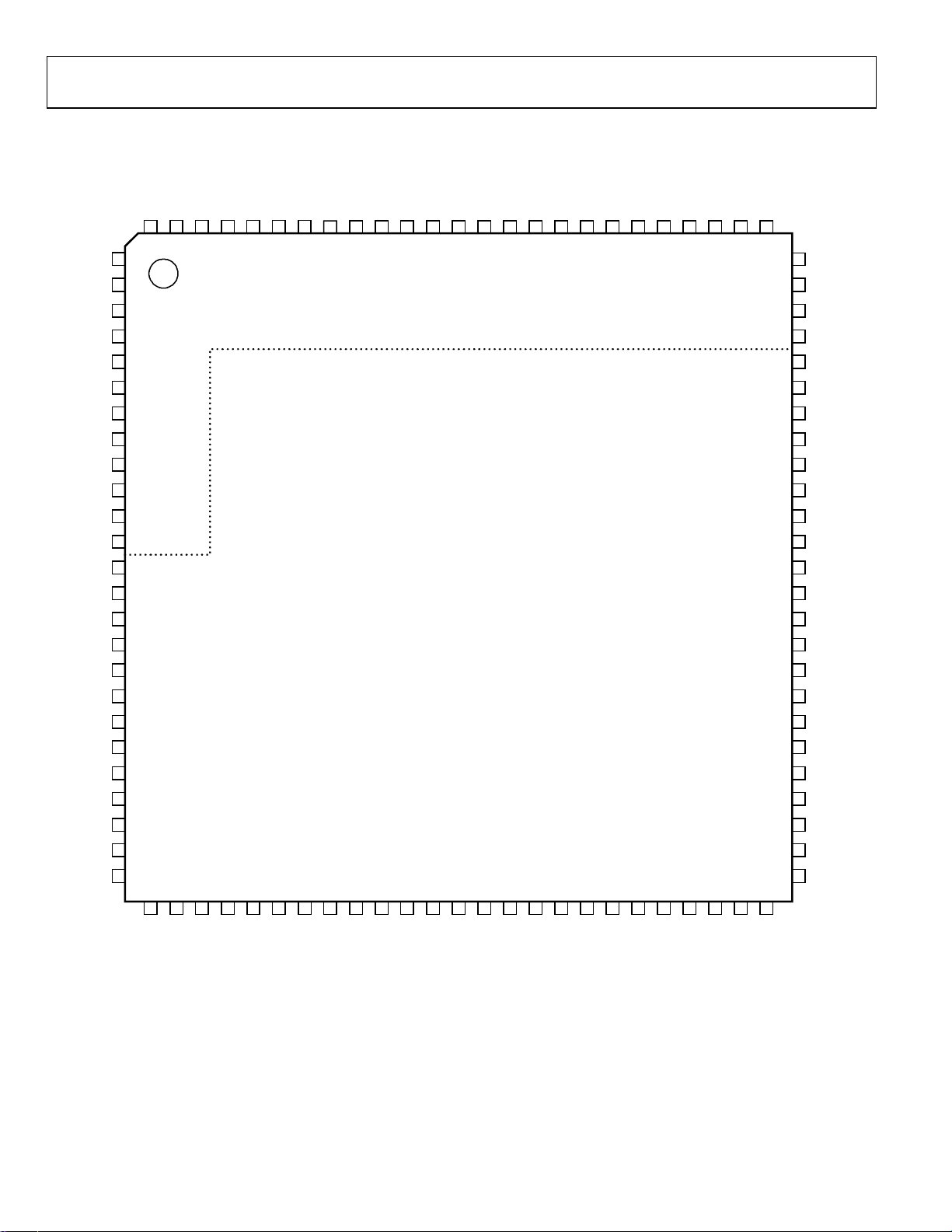

FUNCTIONAL BLOCK DIAGRAM

DAC that provides a sample rate of 1 GSPS, permitting multi

carrier generation up to its Nyquist frequency. It includes features

optimized for direct conversion transmit applications, including

complex digital modulation and gain and offset compensation. The

DAC outputs are optimized to interface seamlessly with analog

quadrature modulators such as the AD8349. A serial peripheral

interface (SPI) provides for programming many internal

parameters and also enables read-back of status registers. The

output current can be programmed over a range of 10mA to 30mA.

The AD9776 is manufactured on an advanced 0.18µm CMOS

process and operates from 1.8V and 3.3V supplies for a total power

consumption of 325mW. It is supplied in a 100-lead QFP package.

PRODUCT HIGHLIGHTS

Ultra-low Noise and Intermodulation Distortion (IMD) enable

high quality synthesis of wideband signals from baseband to high

intermediate frequencies.

Single-ended CMOS interface supports a maximum input rate of

300 MSPS with 1x interpolation.

Manufactured on a CMOS process, the AD9776 uses a proprietary

switching technique that enhances dynamic performance.

The current outputs of the AD9776 can be easily configured for

various single-ended or differential circuit topologies.

SYNC_O

SYNC_I

DATACLK_OUT

P1D[11:0]

P2D[11:0]

Delay Line

Delay Line

Data

Assembler

ILatch

QLatch

Serial

Peripheral

Interface

SDO

SDIO

Clock Generation/Distribution

2X2X

Digital Controller

Power-On

Reset

CSB

SCLK

Figure 1 Functional Block Diagram

Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

Clock

Multiplie r

2X/4X/8X

-1

Sinc

2X2X2X

n*Fdac/8

n = 1, 2, 3… 7

2X

Complex

Modulator

-1

Sinc

10

10

10

10

Gain

Gain

Offset

Offset

16-Bit

IDAC

16-Bit

QDAC

Reference

& Bias

CLK+

CLK-

IOUT1_P

IOUT1_N

IOUT2_P

IOUT2_N

VREF

RSET

AUX1_P

AUX1_N

AUX2_P

AUX2_N

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

AD9776 Preliminary Technical Data

TABLE OF CONTENTS

Specifications............................................................................................3

DC SPECIFICATIONS ......................................................................3

DIGITAL SPECIFICATIONS............................................................4

AC SPECIFICATIONS....................................................................... 4

Pin Function Descriptions .....................................................................5

Pin Configuration....................................................................................6

Interpolation Filter Coefficients............................................................ 7

INTERPOLATION Filter RESPONSE CURVES................................ 8

CHARACTERIZATION DATA ............................................................9

General Description..............................................................................12

Serial Peripheral Interface................................................................12

General Operation of the Serial Interface......................................12

Instruction Byte.................................................................................12

Serial Interface Port Pin Descriptions............................................12

MSB/LSB Transfers ...........................................................................13

Notes on Serial Port Operation.......................................................13

SPI Register Map ...............................................................................14

Internal Reference/Full Scale Current Generation.......................22

Auxiliary DACs..................................................................................22

Power Down and Sleep Modes........................................................22

Internal PLL Clock Multiplier / Clock Distribution.....................23

Timing Information ..........................................................................23

Interpolation Filter Architecture.....................................................25

EvaLuation Board Schematics..............................................................27

REVISION HISTORY

Revision PrA: Initial Version

Rev. PrA | Page 2 of 34

Preliminary Technical Data AD9776

SPECIFICATIONS1

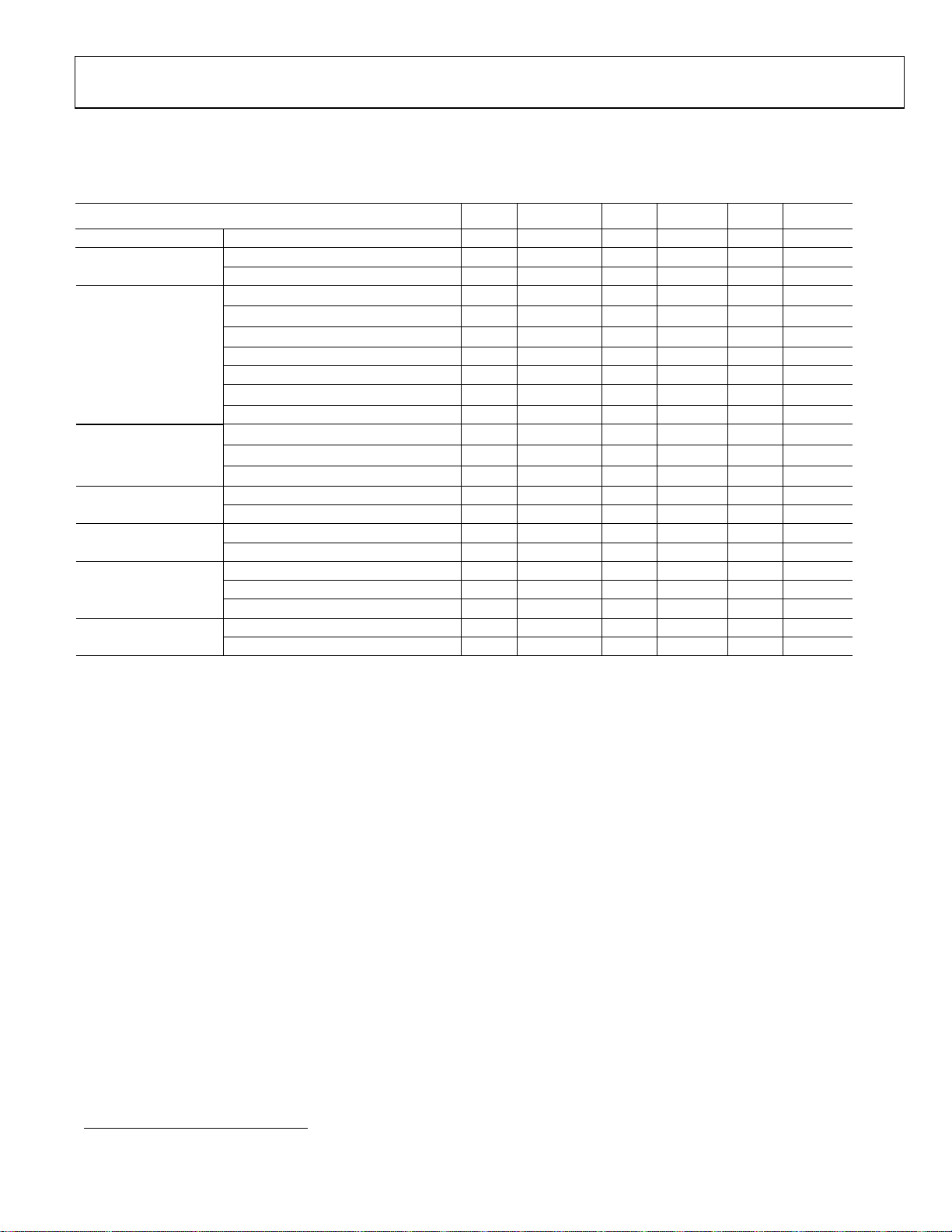

DC SPECIFICATIONS

(VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)

Parameter Temp Test Level Min Typ Max Unit

RESOLUTION 12 Bits

ACCURACY

ANALOG OUTPUTS

TEMPERATURE DRIFT

REFERENCE

ANALOG SUPPLY

VOLTAGES

DIGITAL SUPPLY

VOLTAGES

Integral Nonlinearity (DNL) TBD LSB

Differential Nonlinearity (INL) TBD LSB

Offset Error

Gain Error (With Internal Reference)

Gain Error (Without Internal Reference)

Full Scale Output Current 10 20 30 mA

Output Compliance Range 1.0 V

Output Resistance TBD

Output Capacitance TBD pF

Offset TBD

Gain TBD

Reference Voltage TBD

Internal Reference Voltage 1.2 V

Output Current 100 nA

VDDA33 3.13 3.3 3.47 V

VDDA18 1.70 1.8 1.90 V

VDDD33 3.13 3.3 3.47 V

VDDD18 1.70 1.8 1.90 V

VDDCLK 1.70 1.8 1.90 V

600 MSPS TBD mW POWER CONSUMPTION

Standby Power TBD mW

Table 1: DC Specifications

± TBD

± TBD

± TBD

% FSR

% FSR

% FSR

kΩ

ppm/°C

ppm/°C

ppm/°C

1

Specifications subject to change without notice

Rev. PrA | Page 3 of 34

AD9776 Preliminary Technical Data

DIGITAL SPECIFICATIONS

(VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)

Parameter Temp Test Level Min Typ Max Unit

DAC CLOCK INPUT

(CLK+, CLK-)

SERIAL PERIPHERAL

INTERFACE

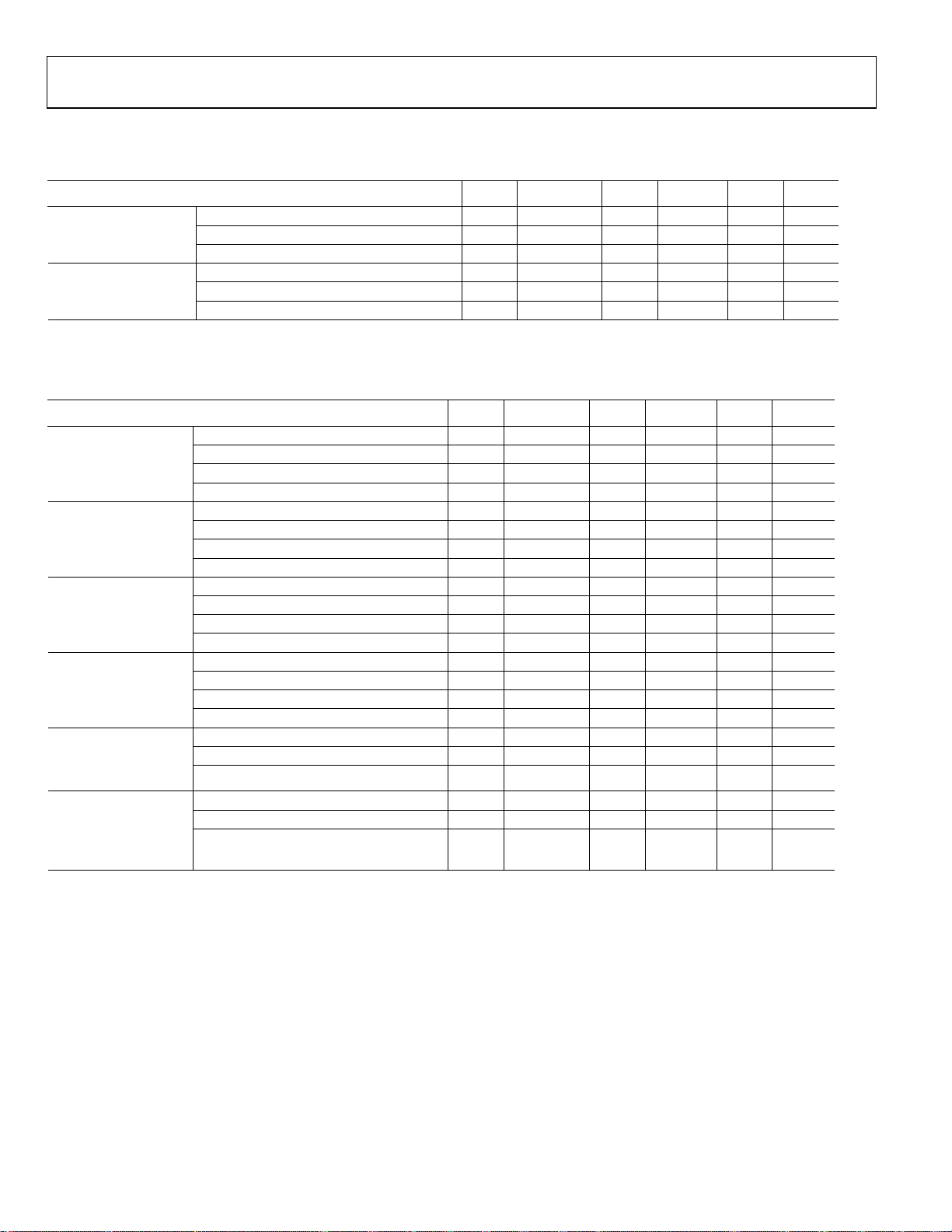

AC SPECIFICATIONS

(VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)

DYNAMIC

PERFORMANCE

SPURIOUS FREE

DYNAMIC RANGE

(SFDR)

TWO-TONE

INTERMODULATION

DISTORTION (IMD)

NOISE SPECTRAL

DENSITY (NSD)

WCDMA ADJACENT

CHANNEL LEAKAGE

RATIO (ACLR), SINGLE

CARRIER

WCDMA SECOND

ADJACENT CHANNEL

LEAKAGE RATIO

(ACLR), SINGLE

CARRIER

Differential peak-to-peak Voltage 800 mV

Common Mode Voltage 400 mV

Maximum Clock Rate 1 GSPS

Maximum Clock Rate (SCLK) 40 MHz

Maximum Pulse width high TBD ns

Maximum pulse width low TBD ns

Table 2: Digital Specifications

Parameter Temp Test Level Min Typ Max Unit

Output Settling Time (tst) (to 0.025%) TBD ns

Output Rise Time (10% to 90%) TBD ns

Output Fall Time (90% to 10%) TBD ns

Output Noise (IoutFS=20mA) TBD pA/rtHz

f

= 100 MSPS, f

DAC

f

= 200 MSPS, f

DAC

f

= 400 MSPS, f

DAC

= 800 MSPS, f

f

DAC

f

= 200 MSPS, f

DAC

f

= 400 MSPS, f

DAC

f

= 400 MSPS, f

DAC

= 800 MSPS, f

f

DAC

f

= 156 MSPS, f

DAC

f

= 200 MSPS, f

DAC

f

= 312 MSPS, f

DAC

= 400 MSPS, f

f

DAC

f

= 245.76 MSPS, f

DAC

f

= 491.52 MSPS, f

DAC

f

= 491.52 MSPS, f

DAC

f

= 245.76 MSPS, f

DAC

f

= 491.52 MSPS, f

DAC

= 491.52 MSPS, f

f

DAC

= 20 MHz 73 dBc

OUT

= 50 MHz 73 dBc

OUT

= 70 MHz 75 dBc

OUT

= 70 MHz 78 dBc

OUT

= 50 MHz 82 dBc

OUT

= 60 MHz 79 dBc

OUT

= 80 MHz 72 dBc

OUT

= 100 MHz 79 dBc

OUT

= 60 MHz -149 dBm/Hz

OUT

= 80 MHz -148 dBm/Hz

OUT

= 100 MHz -150 dBm/Hz

OUT

= 100 MHz -150 dBm/Hz

OUT

= 20 MHz 71 dBc

OUT

= 100 MHz 70 dBc

OUT

= 200 MHz 65 dBc

OUT

= 60 MHz 69 dBc

OUT

= 100 MHz 71 dBc

OUT

= 200 MHz 67 dBc

OUT

Table 3: AC Specifications

Rev. PrA | Page 4 of 34

Preliminary Technical Data AD9776

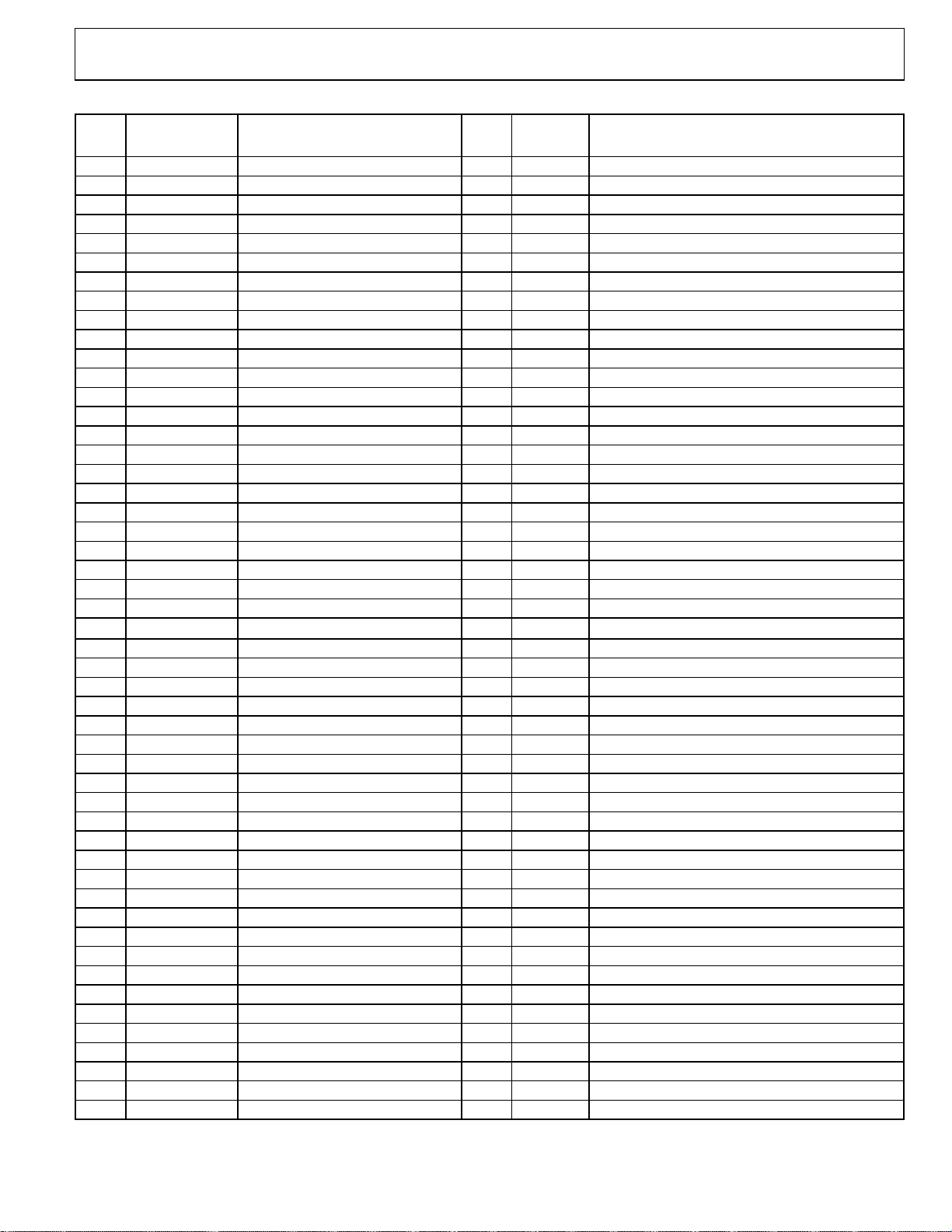

PIN FUNCTION DESCRIPTIONS

Pin

No.

1 VDDC18 1.8 V Clock Supply 51 P2D<6> Port 2 Data Input D6

2 VDDC18 1.8 V Clock Supply 52 P2D<5> Port 2 Data Input D5

3 VSSC Clock Common 53 VDDD18 1.8 V Digital Supply

4 VSSC Clock Common 54 VSSD Digital Common

5 CLK+ Differential Clock Input 55 P1D<4> Port 2 Data Input D4

6 CLK- Differential Clock Input 56 P1D<3> Port 2 Data Input D3

7 VSSC Clock Common 57 P1D<2> Port 2 Data Input D2

8 VSSC Clock Common 58 P1D<1> Port 2 Data Input D1

9 VDDC18 1.8 V Clock Supply 59 P1D<0> Port 2 Data Input D0 (LSB)

10 VDDC18 1.8 V Clock Supply 60 VDDD18 1.8 V Digital Supply

11 VSSC Clock Common 61 VDDD33 3.3 V Digital Supply

12 VSSC Clock Common 62 SYNC_O- Differential Synchronization Output

13 SYNC_I+ Differential Synchronization Input 63 SYNC_O+ Differential Synchronization Output

14 SYNC_I- Differential Synchronization Input 64 VSSD Digital Common

15 VSSD Digital Common 65 PLL_LOCK PLL Lock Indicator

16 VDDD33 3.3 V Digital Supply 66 SPI_SDO SPI Port Data Output

17 P1D<15> Port 1 Data Input D15 (MSB) 67 SPI_SDIO SPI Port Data Input/Output

18 P1D<14> Port 1 Data Input D14 68 SPI_CLK SPI Port Clock

19 P1D<13> Port 1 Data Input D13 69 SPI_CSB SPI Port Chip Select Bar

20 P1D<12> Port 1 Data Input D12 70 RESET Reset

21 P1D<11> Port 1 Data Input D11 71 IRQ Interrupt Request

22 VSSD Digital Common 72 VSS Analog Common

23 VDDD18 1.8 V Digital Supply 73 IPTAT Reference Current

24 P1D<10> Port 1 Data Input D10 74 VREF Voltage Reference Output

25 P1D<9> Port 1 Data Input D9 75 I120

26 P1D<8> Port 1 Data Input D8 76 VDDA33 3.3 V Analog Supply

27 P1D<7> Port 1 Data Input D7 77 VSSA Analog Common

28 P1D<6> Port 1 Data Input D6 78 VDDA33 3.3 V Analog Supply

29 P1D<5> Port 1 Data Input D5 79 VSSA Analog Common

30 P1D<4> Port 1 Data Input D4 80 VDDA33 3.3 V Analog Supply

31 P1D<3> Port 1 Data Input D3 81 VSSA Analog Common

32 VSSD Digital Common 82 VSSA Analog Common

33 VDDD18 1.8 V Digital Supply 83 IOUT2_P Differential DAC Current Output, Channel 2

34 P1D<2> Port 1 Data Input D2 84 IOUT2_N Differential DAC Current Output, Channel 2

35 P1D<1> Port 1 Data Input D1 85 VSSA Analog Common

36 P1D<0> Port 1 Data Input D0 (LSB) 86 AUX2_P Auxiliary DAC Voltage Output, Channel 2

37 DATACLK_OUT Data Clock Output 87 AUX2_N Auxiliary DAC Voltage Output, Channel 2

38 VDDD33 3.3 V Digital Supply 88 VSSA Analog Common

39 TXENABLE Transmit Enable 89 AUX1_N Auxiliary DAC Voltage Output, Channel 1

40 P2D<15> Port 2 Data Input D15 (MSB) 90 AUX1_P Auxiliary DAC Voltage Output, Channel 1

41 P2D<14> Port 2 Data Input D14 91 VSSA Analog Common

42 P2D<13> Port 2 Data Input D13 92 IOUT1_N Differential DAC Current Output, Channel 1

43 VDDD18 1.8 V Digital Supply 93 IOUT1_P Differential DAC Current Output, Channel 1

44 VSSD Digital Common 94 VSSA Analog Common

45 P2D<12> Port 2 Data Input D12 95 VSSA Analog Common

46 P2D<11> Port 2 Data Input D11 96 VDDA33 3.3 V Analog Supply

47 P2D<10> Port 2 Data Input D10 97 VSSA Analog Common

48 P2D<9> Port 2 Data Input D9 98 VDDA33 3.3 V Analog Supply

49 P2D<8> Port 2 Data Input D8 99 VSSA Analog Common

50 P2D<7> Port 2 Data Input D7 100 VDDA33 3.3 V Analog Supply

Name Description Pin

Name Description

No.

120 µA Reference Current

Table 4: Pin Function Descriptions

Rev. PrA | Page 5 of 34

AD9776 Preliminary Technical Data

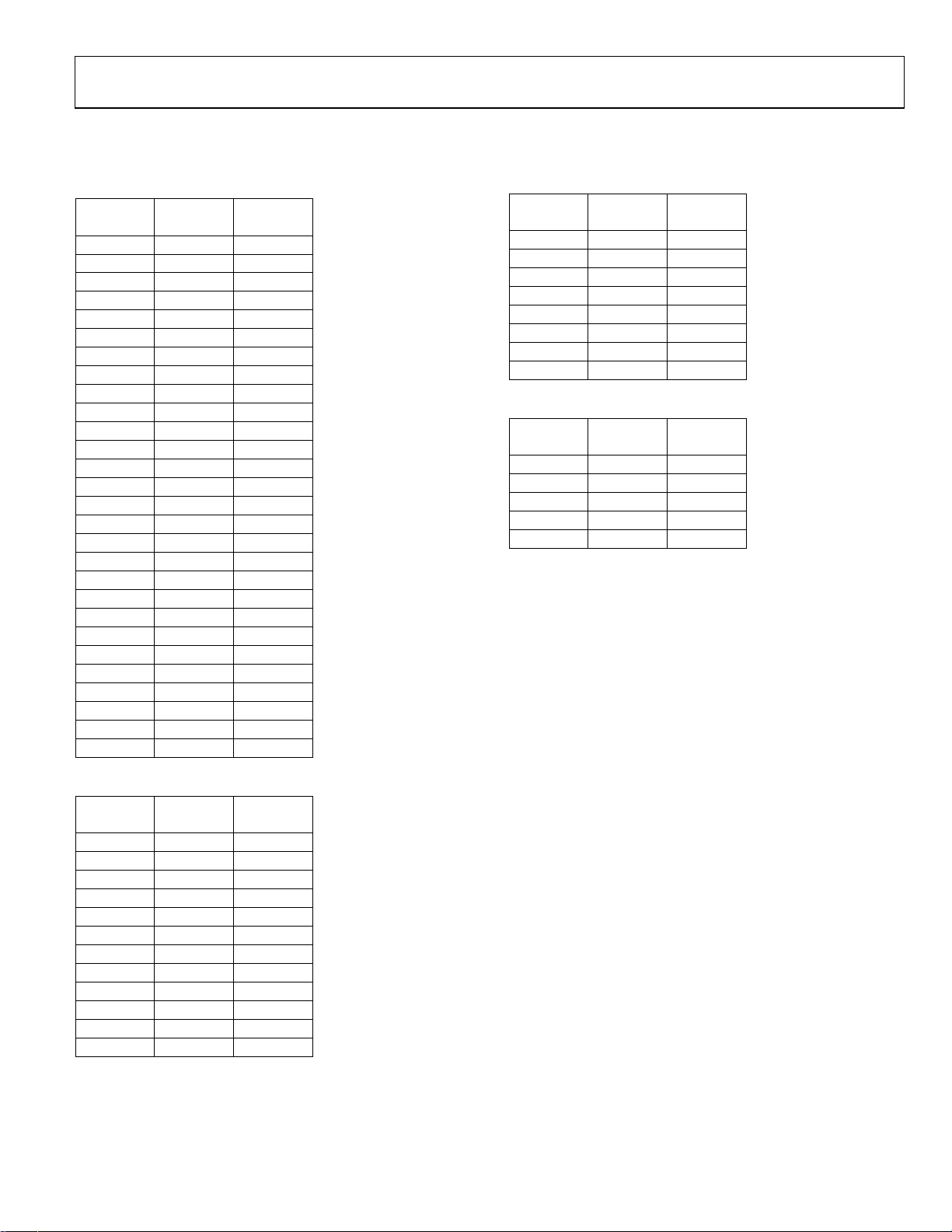

PIN CONFIGURATION

VDDC18

VDDC18

VSSC

VSSC

CLK+

CLKVSSC

VSSC

VDDC18

VDDC18

VSSC

VSSC

SYNC_I+

SYNC_I-

VSSD

VDDD33

P1D<11>

P1D<10>

P1D<9>

P1D<8>

P1D<7>

VSSD

VDDD18

P1D<6>

P1D<5>

VSSA

VDDA33

99

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

VDDA33

989697

VSSA

VDDA33

VSSA

95

VSSA

949293

IOUT1_P

VSSA

IOUT1_N

AUX1_P

90

91

AD9776

VSSA

AUX1_N

898788

AUX2_N

Analog Domain

Digital Domain

VSSA

AUX2_P

85

86

IOUT2_N

848283

IOUT2_P

VSSA

VSSA

81

VDDA33

80

VSSA

79

VDDA33

78

VSSA

77

VDDA33

76

75

74

73

72

71

70

69

SPI_CSB

68

67

66

SPI_SDO

65

PLL_LOCK

64

63

SYNC_O+

62

61

60

59

58

57

56

55

54

53

52

51

I120

VREF

IPTAT

VSS

IRQ

RESET

SPI_CLK

SPI_SDI

VSSD

SYNC_OVDDD33

VDDD18

NC

NC

NC

NC

P2D<0>

VSSD

VDDD18

P2D<1>

P2D<2>

26

P1D<4>

27

28

30

29

32

31

NC

P1D<3>

P1D<2>

P1D<1>

P1D<0>

VSSD

34

33

NC

VDDD18

35

NC

36

NC

37

DCLK

39

38

VDDD33

40

P2D<11>

TXEnable

41

P2D<10>

42

P2D <9 >

444645

VSSD

VDDD18

P2D<7 >

P2D<8 >

48

47

P2D<6 >

P2D<5>

43

49

P2D<4>

50

P2D<3>

Figure 2. Pin Configuration

Rev. PrA | Page 6 of 34

Preliminary Technical Data AD9776

INTERPOLATION FILTER COEFFICIENTS

Table 5: Halfband Filter 1

Lower

Coefficient

H(1) H(55) -4

H(2) H(54) 0

H(3) H(53) 13

H(4) H(52) 0

H(5) H(51) -34

H(6) H(50) 0

H(7) H(49) 72

H(8) H(48) 0

H(9) H(47) -138

H(10) H(46) 0

H(11) H(45) 245

H(12) H(44) 0

H(13) H(43) -408

H(14) H(42) 0

H(15) H(41) 650

H(16) H(40) 0

H(17) H(39) -1003

H(18) H(38) 0

H(19) H(37) 1521

H(20) H(36) 0

H(21) H(35) -2315

H(22) H(34) 0

H(23) H(33) 3671

H(24) H(32) 0

H(25) H(31) -6642

H(26) H(30) 0

H(27) H(29) 20755

H(28) 32768

Table 6: Halfband Filter 2

Lower

Coefficient

H(1) H(23) -2

H(2) H(22) 0

H(3) H(21) 17

H(4) H(20) 0

H(5) H(19) -75

H(6) H(18) 0

H(7) H(17) 238

H(8) H(16) 0

H(9) H(15) -660

H(10) H(14) 0

H(11) H(13) 2530

H(12) 4096

Upper

Coefficient

Upper

Coefficient

Integer

Va l ue

Integer

Va l ue

Table 7: Halfband Filter 3

Lower

Coefficient

H(1) H(15) -39

H(2) H(14) 0

H(3) H(13) 273

H(4) H(12) 0

H(5) H(11) -1102

H(6) H(10) 0

H(7) H(9) 4964

H(8) 8192

Table 8: Inverse Sinc Filter

Lower

Coefficient

H(1) H(9) 2

H(2) H(8) -4

H(3) H(7) 10

H(4) H(6) -35

H(5) 401

Upper

Coefficient

Upper

Coefficient

Integer

Va l ue

Integer

Va l ue

Rev. PrA | Page 7 of 34

AD9776 Preliminary Technical Data

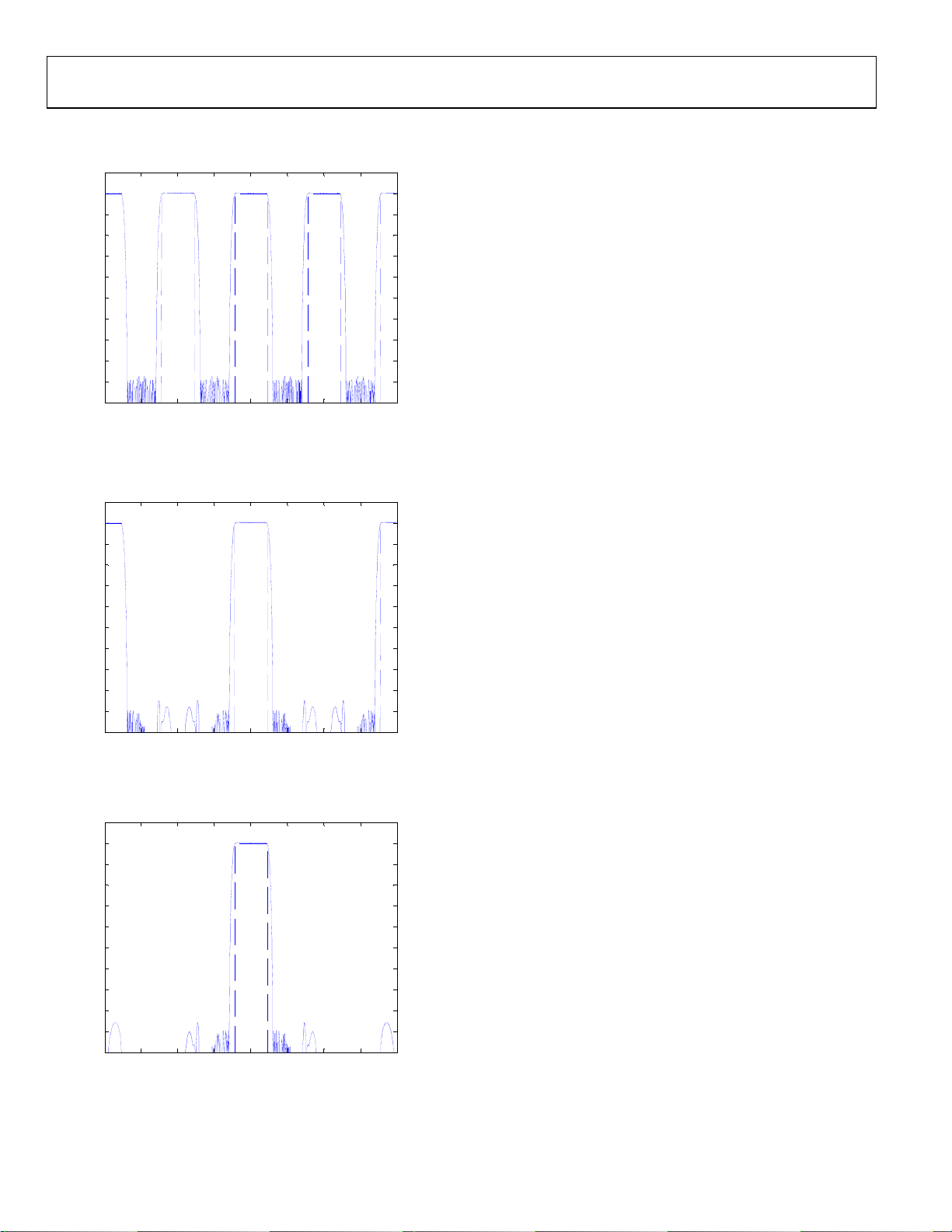

INTERPOLATION FILTER RESPONSE CURVES

10

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-4 -3 -2 -1 0 1 2 3 4

Figure 3. AD9776 2x Interpolation, Low Pass Response to

±4x Input Data Rate (Dotted Lines Indicate 1dBRoll-Off )

10

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-4 -3 -2 -1 0 1 2 3 4

Figure 4. AD9776 4x Interpolation, Low Pass Response to

±4x Input Data Rate (Dotted Lines Indicate 1dBRoll-Off )

10

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-4 -3 -2 -1 0 1 2 3 4

Figure 5.AD9776 8x Interpolation, Low Pass Response to

±4x Input Data Rate (Dotted Lines Indicate 1dBRoll-Off )

Rev. PrA | Page 8 of 34

Preliminary Technical Data AD9776

CHARACTERIZATION DATA

TBD

Figure 6. AD9776 Typical INL

TBD

Figure 7. AD9776 Typical DNL

TBD

Figure 9. SFDR vs . F

, 2x Interpolation

OUT

TBD

Figure 10. SFDR vs. F

, 4x Interpolation

OUT

TBD

Figure 8. SFDR vs . F

, 1x Interpolation

OUT

Rev. PrA | Page 9 of 34

TBD

Figure 11. SFDR vs. F

, 8x Interpolation

OUT

AD9776 Preliminary Technical Data

TBD

Figure 12. Third Order IMD vs. F

TBD

Figure 13. Third Order IMD vs. F

, 1x Interpolation

OUT

, 2x Interpolation

OUT

TBD

Figure 15. Third Order IMD vs. F

, 8x Interpolation

OUT

TBD

Figure 16. Noise Spectral Density vs. F

, 1x Interpolation

OUT

TBD

Figure 14. Third Order IMD vs. F

, 4x Interpolation

OUT

Rev. PrA | Page 10 of 34

TBD

Figure 17. Noise Spectral Density vs. F

, 2x Interpolation

OUT

Preliminary Technical Data AD9776

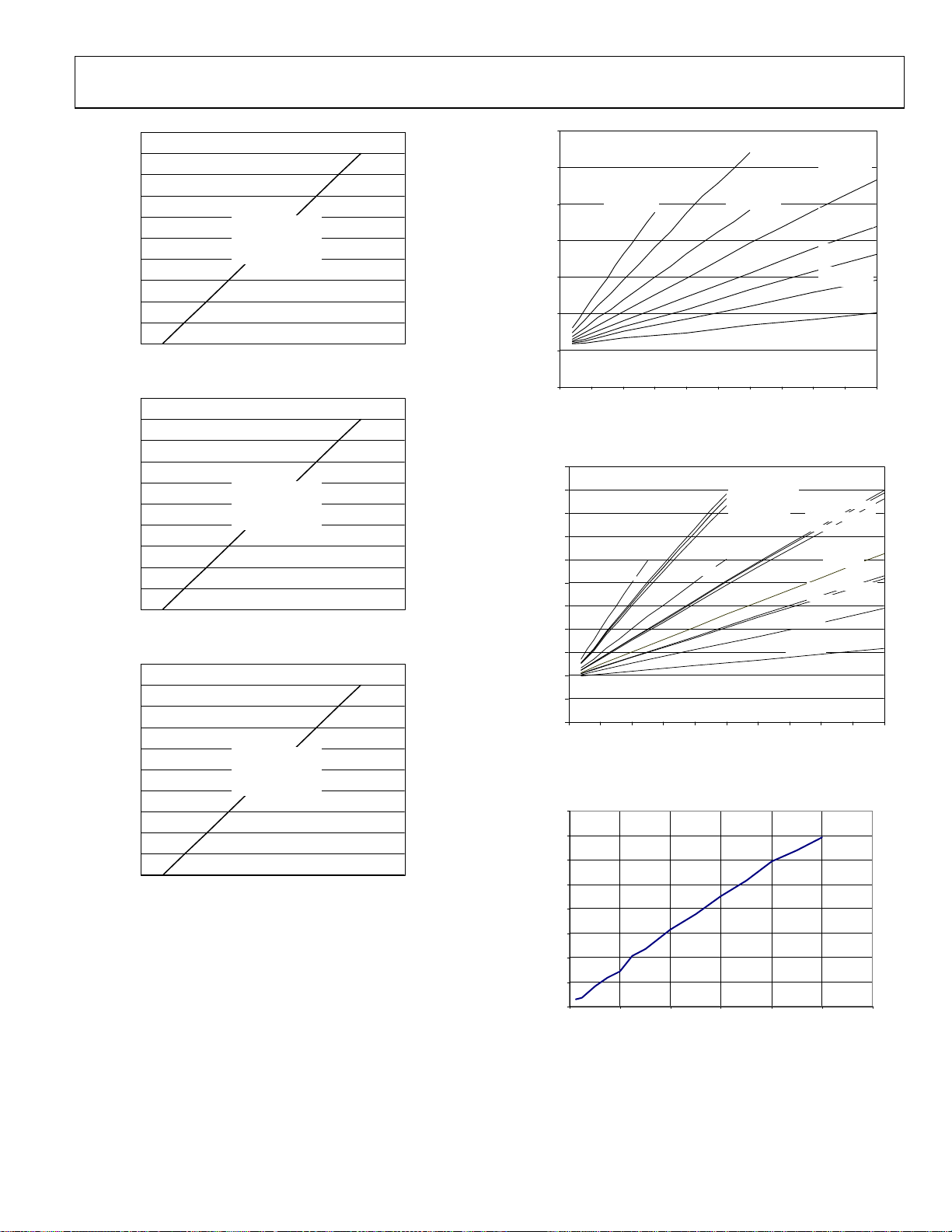

TBD

0.7

0.6

0.5

0.4

Power - W

0.3

0.2

8x Interpolation,

Zero S tuf fi ng

8x Interpolation

4x Interpolation,

Zero S t uff ing

4x Interpolation

2x Interpolation,

Zero S tuffing

2x Interpolation

1x Interpolation,

Zero S tuffing

1x Interpolation

Figure 18. ACLR for 1

st

Adjacent Band WCDMA, 4x Interpolation. On-Chip

Modulation is used to translate baseband signal to IF.

TBD

Figure 19. ACLR for 2nd Adjacent Band WCDMA, 4x Interpolation. On-Chip

Modulation is used to translate baseband signal to IF.

TBD

0.1

0

0 25 50 75 100 125 150 175 200 225 250

F

(MSPS)

DATA

Figure 21. Power Dissipation, Single DAC Mode

1.1

1

0.9

0.8

0.7

0.6

8x Interp olation,

Zero Stuffing

4x Interpolation,

Zero S tuffing

0.5

Power - W

0.4

0.3

0.2

0.1

0

0 25 50 75 100 125 150 175 200 225 250

F

DATA

8x Interpolation,F

8x Interpolation,F

8x Interpolation,F

8x Interpolation,Modulation off

(MSPS)

/4 Modulation

DAC

/2 Modulation

DAC

/8 Modulation

DAC

4x Interpolation,F

4x Interpolation,F

4x Interpolation,Modulation off

2x Interpol ation,F

2x Interpol ation,Modulation off

1x Interp o lation,

Zero S tuffing

1x Interpolation

2x Interpolation,

Zero Stuffing

Figure 22. Power Dissipation, Dual DAC Mode

/4 Mod ulatio n

DAC

/2 Mod ulatio n

DAC

/2 Modulation

DAC

Figure 20. ACLR for 3rd Adjacent Band WCDMA, 4x Interpolation. On-Chip

Modulation is used to translate baseband signal to IF.

Rev. PrA | Page 11 of 34

0.16

0.14

0.12

0.1

0.08

Power - W

0.06

0.04

0.02

0

0 200 400 600 800 1000 1200

F

- MSPS

DAC

Figure 23. Power Dissipation of Inverse Sinc Filter

Loading...

Loading...