REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

AD976/AD976A

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

16-Bit, 100 kSPS/200 kSPS

BiCMOS A/D Converters

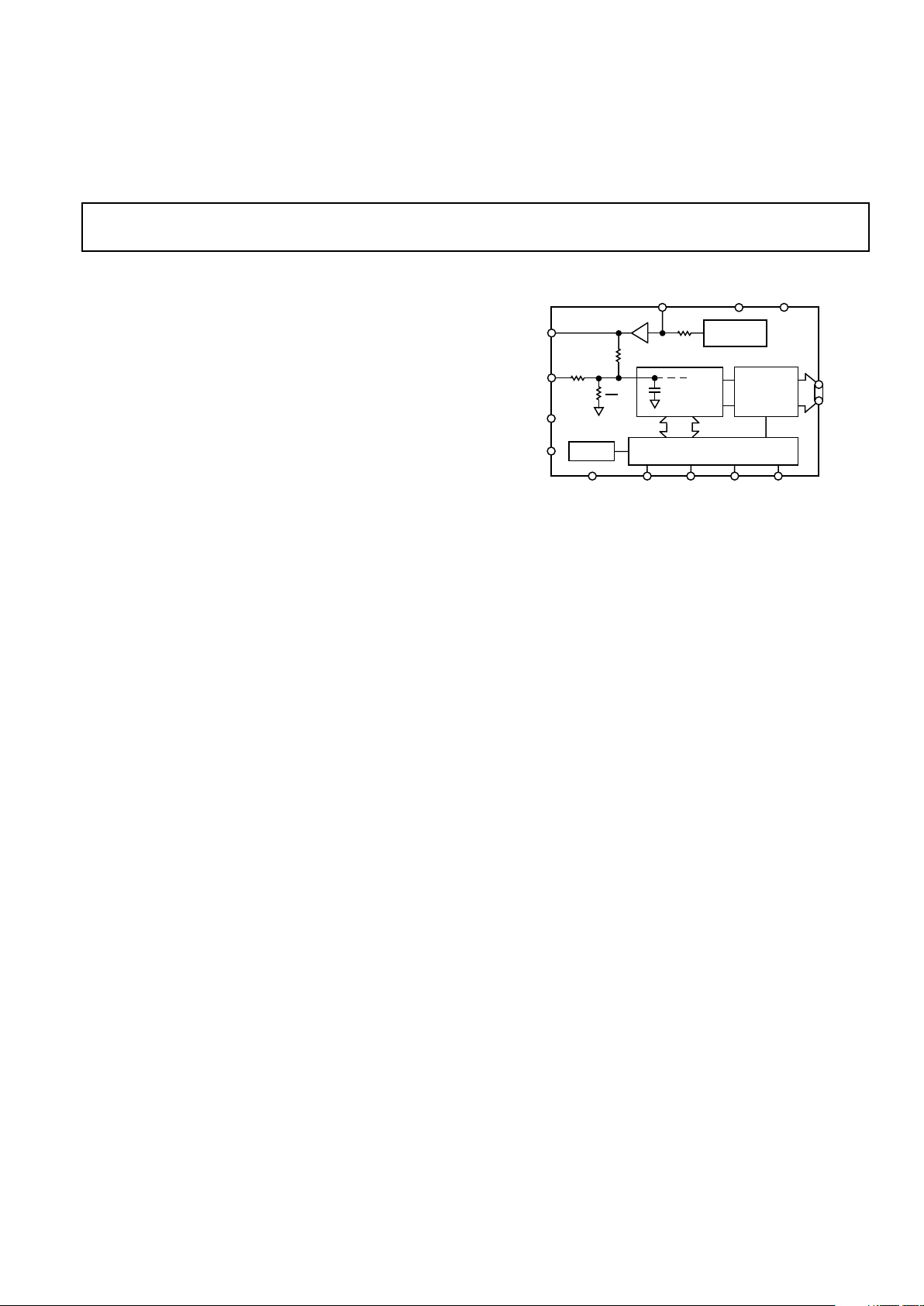

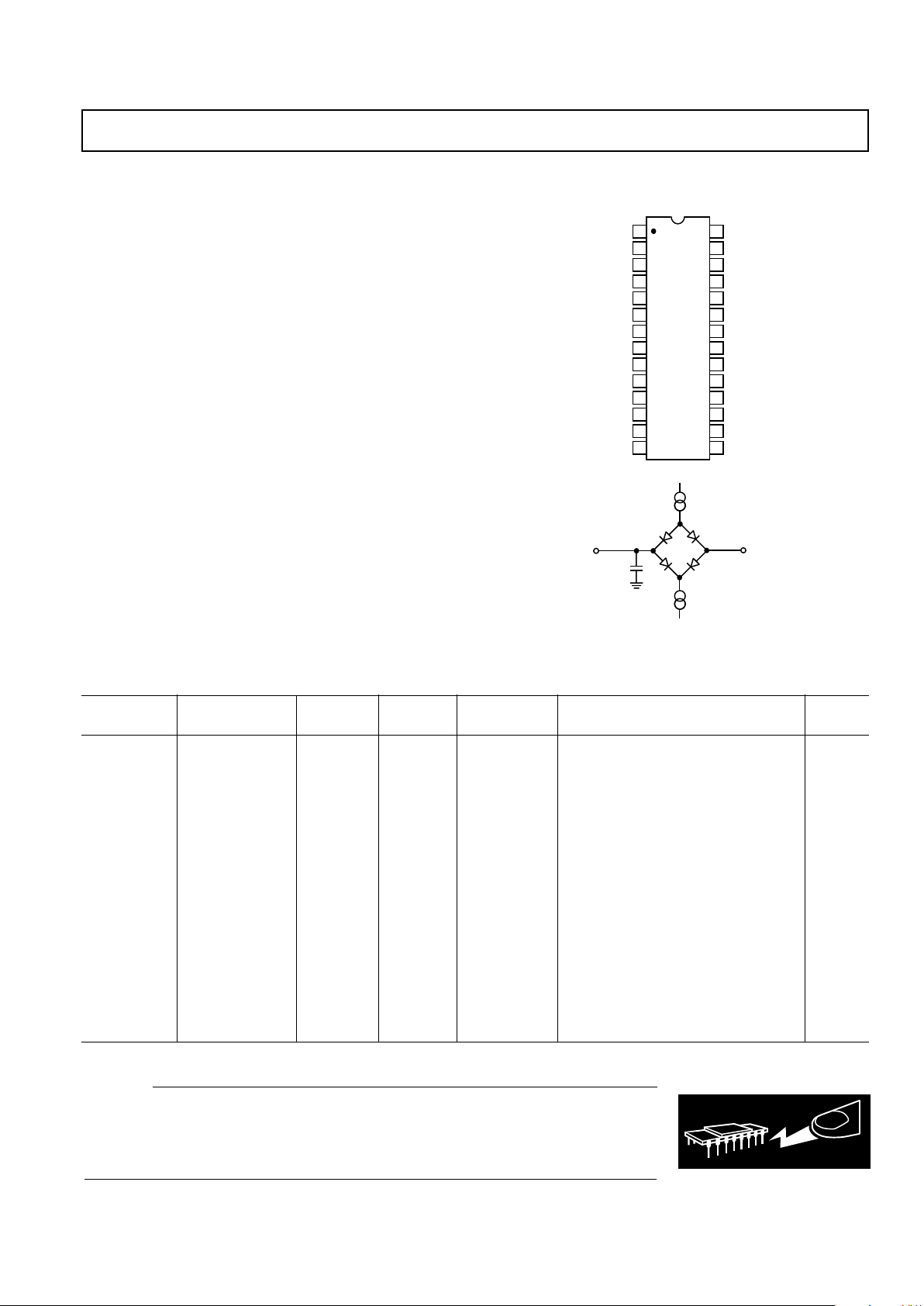

FUNCTIONAL BLOCK DIAGRAM

REF

V

ANA

4kV

R

D15

D0

DGND

BYTE

R/C

CS BUSY

V

DIG

V

IN

AGND2

CAP

AGND1

2.5V

REFERENCE

4R

CONTROL LOGIC &

INTERNAL CALIBRATION CIRCUITRY

CLOCK

PARALLEL

INTERFACE

SWITCHED

CAP ADC

AD976/AD976A

4R

3

R = 6kV AD976

R = 3kV AD976A

FEATURES

Fast 16-Bit ADC

200 kSPS Throughput – AD976A

100 kSPS Throughput – AD976

Single 5 V Supply Operation

Input Range: ⴞ10 V

100 mW Max Power Dissipation

Choice of External or Internal 2.5 V Reference

High Speed Parallel Interface

On-Chip Clock

28-Lead Skinny DIP, SSOP or SOIC Packages

GENERAL DESCRIPTION

The AD976/AD976A is a high speed, low power 16-bit A/D

converter that operates from a single 5 V supply. The part contains a successive approximation, switched capacitor ADC, an

internal 2.5 V reference and a high speed parallel interface. The

ADC is factory calibrated to minimize all linearity errors. The

analog full-scale input is the standard industrial range of ±10 V.

The AD976/AD976A is comprehensively tested for ac parameters such as SNR and THD, as well as the more traditional

parameters of offset, gain and linearity.

The AD976/AD976A is fabricated on Analog Devices’ proprietary BiCMOS process, which has high performance bipolar

devices along with CMOS transistors.

The AD976/AD976A is available in skinny 28-lead DIP, SSOP

and SOIC packages.

PRODUCT HIGHLIGHTS

1. Fast Throughput.

The AD976/AD976A is a high speed (100 kSPS/200 kSPS

throughput rates respectively), 16-bit ADC based on a

switched capacitor architecture.

2. Single-Supply Operation.

The AD976/AD976A operates from a single 5 V supply and

dissipates only 100 mW max.

3. Comprehensive DC and AC Specifications.

The AD976/AD976A is factory calibrated and fully tested for

SNR and THD as well as the traditional specifications of

offset, gain and linearity.

4. Complete A/D Solution.

The AD976/AD976A offers a highly integrated solution

containing an accurate ADC, reference and on-chip clock.

AD976/AD976A

–2–

REV. C

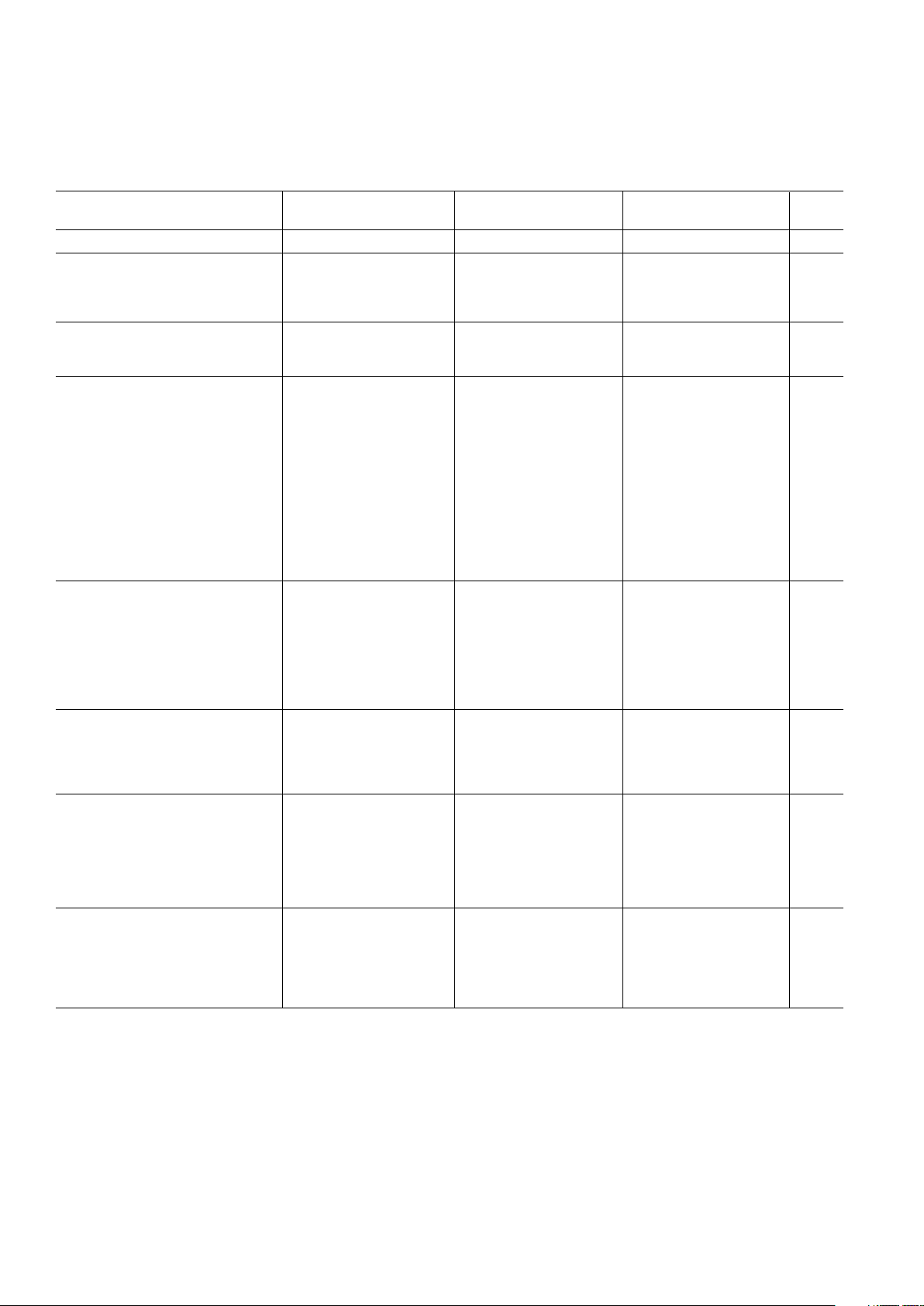

AD976A–SPECIFICATIONS

AD976AA AD976AB AD976AC

Parameter Min Typ Max Min Typ Max Min Typ Max Units

RESOLUTION 16 16 16 Bits

ANALOG INPUT

Voltage Range ±10 ±10 ±10 V

Impedance 13 13 13 kΩ

Capacitance 22 22 22 pF

THROUGHPUT SPEED

Complete Cycle 5 5 5 µs

Throughput Rate 200 200 200 kHz

DC ACCURACY

Integral Linearity Error ±3 ±2 ±3 LSB

1

Differential Linearity Error –2 +3 –1 +1.75 ±2 LSB

No Missing Codes 15 16 15 Bit

Transition Noise

2

1.0 1.0 1.0 LSB

Full-Scale Error

3, 4

±0.5 ±0.25 ±0.5 %

Full-Scale Error Drift ±7 ±7 ±7 ppm/°C

Full-Scale Error, Ext. REF = 2.5 V ±0.5 ±0.25 ±0.5 %

Full-Scale Error Drift, Ext. REF = 2.5 V ±2 ±2 ±2 ppm/°C

Bipolar Zero Error

4

±10 ±10 ±15 mV

Bipolar Zero Error Drift ±2 ±2 ±2 ppm/°C

Power Supply Sensitivity

V

ANA

= V

DIG

= V

D

= 5 V ± 5% ±8 ±8 ±8 LSB

AC ACCURACY

Spurious Free Dynamic Range

5

90 96 90 dB

6

Total Harmonic Distortion

5

–90 –96 –90 dB

Signal to (Noise + Distortion)

5

83 85 83 dB

–60 dB Input 27 28 27 dB

Signal to Noise

5

83 85 83 dB

Full-Power Bandwidth

7

1 1 1 MHz

Input Bandwidth 2.7 2.7 2.7 MHz

SAMPLING DYNAMICS

Aperture Delay 40 40 40 ns

Transient Response

Full-Scale Step 1 1 1 µs

Overvoltage Recovery

8

150 150 150 ns

REFERENCE

Internal Reference Voltage 2.48 2.5 2.52 2.48 2.5 2.52 2.48 2.5 2.52 V

Internal Reference Source Current 1 1 1 µA

External Reference Voltage Range

for Specified Linearity 2.3 2.5 2.7 2.3 2.5 2.7 2.3 2.5 2.7 V

External Reference Current Drain

Ext. REF = 2.5 V 100 100 100 µA

DIGITAL INPUTS

Logic Levels

V

IL

–0.3 +0.8 –0.3 +0.8 –0.3 +0.8 V

V

IH

+2.0 V

DIG

+ 0.3 +2.0 V

DIG

+ 0.3 +2.0 V

DIG

+ 0.3 V

I

IL

±10 ±10 ±10 µA

I

IH

±10 ±10 ±10 µA

NOTES

1

LSB means least significant bit. With a ±10 V input, one LSB is 305 µV.

2

Typical rms noise at worst case transitions and temperatures.

3

Measured with fixed resistors as shown in Figure 5 (AD976) and Figure 6 (AD976A). Adjustable to zero as shown in Figure 7.

4

Full-scale error is expressed as the % difference between the actual full-scale code transition voltage and the ideal full-scale transition voltage and includes the effect

of offset error. The full-scale error is the worst case of either the –full-scale or +full-scale code transition voltage errors.

5

fIN = 20 kHz (AD976) and fIN = 45 kHz (AD976A), 0.5 dB down, unless otherwise noted.

6

All specifications in dB are referred to a full scale ±10 V input.

7

Full-power bandwidth is defined as full-scale input frequency at which signal-to-(noise + distortion) degrades to 60 dB or 10 bits of accuracy.

8

Recovers to specified performance after a 2 × F

S

input overvoltage.

Specifications subject to change without notice.

(–40ⴗC to +85ⴗC, FS = 200 kHz, Ref = Internal Reference, V

DIG

= V

ANA

= +5 V unless

otherwise noted)

–3–

REV. C

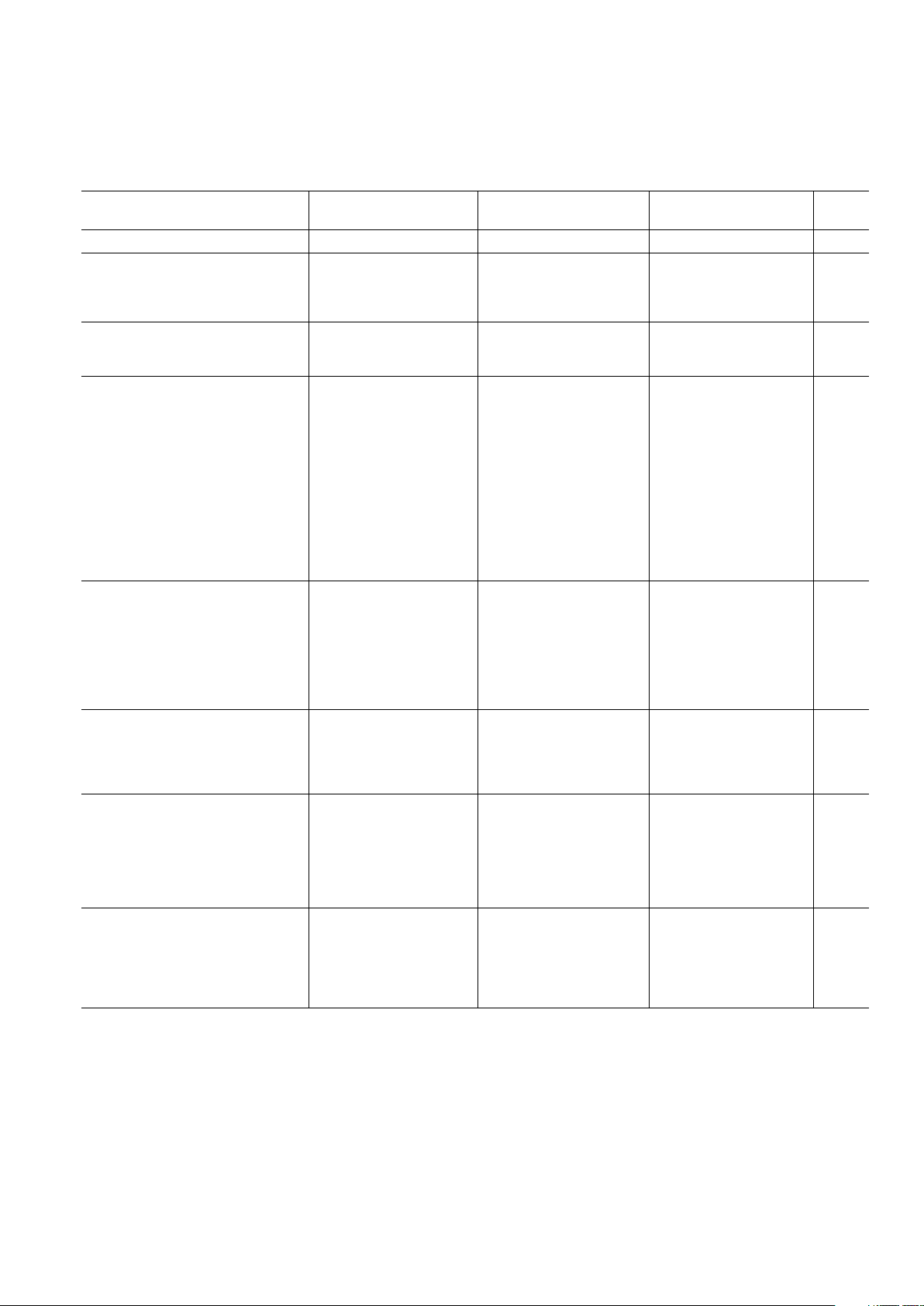

AD976/AD976A

AD976–SPECIFICATIONS

AD976A AD976B AD976C

Parameter Min Typ Max Min Typ Max Min Typ Max Units

RESOLUTION 16 16 16 Bits

ANALOG INPUT

Voltage Range ±10 ±10 ±10 V

Impedance 23 23 23 kΩ

Capacitance 22 22 22 pF

THROUGHPUT SPEED

Complete Cycle 10 10 10 µs

Throughput Rate 100 100 100 kHz

DC ACCURACY

Integral Linearity Error ±3 ±2 ±3 LSB

1

Differential Linearity Error –2 +3 –1 +1.75 ±2 LSB

No Missing Codes 15 16 15 Bit

Transition Noise

2

1.0 1.0 1.0 LSB

Full-Scale Error

3, 4

±0.5 ±0.25 ±0.5 %

Full-Scale Error Drift ±7 ±7 ±7 ppm/°C

Full-Scale Error, Ext. REF = 2.5 V ±0.5 ±0.25 ±0.5 %

Full-Scale Error Drift, Ext. REF = 2.5 V ±2 ±2 ±2 ppm/°C

Bipolar Zero Error

4

±10 ±10 ±15 mV

Bipolar Zero Error Drift ±2 ±2 ±2 ppm/°C

Power Supply Sensitivity

V

ANA

= V

DIG

= V

D

= 5 V ± 5% ±8 ±8 ±8 LSB

AC ACCURACY

Spurious Free Dynamic Range

5

90 96 90 dB

6

Total Harmonic Distortion

5

–90 –96 –90 dB

Signal to (Noise + Distortion)

5

83 85 83 dB

–60 dB Input 27 28 27 dB

Signal to Noise

5

83 85 83 dB

Full-Power Bandwidth

7

700 700 700 kHz

Input Bandwidth 1.5 1.5 1.5 MHz

SAMPLING DYNAMICS

Aperture Delay 40 40 40 ns

Transient Response

Full-Scale Step 2 2 2 µs

Overvoltage Recovery

8

150 150 150 ns

REFERENCE

Internal Reference Voltage 2.48 2.5 2.52 2.48 2.5 2.52 2.48 2.5 2.52 V

Internal Reference Source Current 1 1 1 µA

External Reference Voltage Range

for Specified Linearity 2.3 2.5 2.7 2.3 2.5 2.7 2.3 2.5 2.7 V

External Reference Current Drain

Ext. REF = 2.5 V 100 100 100 µA

DIGITAL INPUTS

Logic Levels

V

IL

–0.3 +0.8 –0.3 +0.8 –0.3 +0.8 V

V

IH

+2.0 V

DIG

+ 0.3 +2.0 V

DIG

+ 0.3 +2.0 V

DIG

+ 0.3 V

I

IL

±10 ±10 ±10 µA

I

IH

±10 ±10 ±10 µA

NOTES

1

LSB means least significant bit. With a ±10 V input, one LSB is 305 µV.

2

Typical rms noise at worst case transitions and temperatures.

3

Measured with fixed resistors as shown in Figure 5 (AD976) and Figure 6 (AD976A). Adjustable to zero as shown in Figure 7.

4

Full-scale error is expressed as the % difference between the actual full-scale code transition voltage and the ideal full-scale transition voltage and includes the effect

of offset error. The full-scale error is the worst case of either the –full-scale or +full-scale code transition voltage errors.

5

fIN = 20 kHz (AD976) and fIN = 45 kHz (AD976A), 0.5 dB down, unless otherwise noted.

6

All specifications in dB are referred to a full scale ±10 V input.

7

Full-power bandwidth is defined as full-scale input frequency at which signal-to-(noise + distortion) degrades to 60 dB or 10 bits of accuracy.

8

Recovers to specified performance after a 2 × F

S

input overvoltage.

Specifications subject to change without notice.

(–40ⴗC to +85ⴗC, FS = 100 kHz, Ref = Internal Reference,

V

DIG

= V

ANA

= +5 V unless otherwise noted)

AD976/AD976A

–4–

REV. C

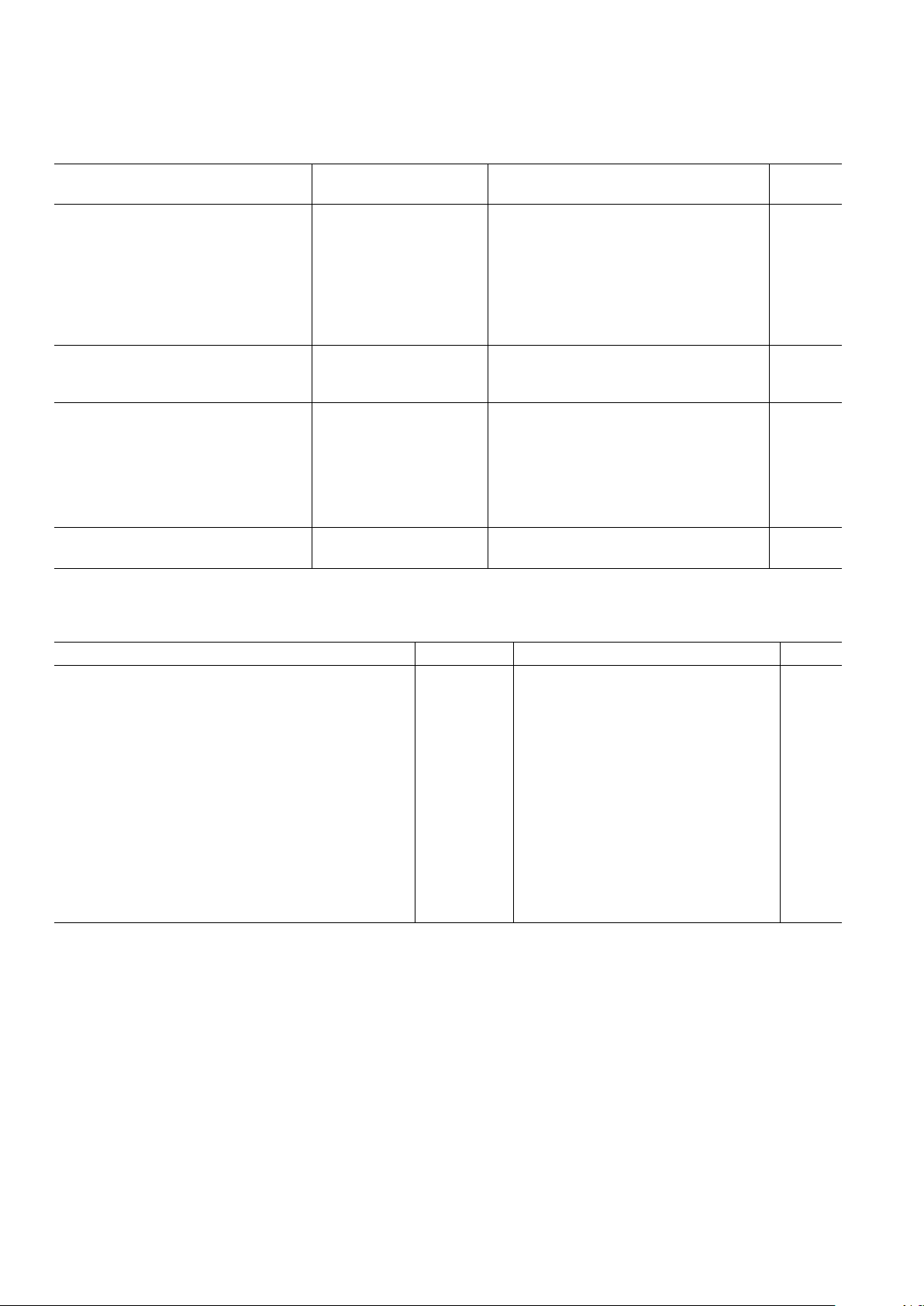

All Grades

Parameter Conditions Min Typ Max Units

DIGITAL OUTPUTS

Data Format Parallel 16 Bits

Data Coding Binary Twos Complement

V

OL

I

SINK

= 1.6 mA +0.4 V

V

OH

I

SOURCE

= 500 µA+4 V

Leakage Current High-Z State, ±5 µA

V

OUT

= 0 V to V

DIG

Output Capacitance High-Z State 15 pF

DIGITAL TIMING

Bus Access Time 83 ns

Bus Relinquish Time 83 ns

POWER SUPPLIES

Specified Performance

V

DIG

4.75 5 5.25 V

V

ANA

4.75 5 5.25 V

I

DIG

3.0 mA

I

ANA

11 mA

Power Dissipation 100 mW

TEMPERATURE RANGE

Specified Performance –40 +85 °C

Specifications subject to change without notice.

TIMING SPECIFICATIONS

(AD976A: FS = 200 kHz; AD976: FS = 100 kHz; –40ⴗC to +85ⴗC, V

DIG

= V

ANA

= +5 V unless otherwise noted)

Symbol Min Typ Max Units

Convert Pulsewidth t

1

50 ns

Data Valid Delay after R/C Low (AD976A/AD976) t

2

4.0/8.0 µs

BUSY Delay from R/C Low t

3

83 ns

BUSY Low (AD976A/AD976) t

4

4.0/8.0 µs

BUSY Delay after End of Conversion (AD976A/AD976) t

5

180/360 ns

Aperture Delay t

6

40 ns

Conversion Time (AD976A/AD976) t

7

3.8/7.6 4.0/8.0 µs

Acquisition Time t

8

1.0/2.0 µs

Bus Relinquish Time t

9

10 35 83 ns

BUSY Delay after Data Valid (AD976A/AD976) t

10

50 180/360 ns

Previous Data Valid after R/C Low (AD976A/AD976) t

11

3.7/7.4 µs

Throughput Time (AD976A/AD976) t

7

+ t

8

5/10 µs

R/C to CS Setup Time t

12

10 ns

Time Between Conversions (AD976A/AD976) t

13

5/10 µs

Bus Access and Byte Delay t

14

10 83 ns

Specifications subject to change without notice.

AD976/AD976A

–5–

REV. C

ABSOLUTE MAXIMUM RATINGS

1

Analog Inputs

V

IN

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±25 V

CAP . . . . . . . . . . . . . . . . +V

ANA

+ 0.3 V to AGND2 – 0.3 V

REF . . . . . . . . . . . . . . . . . . . . . Indefinite Short to AGND2

Ground Voltage Differences

DGND, AGND1, AGND2 . . . . . . . . . . . . . . . . . . . . ±0.3 V

Supply Voltages

V

ANA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

V

DIG

to V

ANA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±7 V

V

DIG

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Digital Inputs . . . . . . . . . . . . . . . . . . . –0.3 V to V

DIG

+ 0.3 V

Internal Power Dissipation

2

PDIP (N), SOIC (R), SSOP (RS) . . . . . . . . . . . . . 700 mW

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . +150°C

Storage Temperature Range (N, R, RS) . . . –65°C to +150°C

Lead Temperature Range

(Soldering 10 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . +300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Specification is for device in free air:

28-Lead PDIP: θJA = 74°C/W; θJC = 24°C/W,

28-Lead SOIC: θJA = 72°C/W; θJC = 23°C/W,

28-Lead SSOP: θJA = 109°C/W; θJC = 39°C/W.

ORDERING GUIDE

Temperature Max Min Throughput Package Package

Model Range INL S/(N+D) Rate Descriptions Options

AD976AN –40°C to +85°C ±3.0 LSB 83 dB 100 kSPS 28-Lead, 300 mil Plastic DIP N-28B

AD976BN –40°C to +85°C ±2.0 LSB 85 dB 100 kSPS 28-Lead, 300 mil Plastic DIP N-28B

AD976CN –40°C to +85°C 83 dB 100 kSPS 28-Lead, 300 mil Plastic DIP N-28B

AD976AAN –40°C to +85°C ±3.0 LSB 83 dB 200 kSPS 28-Lead, 300 mil Plastic DIP N-28B

AD976ABN –40°C to +85°C ±2.0 LSB 85 dB 200 kSPS 28-Lead, 300 mil Plastic DIP N-28B

AD976ACN –40°C to +85°C 83 dB 200 kSPS 28-Lead, 300 mil Plastic DIP N-28B

AD976AR –40°C to +85°C ±3.0 LSB 83 dB 100 kSPS 28-Lead Small Outline Package R-28

AD976BR –40°C to +85°C ±2.0 LSB 85 dB 100 kSPS 28-Lead Small Outline Package R-28

AD976CR –40°C to +85°C 83 dB 100 kSPS 28-Lead Small Outline Package R-28

AD976AAR –40°C to +85°C ±3.0 LSB 83 dB 200 kSPS 28-Lead Small Outline Package R-28

AD976ABR –40°C to +85°C ±2.0 LSB 85 dB 200 kSPS 28-Lead Small Outline Package R-28

AD976ACR –40°C to +85°C 83 dB 200 kSPS 28-Lead Small Outline Package R-28

AD976ARS –40°C to +85°C ±3.0 LSB 83 dB 100 kSPS 28-Lead Shrink Small Outline Package RS-28

AD976BRS –40°C to +85°C ±2.0 LSB 85 dB 100 kSPS 28-Lead Shrink Small Outline Package RS-28

AD976CRS –40°C to +85°C 83 dB 100 kSPS 28-Lead Shrink Small Outline Package RS-28

AD976AARS –40°C to +85°C ±3.0 LSB 83 dB 200 kSPS 28-Lead Shrink Small Outline Package RS-28

AD976ABRS –40°C to +85°C ±2.0 LSB 85 dB 200 kSPS 28-Lead Shrink Small Outline Package RS-28

AD976ACRS –40°C to +85°C 83 dB 200 kSPS 28-Lead Shrink Small Outline Package RS-28

PIN CONFIGURATION

DIP, SOIC and SSOP Packages

14

13

12

11

10

9

8

2

3

4

7

6

5

1

TOP VIEW

(Not to Scale)

17

16

15

19

18

20

28

27

26

25

24

23

22

21

AD976

AD976A

V

IN

CS

BUSY

V

ANA

V

DIG

AGND1

REF

CAP

D0 (LSB)

BYTE

R/C

AGND2

D15 (MSB)

D14

D13

D12

D11

D3

D2

D1

D10

D9

D8

DGND

D4

D7

D6

D5

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD976/AD976A features proprietary ESD protection circuitry, permanent damage

may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

1.6mA I

OL

TO

OUTPUT

PIN

C

L

100pF

500mA

I

OH

+2.1V

Figure 1. Load Circuit for Digital Interface Timing

WARNING!

ESD SENSITIVE DEVICE

Loading...

Loading...