8-/10-/12-/14-Bit, 175 MSPS TxDAC

Data Sheet

FEATURES

175 MSPS update rate

Low power member of pin-compatible

TxDAC product family

Low power dissipation

12 mW at 80 MSPS, 1.8 V

50 mW at 175 MSPS, 3.3 V

Wide supply voltage: 1.7 V to 3.6 V

SFDR to Nyquist

AD9707: 84 dBc at 5 MHz output

AD9707: 83 dBc at 10 MHz output

AD9707: 75 dBc at 20 MHz output

Adjustable full-scale current outputs: 1 mA to 5 mA

On-chip 1.0 V reference

CMOS-compatible digital interface

Common-mode output: adjustable 0 V to 1.2 V

Power-down mode <2 mW at 3.3 V (SPI controllable)

Self-calibration

Compact 32-lead LFCSP_VQ, RoHS compliant package

GENERAL DESCRIPTION

The AD9704/AD9705/AD9706/AD9707 are the fourth-generation

family in the TxDAC series of high performance, CMOS digital-toanalog converters (DACs). This pin-compatible, 8-/10-/12-/14-bit

resolution family is optimized for low power operation, while

maintaining excellent dynamic performance. The AD9704/

AD9705/AD9706/AD9707 family is pin-compatible with the

AD9748/AD9740/AD9742/AD9744 family of TxDAC converters

and is specifically optimized for the transmit signal path of

communication systems. All of the devices share the same

interface, LFCSP_VQ package, and pinout, providing an upward or

downward component selection path based on performance,

resolution, and cost. The AD9704/AD9705/AD9706/AD9707

offers exceptional ac and dc performance, while supporting

update rates up to 175 MSPS.

The flexible power supply operating range of 1.7 V to 3.6 V and low

power dissipation of the AD9704/AD9705/AD9706/AD9707 parts

make them well-suited for portable and low power applications.

Power dissipation of the AD9704/AD9705/AD9706/AD9707 can

be reduced to 15 mW, with a small trade-off in performance, by

lowering the full-scale current output. In addition, a power-down

mode reduces the standby power dissipation to approximately

2.2 mW.

Digital-to-Analog Converters

AD9704/AD9705/AD9706/AD9707

The AD9704/AD9705/AD9706/AD9707 has an optional serial

peripheral interface (SPI®) that provides a higher level of programmability to enhance performance of the DAC. An adjustable

output, common-mode feature allows for easy interfacing to

other components that require common modes from 0 V to 1.2 V.

Edge-triggered input latches and a 1.0 V temperature-compensated

band gap reference have been integrated to provide a complete,

monolithic DAC solution. The digital inputs support 1.8 V and

3.3 V CMOS logic families.

PRODUCT HIGHLIGHTS

1. Pin Compatible. The AD9704/AD9705/AD9706/AD9707

line of TxDAC® converters is pin-compatible with the

AD9748/AD9740/AD9742/AD9744 TxDAC line

(LFCSP_VQ package).

2. Low Power. Complete CMOS DAC operates on a single

supply of 3.6 V down to 1.7 V, consuming 50 mW (3.3 V)

and 12 mW (1.8 V). The DAC full-scale current can be

reduced for lower power operation. Sleep and power-down

modes are provided for low power idle periods.

3. Self-Calibration. Self-calibration enables true 14-bit INL

and DNL performance in the AD9707.

4. Twos Complement/Binary Data Coding Support. Data

input supports twos complement or straight binary data

coding.

5. Flexible Clock Input. A selectable high speed, single-ended,

and differential CMOS clock input supports 175 MSPS

conversion rate.

6. Device Configuration. Device can be configured through

pin strapping, and SPI control offers a higher level of

programmability.

7. Easy Interfacing to Other Components. Adjustable

common-mode output allows for easy interfacing to other

signal chain components that accept common-mode levels

from 0 V to 1.2 V.

8. On-Chip Voltage Reference. The AD9704/AD9705/AD9706/

AD9707 include a 1.0 V temperature-compensated band

gap voltage reference.

9. Industry-Standard 32-Lead LFCSP_VQ Package.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006–2011 Analog Devices, Inc. All rights reserved.

AD9704/AD9705/AD9706/AD9707 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Functional Block Diagram .............................................................. 4

Specifications..................................................................................... 5

DC Specifications (3.3 V)............................................................ 5

Dynamic Specifications (3.3 V).................................................. 6

Digital Specifications (3.3 V) ...................................................... 7

DC Specifications (1.8 V)............................................................ 8

Dynamic Specifications (1.8 V).................................................. 9

Digital Specifications (1.8 V) .................................................... 10

Timing Diagram......................................................................... 10

Absolute Maximum Ratings.......................................................... 11

Thermal Characteristics ............................................................11

ESD Caution................................................................................ 11

Pin Configurations and Function Descriptions ......................... 12

AD9707........................................................................................ 12

AD9706........................................................................................ 13

AD9705........................................................................................ 14

AD9704........................................................................................ 15

Typical Performance Characteristics ........................................... 16

AD9707........................................................................................ 16

AD9704, AD9705, and AD9706............................................... 23

REVISION HISTORY

10/11—Rev. A to Rev. B

Changes to Features Section............................................................ 1

Changes to Table 1............................................................................ 5

Changes to Table 2............................................................................ 6

Changes to Table 4............................................................................ 8

Changes to Table 5............................................................................ 9

Changes to Figure 3 and Table 9................................................... 12

Changes to Figure 4 and Table 10................................................. 13

Changes to Figure 5 and Table 11................................................. 14

Changes to Figure 6 and Table 12................................................. 15

Changes to Figure 15 and Figure 16............................................. 17

Moved Figure 41 to Figure 24 Position........................................ 18

Moved Figure 42 to Figure 25 Position and Moved Figure 43 to

Figure 26 Position........................................................................... 19

Changes to Figure 27...................................................................... 20

Changes to Figure 33 to Figure 35................................................ 21

Moved Figure 24 to Figure 41 Position........................................ 22

Moved Figure 25 to Figure 43 Position and Moved Figure 26 to

Figure 44 Position........................................................................... 23

Changes to Figure 44...................................................................... 23

Rev. B | Page 2 of 44

Terminology.................................................................................... 29

Theory of Operation ...................................................................... 30

Serial Peripheral Interface......................................................... 30

SPI Register Map ........................................................................ 32

SPI Register Descriptions.......................................................... 33

Reference Operation .................................................................. 34

Reference Control Amplifier .................................................... 34

DAC Transfer Function............................................................. 35

Analog Outputs .......................................................................... 35

Adjustable Output Common Mode......................................... 36

Digital Inputs .............................................................................. 36

Clock Input.................................................................................. 36

DAC Timing................................................................................ 36

Power Dissipation....................................................................... 37

Self-Calibration........................................................................... 38

Applications Information.............................................................. 40

Output Configurations.............................................................. 40

Differential Coupling Using a Transformer ............................... 40

Single-Ended Buffered Output Using an Op Amp................ 40

Differential Buffered Output Using an Op Amp ................... 41

Evaluation Board........................................................................ 41

Outline Dimensions....................................................................... 42

Ordering Guide .......................................................................... 42

Changes to Figure 57...................................................................... 26

Changes to Figure 70...................................................................... 29

Changes to Serial Peripheral Interface Section .......................... 30

Changes to Table 15 ....................................................................... 32

Deleted Table 23; Renumbered Sequentially .............................. 33

Changes to Reference Operation Section and Reference Control

Amplifier Section............................................................................ 34

Changes to Adjustable Output Common Mode Section and

DAC Timing Section...................................................................... 36

Added the Deskew Mode Section ................................................ 36

Deleted Figure 80; Renumbered Sequentially ............................ 36

Changed Sleep and Power-Down Operation (Pin Mode) Section

to Sleep Operation (Pin Mode) Section ...................................... 38

Changes to Sleep Operation (Pin Mode) Section ...................... 38

Changes to Self-Calibration Section ............................................ 39

Changes to Evaluation Board Section.......................................... 41

Added Exposed Pad Notation to Outline Dimensions ............. 42

Changes to Ordering Guide.......................................................... 42

Deleted Evaluation Board Schematics Section........................... 43

Deleted Figure 92 to Figure 102 ................................................... 43

Data Sheet AD9704/AD9705/AD9706/AD9707

4/07—Rev. 0 to Rev. A

Changes to Features List...................................................................1

Changes to Product Highlights .......................................................1

Changes to General Description .....................................................3

Changes to Table 3 ............................................................................6

Changes to Table 4 ............................................................................7

Changes to Table 6 ............................................................................9

Changes to Figure 17 and Figure 18 .............................................16

Deleted Figure 29, Renumbered Sequentially.............................19

Changes to Figure 44 ......................................................................22

Changes to Figure 57 Caption .......................................................25

Changes to Figure 73, Figure 75, and Figure 77..........................31

Changes to Table 16 ........................................................................32

Replaced Single-Ended Buffered Output Using an Op

Amp Section ....................................................................................40

Changes to Figure 91 ......................................................................41

Changes to Figure 93 ......................................................................44

Changes to Figure 96 ......................................................................47

7/06—Revision 0: Initial Version

Rev. B | Page 3 of 44

AD9704/AD9705/AD9706/AD9707 Data Sheet

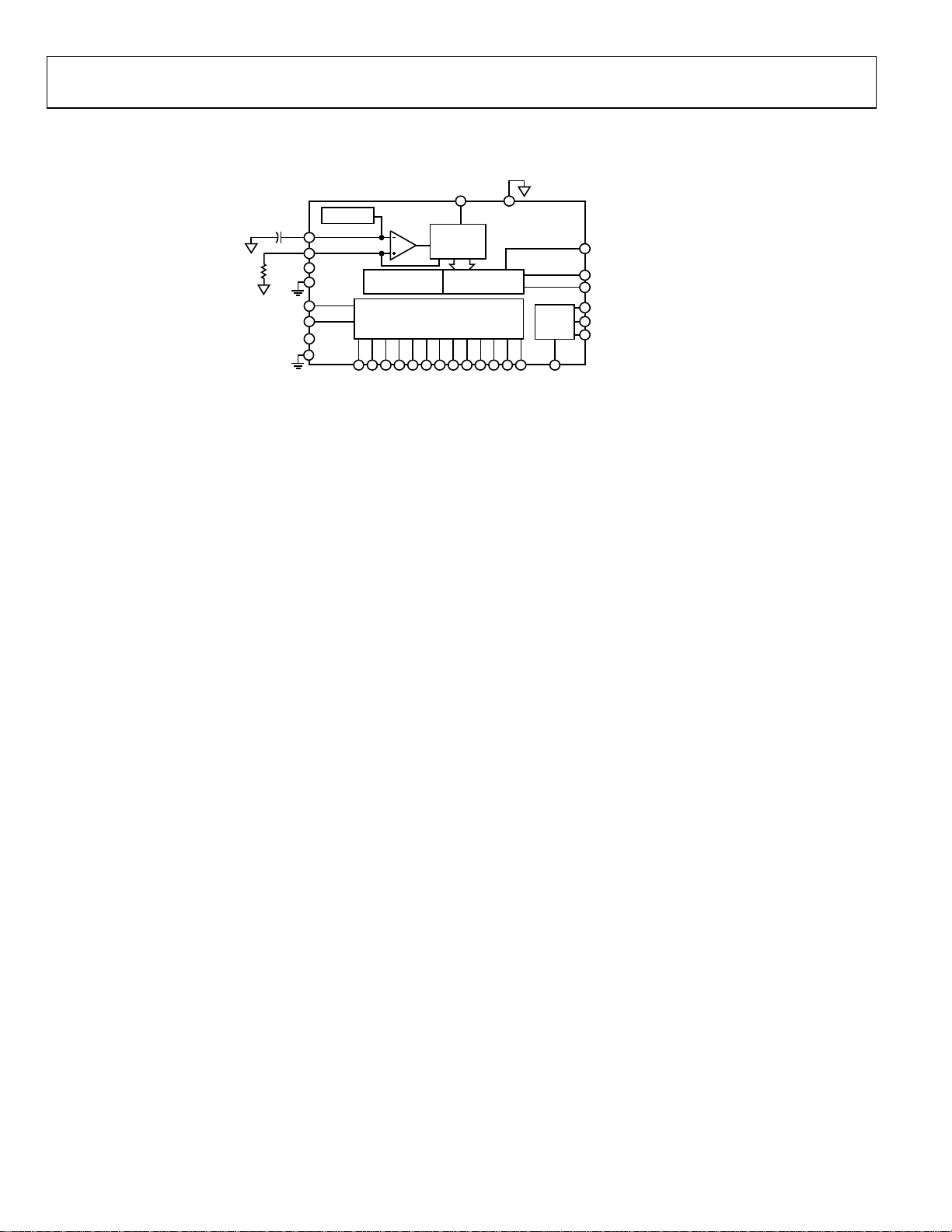

FUNCTIONAL BLOCK DIAGRAM

1.7V TO 3.6V

AVDD

CURRENT

SOURCE

ARRAY

LATCHES

3.6V

1.0V REF

REFIO

FS ADJ

CLKVDD

CLKCOM

DVDD

DCOM

SEGMENTED

SWITCHES

DIGITAL INPUTS (DB13 TO DB0)

0.1µF

1.7V

R

SET

TO

3.6V

CLK+

CLK–

1.7V TO

Figure 1.

ACOM

AD9707

LSB

SWITCHES

OTCM

IOUTA

IOUTB

SLEEP/CSB

PIN/SPI/RESET

MODE/SDIOSPI

CMODE/SCLK

05926-001

Rev. B | Page 4 of 44

Data Sheet AD9704/AD9705/AD9706/AD9707

SPECIFICATIONS

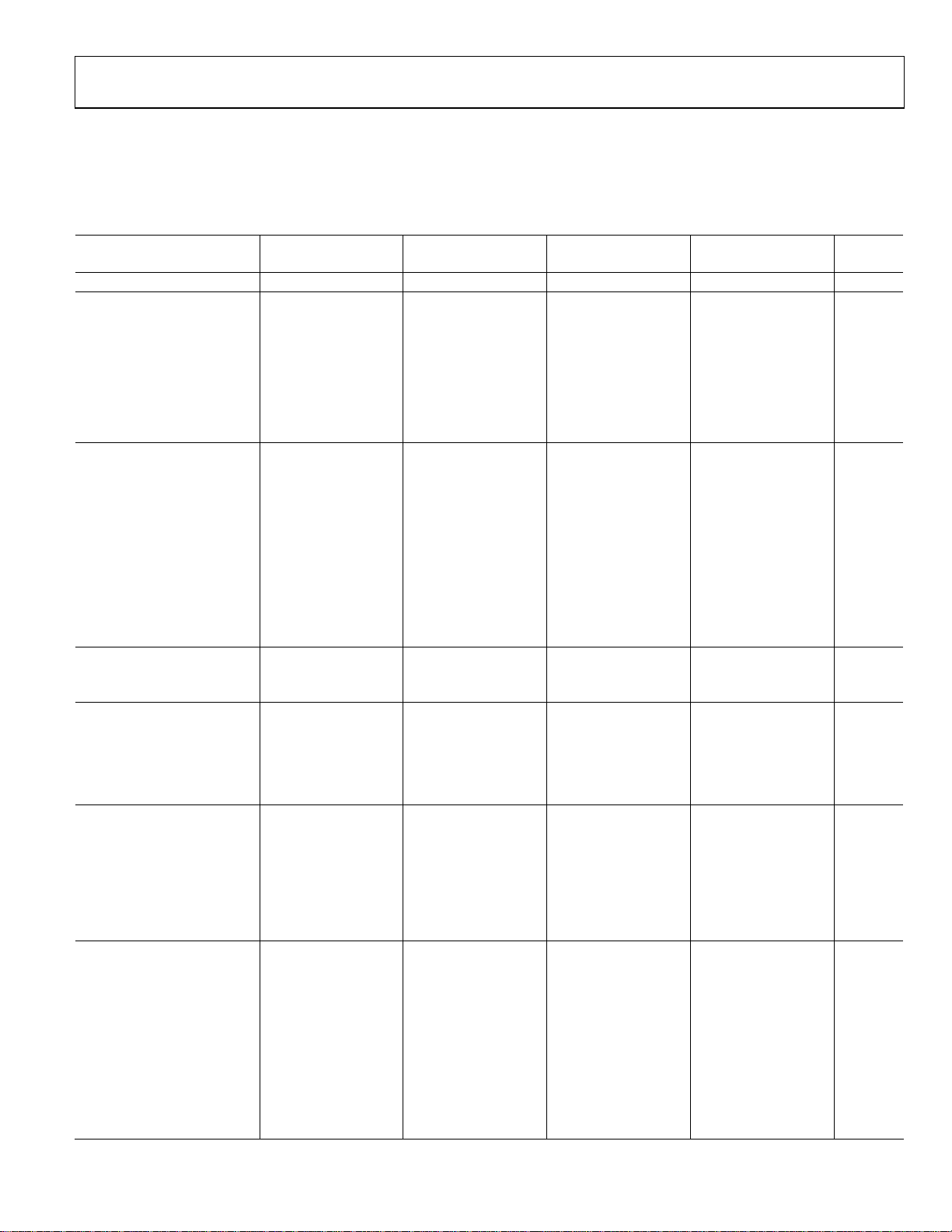

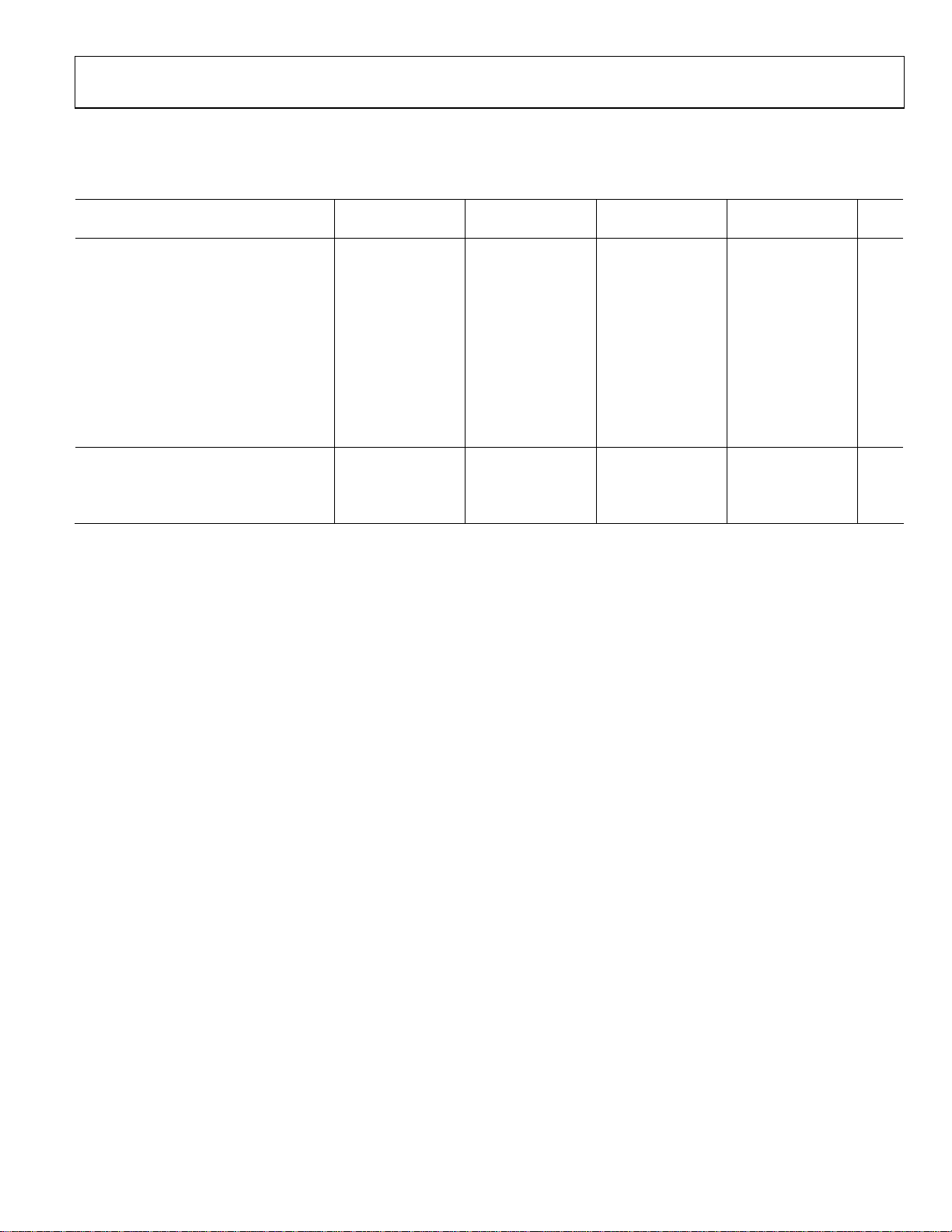

DC SPECIFICATIONS (3.3 V)

T

to T

MIN

Table 1.

AD9707 AD9706 AD9705 AD9704

Parameter Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

RESOLUTION 14 12 10 8 Bits

DC ACCURACY1

Integral Nonlinearity (INL)

Integral Nonlinearity (INL)

Differential Nonlinearity

Differential Nonlinearity

ANALOG OUTPUT

Offset Error −0.03 0 +0.03 −0.03 0 +0.03 −0.03 0 +0.03 −0.03 0 +0.03 % of FSR

Gain Error (With External

Gain Error (With Internal

Full-Scale Output Current2 1 2 5 1 2 5 1 2 5 1 2 5 mA

Output Compliance Range

Output Resistance 200 200 200 200 MΩ

Output Capacitance 5 5 5 5 pF

REFERENCE OUTPUT

Reference Voltage 0.98 1.025 1.08 0.98 1.025 1.08 0.98 1.025 1.08 0.98 1.025 1.08 V

Reference Output Current3 100 100 100 100 nA

REFERENCE INPUT

Input Compliance Range 0.1 1.25 0.1 1.25 0.1 1.25 0.1 1.25 V

Reference Input Resistance

Reference Input Resistance

TEMPERATURE COEFFICIENTS

Offset Drift 0 0 0 0 ppm of

Gain Drift (Without Internal

Gain Drift (With Internal

Reference Voltage Drift ±25 ±25 ±25 ±25 ppm/°C

POWER SUPPLY

Supply Voltage

Analog Supply Current (I

Digital Supply Current (I

Clock Supply Current (I

Power Dissipation4

Supply Current Sleep Mode

, AVDD = 3.3 V, DVDD = 3.3 V, CLKVDD = 3.3 V, I

MAX

= 2 mA, unless otherwise noted.

OUTFS

±1.4 ±6.0 ±0.41 ±1.48 ±0.10 ±0.36 ±0.03 ±0.09 LSB

Precalibration

±0.9 ±0.30 ±0.10 LSB

Postcalibration

±1.2 ±4.4 ±0.35 ±1.17 ±0.09 ±0.31 ±0.02 ±0.08 LSB

(DNL) Precalibration

±0.4 ±0.13 ±0.03 LSB

(DNL) Postcalibration

−2.7 −0.1 +2.7 −2.7 −0.1 +2.7 −2.7 −0.1 +2.7 −2.7 −0.1 +2.7 % of FSR

Reference)

−2.7 −0.1 +2.7 −2.7 −0.1 +2.7 −2.7 −0.1 +2.7 −2.7 −0.1 +2.7 % of FSR

Reference)

−0.8 +0.8 −0.8 +0.8 −0.8 +0.8 −0.8 +0.8 V

(From OTCM to

IOUTA/IOUTB)

10 10 10 10 kΩ

(Reference Powered Up)

1 1 1 1 MΩ

(Reference Powered Down)

FSR/°C

±29 ±29 ±29 ±29 ppm of

Reference)

FSR/°C

±40 ±40 ±40 ±40 ppm of

Reference)

FSR/°C

AVDD 3.3 3.6 3.3 3.6 3.3 3.6 3.3 3.6 V

DVDD 3.3 3.6 3.3 3.6 3.3 3.6 3.3 3.6 V

CLKVDD 3.3 3.6 3.3 3.6 3.3 3.6 3.3 3.6 V

) 5.2 6.7 5.2 6.7 5.1 6.7 5.1 6.7 mA

AVDD

)4 5.9 6.6 5.4 6.6 5.0 6.6 4.6 6.6 mA

DVDD

4

4.1 4.7 4.1 4.7 4.1 4.7 4.1 4.7 mA

)

CLKVDD

50.2 57 48.5 57 46.9 57 45.5 57 mW

0.37 0.4 0.37 0.4 0.37 0.4 0.37 0.4 mA

)

(I

AVDD

Rev. B | Page 5 of 44

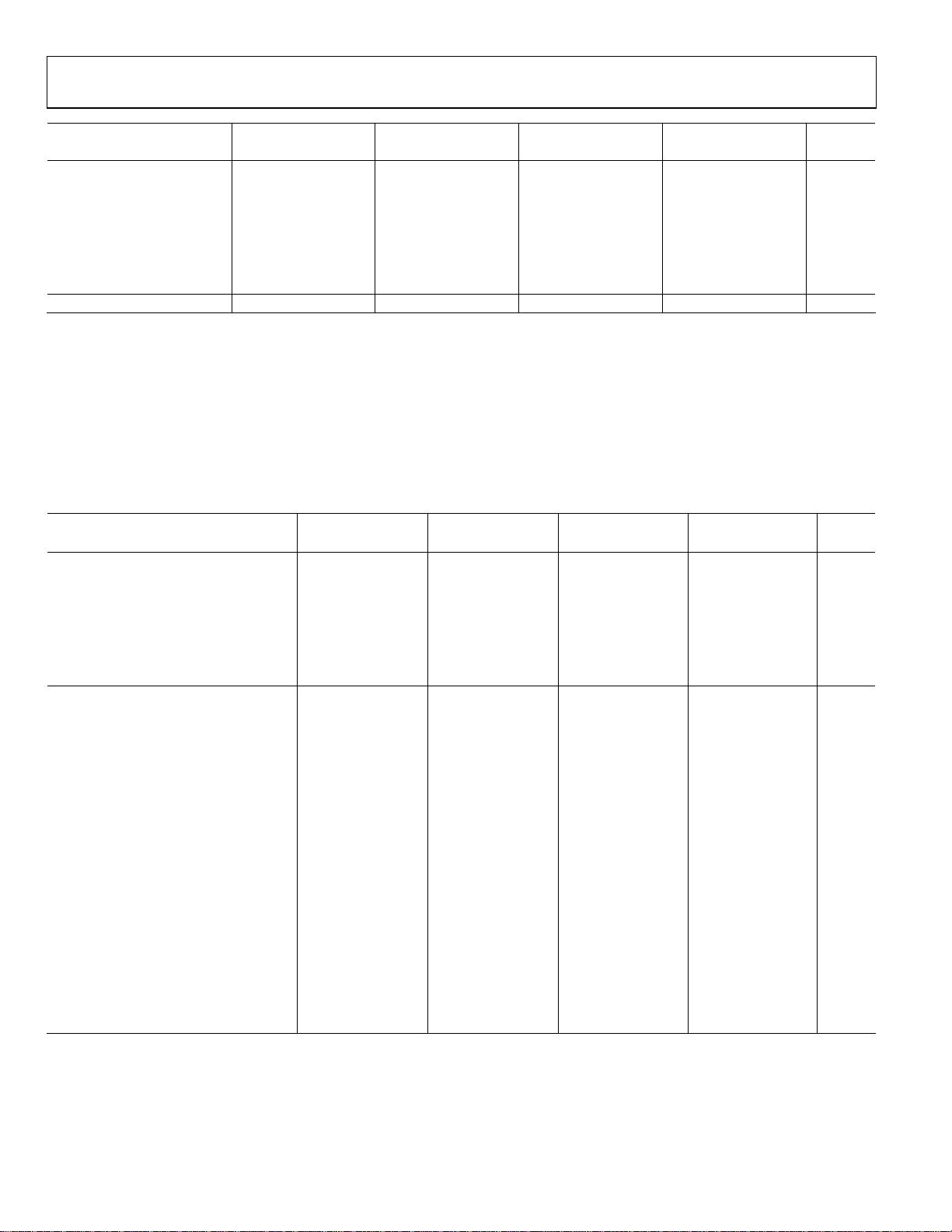

AD9704/AD9705/AD9706/AD9707 Data Sheet

AD9707 AD9706 AD9705 AD9704

Parameter Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

Supply Current Power-Down

AVDD

)

Mode (I

Supply Current Clock Power-

Down Mode (I

DVDD

)5

Supply Current Clock Power-

Down Mode (I

Power Supply Rejection Ratio

(AVDD)

6

CLKVDD

)5

OPERATING RANGE −40 +85 −40 +85 −40 +85 −40 +85 °C

1

Measured at IOUTA, driving a virtual ground.

2

Normal full scale current, I

3

Use an external buffer amplifier with an input bias current <100 nA to drive any external load.

4

Measured at f

5

Measured at f

6

± 5% power supply variation.

CLOCK

CLOCK

OUTFS

= 175 MSPS and f

= 100 MSPS and f

DYNAMIC SPECIFICATIONS (3.3 V)

T

to T

MIN

differentially terminated unless otherwise noted.

Table 2.

AD9707 AD9706 AD9705 AD9704

Parameter Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

DYNAMIC PERFORMANCE

Maximum Output Update Rate, f

Output Settling Time, tST (to 0.1%)1 11 11 11 11 ns

Output Propagation Delay, tPD 4 4 4 4 ns

Glitch Impulse 5 5 5 5 pV-s

Output Rise Time (10% to 90%)1 2.5 2.5 2.5 2.5 ns

Output Fall Time (10% to 90%)1 2.5 2.5 2.5 2.5 ns

AC LINEARITY

Spurious-Free Dynamic Range to

Noise Spectral Density

1

Measured single-ended into 500 Ω load.

, AVDD = 3.3 V, DVDD = 3.3 V, CLKVDD = 3.3 V, I

MAX

Nyquist

f

= 10 MSPS, f

CLOCK

f

= 25 MSPS, f

CLOCK

f

= 65 MSPS, f

CLOCK

f

= 65 MSPS, f

CLOCK

f

= 80 MSPS, f

CLOCK

f

= 125 MSPS, f

CLOCK

f

= 125 MSPS, f

CLOCK

f

= 175 MSPS, f

CLOCK

f

= 175 MSPS, f

CLOCK

f

= 175 MSPS, f

CLOCK

= 2 mA

I

OUTFS

f

= 175 MSPS, f

CLOCK

I

= 5 mA

OUTFS

f

= 175 MSPS, f

CLOCK

= 1 mA

I

OUTFS

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

0.7 7.5 0.7 7.5 0.7 7.5 0.7 7.5

μA

0.6 1 0.6 1 0.6 1 0.6 1 mA

42.5 64 42.5 64 42.5 64 42.5 64

μA

−0.2 +0.03 +0.2 −0.2 +0.03 +0.2 −0.2 +0.03 +0.2 −0.2 +0.03 +0.2 % of

FSR/V

is 32 × the I

current.

REF

= 1.0 MHz, using a differential clock.

OUT

= 1.0 MHz, using a differential clock.

OUT

= 2 mA, differential transformer coupled output, 453 Ω

OUTFS

175 175 175 175 MSPS

CLOCK

= 2.1 MHz 84 84 84 70 dBc

= 2.1 MHz 84 83 84 68 dBc

= 5.1 MHz 84 84 84 70 dBc

= 10.1 MHz 83 83 83 71 dBc

= 1.0 MHz 74 83 72 82 72 82 66 70 dBc

= 15.1 MHz 78 78 78 68 dBc

= 25.1 MHz 77 77 76 69 dBc

= 20.1 MHz 75 75 75 69 dBc

= 40.1 MHz 72 71 71 67 dBc

= 6.0 MHz,

OUT

= 6.0 MHz,

OUT

= 6.0 MHz,

OUT

−152 −152 −144 −136 dBc/Hz

−161 dBc/Hz

−146 dBc/Hz

Rev. B | Page 6 of 44

Data Sheet AD9704/AD9705/AD9706/AD9707

DIGITAL SPECIFICATIONS (3.3 V)

T

to T

MIN

Table 3.

AD9707 AD9706 AD9705 AD9704

Parameter Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

DIGITAL INPUTS1

Logic 1 Voltage 2.1 3 2.1 3 2.1 3 2.1 3 V

Logic 0 Voltage 0 0.9 0 0.9 0 0.9 0 0.9 V

Logic 1 Current −10 +10 −10 +10 −10 +10 −10 +10 μA

Logic 0 Current 10 10 10 10 μA

Input Capacitance 5 5 5 5 pF

Input Setup Time, tS, +25°C 1.4 1.4 1.4 1.4 ns

Input Hold Time, tH, +25°C 0.3 0.3 0.3 0.3 ns

Input Setup Time, tS, −40°C to +85°C 1.6 1.6 1.6 1.6 ns

Input Hold Time, tH, −40°C to +85°C 0.6 0.6 0.6 0.6 ns

Latch Pulse Width, t

CLK INPUTS2

Input Voltage Range 0 3 0 3 0 3 0 3 V

Common-Mode Voltage 0.75 1.5 2.25 0.75 1.5 2.25 0.75 1.5 2.25 0.75 1.5 2.25 V

Differential Voltage 0.5 1.5 0.5 1.5 0.5 1.5 0.5 1.5 V

1

Includes CLK+ pin in single-ended clock input mode.

2

Applicable to CLK+ input and CLK− input when configured for differential clock input mode.

, AVDD = 3.3 V, DVDD = 3.3 V, CLKVDD = 3.3 V, I

MAX

2.8 2.8 2.8 2.8 ns

LPW

= 2 mA, unless otherwise noted.

OUTFS

Rev. B | Page 7 of 44

AD9704/AD9705/AD9706/AD9707 Data Sheet

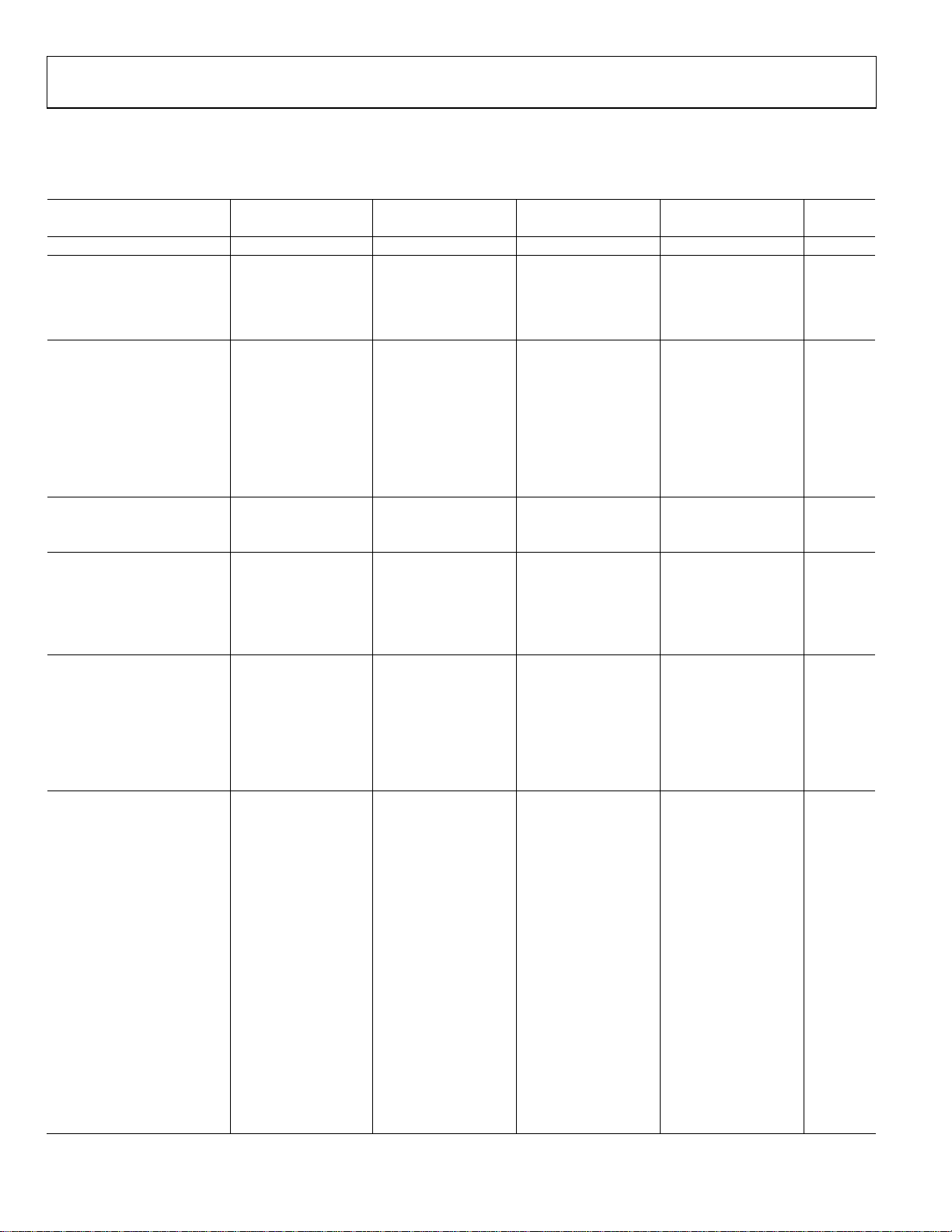

DC SPECIFICATIONS (1.8 V)

T

to T

MIN

, AVDD = 1.8 V, DVDD = 1.8 V, CLKVDD = 1.8 V, I

MAX

Table 4.

AD9707 AD9706 AD9705 AD9704

Parameter Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

RESOLUTION 14 12 10 8 Bits

DC ACCURACY

Integral Nonlinearity (INL)

Precalibration

Differential Nonlinearity

(DNL) Precalibration

ANALOG OUTPUT

Offset Error −0.03 0 +0.03 −0.03 0 +0.03 −0.03 0 +0.03 −0.03 0 +0.03 % of FSR

Gain Error (With Internal

Reference)

Full-Scale Output Current2 1 2 2.5 1 2 2.5 1 2 2.5 1 2 2.5 mA

Output Compliance Range

(With OTCM = AGND)

Output Resistance 200 200 200 200 MΩ

Output Capacitance 5 5 5 5 pF

REFERENCE OUTPUT

Reference Voltage 0.98 1.025 1.08 0.98 1.025 1.08 0.98 1.025 1.08 0.98 1.025 1.08 V

Reference Output Current3 100 100 100 100 nA

REFERENCE INPUT

Input Compliance Range 0.1 1.25 0.1 1.25 0.1 1.25 0.1 1.25 V

Reference Input Resistance

(Reference Powered Up)

Reference Input Resistance

(External Reference)

TEMPERATURE COEFFICIENTS

Offset Drift 0 0 0 0 ppm of

Gain Drift (Without Internal

Reference)

Gain Drift (With Internal

Reference)

Reference Voltage Drift ±25 ±25 ±25 ±25 ppm/°C

POWER SUPPLY

Supply Voltage

AVDD 1.7 1.8 1.7 1.8 1.7 1.8 1.7 1.8 V

DVDD 1.7 1.8 1.7 1.8 1.7 1.8 1.7 1.8 V

CLKVDD 1.7 1.8 1.7 1.8 1.7 1.8 1.7 1.8 V

Analog Supply Current

(I

AVDD

Digital Supply Current

(I

DVDD

Clock Supply Current

(I

CLKVDD

Power Dissipation

Supply Current Sleep Mode

(I

Supply Current Power-Down

Mode (I

Supply Current Clock Power-

Down Mode (I

Supply Current Clock Power-

Down Mode (I

AVDD

1

±1.4 ±6.03 ±0.42 ±1.50 ±0.10 ±0.36 ±0.03 ±0.09 LSB

±1.2 ±4.34 ±0.36 ±1.17 ±0.09 ±0.30 ±0.02 ±0.07 LSB

−2.7 −0.2 +2.7 −2.7 −0.2 +2.7 −2.7 −0.2 +2.7 −2.7 −0.2 +2.7 % of FSR

−0.8 +0.8 −0.8 +0.8 −0.8 +0.8 −0.8 +0.8 V

10 10 10 10 kΩ

1 1 1 1 MΩ

±30 ±30 ±30 ±30 ppm of

±60 ±60 ±60 ±60 ppm of

3.8 4.8 3.8 4.8 3.8 4.8 3.8 4.8 mA

)4

4, 5

)

4, 5

)

4, 5

1.3 1.5 1.2 1.5 1.1 1.5 1.0 1.5 mA

1.3 1.5 1.3 1.5 1.3 1.5 1.3 1.5 mA

11.5 13.2 11.3 13.2 11.1 13.2 11.0 13.2 mW

0.3 0.4 0.3 0.4 0.3 0.4 0.3 0.4 mA

)

5 6 5 6 5 6 5 6 μA

)

AVDD

0.22 0.28 0.22 0.28 0.22 0.28 0.22 0.28 mA

)5

DVDD

9.5 16 9.5 16 9.5 16 9.5 16 μA

5

)

CLKVDD

= 2 mA, unless otherwise noted.

OUTFS

FSR/°C

FSR/°C

FSR/°C

Rev. B | Page 8 of 44

Data Sheet AD9704/AD9705/AD9706/AD9707

AD9707 AD9706 AD9705 AD9704

Parameter Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

Power Supply Rejection

Ratio (AVDD)

6

OPERATING RANGE −40 +85 −40 +85 −40 +85 −40 +85 °C

1

Measured at IOUTA, driving a virtual ground.

2

Nominal full-scale current, I

3

Use an external buffer amplifier with an input bias current <100 nA to drive any external load.

4

Measured at I

5

Measured at f

6

±5% power supply variation.

= 1 mA.

OUTFS

= 80 MSPS and f

CLOCK

DYNAMIC SPECIFICATIONS (1.8 V)

T

to T

MIN

terminated unless otherwise noted.

Table 5.

AD9707 AD9706 AD9705 AD9704

Parameter Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

DYNAMIC PERFORMANCE

Maximum Output Update Rate, f

Output Settling Time, tST, (to 0.1%)1 11 11 11 11 ns

Output Propagation Delay (tPD) 5.6 5.6 5.6 5.6 ns

Glitch Impulse 5 5 5 5 pV-s

Output Rise Time (10% to 90%)1 2.5 2.5 2.5 2.5 ns

Output Fall Time (10% to 90%)1 2.5 2.5 2.5 2.5 ns

AC LINEARITY

Spurious-Free Dynamic Range to

Noise Spectral Density

1

Measured single-ended into 500 Ω load.

, AVDD = 1.8 V, DVDD = 1.8 V, CLKVDD = 1.8 V, I

MAX

Nyquist

f

= 10 MSPS; f

CLOCK

f

= 25 MSPS; f

CLOCK

f

= 25 MSPS; f

CLOCK

f

= 65 MSPS; f

CLOCK

f

= 65 MSPS; f

CLOCK

f

= 80 MSPS; f

CLOCK

f

= 80 MSPS; f

CLOCK

f

= 80 MSPS; f

CLOCK

f

= 80 MSPS; f

CLOCK

I

OUTFS

f

= 80 MSPS; f

CLOCK

I

OUTFS

= 1 mA

= 2 mA

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

−2 −0.1 +2 −2 −0.1 +2 −2 −0.1 +2 −2 −0.1 +2 % of

FSR/V

, is 32 × the I

OUTFS

OUT

current.

REF

= 1 MHz, using a differential clock.

= 1 mA, differential transformer coupled output, 453 Ω differentially

OUTFS

125 125 125 125 MSPS

CLOCK

= 2.1 MHz 86 86 85 70 dBc

= 2.1 MHz 87 86 84 68 dBc

= 5.1 MHz 82 82 82 68 dBc

= 10.1 MHz 82 79 78 70 dBc

= 15.1 MHz 77 76 74 69 dBc

= 1.0 MHz 74 82 72 82 72 82 66 70 dBc

= 15.1 MHz 77 77 77 68 dBc

= 30.1 MHz 60 59 59 60 dBc

= 10 MHz;

= 10 MHz;

−145 −144 −140 −128 dBc/Hz

−151 dBc/Hz

Rev. B | Page 9 of 44

AD9704/AD9705/AD9706/AD9707 Data Sheet

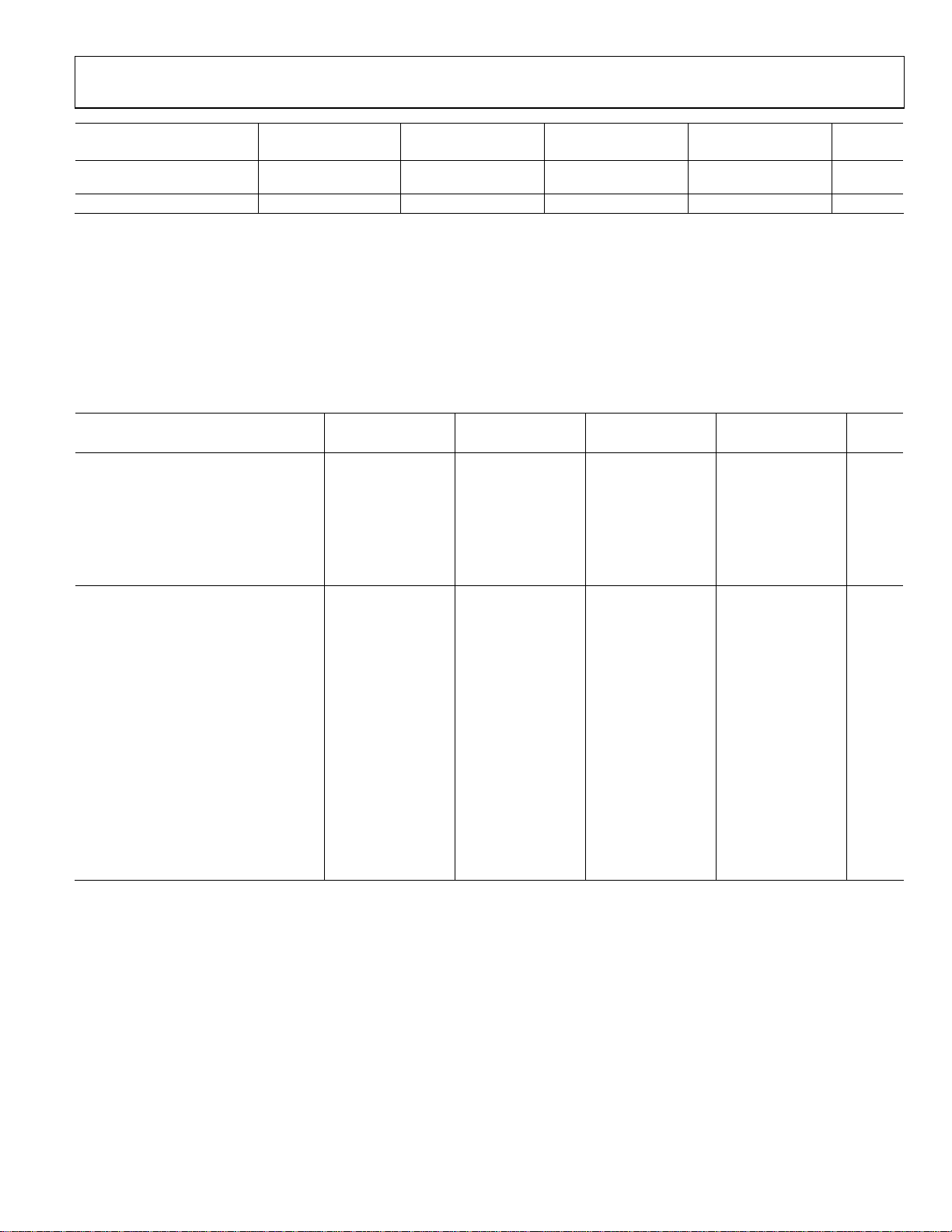

DIGITAL SPECIFICATIONS (1.8 V)

T

to T

MIN

, AVDD = 1.8 V, DVDD = 1.8 V, CLKVDD = 1.8 V, I

MAX

Table 6.

AD9707 AD9706 AD9705 AD9704

Parameter Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

DIGITAL INPUTS1

Logic 1 Voltage 1.2 1.8 1.2 1.8 1.2 1.8 1.2 1.8 V

Logic 0 Voltage 0 0.5 0 0.5 0 0.5 0 0.5 V

Logic 1 Current −10 +10 −10 +10 −10 +10 −10 +10 μA

Logic 0 Current +10 +10 +10 +10 μA

Input Capacitance 5 5 5 5 pF

Input Setup Time, tS, 25°C 2.3 2.3 2.3 2.3 ns

Input Hold Time, tH, 25°C 0 0 0 0 ns

Input Setup Time, tS, −40°C to +85°C 2.4 2.4 2.4 2.4 ns

Input Hold Time, tH, −40°C to +85°C 0.1 0.1 0.1 0.1 ns

Latch Pulse Width, t

6.2 6.2 6.2 6.2 ns

LPW

CLK INPUTS2

Input Voltage Range 0 1.8 0 1.8 0 1.8 0 1.8 V

Common-Mode Voltage 0.4 0.9 1.3 0.4 0.9 1.3 0.4 0.9 1.3 0.4 0.9 1.3 V

Differential Voltage 0.5 1.5 0.5 1.5 0.5 1.5 0.5 1.5 V

1

Includes CLK+ pin in single-ended clock input mode.

2

Applicable to CLK+ input and CLK– input when configured for differential clock input mode.

= 1 mA, unless otherwise noted.

OUTFS

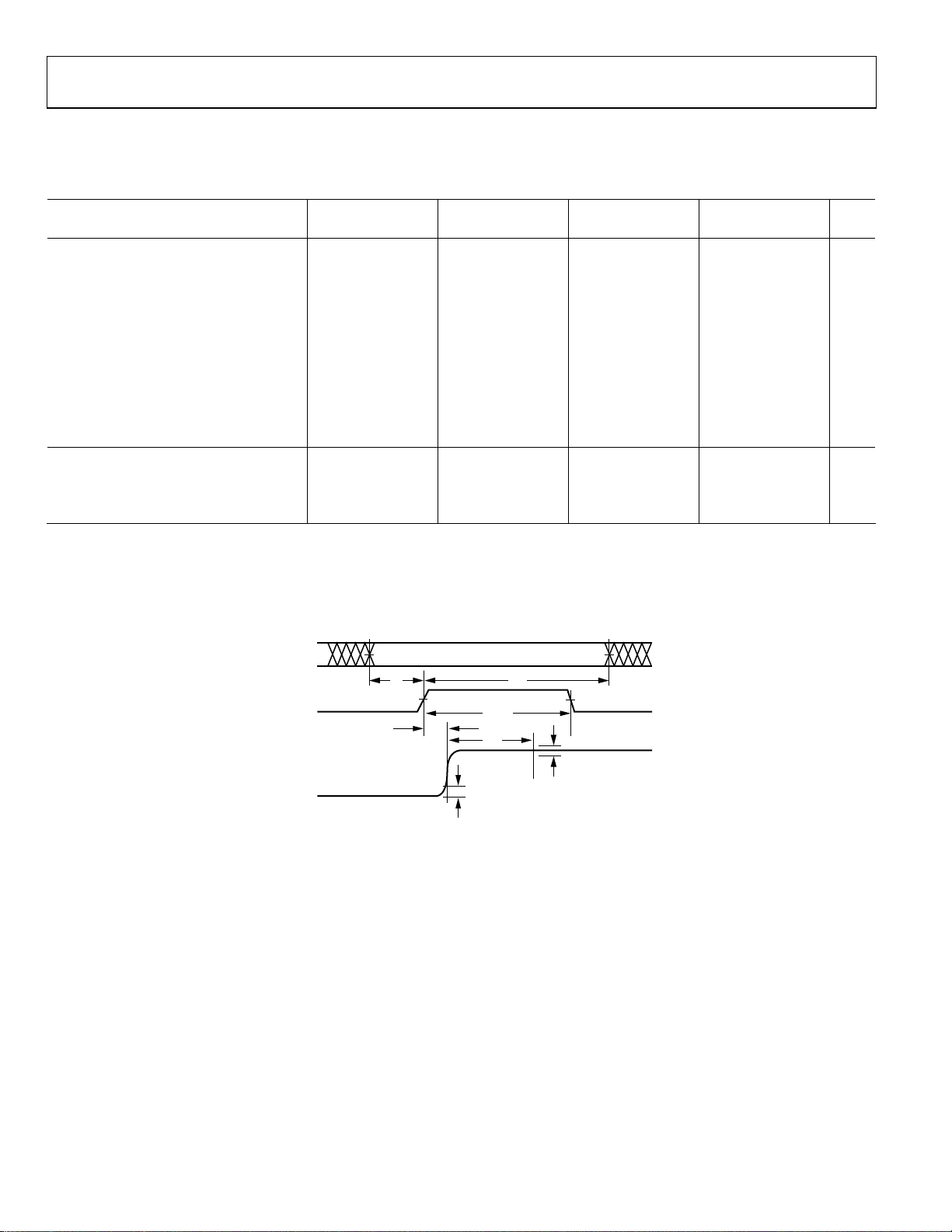

TIMING DIAGRAM

DB0 TO DB13

CLOCK

IOUTA

IOUTB

OR

t

S

t

0.1%

LPW

t

ST

t

PD

Figure 2. Timing Diagram

t

H

0.1%

5926-002

Rev. B | Page 10 of 44

Data Sheet AD9704/AD9705/AD9706/AD9707

ABSOLUTE MAXIMUM RATINGS

Table 7.

Parameter Rating

AVDD to ACOM −0.3 V to +3.9 V

DVDD to DCOM −0.3 V to +3.9 V

CLKVDD to CLKCOM −0.3 V to +3.9 V

ACOM to DCOM −0.3 V to +0.3 V

ACOM to CLKCOM −0.3 V to +0.3 V

DCOM to CLKCOM −0.3 V to +0.3 V

AVDD to DVDD −3.9 V to +3.9 V

AVDD to CLKVDD −3.9 V to +3.9 V

DVDD to CLKVDD −3.9 V to +3.9 V

SLEEP to DCOM −0.3 V to DVDD + 0.3 V

Digital Inputs, MODE to DCOM −0.3 V to DVDD + 0.3 V

IOUTA, IOUTB to ACOM −1.0 V to AVDD + 0.3 V

REFIO, FS ADJ, OTCM to ACOM −0.3 V to AVDD + 0.3 V

CLK+, CLK–, CMODE to CLKCOM −0.3 V to CLKVDD + 0.3 V

Junction Temperature 150°C

Storage Temperature Range −65°C to +150°C

Lead Temperature (10 sec) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

Thermal impedance measurements were taken on a 4-layer board

in still air, in accordance with EIA/JESD51-7.

Table 8. Thermal Resistance

Package Type θJA Unit

32-Lead LFCSP_VQ 32.5 °C/W

ESD CAUTION

Rev. B | Page 11 of 44

AD9704/AD9705/AD9706/AD9707 Data Sheet

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

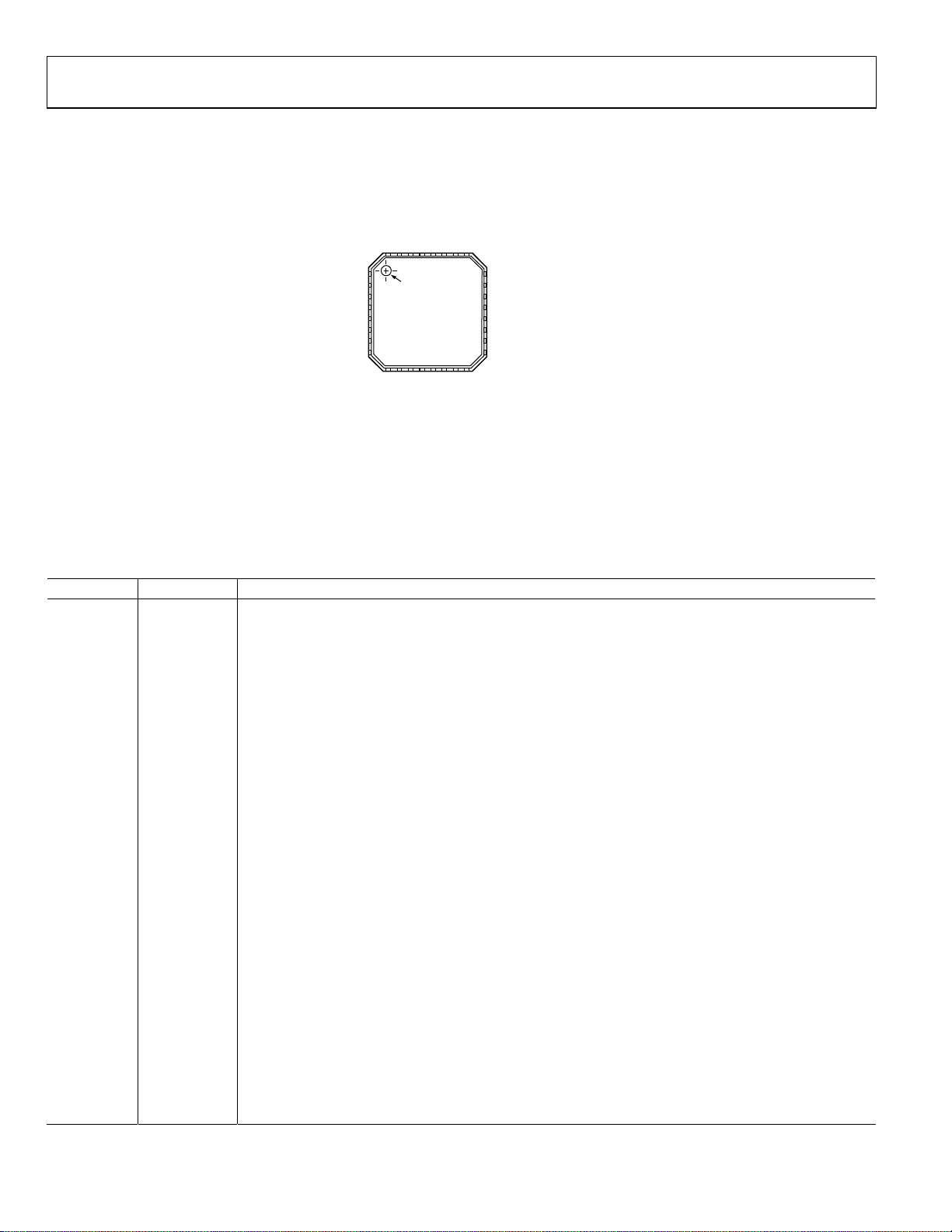

AD9707

SLEEP/CSB

DCOM

DB13 (MSB)

DB12

DB11

DB10

DB9

DB8

30

31

32

1

DB7

DB6

DVDD

DB5

DB4

DB3

DB2

DB1

NOTES

1. IT I S RECOMMENDED THAT T HE EXPOSE D PAD BE

THERMALLY CONNECTED T O A COPPE R GROUND

PLANE FOR ENHANCED ELECT RICAL AND THERMAL

PERFORMANCE .

2

3

4

5

6

7

8

PIN 1

INDICA TOR

AD9707

TOP VIEW

(Not to Scale)

9

11

10

DCOM

CLKVDD

DB0 (LSB)

Figure 3. AD9707 Pin Configuration

25

26

272829

24

FS ADJ

23

REFIO

22

ACOM

21

IOUTA

20

IOUTB

19

OTCM

18

AVDD

17

PIN/SPI/RESET

16

15

141312

CLK–

CLK+

CLKCOM

MODE/SDI O

CMODE/SCLK

5926-003

Table 9. AD9707 Pin Function Descriptions

Pin No. Mnemonic Description

28 to 32, 1,

DB12 to DB1 Data Bit 12 to Data Bit 1.

2, 4 to 8

3 DVDD Digital Supply Voltage (1.7 V to 3.6 V).

9 DB0 (LSB) Least Significant Data Bit (LSB).

10, 26 DCOM Digital Common.

11 CLKVDD Clock Supply Voltage (1.7 V to 3.6 V).

12 CLK+ Positive Differential Clock Input.

13 CLK− Negative Differential Clock Input.

14 CLKCOM Clock Common.

15 CMODE/SCLK

In pin mode, this pin selects the clock input type. Connect to CLKCOM for single-ended clock receiver

(drive CLK+ and float CLK–). Connect to CLKVDD for differential receiver. In SPI mode, this pin is the serial

data clock input.

16 MODE/SDIO

In pin mode, this pin selects the input data format. Connect to DCOM for straight binary, and DVDD for twos

complement. In SPI mode, this pin acts as SPI data input/output.

17 PIN/SPI/RESET

Selects SPI Mode or Pin Mode Operation. Active high for pin mode operation and active low for SPI mode

operation. Pulse high to reset SPI registers to default values.

18 AVDD Analog Supply Voltage (1.7 V to 3.6 V).

19 OTCM Adjustable Output Common Mode. Refer to the Theory of Operation section for details.

20 IOUTB Complementary DAC Current Output. Full-scale current is sourced when all data bits are 0s.

21 IOUTA DAC Current Output. Full-scale current is sourced when all data bits are 1s.

22 ACOM Analog Common.

23 REFIO

Reference Input/Output. Serves as reference input when internal reference disabled. Serves as 1.0 V

reference output when internal reference is activated. Requires a 0.1 μF capacitor to ACOM when internal

reference is activated.

24 FS ADJ Full-Scale Current Output Adjust.

25 SLEEP/CSB In pin mode, active high powers down chip. In SPI mode, this pin is the serial port chip select (active low).

27 DB13 (MSB) Most Significant Data Bit (MSB).

EPAD

It is recommended that the exposed pad be thermally connected to a copper ground plane for enhanced

electrical and thermal performance.

Rev. B | Page 12 of 44

Data Sheet AD9704/AD9705/AD9706/AD9707

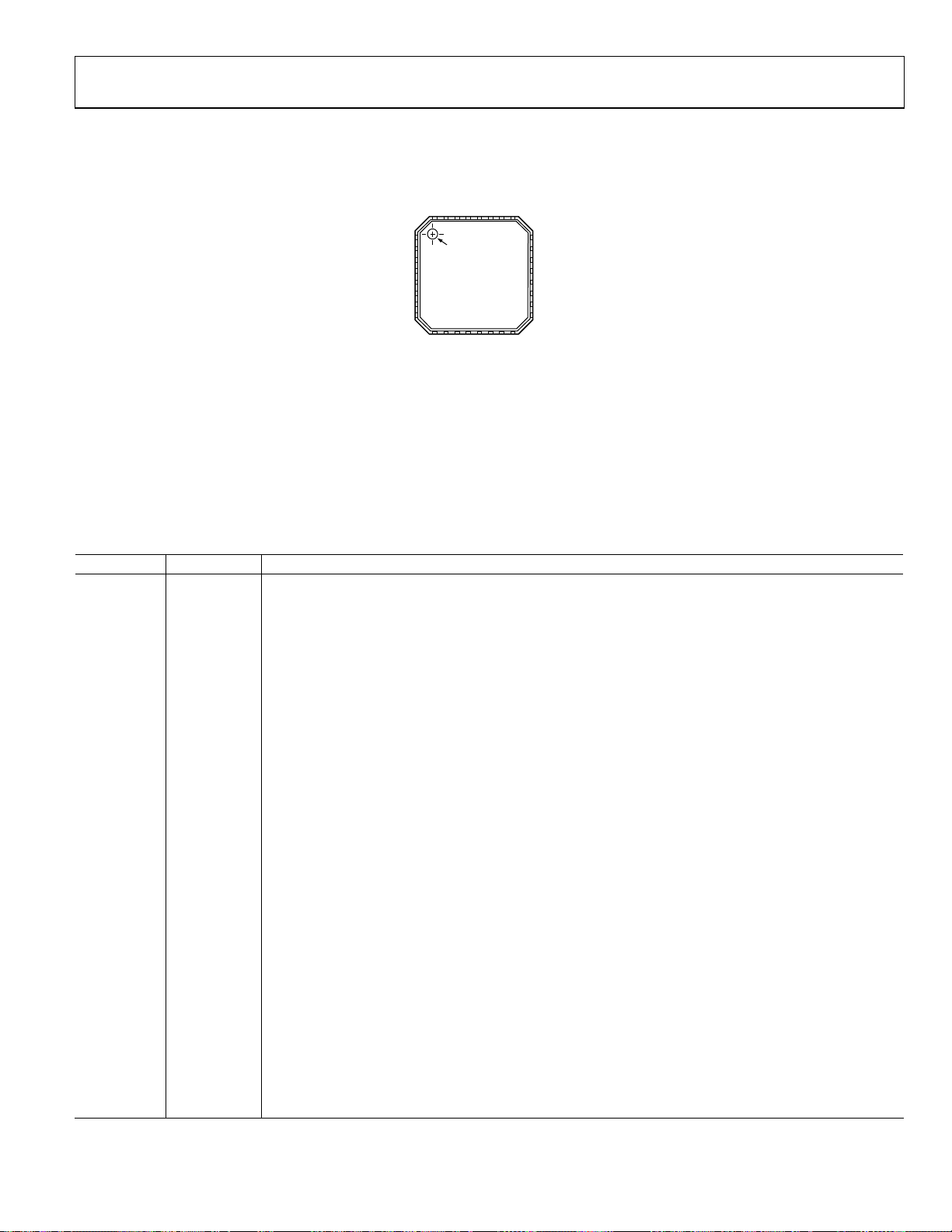

AD9706

SLEEP/CSB

DCOM

DB11 (MSB)

DB10

DB9

DB8

DB7

DB6

30

31

32

1

DB5

DB4

DVDD

DB3

DB2

DB1

DB0 (LSB)

NC

NOTES

1. NC = NO CONNEC T. DO NOT CONNECT TO THIS PIN.

2. IT IS RECOMMENDED T HAT THE EXPOSED PAD BE

THERMALLY CONNECTED TO A COPPER GROUND

PLANE FOR ENHANCED ELECTRICAL AND THERMAL

PERFORMANCE.

2

3

4

5

6

7

8

PIN 1

INDICATO R

AD9706

TOP VIEW

(Not to Scale)

9

11

10

NC

DCOM

CLKVDD

Figure 4. AD9706 Pin Configuration

25

262728

29

24

FS ADJ

23

REFIO

22

ACOM

21

IOUTA

20

IOUTB

19

OTCM

18

AVD D

17

PIN/SPI/RESET

16

151413

12

CLK–

CLK+

CLKCOM

MODE/SDIO

CMODE/SCLK

05926-083

Table 10. AD9706 Pin Function Descriptions

Pin No. Mnemonic Description

28 to 32, 1,

DB10 to DB1 Data Bit 10 to Data Bit 1.

2, 4 to 6

3 DVDD Digital Supply Voltage (1.7 V to 3.6 V).

7 DB0 (LSB) Least Significant Data Bit (LSB).

8, 9 NC No Connect.

10, 26 DCOM Digital Common.

11 CLKVDD Clock Supply Voltage (1.7 V to 3.6 V).

12 CLK+ Positive Differential Clock Input.

13 CLK− Negative Differential Clock Input.

14 CLKCOM Clock Common.

15 CMODE/SCLK

In pin mode, this pin selects the clock input type. Connect to CLKCOM for single-ended clock receiver (drive

CLK+ and float CLK–). Connect to CLKVDD for differential receiver. In SPI mode, this pin is the serial data

clock input.

16 MODE/SDIO

In pin mode, this pin selects the input data format. Connect to DCOM for straight binary, and DVDD for twos

complement. In SPI mode, this pin acts as SPI data input/output.

17 PIN/SPI/RESET

Selects SPI Mode or Pin Mode Operation. Active high for pin mode operation, and active low for SPI mode

operation. Pulse high to reset SPI registers to default values.

18 AVDD Analog Supply Voltage (1.7 V to 3.6 V).

19 OTCM Adjustable Output Common Mode. Refer to the Theory of Operation section for details.

20 IOUTB Complementary DAC Current Output. Full-scale current is sourced when all data bits are 0s.

21 IOUTA DAC Current Output. Full-scale current is sourced when all data bits are 1s.

22 ACOM Analog Common.

23 REFIO

Reference Input/Output. Serves as reference input when internal reference disabled. Serves as 1.0 V

reference output when internal reference is activated. Requires a 0.1 μF capacitor to ACOM when internal

reference is activated.

24 FS ADJ Full-Scale Current Output Adjust.

25 SLEEP/CSB In pin mode, active high powers down chip. In SPI mode, this pin is the serial port chip select (active low).

27 DB11 (MSB) Most Significant Data Bit (MSB).

EPAD

It is recommended that the exposed pad be thermally connected to a copper ground plane for enhanced

electrical and thermal performance.

Rev. B | Page 13 of 44

AD9704/AD9705/AD9706/AD9707 Data Sheet

2

AD9705

SLEEP/CSB

DCOM

DB9 (MSB)

DB8

DB7

DB6

DB5

DB4

30

31

32

1

DB3

DB2

DVDD

DB1

DB0 (LSB)

NC

NC

NC

NOTES

1. NC = NO CONNECT. DO NOT CONNECT TO THIS PIN.

. IT IS RECOMMENDED THAT THE EXPOS ED PAD BE

THERMALLY CONNECTED TO A COPPER GROUND

PLANE FOR ENHANCED ELECTRICAL AND THERMAL

PERFORMANCE.

2

3

4

5

6

7

8

PIN 1

INDICATO R

AD9705

TOP VIEW

(Not to Scale)

9

11

10

NC

DCOM

CLKVDD

Figure 5. AD9705 Pin Configuration

25

26

272829

24

FS ADJ

23

REFIO

22

ACOM

21

IOUTA

20

IOUTB

19

OTCM

18

AVD D

17

PIN/SPI/RESET

16

15

141312

CLK–

CLK+

CLKCOM

MODE/SDIO

CMODE/SCLK

05926-085

Table 11. AD9705 Pin Function Descriptions

Pin No. Mnemonic Description

28 to 32,

DB8 to DB1 Data Bit 8 to Data Bit 1.

1, 2, 4

3 DVDD Digital Supply Voltage (1.7 V to 3.6 V).

5 DB0 (LSB) Least Significant Data Bit (LSB).

6 to 9 NC No Connect.

10, 26 DCOM Digital Common.

11 CLKVDD Clock Supply Voltage (1.7 V to 3.6 V).

12 CLK+ Positive Differential Clock Input.

13 CLK− Negative Differential Clock Input.

14 CLKCOM Clock Common.

15 CMODE/SCLK

In pin mode, this pin selects the clock input type. Connect to CLKCOM for single-ended clock receiver (drive

CLK+ and float CLK–). Connect to CLKVDD for differential receiver. In SPI mode, this pin is the serial data clock input.

16 MODE/SDIO

In pin mode, this pin selects the input data format. Connect to DCOM for straight binary, and DVDD for twos

complement. In SPI mode, this pin acts as SPI data input/output.

17 PIN/SPI/RESET

Selects SPI Mode or Pin Mode Operation. Active high for pin mode operation and active low for SPI mode

operation. Pulse high to reset SPI registers to default values.

18 AVDD Analog Supply Voltage (1.7 V to 3.6 V).

19 OTCM Adjustable Output Common Mode. Refer to the Theory of Operation section for details.

20 IOUTB Complementary DAC Current Output. Full-scale current is sourced when all data bits are 0s.

21 IOUTA DAC Current Output. Full-scale current is sourced when all data bits are 1s.

22 ACOM Analog Common.

23 REFIO

Reference Input/Output. Serves as reference input when internal reference disabled. Serves as 1.0 V reference

output when internal reference is activated. Requires a 0.1 μF capacitor to ACOM when internal reference is activated.

24 FS ADJ Full-Scale Current Output Adjust.

25 SLEEP/CSB In pin mode, active high powers down chip. In SPI mode, this pin is the serial port chip select (active low).

27 DB9 (MSB) Most Significant Data Bit (MSB).

EPAD

It is recommended that the exposed pad be thermally connected to a copper ground plane for enhanced

electrical and thermal performance.

Rev. B | Page 14 of 44

Loading...

Loading...