ANALOG DEVICES AD9644 Service Manual

14-Bit, 80 MSPS/155 MSPS, 1.8 V Dual

A

A

Serial Output Analog-to-Digital Converter (ADC)

FEATURES

JESD204A coded serial digital outputs

SNR = 73.7 dBFS at 70 MHz and 80 MSPS

SNR = 71.7 dBFS at 70 MHz and 155 MSPS

SFDR = 92 dBc at 70 MHz and 80 MSPS

SFDR = 92 dBc at 70 MHz and 155 MSPS

Low power: 423 mW at 80 MSPS, 567 mW at 155 MSPS

1.8 V supply operation

Integer 1-to-8 input clock divider

IF sampling frequencies to 250 MHz

−148.6 dBFS/Hz input noise at 180 MHz and 80 MSPS

−150.3 dBFS/Hz input noise at 180 MHz and 155 MSPS

Programmable internal ADC voltage reference

Flexible analog input range: 1.4 V p-p to 2.1 V p-p

ADC clock duty cycle stabilizer

Serial port control

User-configurable, built-in self-test (BIST) capability

Energy-saving power-down modes

APPLICATIONS

Communications

Diversity radio systems

Multimode digital receivers (3G and 4G)

GSM, EDGE, W-CDMA, LTE,

CDMA2000, WiMAX, TD-SCDMA

I/Q demodulation systems

Smart antenna systems

General-purpose software radios

Broadband data applications

Ultrasound equipment

AD9644

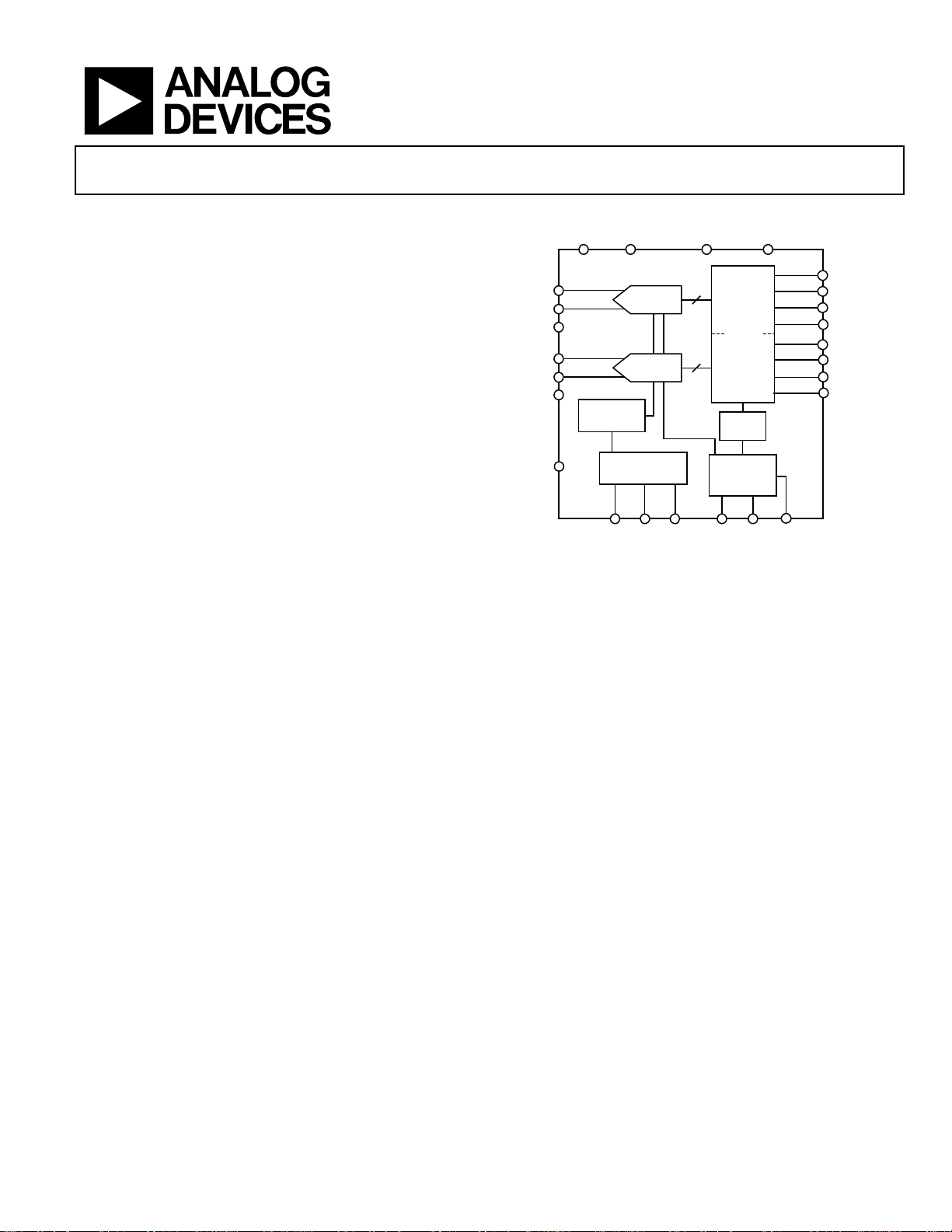

FUNCTIONAL BLOCK DIAGRAM

VDD

GND

AD9644

VIN+A

VIN–A

VCMA

VIN+B

VIN–B

VCMB

PDWN

PIPELINE

14-BIT ADC

PIPELINE

14-BIT ADC

REFERENCE

SERIAL PORT

(SPI)

SCLK SDIO CSB

Figure 1. 48-Lead 7 mm × 7 mm LFCSP

PRODUCT HIGHLIGHTS

1. An on-chip PLL allows users to provide a single ADC

sampling clock; the PLL multiplies the ADC sampling

clock to produce the corresponding JESD204A data rate

clock.

2. The configurable JESD204A output block supports up to

1.6 Gbps per channel data rate when using a dedicated

data link per ADC or 3.2 Gbps data rate when using a

single shared data link for both ADCs.

3. Proprietary differential input that maintains excellent SNR

performance for input frequencies up to 250 MHz.

4. Operation from a single 1.8 V power supply.

5. Standard serial port interface (SPI) that supports various

product features and functions, such as data formatting

(offset binary, twos complement, or gray coding),

controlling the clock DCS, power-down, test modes,

voltage reference mode, and serial output configuration.

DRVDD DRGND

14

14

JESD204A 8-BIT/ 10-BIT

CODING, SE RIALIZER AND

PLL

1 TO 8

CLOCK

DIVIDER

CLK+ CLK–

CML DRIVERS

DOUT+A

DOUT–A

DSYNC+A

DSYNC–A

DOUT+B

DOUT–B

DSYNC+B

DSYNC–B

SYNC

9180-001

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010–2011 Analog Devices, Inc. All rights reserved.

AD9644

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

General Description ......................................................................... 3

Specifications..................................................................................... 4

ADC DC Specifications................................................................. 4

ADC AC Specifications ................................................................. 5

Digital Specifications ................................................................... 6

Switching Specifications................................................................ 8

Timing Specifications .................................................................. 9

Absolute Maximum Ratings.......................................................... 10

Thermal Characteristics ................................................................ 10

ESD Caution................................................................................ 10

Pin Configuration and Function Descriptions........................... 11

Typical Performance Characteristics ........................................... 13

Equivalent Circuits......................................................................... 19

Theory of Operation ...................................................................... 20

ADC Architecture ......................................................................20

Analog Input Considerations.................................................... 20

Voltage Reference ....................................................................... 22

Clock Input Considerations...................................................... 22

Channel/Chip Synchronization................................................ 24

Power Dissipation and Standby Mode .................................... 24

Digital Outputs........................................................................... 24

Built-In Self-Test (BIST) and Output Test .................................. 29

Built-In Self-Test (BIST)............................................................ 29

Output Test Modes..................................................................... 29

Serial Port Interface (SPI).............................................................. 31

Configuration Using the SPI..................................................... 31

Hardware Interface..................................................................... 32

SPI Accessible Features.............................................................. 32

Memory Map .................................................................................. 33

Reading the Memory Map Register Table............................... 33

Memory Map Register Table..................................................... 34

Memory Map Register Descriptions........................................ 38

Applications Information.............................................................. 42

Design Guidelines ...................................................................... 42

Outline Dimensions....................................................................... 43

Ordering Guide .......................................................................... 43

REVISION HISTORY

6/11—Rev. A to Rev. B

Added Figure 23 to Figure 40; Renumbered Sequentially ........ 16

Changes to Clock Input Considerations Section........................ 22

Added Figure 61.............................................................................. 24

Changes to Digital Outputs and Timing Section ....................... 27

Added Figure 69.............................................................................. 28

Changes to Output Test Modes Section ...................................... 29

Changes to SPI Accessible Features Section ............................... 32

4/11—Rev. 0 to Rev. A

Added Model -155......................................................... Throughout

Changes to Features Section and Figure 1 .....................................1

Changes to General Description Section .......................................3

Changes to Table 1.............................................................................4

Changes to Table 2.............................................................................5

Changes to Table 4.............................................................................8

Additions to TPC Introductory Statement ................................. 13

Changes to Speed Grade ID Bits in Table 17 .............................. 31

Changes to Ordering Guide.......................................................... 40

6/10—Revision 0: Initial Version

Rev. B | Page 2 of 44

AD9644

GENERAL DESCRIPTION

The AD9644 is a dual, 14-bit, analog-to-digital converter (ADC)

with a high speed serial output interface and sampling speeds

of either 80 MSPS or 155 MSPS.

The AD9644 is designed to support communications applications where high performance, combined with low cost, small

size, and versatility, is desired. The JESD204A high speed serial

interface reduces board routing requirements and lowers pin count

requirements for the receiving device.

The dual ADC core features a multistage, differential pipelined

architecture with integrated output error correction logic. Each

ADC features wide bandwidth differential sample-and-hold

analog input amplifiers that support a variety of user-selectable

input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for

variations in the ADC clock duty cycle, allowing the converters

to maintain excellent performance.

By default the ADC output data is routed directly to the two

external JESD204A serial output ports. These outputs are at CML

voltage levels. Two modes are supported such that output coded

data is either sent through one data link or two. (L = 1; F = 4 or

L = 2; F = 2). Independent synchronization inputs (DSYNC) are

provided for each channel.

Flexible power-down options allow significant power savings,

when desired.

Programming for setup and control is accomplished using a 3-wire

SPI-compatible serial interface.

The AD9644 is available in a 48-lead LFCSP and is specified over

the industrial temperature range of −40°C to +85°C.

Rev. B | Page 3 of 44

AD9644

SPECIFICATIONS

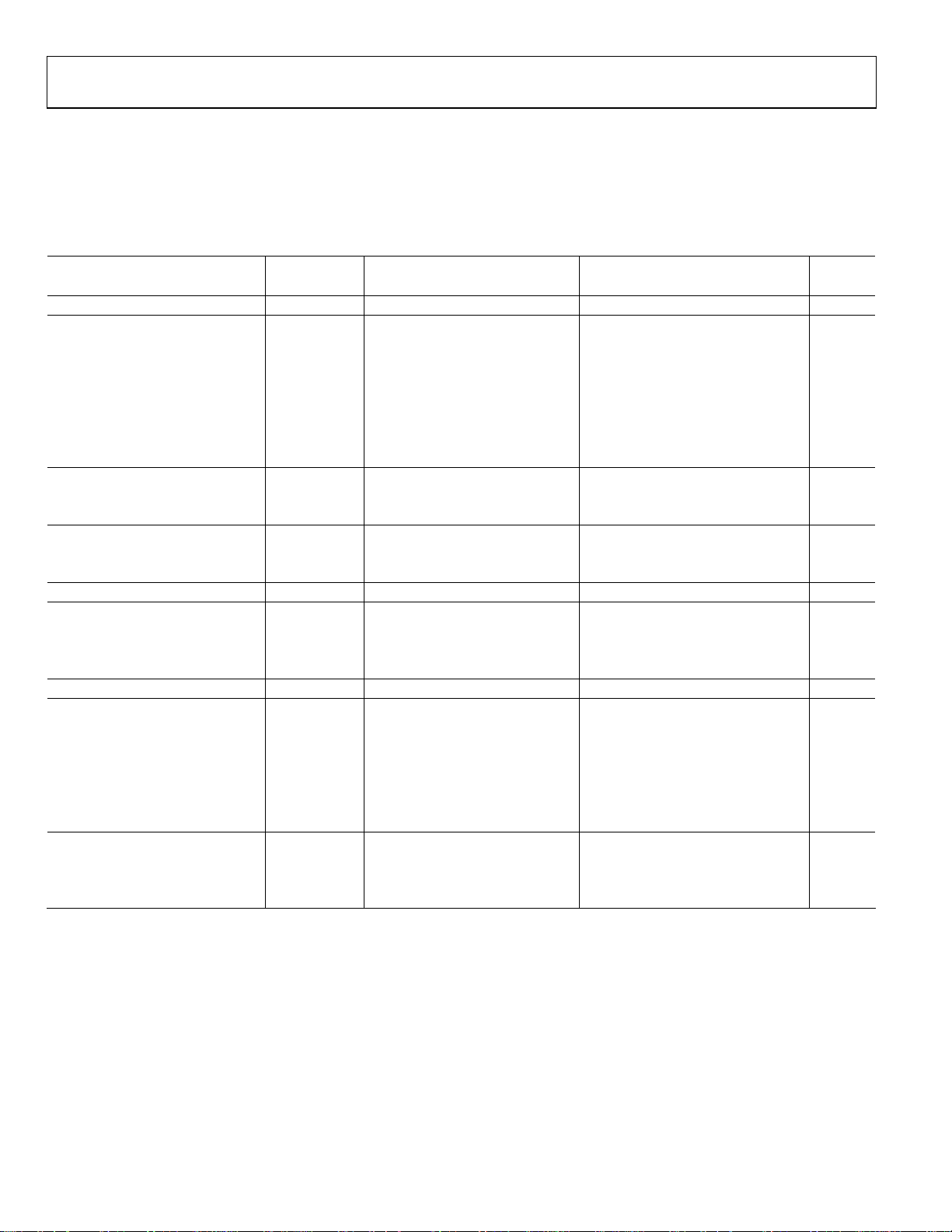

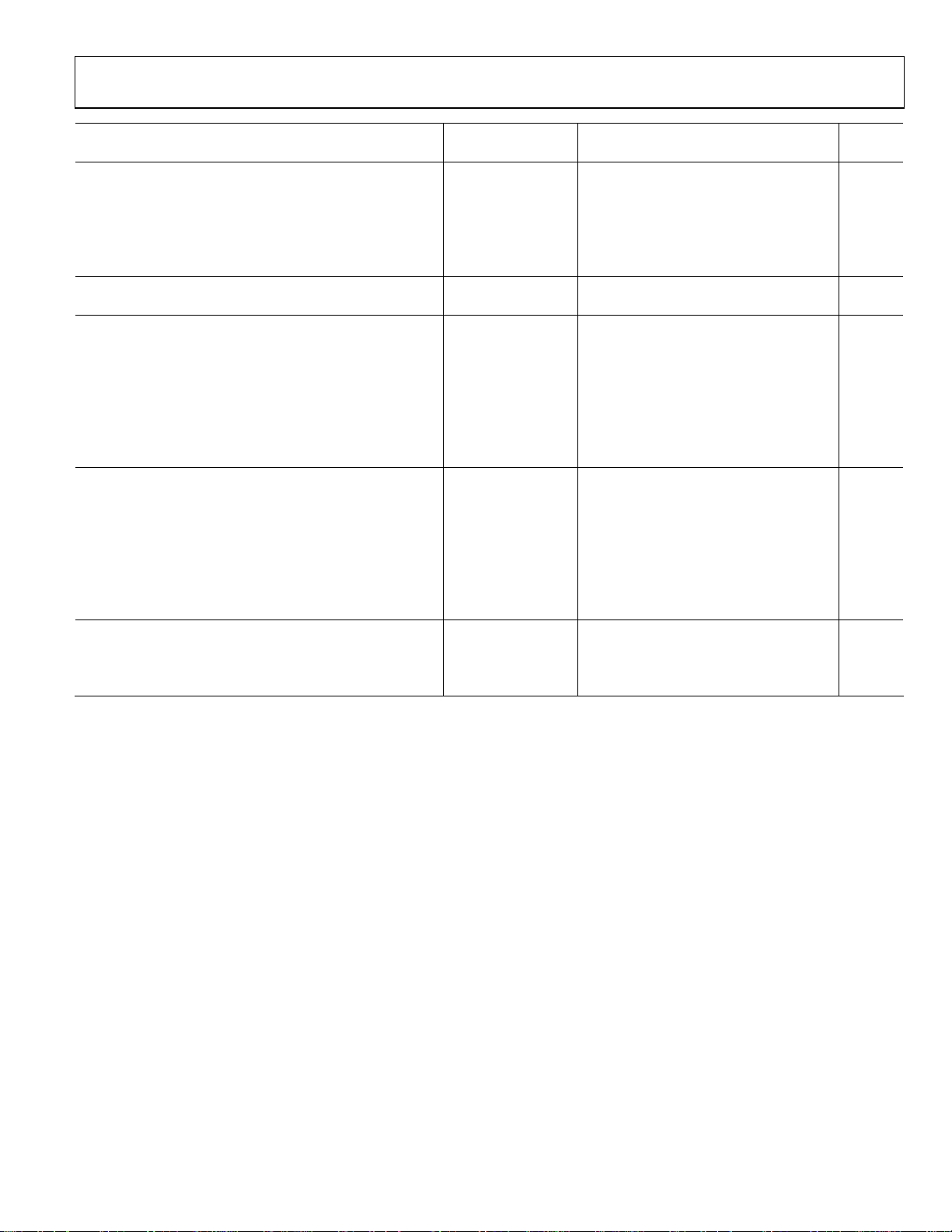

ADC DC SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, maximum sample rate, 1.75 V p-p differential input, VIN = −1.0 dBFS differential input, DCS enabled,

unless otherwise noted.

Table 1.

AD9644-80 AD9644-155

Parameter Temperature Min Typ Max Min Typ Max Unit

RESOLUTION Full 14 14 Bits

ACCURACY

No Missing Codes Full Guaranteed Guaranteed

Offset Error Full ±2 ±10 ±2.2 ±11 mV

Gain Error Full −7 −2.5 +1 −6 −1.5 +4 % FSR

Differential Nonlinearity (DNL)1 Full ±0.55 ±0.55 LSB

25°C ±0.3 ±0.3 LSB

Integral Nonlinearity (INL)1 Full ±1.1 ±1.25 LSB

25°C ±0.5 ±0.55 LSB

MATCHING CHARACTERISTIC

Offset Error Full −7 +1.5 +10 −6 +1.5 +9 mV

Gain Error Full −1.5 +0.6 +2.75 −3.1 +0.75 +5 % FSR

TEMPERATURE DRIFT

Offset Error Full ±2 ±2 ppm/°C

Gain Error Full ±35 ±144 ppm/°C

INPUT REFERRED NOISE 25°C 0.7 0.7 LSB rms

ANALOG INPUT

Input Span Full 1.383 1.75 2.087 1.383 1.75 2.087 V p-p

Input Capacitance2 Full 7 5 pF

Input Resistance Full 20 20 kΩ

VCM OUTPUT LEVEL Full 0.88 0.9 0.92 0.87 0.9 0.93 V

POWER SUPPLIES

Supply Voltage

AVDD Full 1.7 1.8 1.9 1.7 1.8 1.9 V

DRVDD Full 1.7 1.8 1.9 1.7 1.8 1.9 V

Supply Current

IAVDD1 Full 175 190 226 242 mA

IDRVDD1 Full 60 67 89 97 mA

POWER CONSUMPTION

Sine Wave Input1 Full 423 460 567 610 mW

Standby Power3 Full 85 168 mW

Power-Down Power Full 15 27 18 27 mW

1

Measured with a low input frequency, full-scale sine wave.

2

Input capacitance refers to the effective capacitance between one differential input pin and AGND.

3

Standby power is measured with a dc input and with the CLK pins inactive (set to AVDD or AGND).

Rev. B | Page 4 of 44

AD9644

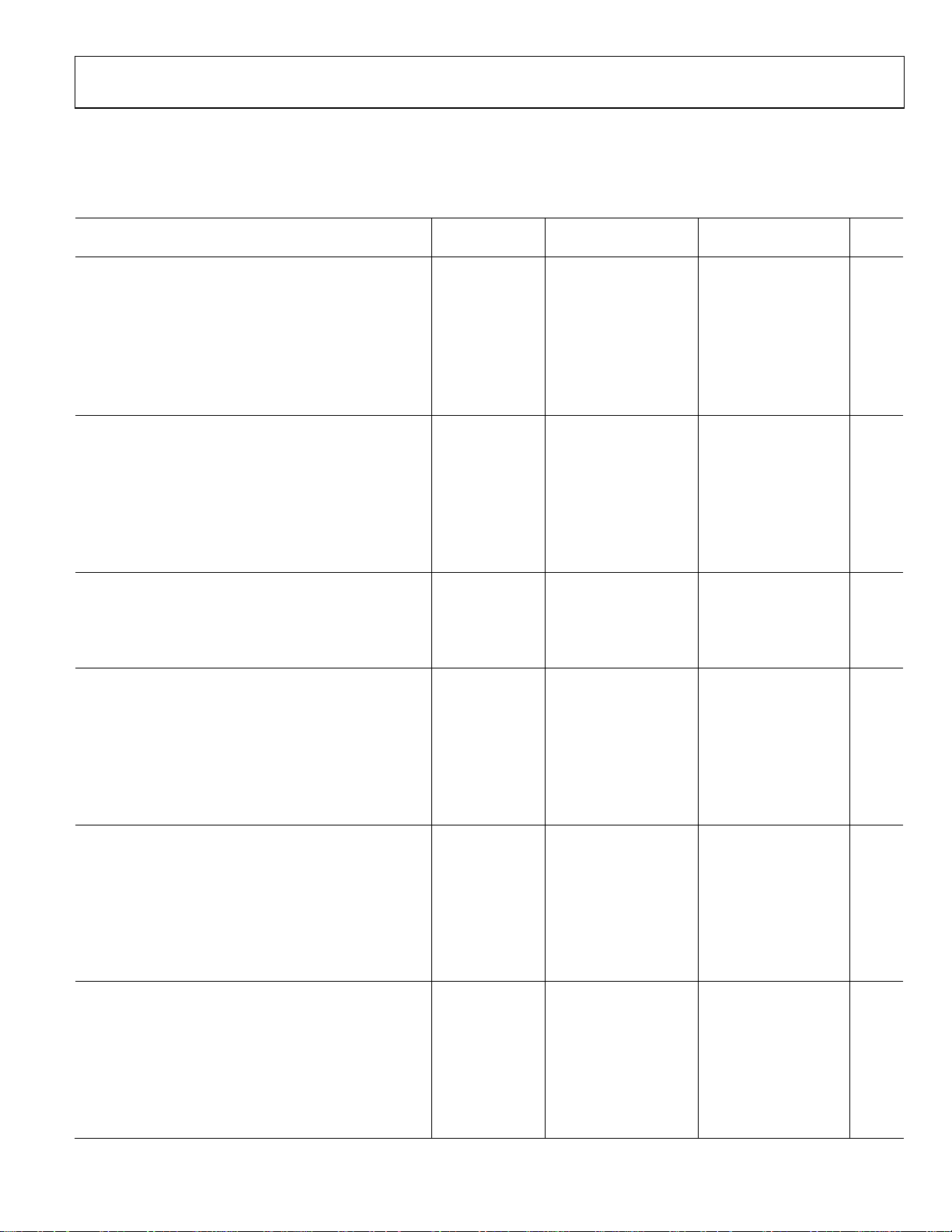

ADC AC SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, maximum sample rate, 1.75 V p-p differential input, VIN = −1.0 dBFS differential input, DCS enabled,

unless otherwise noted.

Table 2.

AD9644-80 AD9644-155

Parameter1 Temperature Min Typ Max Min Typ Max Unit

SIGNAL-TO-NOISE-RATIO (SNR)

fIN = 10 MHz 25°C 73.8 71.9 dBFS

fIN = 70 MHz 25°C 73.7 71.7 dBFS

fIN = 180 MHz

AD9644BCPZ-80

AD9644CCPZ-80

AD9644BCPZ-155

fIN = 220 MHz 25°C 72.0 71.0 dBFS

SIGNAL-TO-NOISE AND DISTORTION (SINAD)

fIN = 10 MHz 25°C 72.7 70.8 dBFS

fIN = 70 MHz 25°C 72.6 70.7 dBFS

fIN = 180 MHz 25°C 71.5 70.3 dBFS

AD9644BCPZ-80

AD9644CCPZ-80

AD9644BCPZ-155

fIN = 220 MHz 25°C 71.1 69.9 dBFS

EFFECTIVE NUMBER OF BITS (ENOB)

fIN = 10 MHz

fIN = 70 MHz

fIN = 180 MHz

fIN = 220 MHz

WORST SECOND OR THIRD HARMONIC

fIN = 10 MHz

fIN = 70 MHz

fIN = 180 MHz

AD9644BCPZ-80

AD9644CCPZ-80

AD9644BCPZ-155

fIN = 220 MHz

SPURIOUS-FREE DYNAMIC RANGE (SFDR)

fIN = 10 MHz

fIN = 70 MHz

fIN = 180 MHz

AD9644BCPZ-80

AD9644CCPZ-80

AD9644BCPZ-155

fIN = 220 MHz

WORST OTHER (HARMONIC OR SPUR)

fIN = 10 MHz

fIN = 70 MHz

fIN = 180 MHz

AD9644BCPZ-80

AD9644CCPZ-80

AD9644BCPZ-155

fIN = 220 MHz

25°C 72.6 71.4 dBFS

Full 71.8 dBFS

Full 70.0 dBFS

Full 69.8 dBFS

Full 70.4 dBFS

Full 68.6 dBFS

Full 68.7 dBFS

25°C

25°C

25°C

25°C

25°C

25°C

25°C

Full

−94

−92

−87

−80

Full −73

Full

25°C

25°C

25°C

25°C

Full

−85

94

92

87

80

Full 73

Full

25°C

25°C

25°C

25°C

Full

Full

Full

25°C

85

−98

−98

−96

−90

−87

−95

11.8

11.8

11.6

11.5

11.5 Bits

11.5 Bits

11.4 Bits

11.3 Bits

−94 dBc

−92

−92 dBc

dBc

dBc

dBc

−90

−80

dBc

dBc

94 dBc

92 dBc

92 dBc

dBc

dBc

80 dBc

90 dBc

−97

−97

−95

dBc

dBc

dBc

dBc

dBc

−94

−89

dBc

dBc

Rev. B | Page 5 of 44

AD9644

AD9644-80 AD9644-155

Parameter1 Temperature Min Typ Max Min Typ Max Unit

TWO-TONE SFDR

fIN = +30 MHz (−7 dBFS ), +33 MHz (−7 dBFS )

fIN = +169 MHz (−7 dBFS ), +172 MHz (−7 dBFS )

CROSSTALK2

ANALOG INPUT BANDWIDTH3

1

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

2

Crosstalk is measured at 100 MHz with −1.0 dBFS on one channel and no input on the alternate channel.

3

Analog input bandwidth specifies the −3 dB input BW of the AD9644 input. The usable full-scale BW of the part with good performance is 250 MHz.

25°C

25°C

Full

25°C

93

89

−105

780

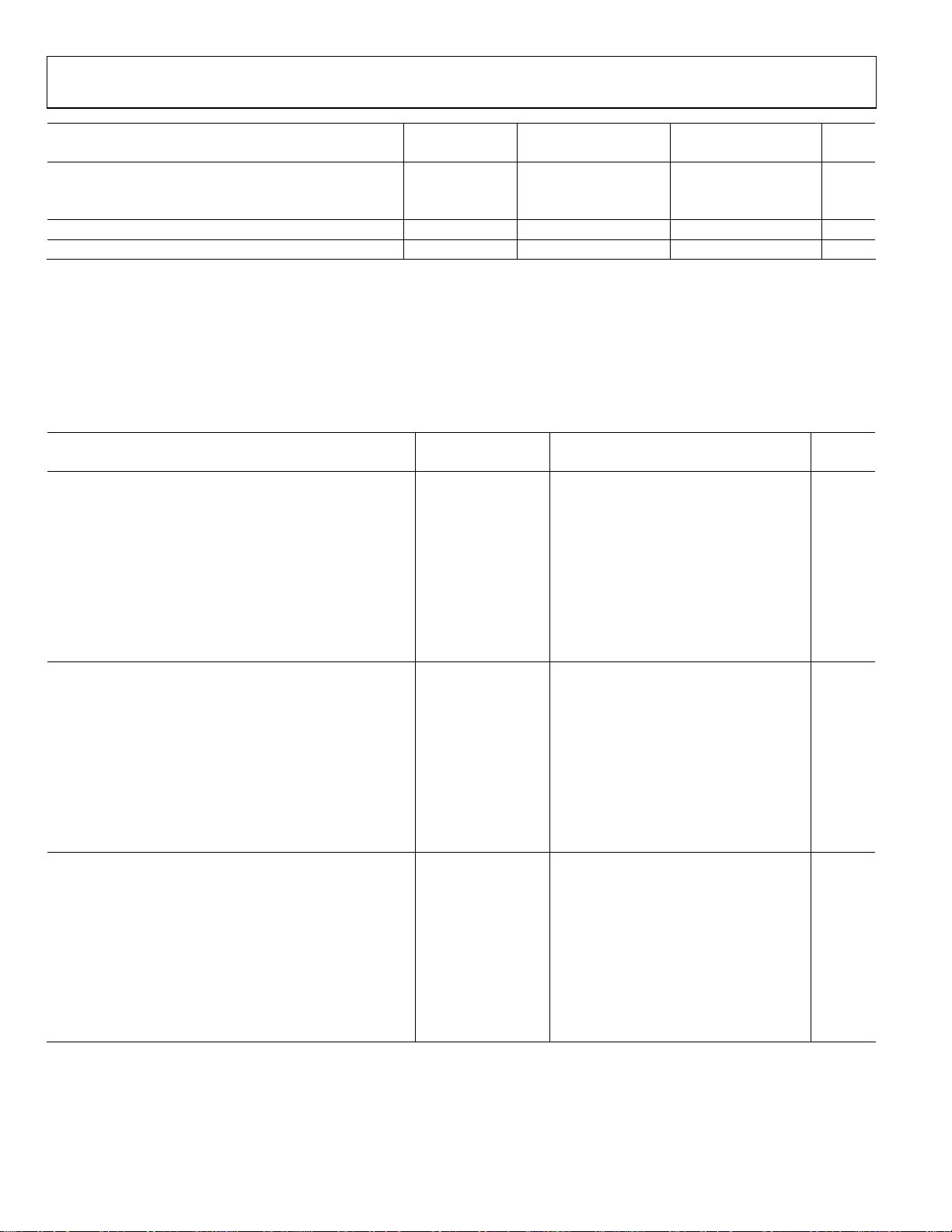

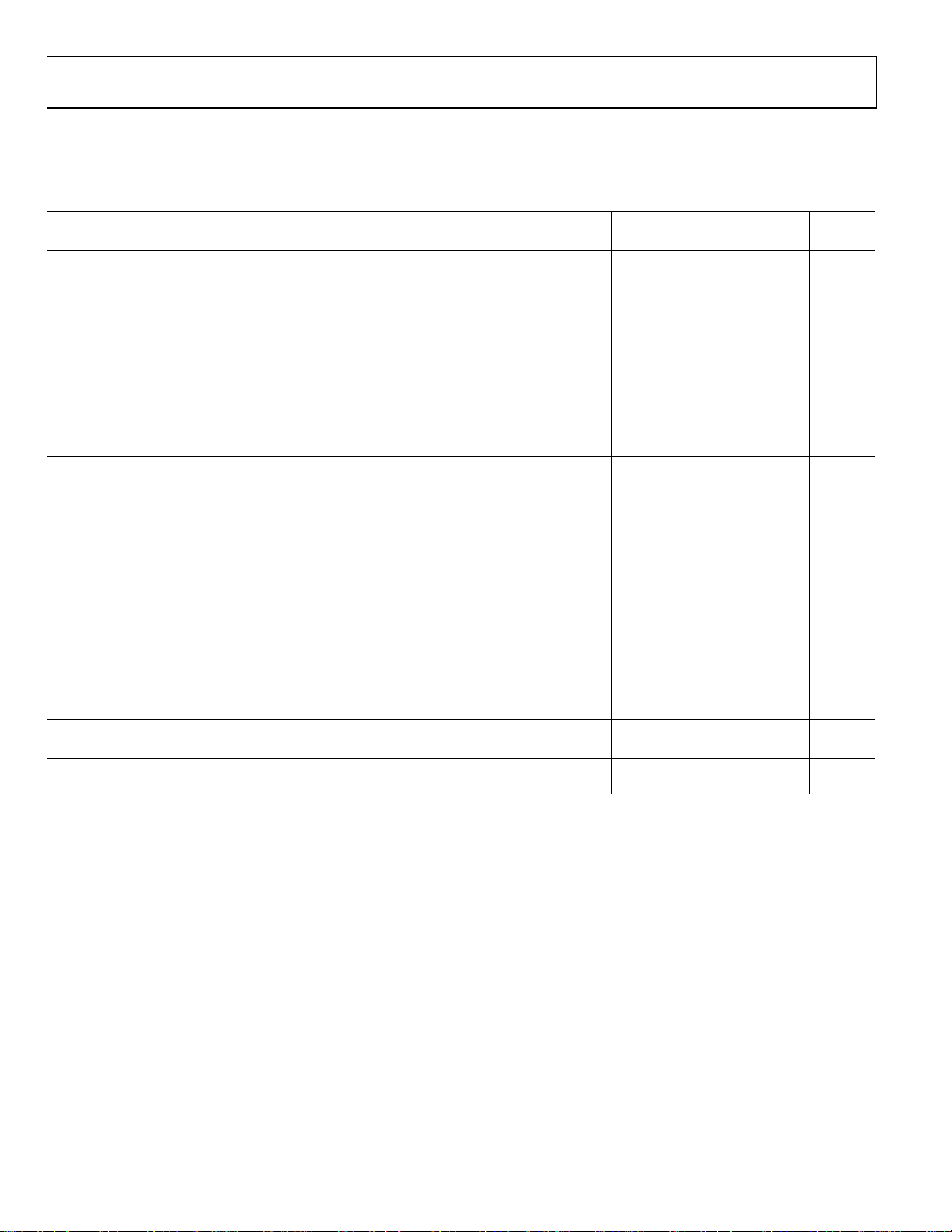

DIGITAL SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, maximum sample rate, 1.75 V p-p differential input, VIN = −1.0 dBFS differential input, and DCS enabled,

unless otherwise noted.

Table 3.

AD9644-80/AD9644-155

Parameter Temperature Min Typ Max Unit

DIFFERENTIAL CLOCK INPUTS (CLK+, CLK−)

Logic Compliance CMOS/LVDS/LVPECL

Internal Common-Mode Bias Full 0.9 V

Differential Input Voltage Full 0.3 3.6 V p-p

Input Voltage Range Full AGND AVDD V

Input Common-Mode Range Full 0.9 1.4 V

High Level Input Current Full −100 +100 μA

Low Level Input Current Full −100 +100 μA

Input Capacitance Full 4 pF

Input Resistance Full 8 10 12 kΩ

SYNC INPUT

Logic Compliance CMOS

Internal Bias Full 0.9 V

Input Voltage Range Full AGND AVDD V

High Level Input Voltage Full 1.2 AVDD V

Low Level Input Voltage Full AGND 0.6 V

High Level Input Current Full −100 +100 μA

Low Level Input Current Full −100 +100 μA

Input Capacitance Full 1 pF

Input Resistance Full 12 16 20 kΩ

DSYNC INPUT

Logic Compliance CMOS/LVDS

Internal Bias Full 0.9 V

Input Voltage Range Full AGND AVDD V

High Level Input Voltage Full 1.2 AVDD V

Low Level Input Voltage Full AGND 0.6 V

High Level Input Current Full −100 +100 μA

Low Level Input Current Full −100 +100 μA

Input Capacitance Full 1 pF

Input Resistance Full 12 16 20 kΩ

90 dBc

89 dBc

−105 dB

780 MHz

Rev. B | Page 6 of 44

AD9644

AD9644-80/AD9644-155

Parameter Temperature Min Typ Max Unit

LOGIC INPUT (CSB)1

Logic Compliance CMOS

High Level Input Voltage Full 1.22 2.1 V

Low Level Input Voltage Full 0 0.6 V

High Level Input Current Full −10 +10 μA

Low Level Input Current Full 40 132 μA

Input Resistance Full 26 kΩ

Input Capacitance Full 2 pF

LOGIC INPUT (SCLK, PDWN)2

Logic Compliance CMOS

High Level Input Voltage Full 1.22 2.1 V

Low Level Input Voltage Full 0 0.6 V

High Level Input Current (VIN = 1.8 V) Full −92 −135 μA

Low Level Input Current Full −10 +10 μA

Input Resistance Full 26 kΩ

Input Capacitance Full 2 pF

LOGIC INPUT/OUTPUT (SDIO)1

Logic Compliance CMOS

High Level Input Voltage Full 1.22 2.1 V

Low Level Input Voltage Full 0 0.6 V

High Level Input Current Full −10 +10 μA

Low Level Input Current Full 38 128 μA

Input Resistance Full 26 kΩ

Input Capacitance Full 5 pF

DIGITAL OUTPUTS

Logic Compliance Full CML

Differential Output Voltage (VOD) Full 0.6 0.8 1.1 V

Output Offset Voltage (VOS) Full 0.75 DRVDD/2 1.05 V

1

Pull up.

2

Pull down.

Rev. B | Page 7 of 44

AD9644

SWITCHING SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, maximum sample rate, 1.75 V p-p differential input, VIN = −1.0 dBFS differential input, and DCS enabled,

unless otherwise noted.

Table 4.

AD9644-80 AD9644-155

Parameter Temperature Min Typ Max Min Typ Max Unit

CLOCK INPUT PARAMETERS

Input Clock Rate Full 640 640 MHz

Conversion Rate1 Full 40 80 40 155 MSPS

CLK Period—Divide-by-1 Mode (t

CLK Pulse Width High (tCH)

Divide-by-1 Mode, DCS Enabled Full 3.75 6.25 8.75 1.935 3.225 4.515 ns

Divide-by-1 Mode, DCS Disabled Full 5.95 6.25 6.55 3.065 3.225 3.385 ns

Divide-by-2 Mode Through Divide-by-8

Mode

Aperture Delay (tA) Full 0.78 0.78 ns

Aperture Uncertainty (Jitter, tJ) Full 0.125 0.125 ps rms

DATA OUTPUT PARAMETERS

Data Output Period or UI (Unit Interval) Full 1/(20 × f

Data Output Duty Cycle

Data Valid Time

PLL Lock Time (t

LOCK

)

Wake Up Time (Standby)

Wake Up Time (Power-Down)2 25°C 2.5 2.5 ms

Pipeline Delay (Latency) Full 23 24 23 24

Data Rate per Channel (NRZ)

Deterministic Jitter

Random Jitter at 1.6 Gbps

Random Jitter at 3.2 Gbps

Output Rise/Fall Time

TERMINATION CHARACTERISTICS

Differential Termination Resistance

OUT-OF-RANGE RECOVERY TIME

1

Conversion rate is the clock rate after the divider.

2

Wake-up time is defined as the time required to return to normal operation from power-down mode.

) Full 12.5 6.45 ns

CLK

Full 0.8 0.8 ns

25°C

25°C

25°C

25°C

) 1/(20 × f

CLK

50

50 %

0.78 0.74 UI

4 4 μs

5

5 μs

) Seconds

CLK

CLK

cycles

25°C

25°C

25°C

25°C

25°C

25°C

25°C

1.6 3.1 Gbps

40 40 ps

9.5 ps rms

5.2 5.2 ps rms

50 50 ps

100 100 Ω

2 2

CLK

cycles

Rev. B | Page 8 of 44

AD9644

A

G

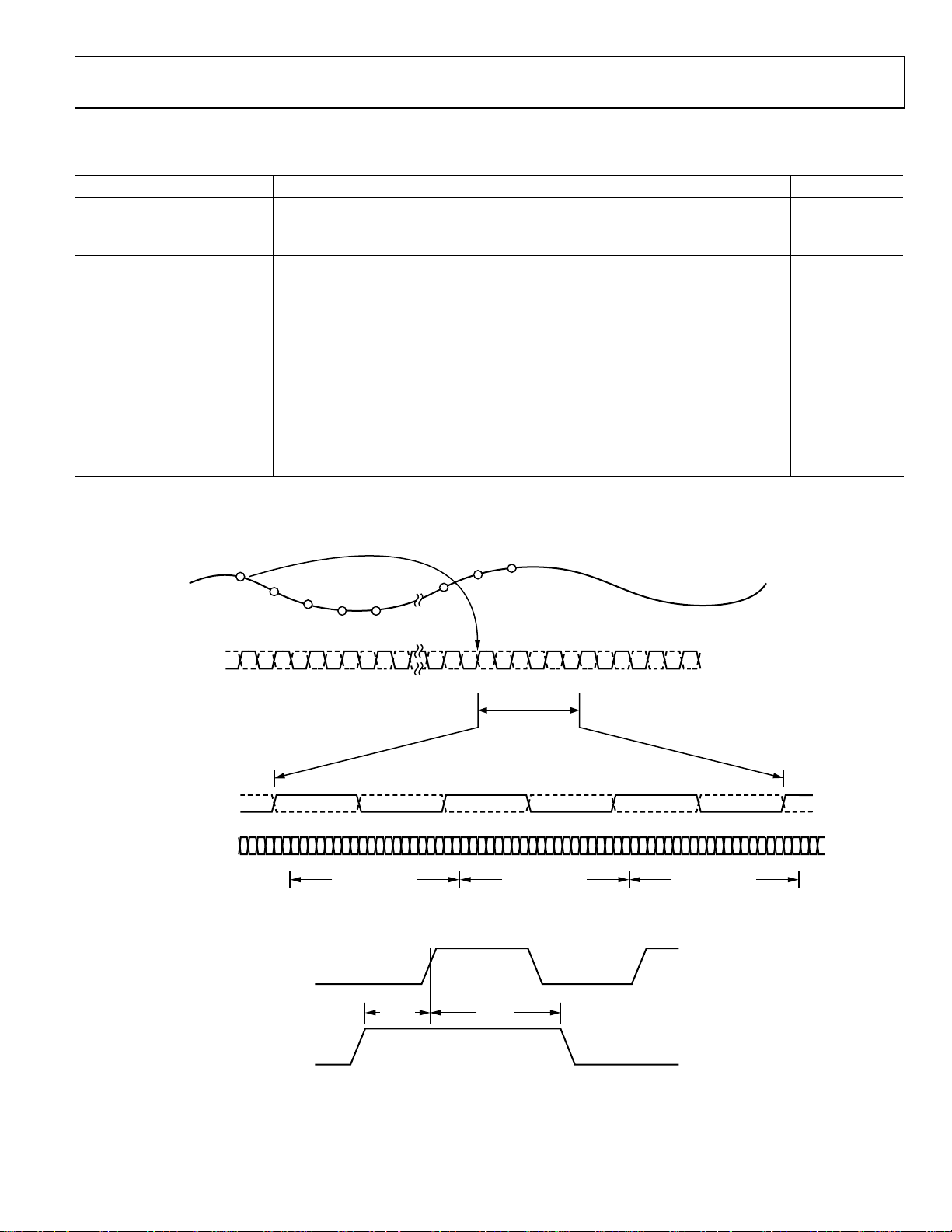

TIMING SPECIFICATIONS

Table 5.

Parameter Conditions Limit

SYNC TIMING REQUIREMENTS

t

SYNC to rising edge of CLK+ setup time 0.30 ns typ

SSYNC

t

SYNC to rising edge of CLK+ hold time 0.30 ns typ

HSYNC

SPI TIMING REQUIREMENTS

tDS Setup time between the data and the rising edge of SCLK 2 ns min

tDH Hold time between the data and the rising edge of SCLK 2 ns min

t

Period of the SCLK 40 ns min

CLK

tS Setup time between CSB and SCLK 2 ns min

tH Hold time between CSB and SCLK 2 ns min

t

SCLK pulse width high 10 ns min

HIGH

t

SCLK pulse width low 10 ns min

LOW

t

EN_SDIO

t

DIS_SDIO

Timing Diagrams

NALO

INPUT

SIGNAL

N – 23

Time required for the SDIO pin to switch from an input to an output relative to the SCLK

falling edge

Time required for the SDIO pin to switch from an output to an input relative to the SCLK

rising edge

SAMPLE

N – 22

N – 21

N – 20

N

N + 1

N – 1

10 ns min

10 ns min

CLK–

CLK+

CLK–

CLK+

DOUT+

DOUT–

SAMPLE N – 23

ENCODED INTO 2

8b/10b SYMBOLS

SAMPLE N – 22

ENCODED INTO 2

8b/10b SYMBOLS

SAMPLE N – 21

ENCODED INTO 2

8b/10b SYMBOLS

09180-002

Figure 2. Data Output Timing

CLK+

t

HSYNC

09180-004

SYNC

t

SSYNC

Figure 3. SYNC Input Timing Requirements

Rev. B | Page 9 of 44

AD9644

ABSOLUTE MAXIMUM RATINGS

Table 6.

Parameter Rating

ELECTRICAL

AVDD to AGND −0.3 V to +2.0 V

DRVDD to AGND −0.3 V to +2.0V

VIN+A/VIN+B, VIN−A/VIN−B to AGND −0.3 V to AVDD + 0.2 V

CLK+, CLK− to AGND −0.3 V to AVDD + 0.2 V

SYNC to AGND −0.3 V to AVDD + 0.2 V

VCMA, VCMB to AGND −0.3 V to AVDD + 0.2 V

CSB to AGND −0.3 V to DRVDD + 0.2 V

SCLK to AGND −0.3 V to DRVDD + 0.2 V

SDIO to AGND −0.3 V to DRVDD + 0.2 V

PDWN to AGND −0.3 V to DRVDD + 0.2 V

DOUT+A, DOUT0−A, DOUT0+B,

DOUT−B to AGND

DSYNC+A, DSYNC−A, DSYNC+B,

DSYNC−B to AGND

−0.3 V to DRVDD + 0.2 V

−0.3 V to DRVDD + 0.2 V

ENVIRONMENTAL

Operating Temperature Range

−40°C to +85°C

(Ambient)

Maximum Junction Temperature

150°C

Under Bias

Storage Temperature Range

−65°C to +150°C

(Ambient)

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

The exposed paddle must be soldered to the ground plane for

the LFCSP package. Soldering the exposed paddle to the PCB

increases the reliability of the solder joints and maximizes the

thermal capability of the package.

Table 7. Thermal Resistance

Airflow

Veloc ity

Packa ge Type

48-Lead LFCSP

7 mm × 7 mm

(CP-48-8)

1

Per JEDEC 51-7, plus JEDEC 25-5 2S2P test board.

2

Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

3

Per MIL-STD 883, Method 1012.1.

4

Per JEDEC JESD51-8 (still air).

(m/sec) θ

0 25 2 14 °C/W

1.0 22 °C/W

2.5 20 °C/W

1, 2

JA

1, 3

θ

JC

1, 4

θ

Unit

JB

Typical θJA is specified for a 4-layer PCB with a solid ground

plane. As shown Tabl e 7, airflow improves heat dissipation,

which reduces θ

. In addition, metal in direct contact with the

JA

package leads from metal traces, through holes, ground, and

power planes, reduces θ

.

JA

ESD CAUTION

Rev. B | Page 10 of 44

AD9644

B

A

A

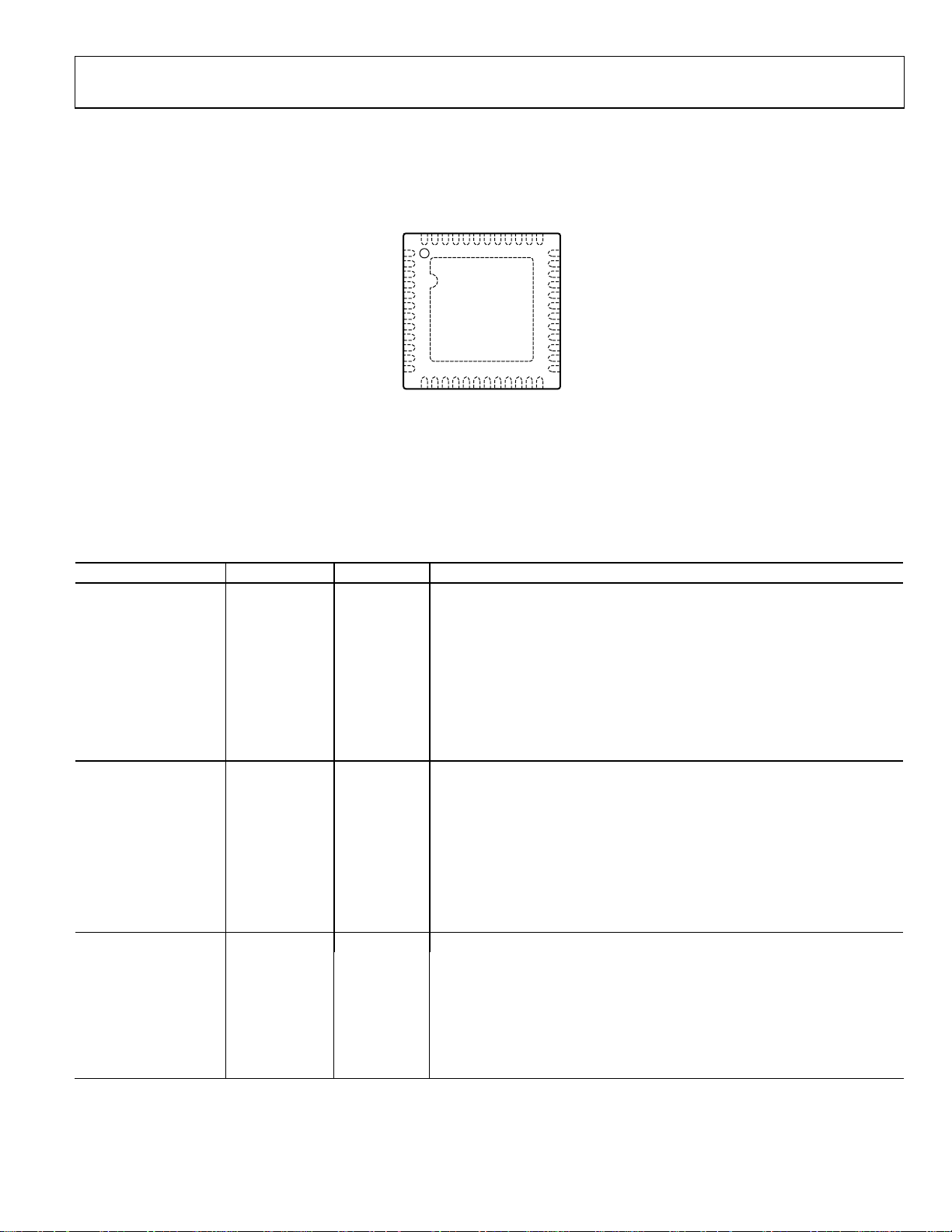

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

D

AVDD

84

AVDD

AVDD

74

AVDD

VIN–B

VIN+

AVD

64

54

44

VIN–

AVDD

AVDD

AVDD

VIN+

93

14

34

24

73

83

04

1

VCMB

2

AVDD

3

DNC

4

AVDD

5

CLK+

6

CLK–

7

AVDD

8

SYNC

9

AVDD

10

DRGND

11

DRVDD

12

DNC

NOTES

1. DNC = DO NOT CO NNECT.

2. THE EXPO SED THERMAL PAD ON THE BOTTOM OF THE PACKAGE

PROVIDES THE ANALOG GROUND FOR THE PART. THIS EXPOSED PAD

MUST BE CONNECTED TO GROUND FOR PROPER OPERATION.

51

41

31

DRVDD

DSYNC–B

DSYNC+B

AD9644

TOP

VIEW

(Not to Scale)

91

81

71

61

DRGND

DOUT–A

DOUT–B

DOUT+B

32

22

12

02

DRVDD

DRGND

DOUT+A

DSYNC–A

VCMA

36

DNC

35

DNC

34

PDWN

33

32

DNC

CSB

31

SCLK

30

SDIO

29

28

DRVDD

27

DRVDD

DRGND

26

25

DNC

42

DSYNC+A

09180-104

Figure 4. LFCSP Pin Configuration (Top View)

Table 8. Pin Function Descriptions

Pin No. Mnemonic Type Description

ADC Power Supplies

11, 15, 22, 27, 28 DRVDD Supply Digital Output Driver Supply (1.8 V Nominal).

2, 4, 7, 9, 37, 38, 41,

AVDD Supply Analog Power Supply (1.8 V Nominal).

42, 43, 44, 47, 48

3, 12, 25, 32, 34, 35 DNC Do Not Connect.

10, 16, 21, 26 DRGND

Driver

Digital Driver Supply Ground.

Ground

0

AGND,

Exposed Pad

Ground

The exposed thermal pad on the bottom of the package provides the analog

ground for the part. This exposed pad must be connected to ground for

proper operation.

ADC Analog

40 VIN+A Input Differential Analog Input Pin (+) for Channel A.

39 VIN−A Input Differential Analog Input Pin (−) for Channel A.

45 VIN+B Input Differential Analog Input Pin (+) for Channel B.

46 VIN−B Input Differential Analog Input Pin (−) for Channel B.

36 VCMA Output Common-Mode Level Bias Output for Channel A Analog Input.

1 VCMB Output Common-Mode Level Bias Output for Channel B Analog Input.

5 CLK+ Input ADC Clock Input—True.

6 CLK− Input ADC Clock Input—Complement.

Digital Input

8 SYNC Input Input Clock Divider Synchronization Pin.

24 DSYNC+A Input

Active Low JESD204A LVDS Channel A SYNC Input—True/JESD204A CMOS

Channel A SYNC Input.

23 DSYNC−A Input Active Low JESD204A LVDS Channel A SYNC Input—Complement.

14 DSYNC+B Input

Active Low JESD204A LVDS Channel B SYNC Input—True/JESD204A CMOS

Channel A SYNC Input.

13 DSYNC−B Input Active Low JESD204A LVDS Channel B SYNC Input—Complement.

Rev. B | Page 11 of 44

AD9644

Pin No. Mnemonic Type Description

Digital Outputs

20 DOUT+A Output Channel A CML Output Data—True.

19 DOUT−A Output Channel A CML Output Data—Complement.

18 DOUT+B Output Channel B CML Output Data—True.

17 DOUT−B Output Channel B CML Output Data—Complement.

SPI Control

30 SCLK Input SPI Serial Clock.

29 SDIO Input/Output SPI Serial Data Input/Output.

31 CSB Input SPI Chip Select (Active Low).

ADC Configuration

33 PDWN Input

Power-Down Input. Using the SPI interface, this input can be configured as

power-down or standby.

Rev. B | Page 12 of 44

AD9644

TYPICAL PERFORMANCE CHARACTERISTICS

AVDD = 1.8 V, DRVDD = 1.8 V, DCS enabled, 1.75 V p-p differential input, VIN = −1.0 dBFS, and 32k sample,

T

= 25°C, unless otherwise noted.

A

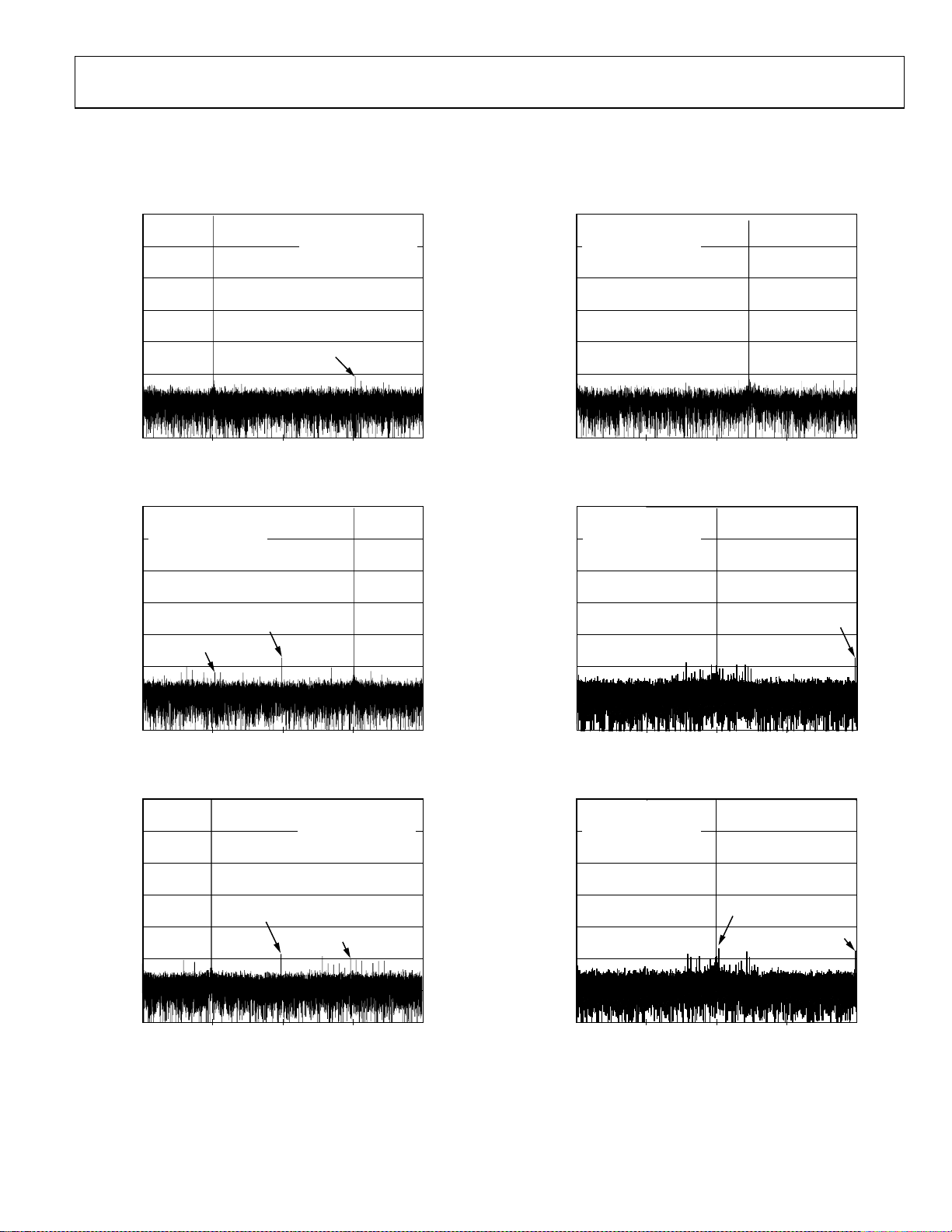

–20

–40

0

80MSPS

10.1MHz @ –1dBFS

SNR = 73.0dB ( 74.0dBFS)

SFDR = 95dBc

0

80MSPS

140.3MHz @ –1dBF S

–20

SNR = 72.2dB (73.2dBFS)

SFDR = 94.0dBc

–40

–60

–80

AMPLITUDE (dBFS)

–100

–120

–140

0 102030

THIRD HARMONIC

FREQUENCY (M Hz)

Figure 5. AD9644-80 Single-Tone FFT with f

0

80MSPS

30.1MHz @ –1dBFS

–20

SNR = 72.7dB (73.7dBFS)

SFDR = 94dBc

–40

–60

–80

AMPLITUDE (dBFS)

THIRD HARMONI C

–100

–120

–140

0 102030

SECOND HARMONIC

FREQUENCY (M Hz)

Figure 6. AD9644-80 Single-Tone FFT with f

0

–20

–40

80MSPS

70.1MHz @ –1dBF S

SNR = 72.5dB (73.5dBFS)

SFDR = 94.0dBc

= 10.1 MHz

IN

= 30.1 MHz

IN

40

09180-005

40

09180-106

–60

–80

AMPLITUDE (dBFS)

–100

–120

–140

0 102030

Figure 8. AD9644-80 Single-Tone FFT with f

0

80MSPS

180.1MHz @ –1dBF S

–20

SNR = 71.6dB (72.6dBFS)

SFDR = 93dBc

–40

–60

–80

AMPLITUDE (dBFS)

–100

–120

–140

0 1020304

Figure 9. AD9644-80 Single-Tone FFT with f

0

80MSPS

220.1MHz @ –1dBF S

–20

SNR = 71.1dB (72.1dBFS)

SFDR = 92dBc

–40

FREQUENCY (M Hz)

FREQUENCY (M Hz)

= 140.1 MHz

IN

SECOND HARMONI C

= 180.1 MHz

IN

40

09180-108

0

09180-109

–60

–80

AMPLITUDE (dBFS)

–100

–120

–140

0 102030

SECOND HARMONI C

THIRD HARMONI C

FREQUENCY (M Hz)

Figure 7. AD9644-80 Single-Tone FFT with f

= 70.1 MHz

IN

40

09180-107

Rev. B | Page 13 of 44

–60

THIRD HARMONI C

–80

AMPLITUDE (dBFS)

–100

–120

–140

0 102030

FREQUENCY (M Hz)

SECOND HARMONI C

Figure 10. AD9644-80 Single-Tone FFT with f

= 220.1 MHz

IN

40

09180-110

AD9644

120

100

100

80

60

40

SNR/SFDR (d Bc/dBFS)

20

SFDR (dBFS)

SFDR (dBc)

SNR (dBFS)

SNR (dBc)

0

–100

–95

–90

–85

–80

–75

–70

–65

–60

–55

–50

–45

–40

–35

–30

INPUT AMPLITUDE (dBFS)

–25

–5

–20

–15

–10

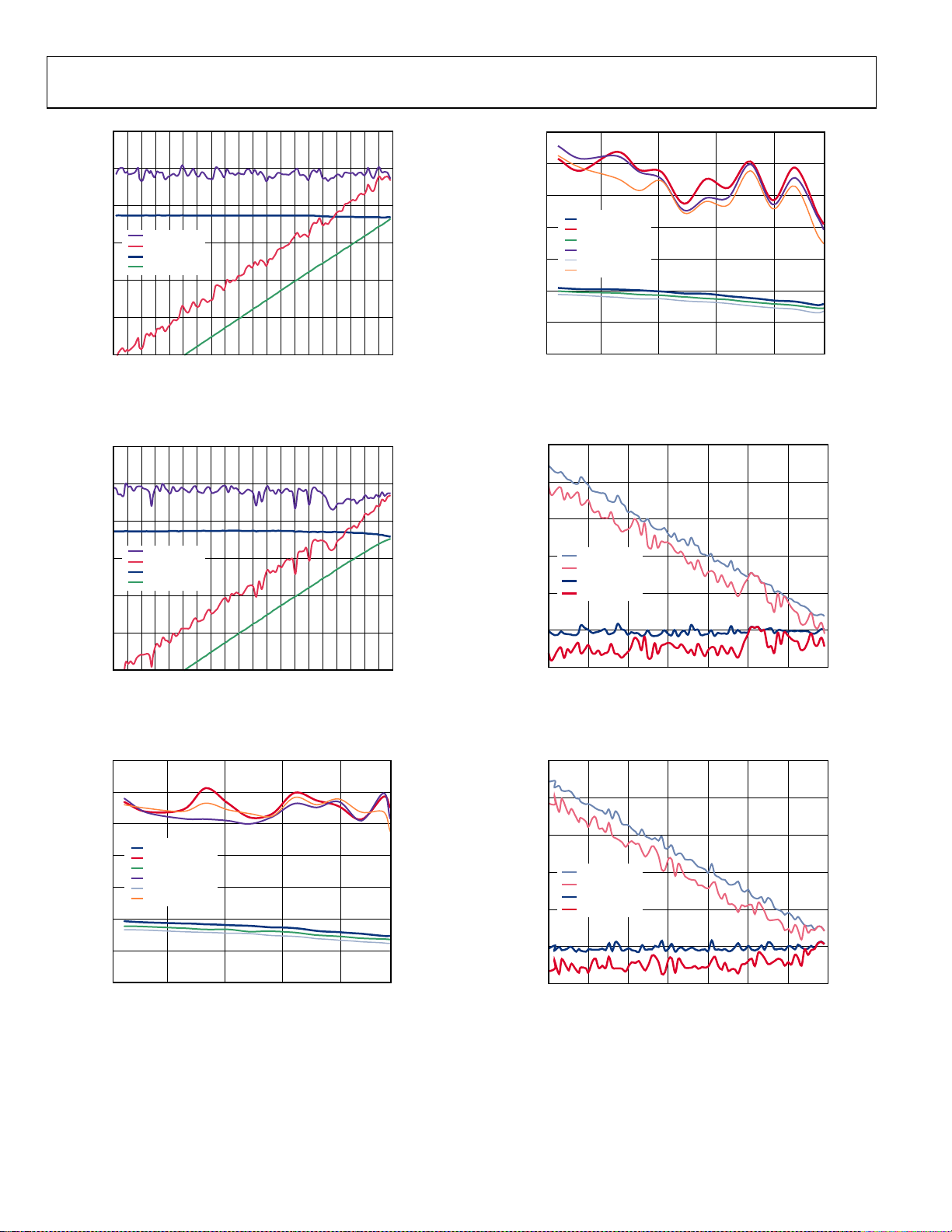

Figure 11. AD9644-80 Single-Tone SNR/SFDR vs. Input Amplitude (A

= 10.1 MHz, fS = 80 MSPS

with f

IN

120

100

80

SFDR (dBFS)

60

SFDR (dBc)

SNR (dBFS)

SNR (dBc)

40

SNR/SFDR (dBc/dBFS)

20

95

90

85

80

SNR/SFDR (dBFS/dBc)

75

70

0

09180-111

)

IN

65

Figure 14. AD9644-80 Single-Tone SNR/SFDR vs. Input Frequency (f

–20

–40

–60

–80

SFDR/IMD3 (dBc/dBFS )

–100

SNR @ –40°C

SFDR @ –40°C

SNR @ +25°C

SFDR @ +25°C

SNR @ +85°C

SFDR @ +85°C

0 50 100 150 200 250

Temperature with 2.0 V p-p Full-Scale, f

0

SFDR (dBc)

IMD3 (d Bc)

SFDR (dBFS)

IMD3 (d BFS)

INPUT FREQUENCY (MHz)

= 80 MSPS

S

) and

IN

09180-114

0

–95

–90

–85

–80

–75

–70

–65

–60

–55

–50

–45

–40

–35

–30

–100

INPUT AMPLITUDE (dBFS)

–25

–5

–20

–15

–10

Figure 12. AD9644-80 Single-Tone SNR/SFDR vs. Input Amplitude (A

with f

= 180 MHz, fS = 80 MSPS

IN

100

95

90

85

80

SNR/SFDR (dBFS/dBc)

75

70

65

SNR @ –40°C

SFDR @ –40°C

SNR @ +25°C

SFDR @ +25°C

SNR @ +85°C

SFDR @ +85°C

0 50 100 150 200 250

INPUT FREQUENCY (MHz)

Figure 13. AD9644-80 Single-Tone SNR/SFDR vs. Input Frequency (f

Temperature with 1.75 V p-p Full-Scale, f

= 80 MSPS

S

0

) and

IN

–120

–90 –78 –66 –54 –42 –30 –18 –6

9180-112

)

IN

Figure 15. AD9644-80 Two-Tone SFDR/IMD3 vs. Input Amplitude (A

with f

0

–20

–40

–60

–80

SFDR/IMD3 ( dBc/dBFS)

–100

–120

09180-113

SFDR (dBc)

IMD3 (dBc)

SFDR (dBFS)

IMD3 (dBFS)

–90 –78 –66 –54 –42 –30 –18 –6

Figure 16. AD9644-80 Two-Tone SFDR/IMD3 vs. Input Amplitude (A

with f

IN1

INPUT AMPLITUDE (dBFS)

= 29.9 MHz, f

IN1

INPUT AMPLITUDE (dBFS)

= 169.1 MHz, f

= 32.9 MHz, fS = 80 MSPS

IN2

= 172.1 MHz, fS = 80 MSPS

IN2

09180-015

)

IN

09180-116

)

IN

Rev. B | Page 14 of 44