Clock Generator with Dual PLLs,

Data Sheet

FEATURES

Fully integrated dual PLL/VCO cores

1 integer-N and 1 fractional-N PLL

Continuous frequency coverage from 11.2 MHz to 200 MHz

Most frequencies from 200 MHz to 637.5 MHz available

PLL1 phase jitter (12 kHz to 20 MHz): 460 fs rms typical

PLL2 phase jitter (12 kHz to 20 MHz)

Integer-N mode: 470 fs rms typical

Fractional-N mode: 660 fs rms typical

Input crystal or reference clock frequency

Optional reference frequency divide-by-2

2

I

C programmable output frequencies

Up to 4 LVDS/LVPECL or up to 8 LVCMOS output clocks

1 CMOS buffered reference clock output

Spread spectrum: downspread [0, −0.5]%

2 pin-controlled frequency maps: margining

Integrated loop filters

Space saving, 6 mm × 6 mm, 40-lead LFCSP package

1.02 W power dissipation (LVDS operation)

1.235 W power dissipation (LVPECL operation)

3.3 V operation

APPLICATIONS

Low jitter, low phase noise multioutput clock generator for

data communications applications including Ethernet,

Fibre Channel, SONET, SDH, PCI-e, SATA, PTN, OTN,

ADC/DAC, and digital video

Spread spectrum clocking

GENERAL DESCRIPTION

The AD9577 provides a multioutput clock generator function,

along with two on-chip phase-locked loop cores, PLL1 and PLL2,

optimized for network clocking applications. The PLL designs

are based on the Analog Devices, Inc., proven portfolio of high

performance, low jitter frequency synthesizers to maximize

network performance. The PLLs have I

frequencies and formats. The fractional-N PLL can support

spread spectrum clocking for reduced EMI radiated peak power.

Both PLLs can support frequency margining. Other applications

with demanding phase noise and jitter requirements can benefit

from this part.

The first integer-N PLL section (PLL1) consists of a low noise phase

frequency detector (PFD), a precision charge pump (CP), a low

phase noise voltage controlled oscillator (VCO), a programmable

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

2

C programmable output

Spread Spectrum, and Margining

AD9577

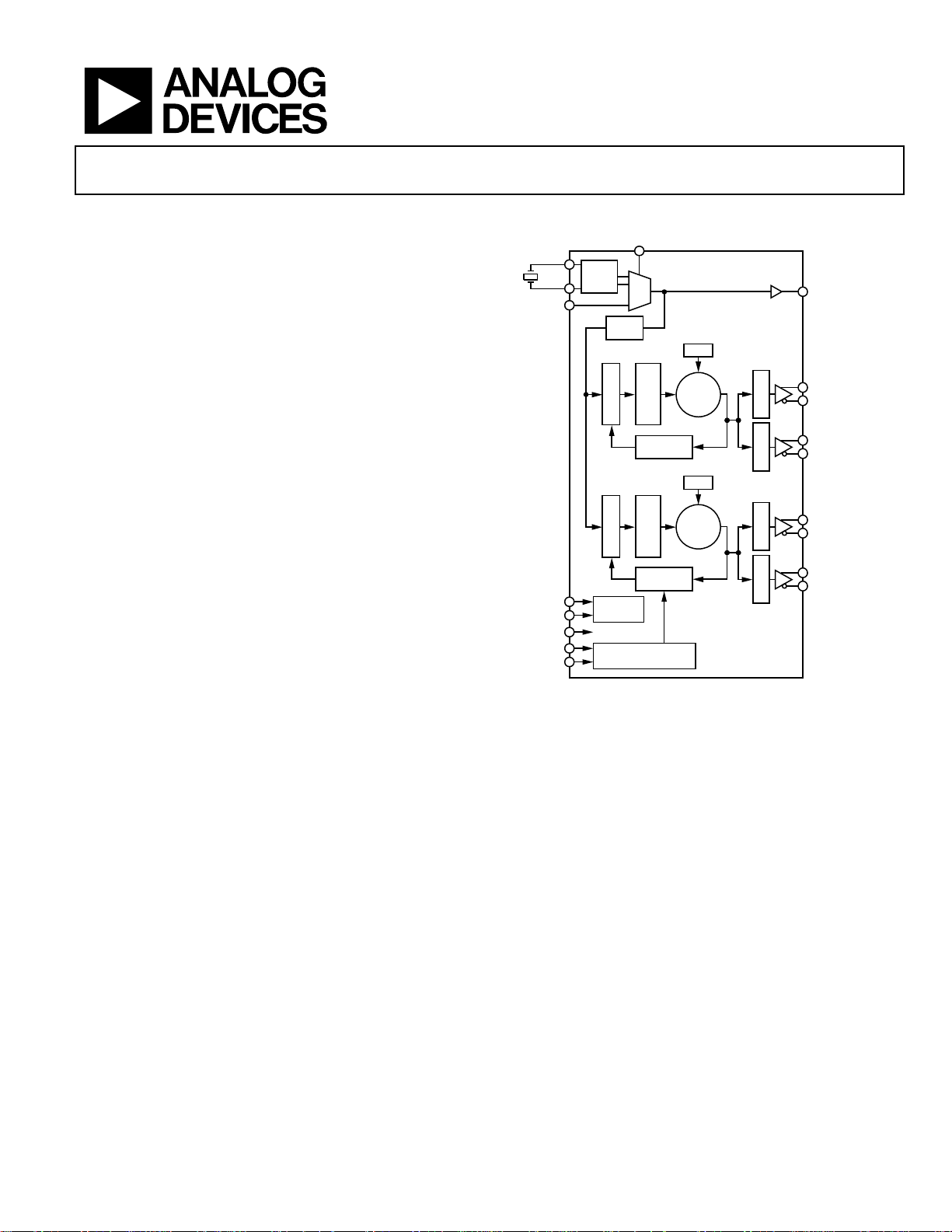

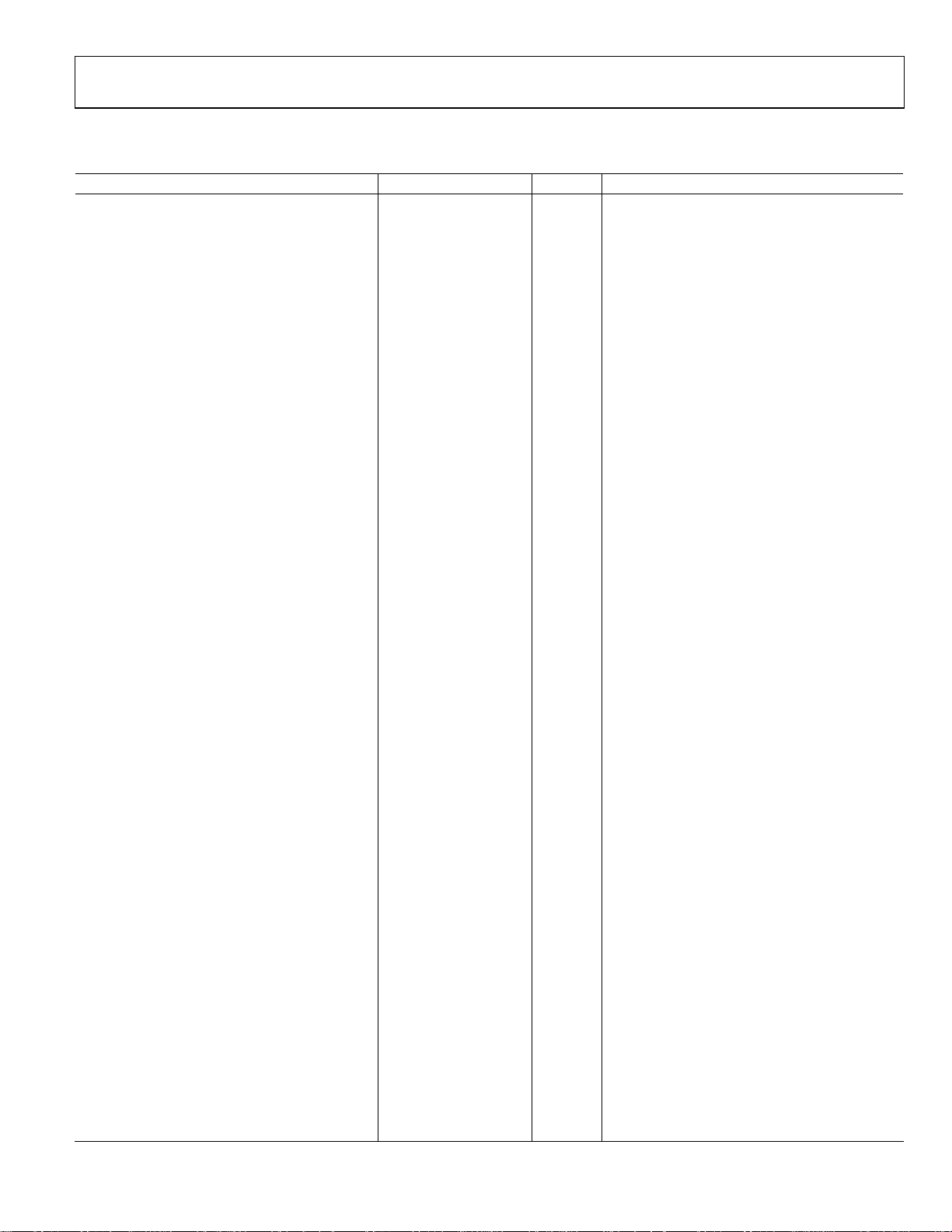

FUNCTIONAL BLOCK DIAGRAM

REFSEL

XT1

XTAL

OSC

XT2

REFCLK

DIVIDE

1 OR 2

THIRD

ORDER LPF

DIVIDER

THIRD

ORDER LPF

DIVIDER

LDO

VCO

2.15GHz

TO

2.55GHz

LDO

VCO

2.15GHz

TO

2.55GHz

Figure 1.

SCL

SDA

MARGIN

SSCG

MAX_BW

PLL1

PFD

f

PFD/CP

FEEDBACK

PLL2

PFD/CP

FEEDBACK

I2C

CONTROL

SPREAD SPECTRUM,

SDM

feedback divider, and two independently programmable output

dividers. By connecting an external crystal or applying a reference

clock to the REFCLK pin, frequencies of up to 637.5 MHz can

be synchronized to the input reference. Each output divider and

feedback divider ratio is I

2

C programmed for the required

output rates.

A second fractional-N PLL (PLL2) with a programmable modulus

allows VCO frequencies that are fractional multiples of the

reference frequency to be synthesized. Each output divider

and feedback divider ratio can be programmed for the required

output rates, up to 637.5 MHz. This fractional-N PLL can also

operate in integer-N mode for the lowest jitter.

Up to four differential output clock signals can be configured

as either LVPECL or LVDS signaling formats. Alternatively,

the outputs can be configured for up to eight CMOS outputs.

Combinations of these formats are supported. No external loop

filter components are required, thus conserving valuable design

time and board space. The AD9577 is available in a 40-lead, 6 mm ×

6 mm LFCSP package and can operate from a single 3.3 V supply.

The operating temperature range is −40°C to +85°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

CMOS

DIVIDERS

DIVIDERS

DIVIDERS

DIVIDERS

AD9577

REFOUT

LVPECL/LVDS

OR 2 × CMOS

LVPECL/LVDS

OR 2 × CMOS

LVPECL/LVDS

OR 2 × CMOS

LVPECL/LVDS

OR 2 × CMOS

09284-001

AD9577 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

PLL1 Characteristics .................................................................... 3

PLL1 Clock Output Jitter............................................................. 5

PLL2 Fractional-N Mode Characteristics ................................. 6

PLL2 Integer-N Mode Characteristics....................................... 7

PLL2 Clock Output Jitter............................................................. 9

CMOS Reference Clock Output Jitter...................................... 11

Timing Characteristics .............................................................. 12

Clock Outputs............................................................................. 13

Power............................................................................................ 14

Crystal Oscillator........................................................................ 15

Reference Input........................................................................... 15

Control Pins ................................................................................ 15

Absolute Maximum Ratings.......................................................... 16

Thermal Characteristics ............................................................16

ESD Caution................................................................................ 16

Pin Configuration and Function Descriptions........................... 17

Typical Performance Characteristics ........................................... 19

REFOUT and PLL1 Phase Noise Performance...................... 19

PLL2 Phase Noise Performance................................................ 20

Output Jitter ................................................................................21

Typical Output Signal ................................................................ 22

Typical Spread Spectrum Performance Characteristics........ 24

Terminology .................................................................................... 25

Detailed Block Diagram ................................................................ 27

Example Application.................................................................. 28

Functional Description.................................................................. 29

Reference Input and Reference Dividers................................. 29

Output Channel Dividers.......................................................... 30

Outputs........................................................................................ 30

Reference Output Buffer ........................................................... 31

PLL1 Integer-N PLL................................................................... 31

PLL1 Phase Frequency Detector (PFD) and Charge Pump . 32

PLL1 VCO................................................................................... 32

PLL1 Feedback Divider ............................................................. 32

Setting the Output Frequency of PLL1.................................... 32

PLL2 Integer/Fractional-N PLL ............................................... 32

PLL2 Phase Frequency Detector (PFD) and Charge Pump . 33

PLL2 Loop Bandwidth............................................................... 33

PLL2 VCO................................................................................... 33

PLL2 Feedback Divider ............................................................. 33

PLL2 Σ-Δ Modulator ................................................................. 33

Spur Mechanisms....................................................................... 33

Optimizing PLL Performance .................................................. 34

Setting the Output Frequency of PLL2.................................... 34

Margining.................................................................................... 35

Spread Spectrum Clock Generation (SSCG).......................... 35

I2C Interface Timing and Internal Register Description........... 38

Default Frequency Map and Output Formats ........................ 40

I2C Interface Operation ............................................................. 40

Typical Application Circuits ..................................................... 42

Power and Grounding Considerations and Power Supply

Rejection...................................................................................... 43

Outline Dimensions....................................................................... 44

Ordering Guide .......................................................................... 44

REVISION HISTORY

10/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 44

Data Sheet AD9577

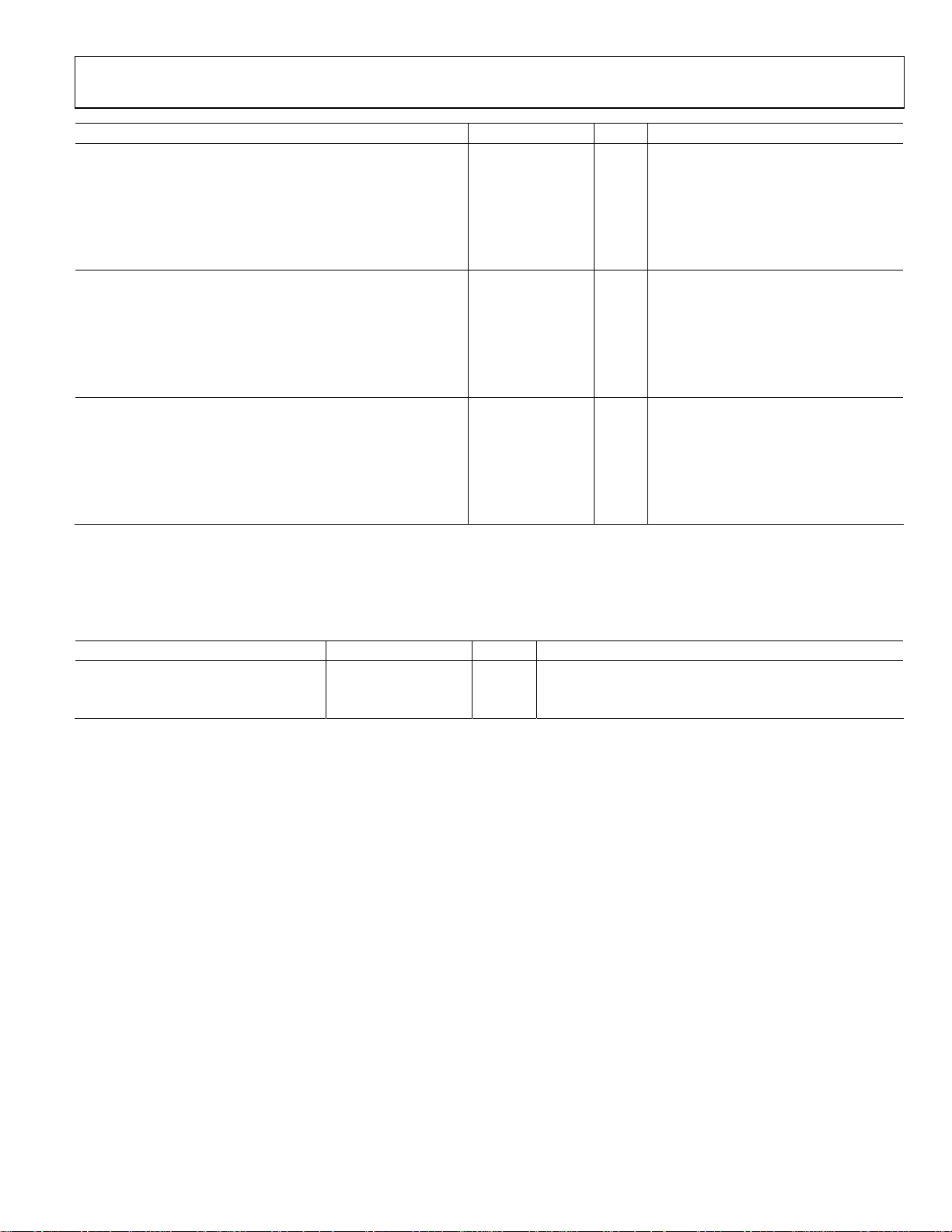

SPECIFICATIONS

Typical (typ) is given for VS = 3.3 V, TA = 25°C, unless otherwise noted. Minimum (min) and maximum (max) values are given over full

(3.0 V to 3.6 V) and TA (−40°C to +85°C) variation. AC coupling capacitors of 0.1 μF used where appropriate. A Fox Electronics

V

S

FX532A 25 MHz crystal is used throughout, unless otherwise stated.

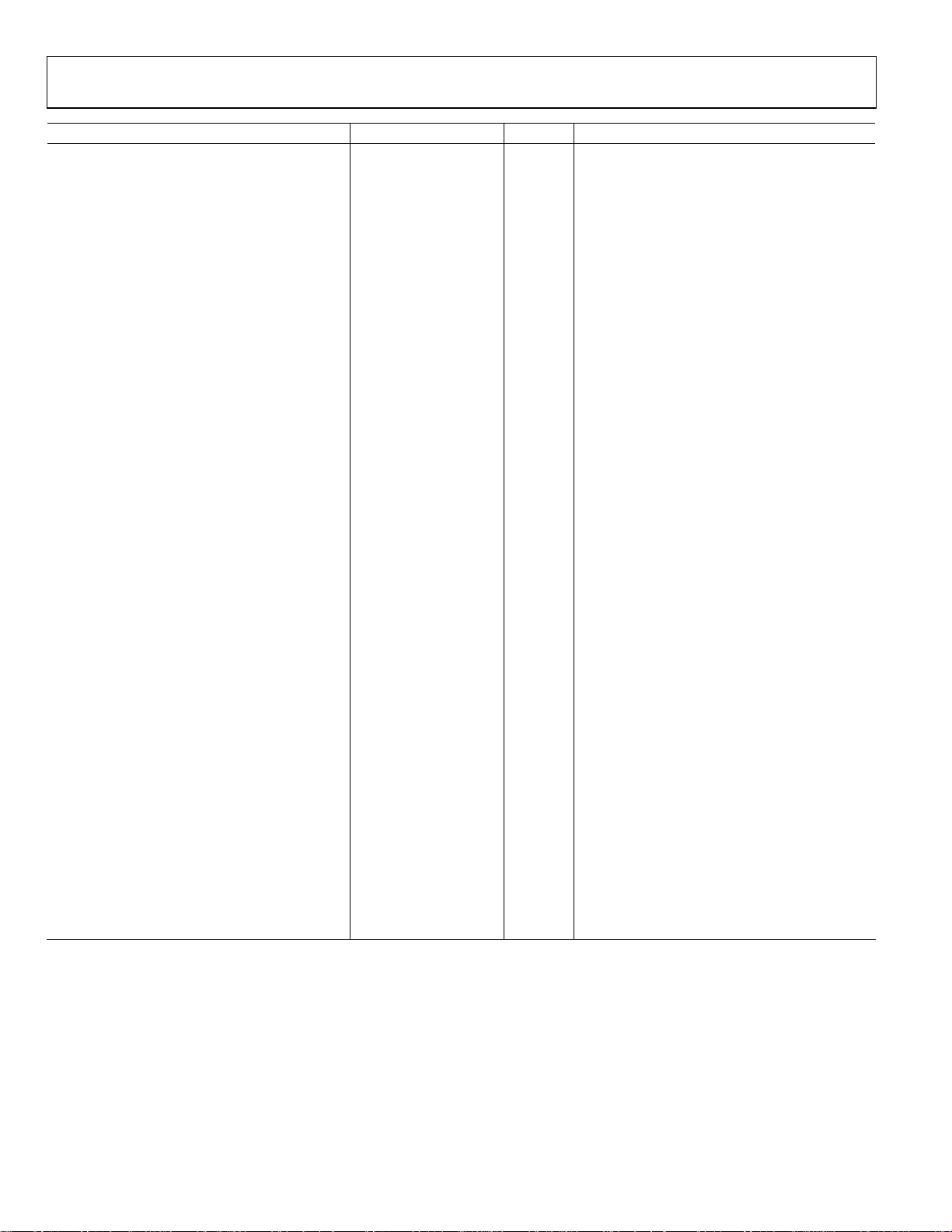

PLL1 CHARACTERISTICS

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments1

NOISE CHARACTERISTICS

Phase Noise (106.25 MHz LVPECL Output) Na = 102, Vx = 4, Dx = 6, f

At 1 kHz −121 dBc/Hz

At 10 kHz −127 dBc/Hz

At 100 kHz −128 dBc/Hz

At 1 MHz −150 dBc/Hz

At 10 MHz −156 dBc/Hz

At 30 MHz −158 dBc/Hz

Phase Noise (156.25 MHz LVPECL Output) Na = 100, Vx = 4, Dx = 4, f

At 1 kHz −117 dBc/Hz

At 10 kHz −124 dBc/Hz

At 100 kHz −124 dBc/Hz

At 1 MHz −147 dBc/Hz

At 10 MHz −156 dBc/Hz

At 30 MHz −156 dBc/Hz

Phase Noise (625 MHz LVPECL Output) Na = 100, Vx = 2, Dx = 2, f

At 1 kHz −105 dBc/Hz

At 10 kHz −112 dBc/Hz

At 100 kHz −112 dBc/Hz

At 1 MHz −135 dBc/Hz

At 10 MHz −150 dBc/Hz

At 30 MHz −150 dBc/Hz

Phase Noise (106.25 MHz LVDS Output) Na = 102, Vx = 4, Dx = 6, f

At 1 kHz −119 dBc/Hz

At 10 kHz −127 dBc/Hz

At 100 kHz −128 dBc/Hz

At 1 MHz −148 dBc/Hz

At 10 MHz −156 dBc/Hz

At 30 MHz −156 dBc/Hz

Phase Noise (156.25 MHz LVDS Output) Na = 100, Vx = 4, Dx = 4, f

At 1 kHz −116 dBc/Hz

At 10 kHz −124 dBc/Hz

At 100 kHz −124 dBc/Hz

At 1 MHz −145 dBc/Hz

At 10 MHz −155 dBc/Hz

At 30 MHz −155 dBc/Hz

Phase Noise (625 MHz LVDS Output) Na = 100, Vx = 2, Dx = 2, f

At 1 kHz −104 dBc/Hz

At 10 kHz −111 dBc/Hz

At 100 kHz −112 dBc/Hz

At 1 MHz −134 dBc/Hz

At 10 MHz −149 dBc/Hz

At 30 MHz −149 dBc/Hz

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

Rev. 0 | Page 3 of 44

AD9577 Data Sheet

Parameter Min Typ Max Unit Test Conditions/Comments1

Phase Noise (106.25 MHz CMOS Output) Na = 102, Vx = 4, Dx = 6, f

At 1 kHz −118 dBc/Hz

At 10 kHz −127 dBc/Hz

At 100 kHz −127 dBc/Hz

At 1 MHz −149 dBc/Hz

At 10 MHz −156 dBc/Hz

At 30 MHz −157 dBc/Hz

Phase Noise (156.25 MHz CMOS Output) Na = 100, Vx = 4, Dx = 4, f

At 1 kHz −115 dBc/Hz

At 10 kHz −124 dBc/Hz

At 100 kHz −124 dBc/Hz

At 1 MHz −146 dBc/Hz

At 10 MHz −155 dBc/Hz

At 30 MHz −155 dBc/Hz

Phase Noise (155.52 MHz LVPECL Output) Na = 112, Vx = 2, Dx = 7, f

At 1 kHz −117 dBc/Hz

At 10 kHz −122 dBc/Hz

At 100 kHz −123 dBc/Hz

At 1 MHz −148 dBc/Hz

At 10 MHz −156 dBc/Hz

At 30 MHz −156 dBc/Hz

Phase Noise (622.08 MHz LVPECL Output) Na = 128, Vx = 2, Dx = 2, f

At 1 kHz −105 dBc/Hz

At 10 kHz −110 dBc/Hz

At 100 kHz −110 dBc/Hz

At 1 MHz −136 dBc/Hz

At 10 MHz −150 dBc/Hz

At 30 MHz −150 dBc/Hz

Phase Noise (155.52 MHz LVDS Output) Na = 112, Vx = 2, Dx = 7, f

At 1 kHz −117 dBc/Hz

At 10 kHz −122 dBc/Hz

At 100 kHz −123 dBc/Hz

At 1 MHz −146 dBc/Hz

At 10 MHz −155 dBc/Hz

At 30 MHz −155 dBc/Hz

Phase Noise (622.08 MHz LVDS Output) Na = 128, Vx = 2, Dx = 2, f

At 1 kHz −105 dBc/Hz

At 10 kHz −110 dBc/Hz

At 100 kHz −110 dBc/Hz

At 1 MHz −134 dBc/Hz

At 10 MHz −149 dBc/Hz

At 30 MHz −150 dBc/Hz

Phase Noise (155.52 MHz CMOS Output) Na = 112, Vx = 2, Dx = 7, f

At 1 kHz −117 dBc/Hz

At 10 kHz −122 dBc/Hz

At 100 kHz −123 dBc/Hz

At 1 MHz −147 dBc/Hz

At 10 MHz −155 dBc/Hz

At 30 MHz −155 dBc/Hz

1

x indicates either 0 or 1 for any given test condition.

= 25 MHz

PFD

= 25 MHz

PFD

= 19.44 MHz

PFD

= 19.44 MHz

PFD

= 19.44 MHz

PFD

= 19.44 MHz

PFD

= 19.44 MHz

PFD

Rev. 0 | Page 4 of 44

Data Sheet AD9577

PLL1 CLOCK OUTPUT JITTER

Table 2.

Parameter1 Min Typ Max Unit Test Conditions/Comments2

LVPECL INTEGRATED RANDOM PHASE JITTER 25 MHz crystal used

RMS Jitter (625 MHz Output) 460 750 fs rms 12 kHz to 20 MHz, Na = 100, Vx = 2, Dx = 2

430 650 fs rms 50 kHz to 80 MHz, Na = 100, Vx = 2, Dx = 2

RMS Jitter (156.25 MHz Output) 460 750 fs rms 12 kHz to 20 MHz, Na = 100, Vx = 4, Dx = 4

RMS Jitter (106.25 MHz Output) 460 750 fs rms 12 kHz to 20 MHz, Na = 102, Vx = 4, Dx = 6

LVDS INTEGRATED RANDOM PHASE JITTER 25 MHz crystal used

RMS Jitter (625 MHz Output) 470 820 fs rms 12 kHz to 20 MHz, Na = 100, Vx = 2, Dx = 2

450 790 fs rms 50 kHz to 80 MHz, Na = 100, Vx = 2, Dx = 2

RMS Jitter (156.25 MHz Output) 470 790 fs rms 12 kHz to 20 MHz, Na = 100, Vx = 4, Dx = 4

RMS Jitter (106.25 MHz Output) 470 790 fs rms 12 kHz to 20 MHz, Na = 102, Vx = 4, Dx = 6

CMOS INTEGRATED RANDOM PHASE JITTER 25 MHz crystal used, 50 Ω load

RMS Jitter (100 MHz Output) 470 920 fS rms 12 kHz to 20 MHz, Na = 96, Vx = 4, Dx = 6

RMS Jitter (33.3 MHz Output) 420 700 fS rms 12 kHz to 5 MHz, Na = 88, Vx = 6, Dx = 11

LVPECL INTEGRATED RANDOM PHASE JITTER 19.44 MHz crystal used

RMS Jitter (622.08 MHz Output) 500 680 fs rms 12 kHz to 20 MHz, Na = 128, Vx = 2, Dx = 2

460 590 fs rms 50 kHz to 80 MHz, Na = 128, Vx = 2, Dx = 2

RMS Jitter (155.52 MHz Output) 480 680 fs rms 12 kHz to 20 MHz, Na = 112, Vx = 2, Dx = 7

LVDS INTEGRATED RANDOM PHASE JITTER 19.44 MHz crystal used

RMS Jitter (622.08 MHz Output) 520 780 fs rms 12 kHz to 20 MHz, Na = 128, Vx = 2, Dx = 2

480 710 fs rms 50 kHz to 80 MHz, Na = 128, Vx = 2, Dx = 2

RMS Jitter (155.52 MHz Output) 480 750 fs rms 12 kHz to 20 MHz, Na = 112, Vx = 2, Dx = 7

CMOS INTEGRATED RANDOM PHASE JITTER 19.44 MHz crystal used, 50 Ω load

RMS Jitter (155.52 MHz Output) 470 700 fs rms 12 kHz to 20 MHz, Na = 112, Vx = 2, Dx = 7

RMS Jitter (38.88 MHz Output) 440 650 fs rms 12 kHz to 5 MHz, Na = 112, Vx = 2, Dx = 28

LVPECL PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT) 25 MHz crystal used, Na = 96, Vx = 4, Dx = 6

Output Peak-to-Peak Period Jitter 13 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 2 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 19 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 3 ps rms 1,000 cycles, average of 25 measurements

LVDS PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT) 25 MHz crystal used, Na = 96, Vx = 4, Dx = 6

Output Peak-to-Peak Period Jitter 17 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 2 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 25 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 4 ps rms 1,000 cycles, average of 25 measurements

CMOS PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT )

Output Peak-to-Peak Period Jitter 25 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 3 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak Cycle-to-Cycle Jitter 36 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 6 ps rms 1,000 cycles, average of 25 measurements

1

All period and cycle-to-cycle jitter measurements are made with a Tektronix DPO70604 oscilloscope.

2

x indicates either 0 or 1 for any given test condition.

25 MHz crystal used, 50 Ω load, Na = 96,

Vx = 4, Dx = 6

Rev. 0 | Page 5 of 44

AD9577 Data Sheet

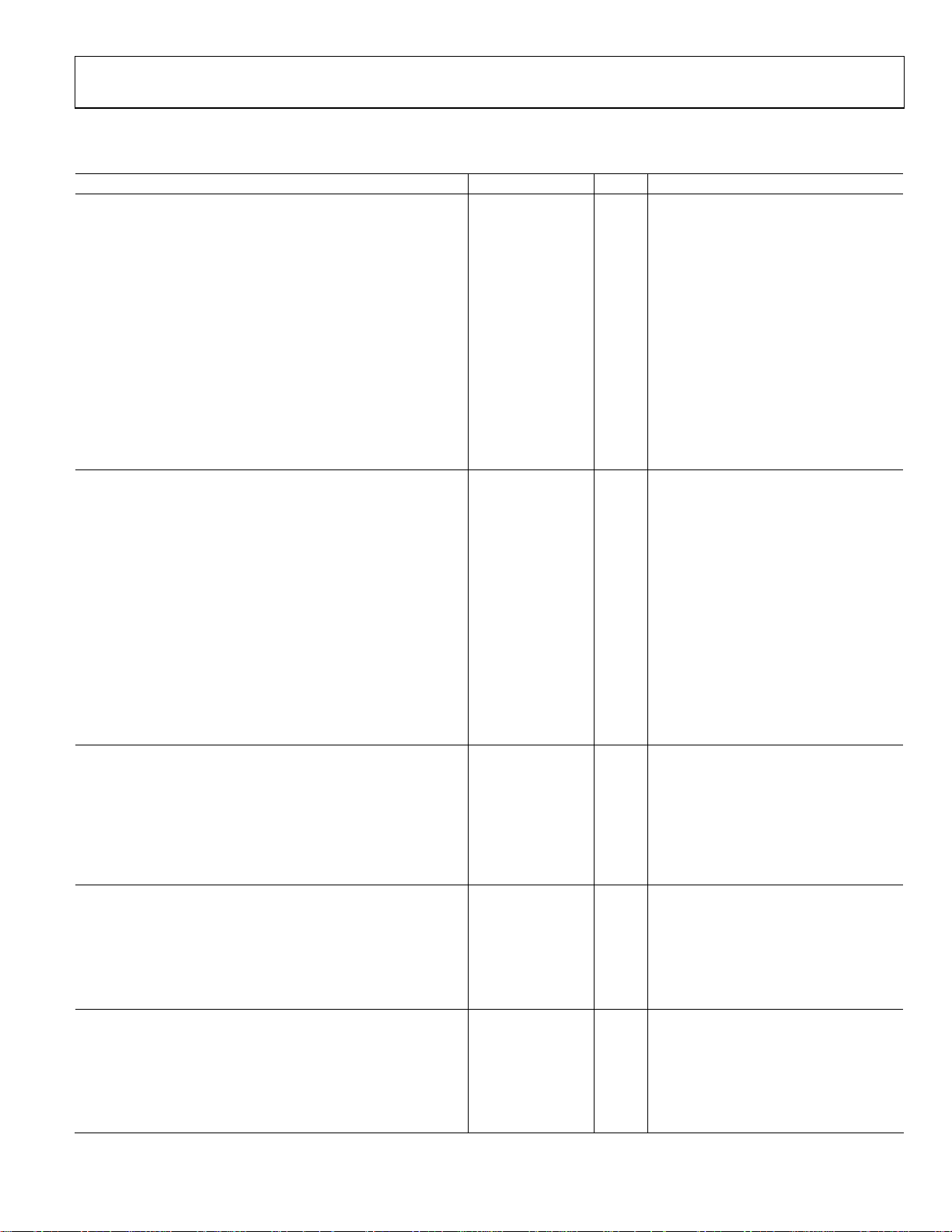

PLL2 FRACTIONAL-N MODE CHARACTERISTICS

Table 3. Bleed = 1

Parameter Min Typ Max Unit Test Conditions/Comments1

NOISE CHARACTERISTICS 25 MHz crystal used

Phase Noise (155.52 MHz LVPECL Output) Nb = 87, FRAC = 57, MOD = 625, Vx = 2, Dx = 7

@ 1 kHz −107 dBc/Hz

@ 10 kHz −115 dBc/Hz

@ 100 kHz −122 dBc/Hz

@ 1 MHz −146 dBc/Hz

@ 10 MHz −153 dBc/Hz

@ 30 MHz −152 dBc/Hz

Phase Noise (622.08 MHz LVPECL Output) Nb = 99, FRAC = 333, MOD = 625, Vx = 2, Dx = 2

@ 1 kHz −95 dBc/Hz

@ 10 kHz −103 dBc/Hz

@ 100 kHz −109 dBc/Hz

@ 1 MHz −133 dBc/Hz

@ 10 MHz −148 dBc/Hz

@ 30 MHz −150 dBc/Hz

Phase Noise (155.52 MHz LVDS Output) Nb = 87, FRAC = 57, MOD = 625, Vx = 2, Dx = 7

@ 1 kHz −107 dBc/Hz

@ 10 kHz −114 dBc/Hz

@ 100 kHz −122 dBc/Hz

@ 1 MHz −145 dBc/Hz

@ 10 MHz −154 dBc/Hz

@ 30 MHz −154 dBc/Hz

Phase Noise (622.08 MHz LVDS Output) Nb = 99, FRAC = 333, MOD = 625, Vx = 2, Dx = 2

@ 1 kHz −95 dBc/Hz

@ 10 kHz −103 dBc/Hz

@ 100 kHz −109 dBc/Hz

@ 1 MHz −132 dBc/Hz

@ 10 MHz −147 dBc/Hz

@ 30 MHz −149 dBc/Hz

Phase Noise (155.52 MHz CMOS Output) Nb = 87, FRAC = 57, MOD = 625, Vx = 2, Dx = 7

@ 1 kHz −107 dBc/Hz

@ 10 kHz −114 dBc/Hz

@ 100 kHz −122 dBc/Hz

@ 1 MHz −146 dBc/Hz

@ 10 MHz −154 dBc/Hz

@ 30 MHz −154 dBc/Hz

SPREAD SPECTRUM

Modulation Range +0.1 −0.5 % Downspread, triangle modulation profile

Modulation Frequency 31.25 kHz Programmable

Peak Power Reduction 10 dB

1

x indicates either 2 or 3 for any given test condition.

First harmonic of 100 MHz output, triangle modulation

profile, spectrum analyzer resolution bandwidth = 20 kHz

Rev. 0 | Page 6 of 44

Data Sheet AD9577

PLL2 INTEGER-N MODE CHARACTERISTICS

Table 4. Bleed = 0

Parameter Min Typ Max Unit Test Conditions/Comments1

NOISE CHARACTERISTICS

Phase Noise (106.25 MHz LVPECL Output) Nb = 102, Vx = 4, Dx = 6, f

@ 1 kHz −116 dBc/Hz

@ 10 kHz −123 dBc/Hz

@ 100 kHz −127 dBc/Hz

@ 1 MHz −148 dBc/Hz

@ 10 MHz −156 dBc/Hz

@ 30 MHz −158 dBc/Hz

Phase Noise (156.25 MHz LVPECL Output) Nb = 100, Vx = 4, Dx = 4, f

@ 1 kHz −113 dBc/Hz

@ 10 kHz −120 dBc/Hz

@ 100 kHz −124 dBc/Hz

@ 1 MHz −146 dBc/Hz

@ 10 MHz −156 dBc/Hz

@ 30 MHz −156 dBc/Hz

Phase Noise (625 MHz LVPECL Output) Nb = 100, Vx = 2, Dx = 2, f

@ 1 kHz −101 dBc/Hz

@ 10 kHz −108 dBc/Hz

@ 100 kHz −112 dBc/Hz

@ 1 MHz −134 dBc/Hz

@ 10 MHz −149 dBc/Hz

@ 30 MHz −150 dBc/Hz

Phase Noise (106.25 MHz LVDS Output) Nb = 102, Vx = 4, Dx = 6, f

@ 1 kHz −117 dBc/Hz

@ 10 kHz −123 dBc/Hz

@ 100 kHz −127 dBc/Hz

@ 1 MHz −147 dBc/Hz

@ 10 MHz −156 dBc/Hz

@ 30 MHz −156 dBc/Hz

Phase Noise (156.25 MHz LVDS Output) Nb = 100, Vx = 4, Dx = 4, f

@ 1 kHz −113 dBc/Hz

@ 10 kHz −120 dBc/Hz

@ 100 kHz −124 dBc/Hz

@ 1 MHz −145 dBc/Hz

@ 10 MHz −155 dBc/Hz

@ 30 MHz −155 dBc/Hz

Phase Noise (625 MHz LVDS Output) Nb = 100, Vx = 2, Dx = 2, f

@ 1 kHz −101 dBc/Hz

@ 10 kHz −108 dBc/Hz

@ 100 kHz −112 dBc/Hz

@ 1 MHz −133 dBc/Hz

@ 10 MHz −148 dBc/Hz

@ 30 MHz −149 dBc/Hz

Phase Noise (106.25 MHz CMOS Output) Nb = 102, Vx = 4, Dx = 6, f

@ 1 kHz −117 dBc/Hz

@ 10 kHz −123 dBc/Hz

@ 100 kHz −127 dBc/Hz

@ 1 MHz −147 dBc/Hz

@ 10 MHz −156 dBc/Hz

@ 30 MHz −157 dBc/Hz

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

= 25 MHz

PFD

Rev. 0 | Page 7 of 44

AD9577 Data Sheet

Parameter Min Typ Max Unit Test Conditions/Comments1

Phase Noise (156.25 MHz CMOS Output) Nb = 100, Vx = 4, Dx = 4, f

@ 1 kHz −113 dBc/Hz

@ 10 kHz −119 dBc/Hz

@ 100 kHz −123 dBc/Hz

@ 1 MHz −145 dBc/Hz

@ 10 MHz −154 dBc/Hz

@ 30 MHz −155 dBc/Hz

Phase Noise (155.52 MHz LVPECL Output) Nb = 112, Vx = 2, Dx = 7, f

@ 1 kHz −112 dBc/Hz

@ 10 kHz −118 dBc/Hz

@ 100 kHz −126 dBc/Hz

@ 1 MHz −147 dBc/Hz

@ 10 MHz −155 dBc/Hz

@ 30 MHz −156 dBc/Hz

Phase Noise (622.08 MHz LVPECL Output) Nb = 128, Vx = 2, Dx = 2, f

@ 1 kHz −100 dBc/Hz

@ 10 kHz −106 dBc/Hz

@ 100 kHz −112 dBc/Hz

@ 1 MHz −134 dBc/Hz

@ 10 MHz −149 dBc/Hz

@ 30 MHz −150 dBc/Hz

Phase Noise (155.52 MHz LVDS Output) Nb = 112, Vx = 2, Dx = 7, f

@ 1 kHz −113 dBc/Hz

@ 10 kHz −118 dBc/Hz

@ 100 kHz −126 dBc/Hz

@ 1 MHz −145 dBc/Hz

@ 10 MHz −154 dBc/Hz

@ 30 MHz −155 dBc/Hz

Phase Noise (622.08 MHz LVDS Output) Nb = 128, Vx = 2, Dx = 2, f

@ 1 kHz −101 dBc/Hz

@ 10 kHz −106 dBc/Hz

@ 100 kHz −112 dBc/Hz

@ 1 MHz −133 dBc/Hz

@ 10 MHz −148 dBc/Hz

@ 30 MHz −150 dBc/Hz

Phase Noise (155.52 MHz CMOS Output) Nb = 112, Vx = 2, Dx = 7, f

@ 1 kHz −113 dBc/Hz

@ 10 kHz −118 dBc/Hz

@ 100 kHz −126 dBc/Hz

@ 1 MHz −146 dBc/Hz

@ 10 MHz −155 dBc/Hz

@ 30 MHz −155 dBc/Hz

1

x indicates either 2 or 3 for any given test condition.

= 25 MHz

PFD

= 19.44 MHz

PFD

= 19.44 MHz

PFD

= 19.44 MHz

PFD

= 19.44 MHz

PFD

= 19.44 MHz

PFD

Rev. 0 | Page 8 of 44

Data Sheet AD9577

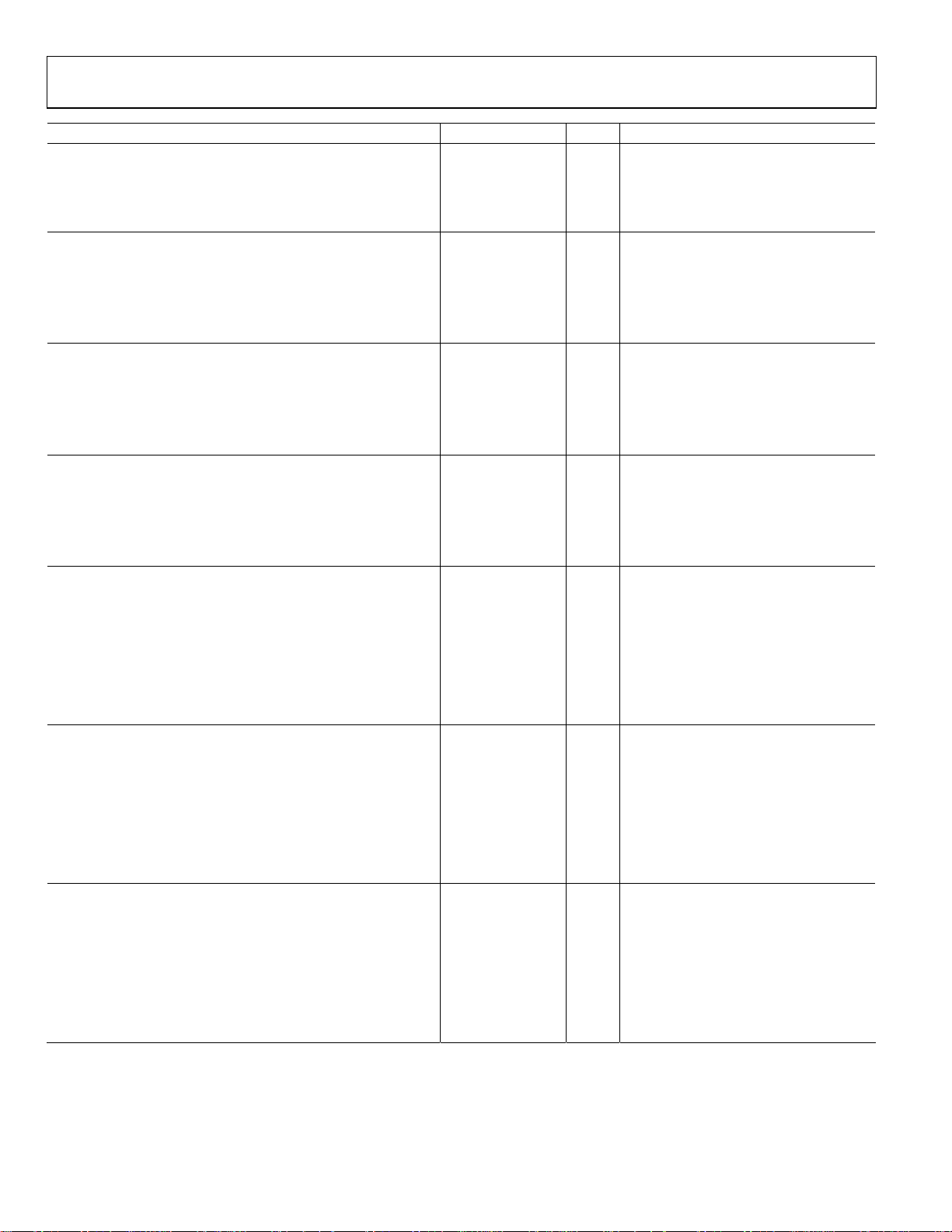

PLL2 CLOCK OUTPUT JITTER

Table 5. Bleed = 0 for Integer-N Mode, Bleed = 1 for Fractional-N Mode

Parameter1 Min Typ Max Unit Test Conditions/Comments2

LVPECL INTEGRATED RANDOM PHASE JITTER 25 MHz crystal used

RMS Jitter (622.08 MHz Output) 660 1200 fs rms

500 900 fs rms

RMS Jitter (625 MHz Output) 470 800 fs rms

380 650 fs rms

RMS Jitter (155.52 MHz Output) 630 1100 fs rms

RMS Jitter (156.25 MHz Output) 470 800 fs rms

LVDS INTEGRATED RANDOM PHASE JITTER 25 MHz crystal used

RMS Jitter (622.08 MHz Output) 660 1200 fs rms

510 900 fs rms

RMS Jitter (625 MHz Output) 470 820 fs rms

380 650 fs rms

RMS Jitter (155.52 MHz Output) 620 1100 fs rms

RMS Jitter (156.25 MHz Output) 480 800 fs rms

CMOS INTEGRATED RANDOM PHASE JITTER 25 MHz crystal used, 50 Ω load

RMS Jitter (155.52 MHz Output) 630 1100 fs rms

RMS Jitter (100 MHz Output) 490 800 fs rms

RMS Jitter (33.33 MHz Output) 450 700 fs rms

LVPECL INTEGRATED RANDOM PHASE JITTER 19.44 MHz crystal used

RMS Jitter (622.08 MHz Output) 510 800 fs rms

380 650 fs rms

RMS Jitter (155.52 MHz Output) 470 800 fs rms

LVDS INTEGRATED RANDOM PHASE JITTER 19.44 MHz crystal used

RMS Jitter (622.08 MHz Output) 530 900 fs rms

390 700 fs rms

RMS Jitter (155.52 MHz Output) 480 750 fs rms

12 kHz to 20 MHz, fractional-N operation,

Nb = 99, FRAC = 333, MOD = 625, Vx = 2,

Dx = 2

50 kHz to 80 MHz, fractional-N operation,

Nb = 99, FRAC = 333, MOD = 625, Vx = 2,

Dx = 2

12 kHz to 20 MHz, integer-N operation,

Nb = 100, Vx = 2, Dx = 2

50 kHz to 80 MHz, integer-N operation,

Nb = 100, Vx = 2, Dx = 2

12 kHz to 20 MHz, fractional-N operation,

Nb = 87, FRAC = 57, MOD = 625, Vx = 2,

Dx = 7

12 kHz to 20 MHz, integer-N operation,

Nb = 100, Vx = 4, Dx = 4

12kHz to 20 MHz, fractional-N operation,

Nb = 99, FRAC = 333, MOD = 625, Vx = 2,

Dx = 2

50 kHz to 80 MHz, fractional-N operation,

Nb = 99, FRAC = 333, MOD = 625, Vx = 2,

Dx = 2

12 kHz to 20 MHz, integer-N operation,

Nb = 100, Vx = 2, Dx = 2

50 kHz to 80 MHz, integer-N operation,

Nb = 100, Vx = 2, Dx = 2

12 kHz to 20 MHz, fractional-N operation,

Nb = 87, FRAC = 57, MOD = 625, Vx = 2,

Dx = 7

12 kHz to 20 MHz, integer-N operation,

Nb = 100, Vx = 4, Dx = 4

12 kHz to 20 MHz, fractional-N operation,

Nb = 87, FRAC = 57, MOD = 625, Vx = 2,

Dx = 7

12 kHz to 20 MHz, integer-N operation,

Nb = 96, Vx = 4, Dx = 6

12 kHz to 5 MHz, integer-N operation,

Nb = 88, Vx = 6, Dx = 11

12 kHz to 20 MHz, integer-N operation,

Nb = 128, Vx = 2, Dx = 2

50 kHz to 80 MHz, integer-N operation,

Nb = 128, Vx = 2, Dx = 2

12 kHz to 20 MHz, integer-N operation,

Nb = 112, Vx = 2, Dx = 7

12 kHz to 20 MHz, integer-N operation,

Nb = 128, Vx = 2, Dx = 2

50 kHz to 80 MHz, integer-N operation,

Nb = 128, Vx = 2, Dx = 2

12 kHz to 20 MHz, integer-N operation,

Nb = 112, Vx = 2, Dx = 7

Rev. 0 | Page 9 of 44

AD9577 Data Sheet

Parameter1 Min Typ Max Unit Test Conditions/Comments2

CMOS INTEGRATED RANDOM PHASE JITTER 19.44 MHz crystal used, 50 Ω load

RMS Jitter (155.52 MHz Output) 470 700 fs rms

RMS Jitter (38.88 MHz Output) 430 650 fs rms

LVPECL PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT)

Output Peak-to-Peak Period Jitter 13 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 2 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 19 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 3 ps rms 1,000 cycles, average of 25 measurements

LVDS PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT )

Output Peak-to-Peak Period Jitter 17 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 2 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 26 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 4 ps rms 1,000 cycles, average of 25 measurements

CMOS PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT )

Output Peak-to-Peak Period Jitter 25 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 3 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle 36 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 6 ps rms 1,000 cycles, average of 25 measurements

LVPECL PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT)

Output Peak-to-Peak Period Jitter 60 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 15 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 20 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 3 ps rms 1,000 cycles, average of 25 measurements

LVDS PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT )

Output Peak-to-Peak Period Jitter 63 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 15 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 25 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 4 ps rms 1,000 cycles, average of 25 measurements

CMOS PERIOD AND CYCLE-TO-CYCLE JITTER (100 MHz OUTPUT )

Output Peak-to-Peak Period Jitter 70 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 15 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 36 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-Cycle Jitter 6 ps rms 1,000 cycles, average of 25 measurements

12 kHz to 20 MHz, integer-N operation,

Nb = 112, Vx = 2, Dx = 7

12 kHz to 5 MHz, integer-N operation,

Nb = 112, Vx = 2, Dx = 28

25 MHz crystal used, integer-N

operation, Nb = 96, Vx = 4, Dx = 6

25 MHz crystal used, integer-N

operation, Nb = 96, Vx = 4, Dx = 6

25 MHz crystal used, 50 Ω load, integer-N

operation, Nb = 96, Vx = 4, Dx = 6

25 MHz crystal used, SSCG on, Nb = 100,

FRAC = 0, MOD = 1000, Vx = 5, Dx = 5,

CkDiv = 7, NumSteps = 59, FracStep = −8,

= 100 MHz with −0.5% downspread

f

OUT

at 30.2 kHz

25 MHz crystal used, SSCG on, Nb = 100,

FRAC = 0, MOD = 1000, Vx = 5, Dx = 5,

CkDiv = 7, NumSteps = 59, FracStep = −8,

= 100 MHz with −0.5% downspread

f

OUT

at 30.2 kHz

25 MHz crystal used, SSCG on, 50 Ω load,

Nb = 100, FRAC = 0, MOD = 1000, Vx = 5,

Dx = 5, CkDiv = 7, NumSteps = 59,

FracStep = −8, f

= 100 MHz with

OUT

−0.5% downspread at 30.2 kHz

Rev. 0 | Page 10 of 44

Data Sheet AD9577

Parameter1 Min Typ Max Unit Test Conditions/Comments2

LVPECL PERIOD AND CYCLE-TO-CYCLE JITTER (100.12 MHz OUTPUT )

Output Peak-to-Peak Period Jitter 13 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 2 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 20 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 3 ps rms 1,000 cycles, average of 25 measurements

LVDS PERIOD AND CYCLE-TO-CYCLE JITTER (100.12 MHz OUTPUT )

Output Peak-to-Peak Period Jitter 17 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 2 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 26 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 4 ps rms 1,000 cycles, average of 25 measurements

CMOS PERIOD AND CYCLE-TO-CYCLE JITTER (100.12 MHz OUTPUT)

Output Peak-to-Peak Period Jitter 25 ps p-p 10,000 cycles, average of 25 measurements

Output RMS Period Jitter 3 ps rms 10,000 cycles, average of 25 measurements

Output Peak-to-Peak, Cycle-to-Cycle Jitter 36 ps p-p 1,000 cycles, average of 25 measurements

Output RMS Cycle-to-Cycle Jitter 6 ps rms 1,000 cycles, average of 25 measurements

1

All period and cycle-to-cycle jitter measurements are made with a Tektronix DPO70604 oscilloscope.

2

x indicates either 2 or 3 for any given test condition.

25 MHz crystal used, fractional-N

operation, Nb = 100, FRAC = 15,

MOD = 125, Vx = 5, Dx = 5

25 MHz crystal used, fractional-N

operation, Nb = 100, FRAC = 15,

MOD = 125, Vx = 5, Dx = 5

25 MHz crystal used, 50 Ω load,

fractional-N operation, Nb = 100,

FRAC = 15, MOD = 125, Vx = 5, Dx = 5

CMOS REFERENCE CLOCK OUTPUT JITTER

Table 6.

Parameter Min Typ Max Unit Test Conditions/Comments

JITTER INTEGRATION BANDWIDTH Jitter measurement at 25 MHz is equipment limited

12 kHz to 5 MHz 680 1000 fs rms 25 MHz

200 kHz to 5 MHz 670 950 fs rms

Rev. 0 | Page 11 of 44

AD9577 Data Sheet

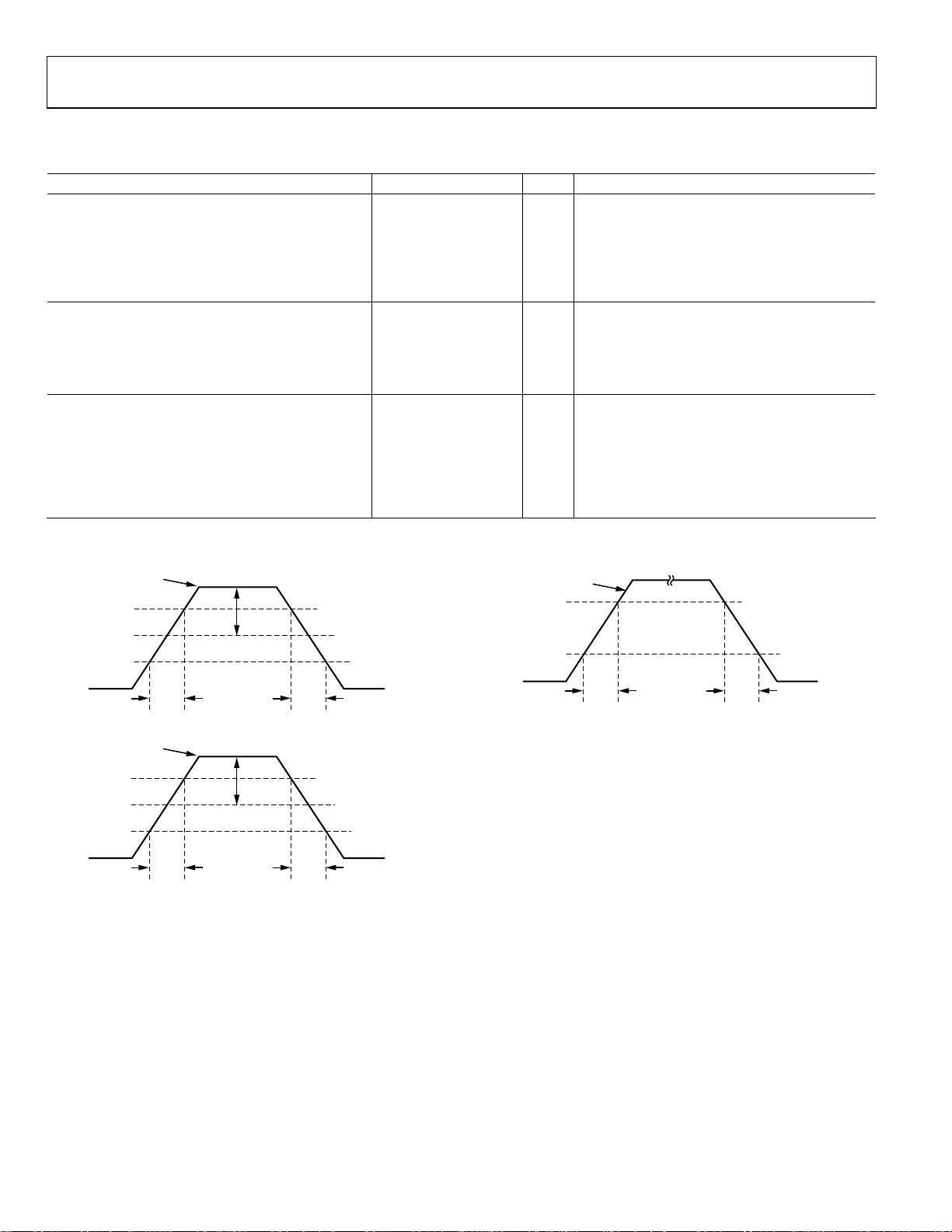

TIMING CHARACTERISTICS

Table 7.

Parameter Min Typ Max Unit Test Conditions/Comments

LVPECL (see Figure 2)

Output Rise Time, tRP 170 225 300 ps 20% to 80%, measured differentially

Output Fall Time, tFP 170 230 310 ps 80% to 20%, measured differentially

Skew 20 ps

LVDS (see Figure 3) Termination = 100 Ω differential; C

Output Rise Time, tRL 180 250 340 ps 20% to 80%, measured differentially

Output Fall Time, tFL 180 260 330 ps 80% to 20%, measured differentially

Skew 20 ps

CMOS (see Figure 4)

Output Rise Time, tRC 250 680 950 ps

Output Fall Time, tFC 350 700 1000 ps

Skew 20 ps

Timing Diagrams

DIFFERENTIAL

80%

50%

20%

DIFFERENTIAL

80%

50%

20%

t

RP

Figure 2. LVPECL Timing, Differential

V

OD

LVPECL

V

OD

LVDS

t

FP

09284-002

Termination = 200 Ω to 0 V, ac-coupled to 50 Ω

oscilloscope; C

LOAD

= 5 pF

Between the outputs of the same PLL at the

same frequency. SyncCh01/SyncCh23 set to 1

Between the outputs of the same PLL at the

same frequency; SyncCh01/SyncCh23 set to 1

Termination is high impedance active probe,

total C

LOAD

= 5 pF, R

= 20 kΩ, 20% to 80%

LOAD

Termination is high impedance active probe,

total C

LOAD

= 5 pF, R

= 20 kΩ, 80% to 20%

LOAD

Between the outputs of the same PLL at the

same frequency; SyncCh01/SyncCh23 set to 1

SINGLE-ENDED

80%

20%

t

RC

Figure 4. CMOS Timing, Single-Ended, 5 pF Load

CMOS

t

FC

LOAD

= 5 pF

09284-004

t

RL

t

FL

09284-003

Figure 3. LVDS Timing, Differential

Rev. 0 | Page 12 of 44

Data Sheet AD9577

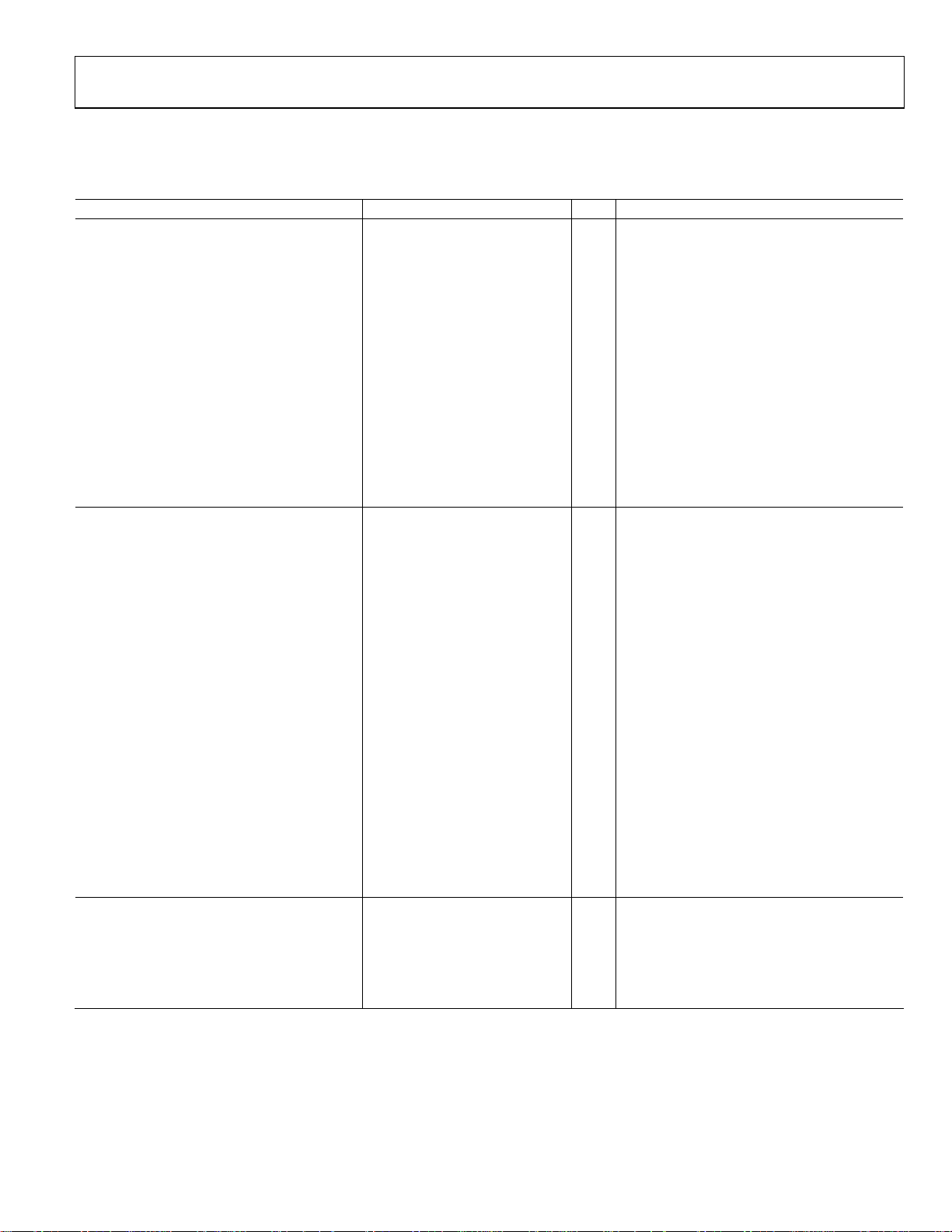

CLOCK OUTPUTS

AC coupling capacitors of 0.1 μF used where appropriate.

Table 8.

Parameter Min Typ Max Unit Test Conditions/Comments

LVPECL CLOCK OUTPUTS

Output Frequency 637.5 MHz

Output Voltage Swing, VOD 610 740 950 mV

Duty Cycle 45 55 %

Output High Voltage, VOH V

Output Low Voltage, VOL V

− 1.24 VS − 0.94 VS − 0.83 V

S

− 2.07 VS − 1.75 VS − 1.62 V

S

LVDS CLOCK OUTPUTS

Output Frequency 637.5 MHz

Differential Output Voltage, VOD 250 350 475 mV

Delta VOD 25 mV

Duty Cycle 45 55 %

Output Offset Voltage, VOS 1.125 1.25 1.375 V

Delta VOS 25 mV

Short-Circuit Current, ISA, ISB 13 24 mA

CMOS CLOCK OUTPUTS

Output Frequency 200 MHz

Output High Voltage, VOH V

− 0.15 V Sourcing 1.0 mA current, outputs static.

S

Output Low Voltage, VOL 0.1 V Sinking 1.0 mA current, outputs static.

Duty Cycle 45 55 %

Load is 200 Ω to GND at output pins, then

ac-coupled to 50 Ω terminated measurement

equipment.

Load is 200 Ω to GND at output pins, then

ac-coupled to 50 Ω terminated measurement

equipment. For differential amplitude, see

Figure 2.

Load is 200 Ω to GND at output pins, then

ac-coupled to 50 Ω terminated measurement

equipment.

Load is 127 Ω/83 Ω potential divider across

supply dc-coupled into 1 MΩ terminated

measurement equipment, outputs static.

Load is 127 Ω/83 Ω potential divider across

supply dc-coupled into 1 MΩ terminated

measurement equipment, outputs static.

Load is ac-coupled to measurement

equipment that provides 100 Ω differential

input termination.

Load is ac-coupled to measurement

equipment that provides 100 Ω differential

input termination. For differential amplitude,

see Figure 3.

Load is ac-coupled to measurement

equipment that provides 100 Ω differential

input termination.

Load is ac-coupled to measurement

equipment that provides 100 Ω differential

input termination.

Load is dc-coupled to a 100 Ω differential

resistor into 1 MΩ terminated measurement

equipment, outputs static.

Load is dc-coupled to a 100 Ω differential

resistor into 1 MΩ terminated measurement

equipment, outputs static.

Load is dc-coupled to a 100 Ω differential

resistor into 1 MΩ terminated measurement

equipment, output shorted to GND.

Termination is high impedance active probe;

total C

LOAD

= 5 pF, R

LOAD

= 20 kΩ.

Rev. 0 | Page 13 of 44

AD9577 Data Sheet

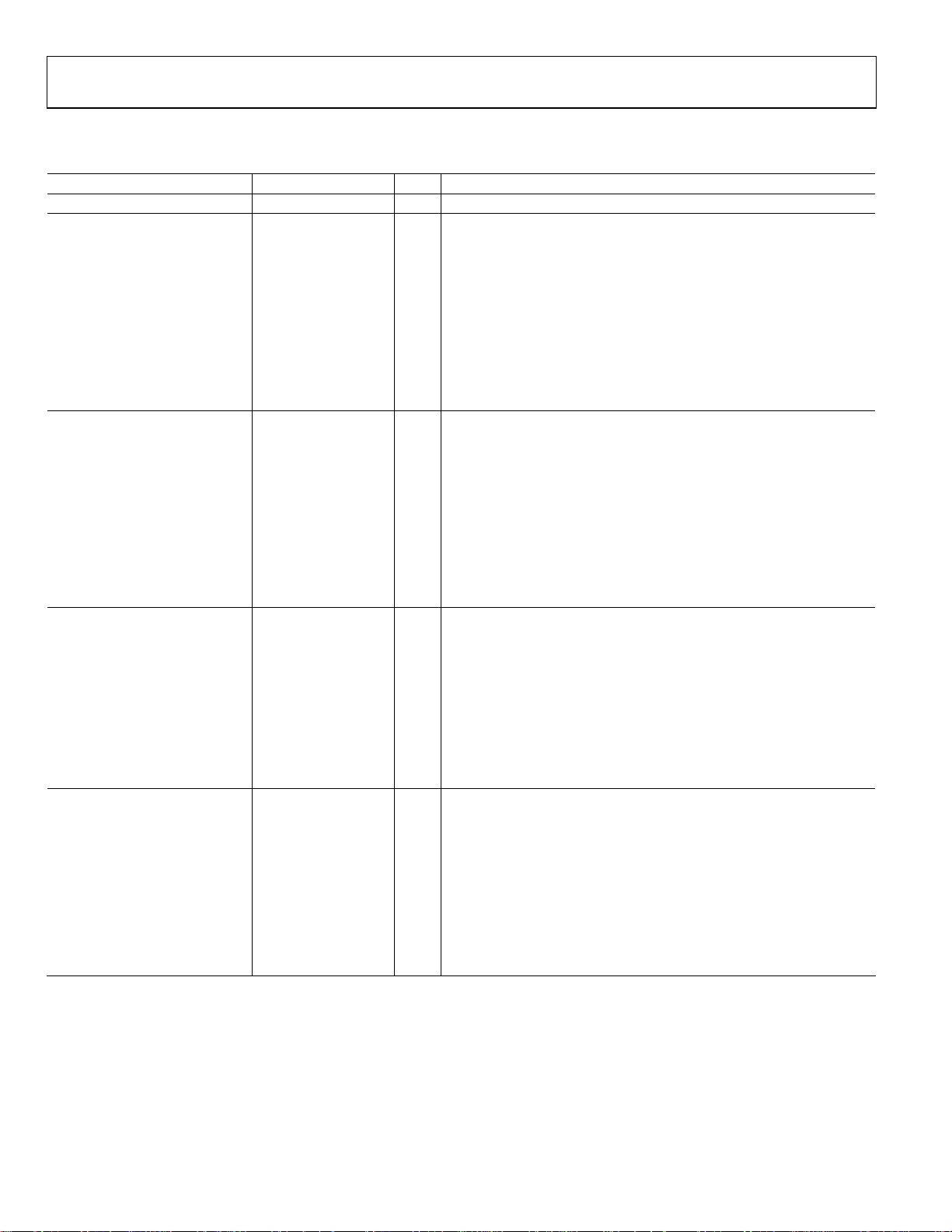

POWER

Table 9.

Parameter Min Typ Max Unit Test Conditions/Comments

POWER SUPPLY 3.0 3.3 3.6 V

LVPECL POWER DISSIPATION 1235 1490 mW

1270 1530 mW

LVDS POWER DISSIPATION 1020 1200 mW

1085 1290 mW

CMOS POWER DISSIPATION 1065 1380 mW

1190 1510 mW

POWER CHANGES

Power-Down 1 LVPECL Channel 160 205 mW

Power-Down 1 LVDS Channel 105 155 mW

Power-Down 1 CMOS Channel 130 170 mW Eight single-ended outputs active, C

Typical part configuration, both PLLs enabled for integer-N operation,

= 156.25 MHz, f

f

OUT0

= 125 MHz, f

OUT1

= 100 MHz, f

OUT2

= 33.33 MHz,

OUT3

Na = 100, V0 = 4, D0 = 4, V1 = 4, D1 = 5, Nb = 96, V2 = 4, D2 = 6, V3 = 4,

D3 = 18, 25 MHz crystal used, load is 200 Ω to GND at output pins, then

ac-coupled to 50 Ω terminated measurement equipment

Worst-case part configuration, PLL2 in fractional-N mode, with SSCG

enabled, f

f

= 359.33 MHz, Na = 91, V0 = 3, D0 = 2, V1 = 3, D1 = 2, Nb = 86,

OUT3

= 379.16 MHz, f

OUT0

= 379.16 MHz, f

OUT1

= 359.33 MHz,

OUT2

V2 = 3, D2 = 2, V3 = 3, D3 = 2, FRAC = 300, MOD = 1250, CkDiv = 5,

NumSteps = 77, FracStep = −7, −0.5% downspread at 32 kHz,

25 MHz crystal used, load is 200 Ω to GND at output pins, then

ac-coupled to 50 Ω terminated measurement equipment

Typical part configuration, both PLLs enabled for integer-N operation,

f

= 156.25 MHz, f

OUT0

= 125 MHz, f

OUT1

= 100 MHz, f

OUT2

= 33.33 MHz,

OUT3

Na = 100, V0 = 4, D0 = 4, V1 = 4, D1 = 5, Nb = 96, V2 = 4, D2 = 6, V3 = 4,

D3 = 18, 25 MHz crystal used, load ac-coupled to measurement

equipment that provides 100 Ω differential input termination

Worst-case part configuration, PLL2 in fractional-N mode, with SSCG

enabled, f

= 359.33 MHz, Na = 91, V0 = 3, D0 = 2, V1 = 3, D1 = 2, Nb = 86,

f

OUT3

= 379.16 MHz, f

OUT0

= 379.16 MHz, f

OUT1

= 359.33 MHz,

OUT2

V2 = 3, D2 = 2, V3 = 3, D3 = 2, FRAC = 300, MOD = 1250, CkDiv = 5,

NumSteps = 77, FracStep = −7, −0.5% downspread at 32 kHz,

25 MHz crystal used, load ac-coupled to measurement equipment

that provides 100 Ω differential input termination

Typical part configuration, both PLLs enabled for integer-N operation,

f

= 156.25 MHz, f

OUT0

= 125 MHz, f

OUT1

= 100 MHz, f

OUT2

= 33.33 MHz,

OUT3

Na = 100, V0 = 4, D0 = 4, V1 = 4, D1 = 5, Nb = 96, V2 = 4, D2 = 6, V3 = 4,

D3 = 18, 25 MHz crystal used, eight single-ended outputs active,

= 5 pF

C

LOAD

Worst-case part configuration, PLL2 in fractional-N mode, with SSCG

enabled, f

f

= 179.66 MHz, Na = 91, V0 = 3, D0 = 4, V1 = 3, D1 = 4, Nb = 86,

OUT3

= 189.58 MHz, f

OUT0

= 189.58 MHz, f

OUT1

= 179.66 MHz,

OUT2

V2 = 3, D2 = 4, V3 = 3, D3 = 4, FRAC = 300, MOD = 1250, CkDiv = 5,

NumSteps = 77, FracStep = −7, −0.5% downspread at 32 kHz,

25 MHz crystal used, eight single-ended outputs active, C

LOAD

= 5 pF

Reduction in power due to turning off a channel of one VCO divider,

one output divider, and one output buffer; data for Channel 1, with

typical part configuration, both PLLs enabled for integer-N operation,

f

= 156.25 MHz, f

OUT0

= 125 MHz, f

OUT1

= 100 MHz, f

OUT2

= 33.33 MHz,

OUT3

Na = 100, V0 = 4, D0 = 4, V1 = 4, D1 = 5, Nb = 96, V2 = 4, D2 = 6, V3 = 4,

D3 = 18, 25 MHz crystal used

Load 200 Ω to GND at output pins, and ac-coupled to 50 Ω terminated

measurement equipment

Load ac-coupled to measurement equipment that provides 100 Ω

differential input termination

= 5 pF

LOAD

Rev. 0 | Page 14 of 44

Loading...

Loading...