Dual/Quad Input Network Clock

FEATURES

Supports Stratum 2 stability in holdover mode

Supports reference switchover with phase build-out

Supports hitless reference switchover

Automatic/manual holdover and reference switchover

2 pairs of reference input pins, with each pair configurable

as a single differential input or as 2 independent single-

ended inputs

Input reference frequencies from 1 kHz to 750 MHz

Reference validation and frequency monitoring (1 ppm)

Programmable input reference switchover priority

30-bit programmable input reference divider

2 pairs of clock output pins, with each pair configurable as

a single differential LVDS/LVPECL output or as 2 single-

ended CMOS outputs

Output frequencies up to 450 MHz

20-bit integer and 10-bit fractional programmable feedback

divider

Programmable digital loop filter covering loop bandwidths

from 0.001 Hz to 100 kHz

Optional low noise LC-VCO system clock multiplier

Optional crystal resonator for system clock input

On-chip EEPROM to store multiple power-up profiles

Software controlled power-down

64-lead LFCSP package

Generator/Synchronizer

AD9547

APPLICATIONS

Network synchronization

Cleanup of reference clock jitter

SONET/SDH clocks up to OC-192, including FEC

Stratum 2 holdover, jitter cleanup, and phase transient

control

Stratum 3E and Stratum 3 reference clocks

Wireless base stations, controllers

Cable infrastructure

Data communications

GENERAL DESCRIPTION

The AD9547 provides synchronization for many systems,

including synchronous optical networks (SONET/SDH). The

AD9547 generates an output clock that is synchronized to one

of two differential or four single-ended external input references.

The digital PLL allows for reduction of input time jitter or phase

noise associated with the external references. The AD9547

continuously generates a clean (low jitter), valid output clock,

even when all references fail, by means of digitally controlled

loop and holdover circuitry.

The AD9547 operates over an industrial temperature range of

−40°C to +85°C.

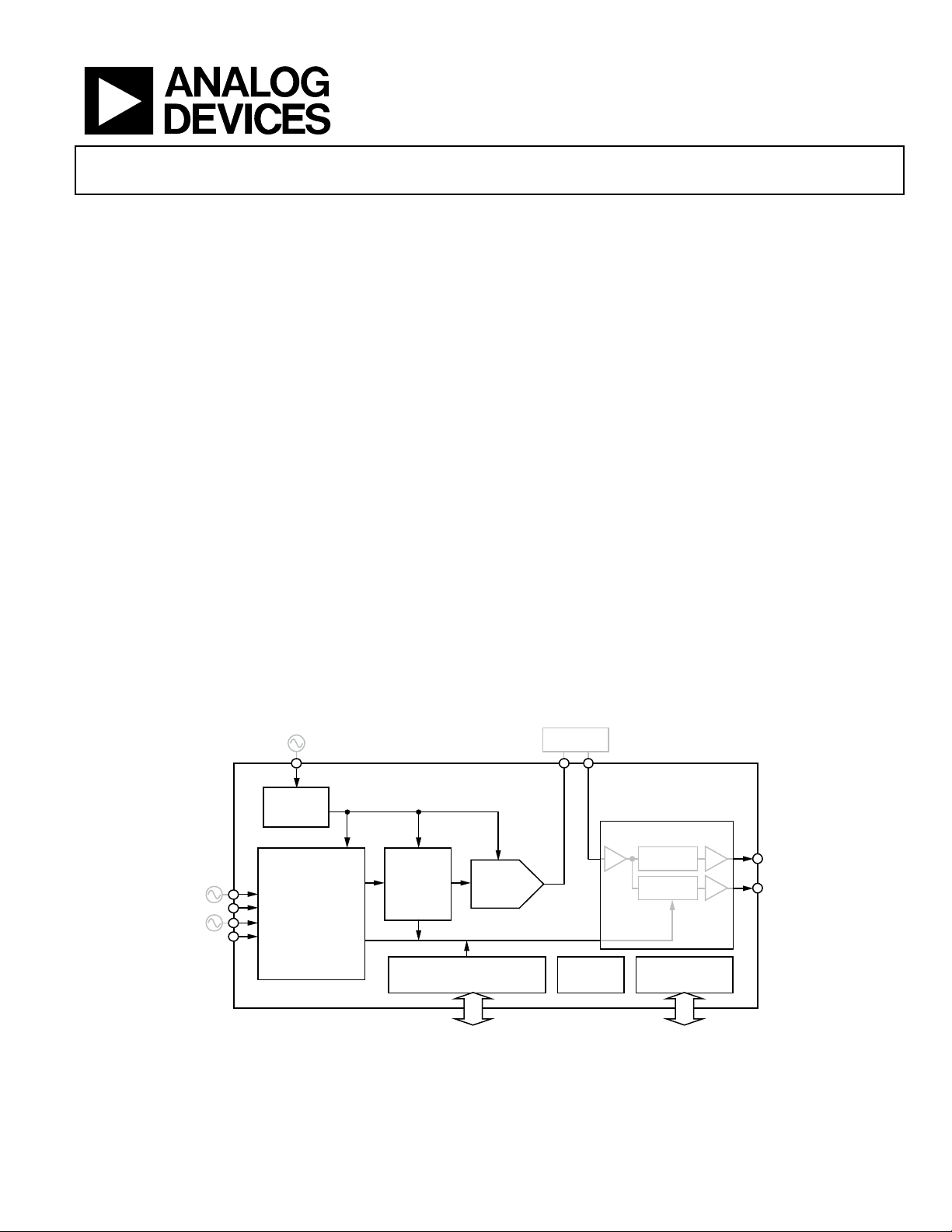

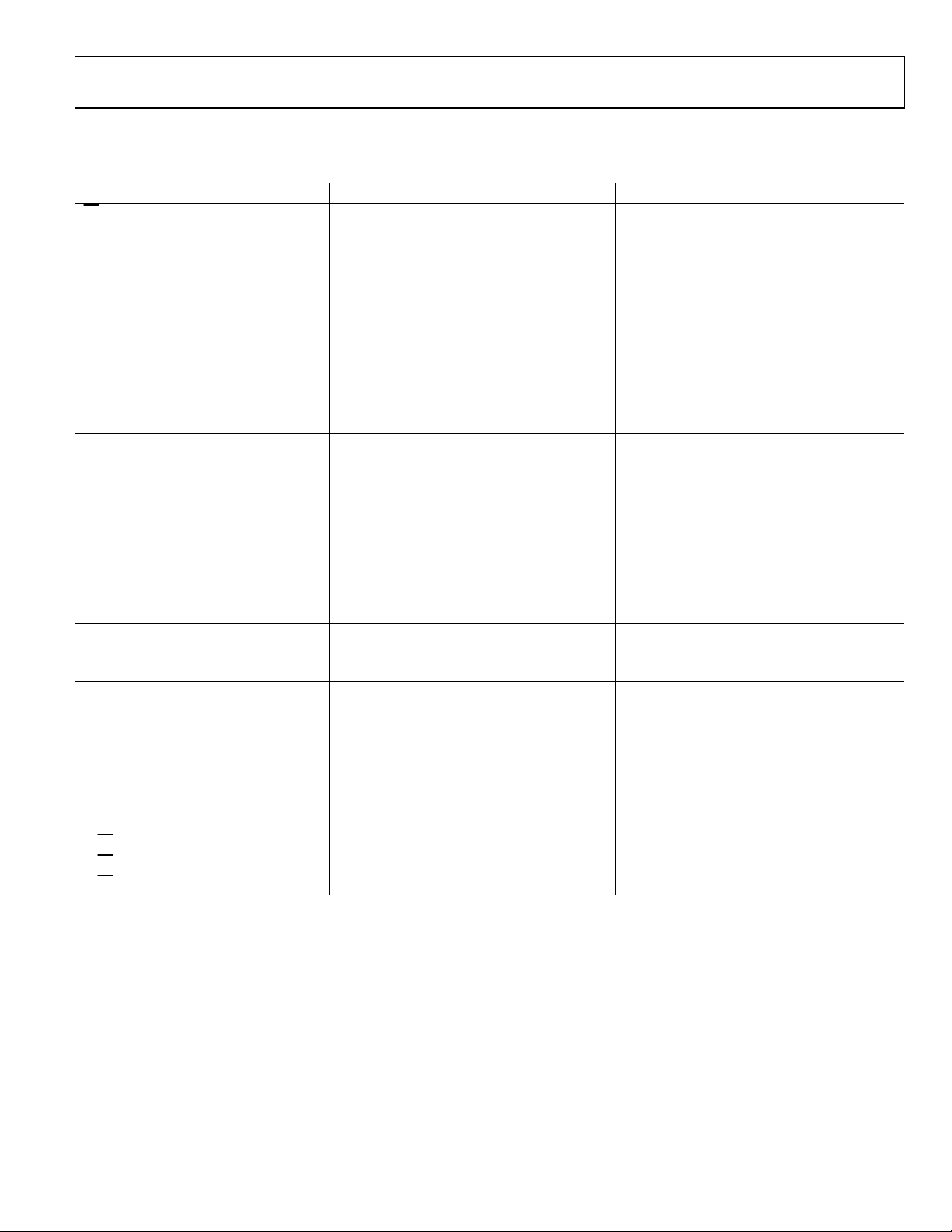

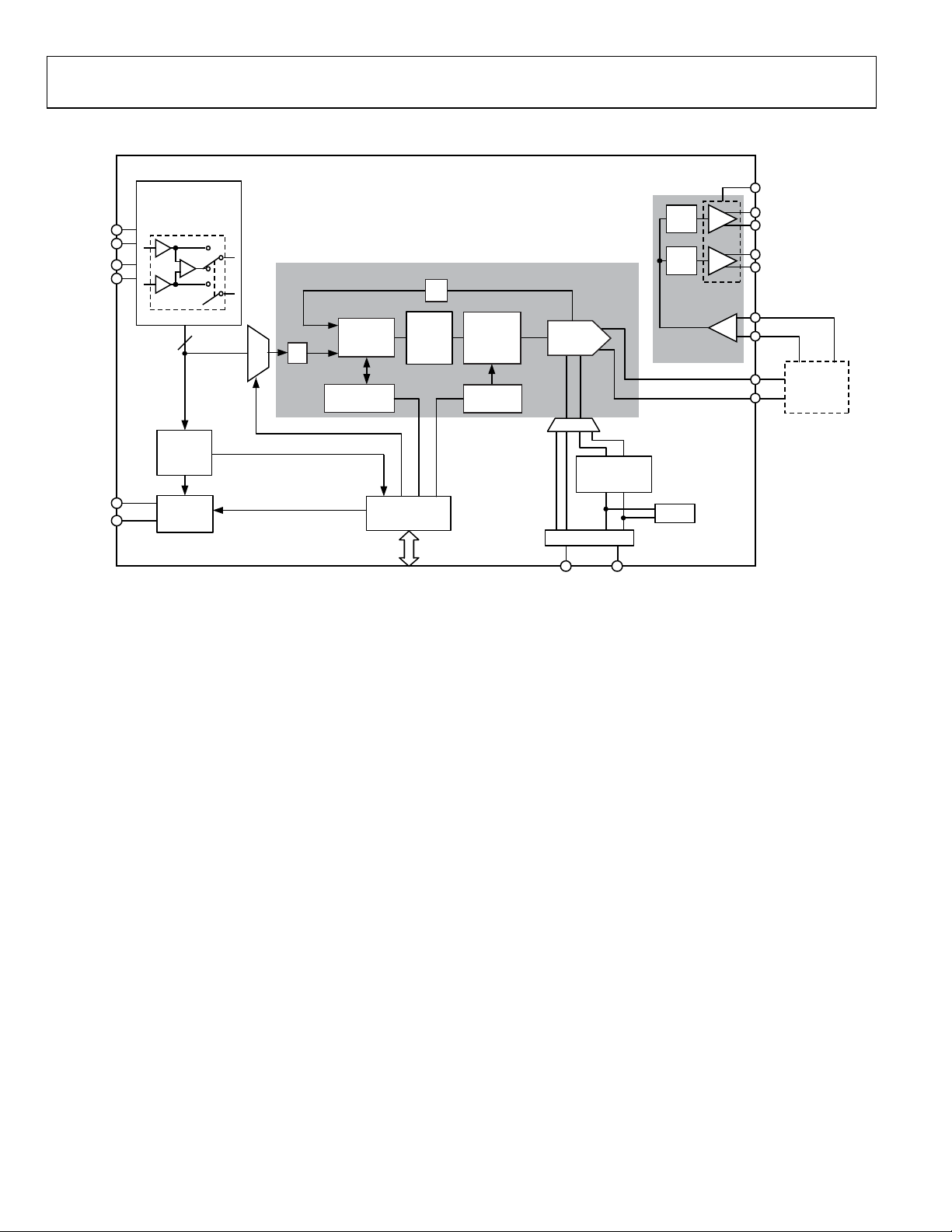

FUNCTIONAL BLOCK DIAGRAM

STABLE

SOURCE

CLOCK

MULTIPLIER

DIGITAL

REFERE NC E INPUT S

AND

MONITOR MUX

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

PLL

SERIAL CONTROL INT ERFACE

(SPI or I

AD9547

DAC

2

C)

Figure 1.

ANALOG

FILTER

CLOCK DIST RIBUTION

CHANNEL 0

DIVIDER

CHANNEL 1

DIVIDER

SYNC

EEPROM

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009–2010 Analog Devices, Inc. All rights reserved.

STATUS AND

CONTROL P INS

08300-001

AD9547

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 3

Specifications ..................................................................................... 4

Supply Voltage ............................................................................... 4

Supply Current .............................................................................. 4

Power Dissipation ......................................................................... 4

Logic Inputs (M0 to M7, RESET) ............................................... 5

Logic Outputs (M0 to M7, IRQ) ................................................ 5

System Clock Inputs (SYSCLKP, SYSCLKN)............................ 5

Distribution Clock Inputs (CLKINP, CLKINN) ...................... 6

Reference Inputs (REFA/REFAA, REFB/REFBB) .................... 7

Reference Monitors ...................................................................... 7

Reference Switchover Specifications .......................................... 8

Distribution Clock Outputs (OUT0, OUT1) ........................... 8

DAC Output Characteristics (DACOUTP, DACOUTN) ....... 9

Time Duration of Digital Functions ........................................ 10

Digital PLL .................................................................................. 10

Digital PLL Lock Detection ...................................................... 10

Holdover Specifications ............................................................. 10

Serial Port Specifications—SPI Mode ...................................... 11

Serial Port Specifications—I2C Mode ...................................... 12

Jitter Generation ......................................................................... 13

Absolute Maximum Ratings .......................................................... 14

ESD Caution ................................................................................ 14

Pin Configuration and Function Descriptions ........................... 15

Typical Performance Characteristics ........................................... 18

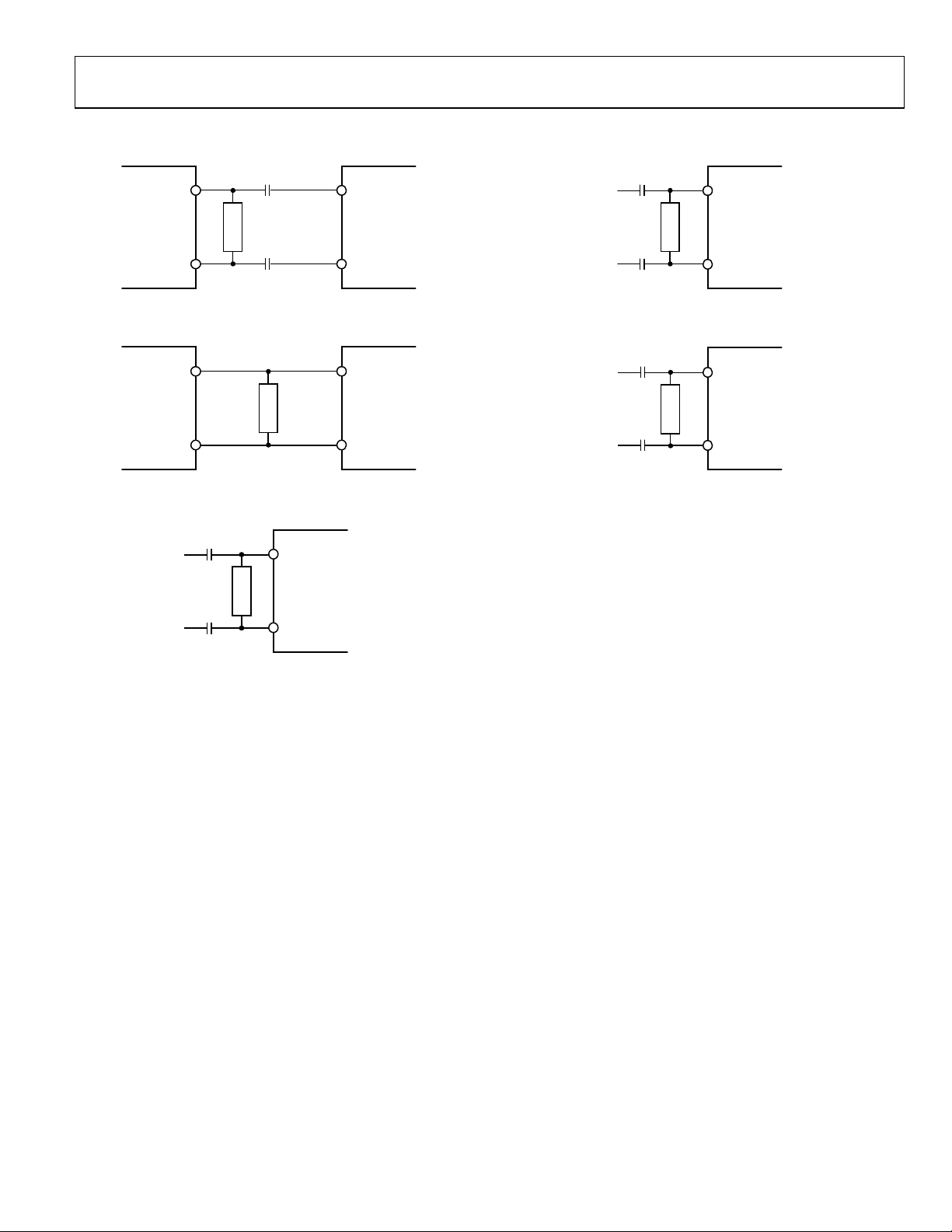

Input/Output Termination Recommendations .......................... 23

Getting Started ................................................................................ 24

Power-On Reset .......................................................................... 24

Initial M0 to M7 Pin Programming ......................................... 24

Device Register Programming .................................................. 24

Theory of Operation ...................................................................... 26

Overview ...................................................................................... 26

Reference Clock Inputs .............................................................. 27

Reference Monitors .................................................................... 27

Reference Profiles ....................................................................... 28

Reference Switchover ................................................................. 30

Rev. B | Page 2 of 104

Digital Phase-Locked Loop (DPLL) Core ............................... 32

Direct Digital Synthesizer (DDS) ............................................. 34

Tuning Word Processing ........................................................... 35

Loop Control State Machine ..................................................... 36

System Clock Inputs ................................................................... 37

SYSCLK PLL Multiplier ............................................................. 38

Clock Distribution ..................................................................... 40

Status and Control .......................................................................... 44

Multifunction Pins (M0 to M7) ............................................... 44

IRQ Pin ........................................................................................ 45

Watchdog Timer ......................................................................... 45

EEPROM ..................................................................................... 46

Serial Control Port ......................................................................... 50

SPI/I2C Port Selection ................................................................ 50

SPI Serial Port Operation .......................................................... 50

IC Serial Port Operation .......................................................... 54

I/O Programming Registers .......................................................... 57

Buffered/Active Registers .......................................................... 57

Autoclearing Registers ............................................................... 57

Register Access Restrictions ...................................................... 57

Register Map ................................................................................... 58

Register Bit Descriptions ............................................................... 67

Serial Port Configuration and Part Identification (Register

0x0000 to Register 0x0005) ....................................................... 67

System Clock (SYSCLK) (Register 0x0100 to Register 0x0108)

....................................................................................................... 68

General Configuration (Register 0x0200 to Register 0x0214)

....................................................................................................... 69

DPLL Configuration (Register 0x0300 to Register 0x031B) 72

Clock Distribution Output Configuration (Register 0x0400 to

Register 0x0417) ......................................................................... 74

Reference Input Configuration (Register 0x0500 to Register

0x0507) ......................................................................................... 76

Profile Registers (Register 0x0600 to Register 0x07FF) ........ 78

Operational Controls (Register 0x0A00 to Register 0x0A10)

....................................................................................................... 88

Status Readback (Register 0x0D00 to Register 0x0D19) ...... 92

Nonvolatile Memory (EEPROM) Control (Register 0x0E00 to

Register 0x0E03) ......................................................................... 94

EEPROM Storage Sequence (Register 0x0E10 to Register

0x0E3F) ........................................................................................ 95

Applications Information .............................................................. 98

AD9547

Power Supply Partitions ............................................................. 98

Thermal Performance ................................................................. 98

Calculating the Digital Filter Coefficients ............................... 99

REVISION HISTORY

11/10—Rev. A to Rev. B

Changes to Pulse Width High, t

SCLK to Valid SDIO and SDO, t

Changes to Addr 0x0002, Def Column, Table 36 and Addr

0x0003, Def Column, Table 36 ...................................................... 58

Changes to Addr 0x0632, Table 36 ............................................... 61

Changes to Addr 0x0680, Table 36 ............................................... 62

Changes to Addr 0x06B2, Table 36 ............................................... 63

Changes to Address 0x0002, Description, Table 39 .................... 67

Changes to Bit 7 and Bit 6, Table 78 ............................................. 78

Changes to Address 0x629 and Address 0x62A, Table 87, and

Bit 7 and Bit 6, Table 88 .................................................................. 80

Changes to Address 0x65B and Address 0x65C, Table 97, and

Bit 7 and Bit 6, Table 98 .................................................................. 82

Changes to Address 0x6A9 and Address 0x6AA, Table 107 ..... 84

Changes to Bit 7 and Bit 6, Table 108 ........................................... 85

Changes to Address 0x6DB and Address 0x6DC, Table 117 ..... 87

Parameter, Table 17 and

HIGH

Parameter, Table 17 ............ 11

DV

Outline Dimensions ...................................................................... 102

Ordering Guide ......................................................................... 102

9/10—Rev. 0 to Rev. A

Change to Frequency Range (CMOS), Single-Ended Operation

Parameter, Table 8 ............................................................................. 7

Added Low Loop Bandwidth Applications Using a

TCXO/OCXO Section and Choosing the System Clock

Oscillator Frequency Section ......................................................... 37

Moved System Clock Period Section ............................................ 39

7/09—Revision 0: Initial Version

Rev. B | Page 3 of 104

AD9547

SPECIFICATIONS

Minimum and maximum values apply for the full range of supply voltage and operating temperature variation. Typical values apply for

AVDD3 = DVDD3 = 3.3 V, AVDD = DVDD

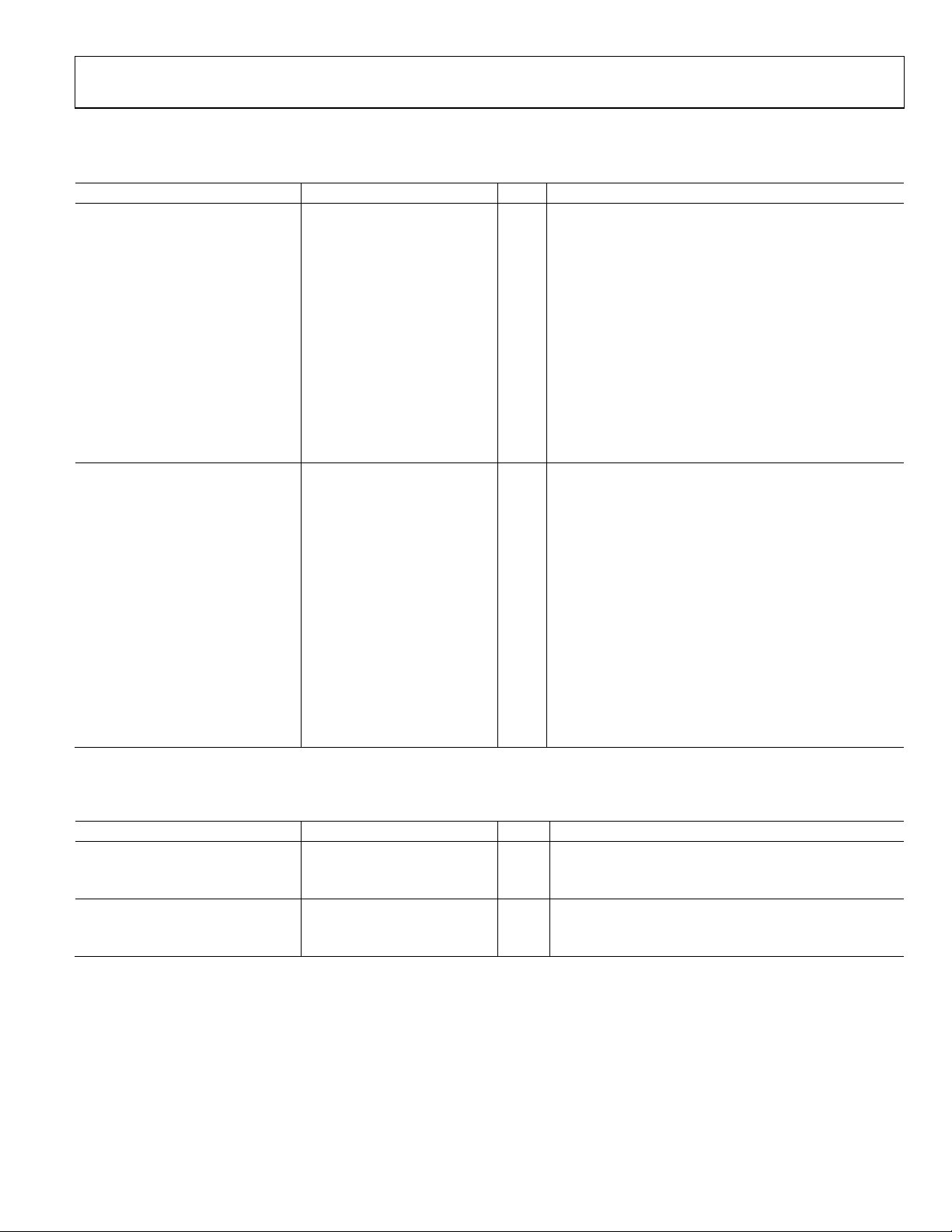

SUPPLY VOLTAGE

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments

DVDD3 3.135 3.30 3.465 V Pin 7, Pin 58

DVDD 1.71 1.80 1.89 V Pin 1, Pin 6, Pin 8, Pin 10, Pin 11, Pin 53, Pin 59, Pin 64

AVDD3 3.135 3.30 3.465 V Pin 16, Pin 33, Pin 43, Pin 49

3.3 V Supply (Typical) 3.135 3.30 3.465 V Pin 25, Pin 31

1.8 V Supply (Alternative) 1.71 1.80 1.89 V Pin 25, Pin 31

AVDD 1.71 1.80 1.89 V Pin 17, Pin 18, Pin 23, Pin 28, Pin 32, Pin 36, Pin 39, Pin 42, Pin 46, Pin 50

SUPPLY CURRENT

The test conditions for the maximum supply current are the same as the test conditions for the All Blocks Running section of Tab le 3 . The

test conditions for the typical supply current are the same as the test conditions for the Typical Configuration section of Tabl e 3.

Table 2.

Parameter Min Typ Max Unit Test Conditions/Comments

I

1.5 3 mA Pin 7, Pin 58

DVDD3

I

190 215 mA Pin 1, Pin 6, Pin 8, Pin 10, Pin 11, Pin 53, Pin 59, Pin 64

DVDD

I

52 70 mA Pin 16, Pin 33, Pin 43, Pin 49

AVDD3

3.3 V Supply (Typical) 24 55 mA Pin 25, Pin 31

1.8 V Supply (Alternative) 24 55 mA Pin 25, Pin 31

I

135 150 mA Pin 17, Pin 18, Pin 23, Pin 28, Pin 32, Pin 36, Pin 39, Pin 42, Pin 46, Pin 50

AVDD

= 1.8 V, TA = 25°C, I

= 20 mA (full scale), unless otherwise noted.

DAC

POWER DISSIPATION

Table 3.

Parameter Min Typ Max Unit Test Conditions/Comments

TYPICAL CONFIGURATION 800 1100 mW

ALL BLOCKS RUNNING 900 1250 mW

FULL POWER-DOWN 13 mW

INCREMENTAL POWER DISSIPATION

SYSCLK PLL Off −105 mW f

Input Reference On

Differential 7 mW

Single-Ended 13 mW

Output Distribution Driver On

LVDS 70 mW

LVPECL 75 mW

CMOS 65 mW Single 3.3 V CMOS output with a 10 pF load

1

f

is the frequency at the SYSCLKP and SYSCLKN pins.

SYSCLK

2

fS is the sample rate of the output DAC.

3

f

is the output frequency of the DDS.

DDS

= 20 MHz1; fS = 1 GHz2; f

f

SYSCLK

DDS

distribution output running at 122.88 MHz (all others powered

down); one input reference running at 100 MHz (all others

powered down)

= 20 MHz1; fS = 1 GHz2; f

f

SYSCLK

= 399 MHz3; all clock distribution

DDS

outputs configured as LVPECL at 399 MHz; all input references

configured as differential at 100 MHz; fractional-N active (R = 10,

S = 39, U = 9, V = 10)

Conditions = typical configuration; no external pull-up or pulldown resistors

Conditions = typical configuration; table values show the change

in power due to the indicated operation

= 1 GHz1; high frequency direct input mode

SYSCLK

= 122.88 MHz3; one LVPECL clock

Rev. B | Page 4 of 104

AD9547

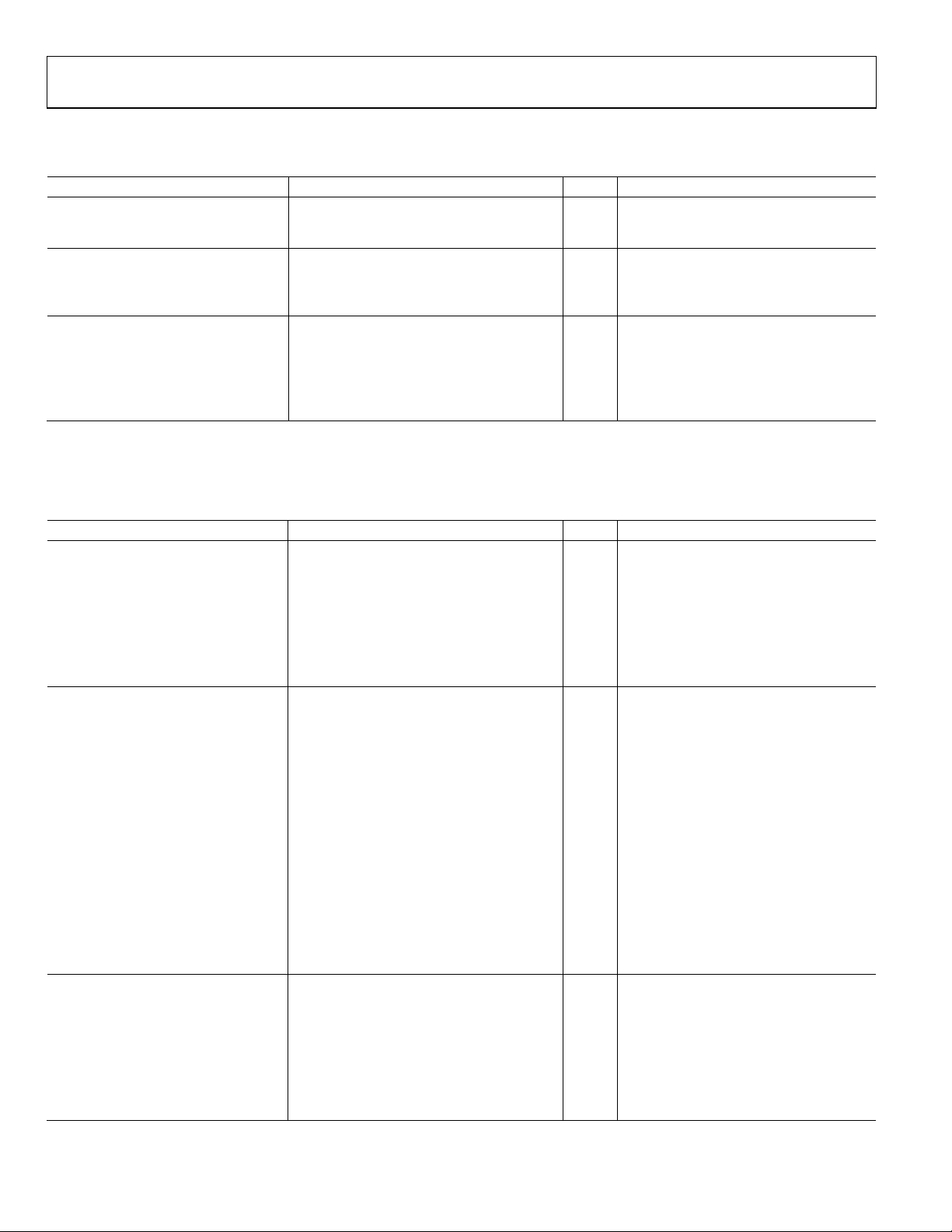

LOGIC INPUTS (M0 TO M7, RESET)

Table 4.

Parameter Min Typ Max Unit Test Conditions/Comments

INPUT VOLTAGE

Input High Voltage (VIH) 2.1 V

Input Low Voltage (VIL) 0.8 V

INPUT CURRENT (I

INPUT CAPACITANCE (CIN) 3 pF

LOGIC OUTPUTS (M0 TO M7, IRQ)

Table 5.

Parameter Min Typ Max Unit Test Conditions/Comments

OUTPUT VOLTAGE

Output High Voltage (VOH) 2.7 V IOH = 1 mA

Output Low Voltage (VOL) 0.4 V IOL = 1 mA

IRQ LEAKAGE CURRENT Open-drain mode

Active Low Output Mode 1 µA VOH = 3.3 V

Active High Output Mode 1 µA VOL = 0 V

SYSTEM CLOCK INPUTS (SYSCLKP, SYSCLKN)

, I

) ±80 ±200 µA

INH

INL

Table 6.

Parameter Min Typ Max Unit Test Conditions/Comments

SYSTEM CLOCK PLL BYPASSED

Input Frequency Range 500 1000 MHz

Minimum Input Slew Rate 1000 V/µs Minimum limit imposed for jitter performance

Duty Cycle 40 60 %

Common-Mode Voltage 1.2 V Internally generated

Differential Input Voltage Sensitivity 100 mV p-p

Input Capacitance 2 pF Single-ended, each pin

Input Resistance 2.5 kΩ

SYSTEM CLOCK PLL ENABLED

PLL Output Frequency Range 900 1000 MHz

Phase Frequency Detector (PFD) Rate 150 MHz

Frequency Multiplication Range 6 255 Assumes valid system clock and PFD rates

VCO Gain 70 MHz/V

High Frequency Path

Input Frequency Range 100.1 500 MHz

Minimum Input Slew Rate 200 V/µs Minimum limit imposed for jitter performance

Frequency Divider Range 1 8 Binary steps (M = 1, 2, 4, 8)

Common-Mode Voltage

Differential Input Voltage Sensitivity 100 mV p-p

Input Capacitance 3 pF Single-ended, each pin

Input Resistance 2.5 kΩ

1 V Internally generated

Minimum voltage across pins is required to ensure

switching between logic states; the instantaneous

voltage on either pin must not exceed the supply rails;

ac ground the unused input to accommodate singleended operation

This is the minimum voltage required across the pins to

ensure switching between logic states; the

instantaneous voltage on either pin must not exceed

the supply rails; ac ground the unused input to

accommodate single-ended operation

Rev. B | Page 5 of 104

AD9547

Parameter Min Typ Max Unit Test Conditions/Comments

Low Frequency Path

Input Frequency Range 3.5 100 MHz

Minimum Input Slew Rate 50 V/µs Minimum limit imposed for jitter performance

Common-Mode Voltage 1.2 V Internally generated

Differential Input Voltage Sensitivity 100 mV p-p

Input Capacitance 3 pF Single-ended, each pin

Input Resistance 4 kΩ

Crystal Resonator Path

Crystal Resonator Frequency Range 10 50 MHz Fundamental mode, AT cut

Maximum Crystal Motional

Resistance

100 Ω See the System Clock Inputs section for recommendations

DISTRIBUTION CLOCK INPUTS (CLKINP, CLKINN)

Table 7.

Parameter Min Typ Max Unit Test Conditions/Comments

INPUT FREQUENCY RANGE 62.5 500 MHz

MINIMUM SLEW RATE 75 V/µs Minimum limit imposed for jitter performance

COMMON-MODE VOLTAGE 700 mV Internally generated

DIFFERENTIAL INPUT VOLTAGE SENSITIVITY 100 mV p-p

DIFFERENTIAL INPUT POWER SENSITIVITY −15 dBm

INPUT CAPACITANCE 3 pF

INPUT RESISTANCE 5 kΩ Each pin has a 2.5 kΩ internal dc bias resistance

This is the minimum voltage required across the pins to

ensure switching between logic states; the

instantaneous voltage on either pin must not exceed

the supply rails; ac ground the unused input to

accommodate single-ended operation

Capacitive coupling required; ac ground the unused

input to accommodate single-ended operation; the

instantaneous voltage on either pin must not exceed

the supply rails

Same as voltage sensitivity but specified as power into a

50 Ω load

Rev. B | Page 6 of 104

AD9547

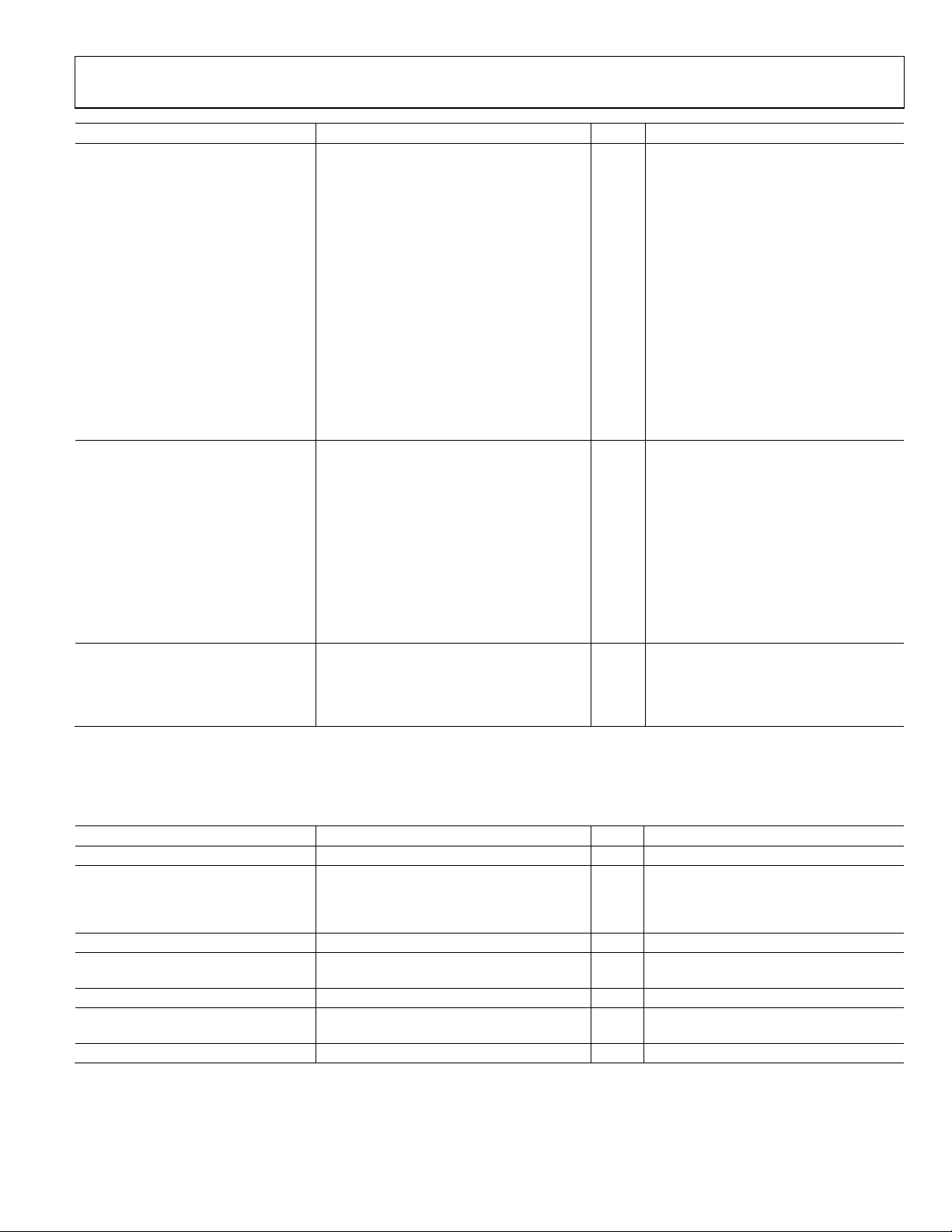

REFERENCE INPUTS (REFA/REFAA, REFB/REFBB)

Table 8.

Parameter Min Typ Max Unit Test Conditions/Comments

DIFFERENTIAL OPERATION

Frequency Range

Sinusoidal Input 10 750 MHz

LVPECL Input 0.001 750 MHz

LVDS Input 0.001 750 MHz

Minimum Input Slew Rate 40 V/µs Minimum limit imposed for jitter performance

Common-Mode Input Voltage 2 V Internally generated

Differential Input Voltage

Sensitivity

Input Resistance 25 kΩ

Input Capacitance 3 pF

Minimum Pulse Width High 620 ps

Minimum Pulse Width Low 620 ps

SINGLE-ENDED OPERATION

Frequency Range (CMOS) 0.001 250 MHz

Minimum Input Slew Rate 40 V/µs Minimum limit imposed for jitter performance

Input Voltage High (VIH)

1.2 V to 1.5 V Threshold Setting 0.9 V

1.8 V to 2.5 V Threshold Setting 1.2 V

3.0 V to 3.3 V Threshold Setting 1.9 V

Input Voltage Low (VIL)

1.2 V to 1.5 V Threshold Setting 0.27 V

1.8 V to 2.5 V Threshold Setting 0.5 V

3.0 V to 3.3 V Threshold Setting 1.0 V

Input Resistance 45 kΩ

Input Capacitance 3 pF

Minimum Pulse Width High 1.5 ns

Minimum Pulse Width Low 1.5 ns

±65 mV

This is the minimum voltage required across the pins to

ensure switching between logic states; the instantaneous

voltage on either pin must not exceed the supply rails

REFERENCE MONITORS

Table 9.

Parameter Min Typ Max Unit Test Conditions/Comments

REFERENCE MONITOR

Loss of Reference Detection Time 1.2 NPDP NPDP = nominal phase detector period (NPDP = f

Frequency Out-of-Range Limits 9.54 × 10−7 0.1 ∆f/f

Programmable (lower bound subject to quality of SYSCLK)

REF

TIMERS

Validation Timer 0.001 65.535 sec Programmable in 1 ms increments

Redetect Timer 0.001 65.535 sec Programmable in 1 ms increments

1

f

is the frequency of the active reference; R is the frequency division factor determined by the R divider.

REF

Rev. B | Page 7 of 104

REF

/R)1

AD9547

REFERENCE SWITCHOVER SPECIFICATIONS

Table 10.

Parameter Min Typ Max Unit Test Conditions/Comments

MAXIMUM OUTPUT PHASE

PERTURBATION (PHASE BUILD-OUT

SWITCHOVER)

MAXIMUM TIME/TIME SLOPE

(HITLESS SWITCHOVER)

TIME REQUIRED TO SWITCH TO A NEW

REFERENCE

Hitless Switchover 5 NPDP

Phase Build-Out Switchover 3 NPDP

1

f

is the frequency of the active reference; R is the frequency division factor determined by the R divider.

REF

DISTRIBUTION CLOCK OUTPUTS (OUT0, OUT1)

Table 11.

Parameter Min Typ Max Unit Test Conditions/Comments

LVPECL MODE

Maximum Output Frequency 725 MHz

Rise/Fall Time1 (20% to 80%) 180 315 ps 100 Ω termination across output pins

Duty Cycle 45 55 %

Differential Output Voltage Swing

Common-Mode Output Voltage AVDD3 − 1.5 AVDD3 − 1.3 AVDD3 − 1.05 V Output driver static

LVDS MODE

Maximum Output Frequency 725 MHz

Rise/Fall Time1 (20% to 80%) 200 350 ps 100 Ω termination across the output pins

Duty Cycle 40 60 %

Differential Output Voltage Swing

Balanced (VOD) 247 454 mV

Unbalanced (∆VOD) 50 mV

Offset Voltage

Common Mode (VOS) 1.125 1.375 V Output driver static

Common-Mode Difference (∆VOS) 50 mV

Short-Circuit Output Current 13 24 mA Output driver static

CMOS MODE

Maximum Output Frequency

3.3 V Supply 10 pF load

Strong Drive Strength Setting 250 MHz

Weak Drive Strength Setting 25 MHz

1.8 V Supply 150 MHz

40 200 ps

Assumes a jitter-free reference; satisfies

Telcordia GR-1244-CORE requirements

315 65,535 ns/sec

Minimum/maximum values are programmable upper bounds; a minimum value

ensures <10% error; satisfies Telcordia

GR-1244-CORE requirements

NPDP = nominal phase detector period

(NPDP = f

NPDP = nominal phase detector period

(NPDP = f

Using internal current setting resistor

(nominal 3.12 kΩ)

630 770 910 mV

Magnitude of voltage across pins; output

driver static

Using internal current setting resistor

(nominal 3.12 kΩ)

Voltage swing between output pins;

output driver static

Absolute difference between voltage

swing of normal pin and inverted pin;

output driver static

Voltage difference between pins; output

driver static

Weak drive option not supported for

operating the CMOS drivers using a 1.8 V

supply

REF

REF

/R)1

/R)1

Rev. B | Page 8 of 104

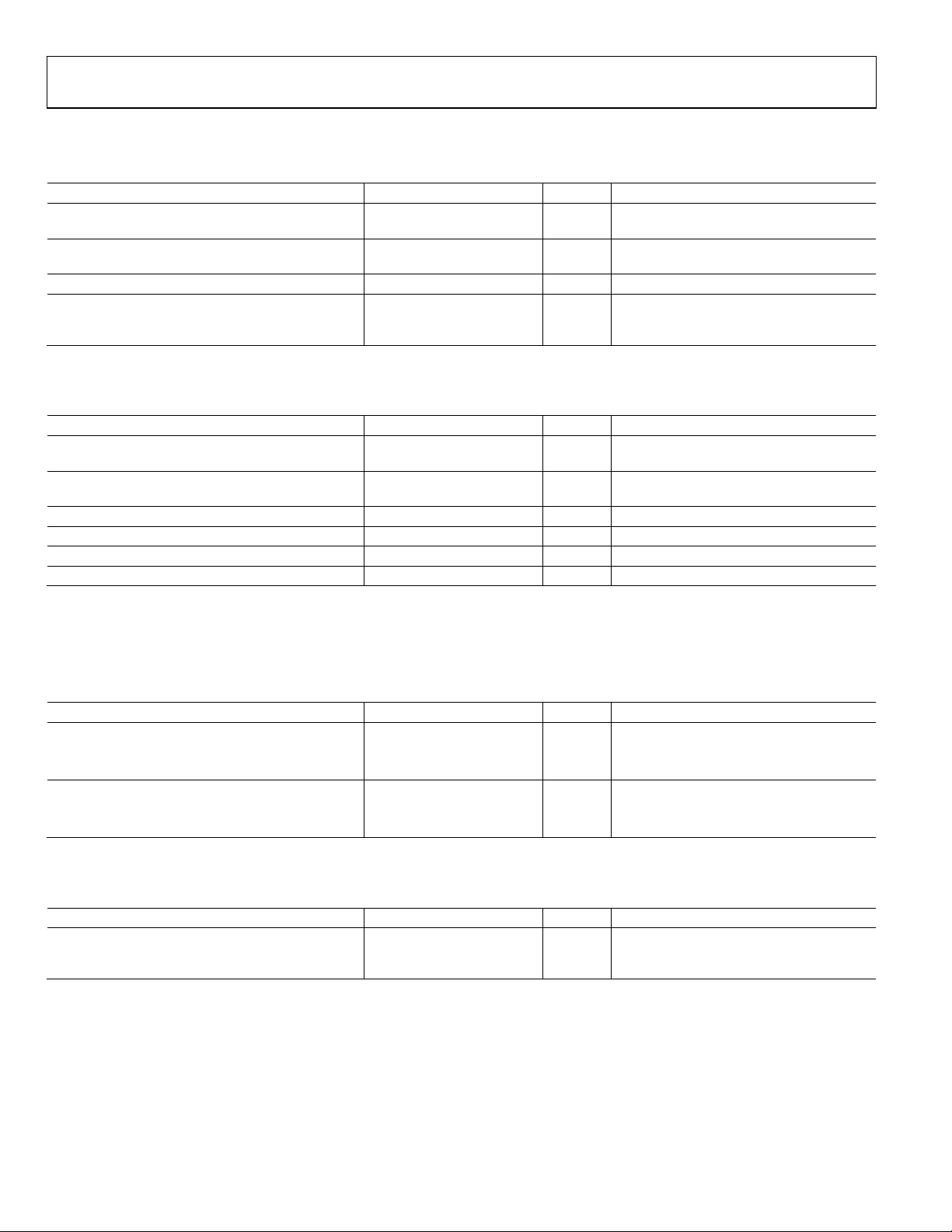

AD9547

Parameter Min Typ Max Unit Test Conditions/Comments

Rise/Fall Time1 (20% to 80%) 10 pF load

3.3 V Supply

Strong Drive Strength Setting 0.5 2 ns

Weak Drive Strength Setting 8 14.5 ns

1.8 V Supply 1.5 2.5 ns

Duty Cycle 40 60 % 10 pF load

Output Voltage High (VOH)

AVDD3 = 3.3 V, IOH = 10 mA 2.6 V

AVDD3 = 3.3 V, IOH = 1 mA 2.9 V

AVDD3 = 1.8 V, IOH = 1 mA 1.5 V

Output Voltage Low (VOL)

AVDD3 = 3.3 V, IOL = 10 mA 0.3 V

AVDD3 = 3.3 V, IOL = 1 mA 0.1 V

AVDD3 = 1.8 V, IOL = 1 mA 0.1 V

OUTPUT TIMING SKEW 10 pF load

Between LVPECL Outputs 14 125 ps Rising edge only; any divide value

Between LVDS Outputs 13 138 ps Rising edge only; any divide value

Between CMOS (3.3 V) Outputs

Strong Drive Strength Setting 23 240 ps

Weak Drive Strength Setting 24 ps

Between CMOS (1.8 V) Outputs 40 ps Weak drive option not supported at 1.8 V

Between LVPECL Outputs and LVDS

Outputs

Between LVPECL Outputs and

CMOS Outputs

ZERO-DELAY TIMING SKEW ±5 ns

1

The listed values are for the slower edge (rising or falling).

14 140 ps

19 ps

Output driver static; strong drive

strength setting

Output driver static; strong drive

strength setting

Output relative to active input reference;

output distribution synchronization to

active reference feature enabled;

assumes manual phase offset

compensation of deterministic latency

DAC OUTPUT CHARACTERISTICS (DACOUTP, DACOUTN)

Table 12.

Parameter Min Typ Max Unit Test Conditions/Comments

FREQUENCY RANGE 62.5 450 MHz

OUTPUT OFFSET VOLTAGE 15 mV

VOLTAGE COMPLIANCE RANGE VSS − 0.5 0.5 VSS + 0.5 V

OUTPUT RESISTANCE 50 Ω

OUTPUT CAPACITANCE 5 pF

FULL-SCALE OUTPUT CURRENT 20 mA

GAIN ERROR −12 +12 % FS

Rev. B | Page 9 of 104

This is the single-ended voltage at either

DAC output pin (no external load) when

the internal DAC code is such that no

current is delivered to that pin

Single-ended; each pin has an internal

50 Ω termination to VSS

Programmable (8 mA to 31 mA; see the

DAC Output section)

AD9547

TIME DURATION OF DIGITAL FUNCTIONS

Table 13.

Parameter Min Typ Max Unit Test Conditions/Comments

EEPROM-TO-REGISTER DOWNLOAD TIME 25 ms

REGISTER-TO-EEPROM UPLOAD TIME 200 ms

MINIMUM POWER-DOWN EXIT TIME 10.5 µs Dependent on loop filter bandwidth

MAXIMUM TIME FROM ASSERTION OF THE RESET PIN

45 ns

TO THE M0 TO M7 PINS ENTERING HIGH

IMPEDANCE STATE

DIGITAL PLL

Table 14.

Parameter Min Typ Max Unit Test Conditions/Comments

PHASE FREQUENCY DETECTOR (PFD) INPUT

FREQUENCY RANGE

LOOP BANDWIDTH 0.001 1 × 105 Hz

PHASE MARGIN 30 89 Degrees Programmable design parameter

REFERENCE INPUT (R) DIVISION FACTOR 1 230 1, 2, …1,073,741,824

INTEGER FEEDBACK (S) DIVISION FACTOR 8 220 8, 9, …1,048,576

FRACTIONAL FEEDBACK DIVIDE RATIO 0 0.999 Maximum value = 1022/1023

1

f

is the frequency at the input to the phase-frequency detector.

PFD

2

fS is the sample rate of the output DAC.

3

f

is the frequency of the active reference; R is the frequency division factor determined by the R divider.

REF

0.001 10 MHz Maximum f

Using default EEPROM storage sequence

(see Register 0x0E10 to Register 0x0E3F)

Using default EEPROM storage sequence

(see Register 0x0E10 to Register 0x0E3F

= fS/100

PFD

1, 2

Programmable design parameter;

maximum f

LOOP

= f

/(20R)3

REF

DIGITAL PLL LOCK DETECTION

Table 15.

Parameter Min Typ Max Unit Test Conditions/Comments

PHASE LOCK DETECTOR

Threshold Programming Range 0.001 65.5 ns

Threshold Resolution 1 ps

FREQUENCY LOCK DETECTOR

Threshold Programming Range 0.001 16,700 ns Reference-to-feedback period difference

Threshold Resolution 1 ps

HOLDOVER SPECIFICATIONS

Table 16.

Parameter Min Typ Max Unit Test Conditions/Comments

FREQUENCY ACCURACY <0.01 ppm

Excludes frequency drift of SYSCLK source;

excludes frequency drift of input reference

prior to entering holdover

Rev. B | Page 10 of 104

AD9547

SERIAL PORT SPECIFICATIONS—SPI MODE

Table 17.

Parameter Min Typ Max Unit Test Conditions/Comments

CS

Input Logic 1 Voltage 2.0 V

Input Logic 0 Voltage 0.8 V

Input Logic 1 Current 30 µA

Input Logic 0 Current 110 µA

Input Capacitance 2 pF

SCLK Internal 30 kΩ pull-down resistor

Input Logic 1 Voltage 2.0 V

Input Logic 0 Voltage 0.8 V

Input Logic 1 Current 1 µA

Input Logic 0 Current 1 µA

Input Capacitance 2 pF

SDIO

As an Input

Input Logic 1 Voltage 2.0 V

Input Logic 0 Voltage 0.8 V

Input Logic 1 Current 1 µA

Input Logic 0 Current 1 µA

Input Capacitance 2 pF

As an Output

Output Logic 1 Voltage 2.7 V 1 mA load current

Output Logic 0 Voltage 0.4 V 1 mA load current

SDO

Output Logic 1 Voltage 2.7 V 1 mA load current

Output Logic 0 Voltage 0.4 V 1 mA load current

TIMING

SCLK

Clock Rate, 1/t

Pulse Width High, t

Pulse Width Low, t

40 MHz

CLK

10 ns

HIGH

12 ns

LOW

SDIO to SCLK Setup, tDS 3 ns

SCLK to SDIO Hold, tDH 0 ns

SCLK to Valid SDIO and SDO, tDV 15 ns

CS to SCLK Setup, tS

CS to SCLK Hold, tC

CS Minimum Pulse Width High

Internal 30 kΩ pull-up resistor

10 ns

0 ns

6 ns

Rev. B | Page 11 of 104

AD9547

SERIAL PORT SPECIFICATIONS—I2C MODE

Table 18.

Parameter Min Typ Max Unit Test Conditions/Comments

SDA (AS INPUT), SCL

Input Logic 1 Voltage 0.7 × DVDD3 V

Input Logic 0 Voltage 0.3 × DVDD3 V

Input Current −10 +10 µA For VIN = 10% to 90% of DVDD3

Hysteresis of Schmitt Trigger Inputs 0.015 × DVDD3 V

Pulse Width of Spikes That Must Be

Suppressed by the Input Filter, t

SP

50 ns

SDA (AS OUTPUT)

Output Logic 0 Voltage 0.4 V IO = 3 mA

Output Fall Time from V

IHmin

to V

20 + 0.1 C

ILmax

1

250 ns 10 pF ≤ Cb ≤ 400 pF

b

TIMING

SCL Clock Rate 400 kHz

Bus Free Time Between a Stop and Start

Condition, t

Repeated Start Condition Setup Time, t

Repeated Hold Time Start Condition, t

Stop Condition Setup Time, t

Low Period of the SCL Clock, t

High Period of the SCL Clock, t

SCL/SDA Rise Time, t

BUF

SU;STA

HD;STA

0.6 µs

SU;STO

1.3 µs

LOW

0.6 µs

R

HIGH

SCL/SDA Fall Time, tF 20 + 0.1 C

Data Setup Time, t

Data Hold Time, t

Capacitive Load for Each Bus Line, C

1

Cb is the capacitance (pF) of a single bus line.

100 ns

SU;DAT

100 ns

HD;DAT

1

400 pF

b

1.3 µs

0.6 µs

0.6 µs

20 + 0.1 C

1

300 ns

b

1

300 ns

b

No internal pull-up/pull-down

resistor

After this period, the first clock

pulse is generated

Rev. B | Page 12 of 104

AD9547

JITTER GENERATION

Table 19.

Parameter Min Typ Max Unit Test Conditions/Comments

CONDITIONS: f

= 100 Hz3

f

LOOP

= 8 kHz1, f

REF

= 155.52 MHz2,

DDS

Bandwidth: 100 Hz to 77 MHz 0.71 ps rms Random jitter

Bandwidth: 5 kHz to 20 MHz 0.34 ps rms Random jitter

Bandwidth: 20 kHz to 80 MHz 0.43 ps rms Random jitter

Bandwidth: 50 kHz to 80 MHz 0.43 ps rms Random jitter

Bandwidth: 4 MHz to 80 MHz 0.31 ps rms Random jitter

CONDITIONS: f

= 1 kHz3

f

LOOP

= 19.44 MHz1, f

REF

= 155.52 MHz2,

DDS

Bandwidth: 100 Hz to 77 MHz 1.05 ps rms Random jitter

Bandwidth: 5 kHz to 20 MHz 0.34 ps rms Random jitter

Bandwidth: 20 kHz to 80 MHz 0.43 ps rms Random jitter

Bandwidth: 50 kHz to 80 MHz 0.43 ps rms Random jitter

Bandwidth: 4 MHz to 80 MHz 0.32 ps rms Random jitter

CONDITIONS: f

= 1 kHz3

f

LOOP

= 19.44 MHz1, f

REF

= 311.04 MHz2,

DDS

Bandwidth: 100 Hz to 100 MHz 0.67 ps rms Random jitter

Bandwidth: 5 kHz to 20 MHz 0.31 ps rms Random jitter

Bandwidth: 20 kHz to 80 MHz 0.33 ps rms Random jitter

Bandwidth: 50 kHz to 80 MHz 0.33 ps rms Random jitter

Bandwidth: 4 MHz to 80 MHz 0.16 ps rms Random jitter

1

f

is the frequency of the active reference.

REF

2

f

is the output frequency of the DDS.

DDS

3

f

is the DPLL digital loop filter bandwidth.

LOOP

4

f

is the frequency at the SYSCLKP and SYSCLKN pins.

SYSCLK

5

fS is the sample rate of the output DAC.

= 50 MHz4 crystal; fS = 1 GHz5;

f

SYSCLK

Q-divider = 1; default SYSCLK PLL charge

pump current; results valid for LVPECL,

LVDS, and CMOS output logic types

= 50 MHz4 crystal; fS = 1 GHz5;

f

SYSCLK

Q-divider = 1; default SYSCLK PLL charge

pump current; results valid for LVPECL,

LVDS, and CMOS output logic types

= 50 MHz4 crystal; fS = 1 GHz5;

f

SYSCLK

Q-divider = 1; default SYSCLK PLL charge

pump current; results valid for LVPECL,

LVDS, and CMOS output logic types

Rev. B | Page 13 of 104

AD9547

ABSOLUTE MAXIMUM RATINGS

Table 20.

Parameter Rating

Analog Supply Voltage (AVDD) 2 V

Digital Supply Voltage (DVDD) 2 V

Digital I/O Supply Voltage

(DVDD3)

DAC Supply Voltage (AVDD3) 3.6 V

Maximum Digital Input Voltage −0.5 V to DVDD3 + 0.5 V

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +85°C

Lead Temperature

(Soldering 10 sec)

Junction Temperature 150°C

3.6 V

300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. B | Page 14 of 104

AD9547

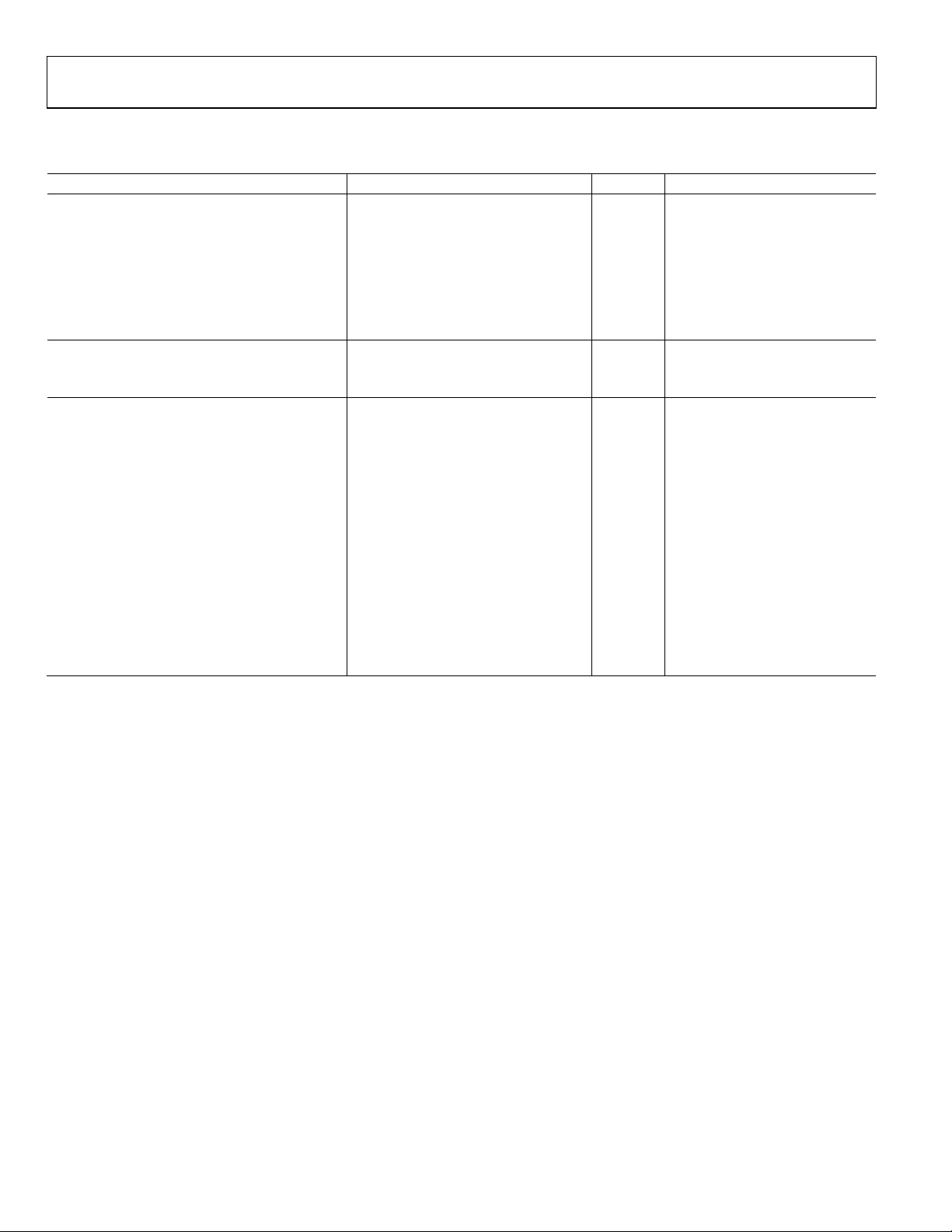

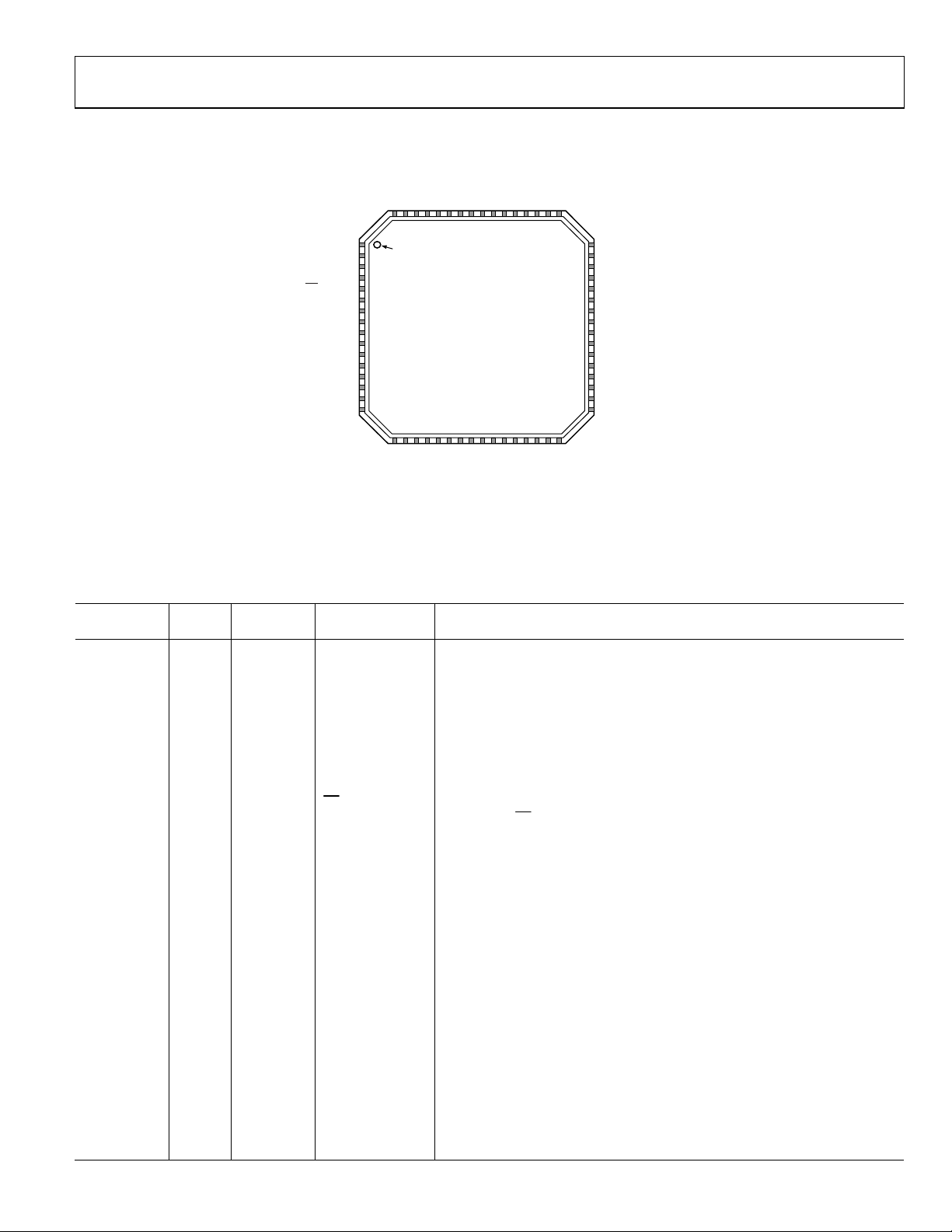

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

DVDDM7M6M5M4

646362616059585756555453525150

DVDD

SCLK/SCL

SDIO

SDO

CS/SDA

DVDD

DVDD3

DVDD

RESET

DVDD

10

DVDD

11

VSS

VSS

AVDD3

12

13

14

15

16

DACOUTP

DACOUTN

NOTES

1. NC = NO CONNEC T.

2. THE EXPOSED PAD MUST BE CONNECTED TO GROUND (VSS).

PIN 1

1

INDICATOR

2

3

4

5

6

7

8

9

171819202122232425262728293031

AVDD

AVDD

VSS

CLKINN

DVDD

DVDD3M3M2M1M0

AD9547

TOP VIEW

(Not to Scale)

VSS

AVDD

CLKINP

OUT_RSET

AVDD3

DVDD

IRQNCAVDD

AVDD3

49

48

REFBB

47

REFB

46

AVDD

45

REFAA

44

REFA

43

AVDD3

42

AVDD

41

TDC_VRT

40

TDC_VRB

39

AVDD

38

SYSCLKP

37

SYSCLKN

36

AVDD

35

SYSCLK_LF

34

SYSCLK_VREG

33

AVDD3

32

AVDD

OUT0P

OUT0N

AVDD

OUT1P

AVDD3

OUT1N

Figure 2. Pin Configuration

Table 21. Pin Function Descriptions

Input/

Pin No.

1, 6, 8, 53, 59,

Output Pin Type Mnemonic Description

I Power DVDD 1.8 V Digital Supply.

64

2 I 3.3 V CMOS SCLK/SCL

3 I/O 3.3 V CMOS SDIO

Serial Programming Clock. Data clock for serial programming. SCLK is used for

SPI mode, and SCL is used for I

2

C® mode.

Serial Data Input/Output. When the device is in 4-wire mode, data is written

via this pin. In 3-wire mode, both data reads and writes occur on this pin.

There is no internal pull-up/pull-down resistor on this pin.

4 O 3.3 V CMOS SDO

Serial Data Output. Use this pin to read data in 4-wire mode (high impedance

in 3-wire mode). There is no internal pull-up/pull-down resistor on this pin.

5 I 3.3 V CMOS

/SDA SPI Mode.

CS

Chip Select (CS) Input. Active low. When programming a device, this pin must

be held low. In systems where more than one AD9547 is present, this pin enables

individual programming of each AD9547. In SPI mode, this pin has an internal

30 kΩ pull-up resistor.

2

C Mode.

I

Serial Data Line (SDA) Input/Output. In I

read operations and an input during write operations. There is no internal

pull-up resistor in I

2

C mode.

7, 58 I Power DVDD3 3.3 V I/O Digital Supply.

9 I 3.3 V CMOS RESET

Chip Reset. Assertion of this pin (active high) resets the device. This pin has an

internal 50 kΩ pull-down resistor.

10, 11 I Power DVDD

1.8 V DAC Decode Digital Supply. Isolate the supply associated with these

DVDD pins from the supply associated with the other DVDD pins.

12, 15, 19, 22 O Ground VSS Analog Ground. Connect to ground.

13 O

Differential

DACOUTP DAC Output. DACOUTP contains an internal 50 Ω pull-down resistor.

output

14 O

Differential

output

DACOUTN

Complementary DAC Output. DACOUTN contains an internal 50 Ω pull-down

resistor.

16 I Power AVDD3 3.3 V Analog (DAC) Power Supply.

17, 18 I Power AVDD 1.8 V Analog (DAC) Power Supply.

Rev. B | Page 15 of 104

08300-002

2

C Mode, this pin is an output during

AD9547

Input/

Pin No.

20 I

21 I

23 I Power AVDD 1.8 V Analog (Input Receiver) Power Supply.

24 O

25, 31 I Power AVDD3

26 O

27 O

28, 32 I Power AVDD 1.8 V Analog (Output Divider) Power Supply.

29 O

30 O

33 I Power AVDD3 3.3 V Analog (System Clock) Power Supply.

34 I SYSCLK_VREG

35 O SYSCLK_LF

36, 39 I Power AVDD 1.8 V Analog (System Clock) Power Supply.

37 I

38 I

40, 41 I

42 I Power AVDD 1.8 V Analog (Time-to-Digital Converter) Power Supply.

43, 49 I Power AVDD3 3.3 V Analog (Reference Input) Power Supply.

44 I

45 I

46, 50 I Power AVDD 1.8 V Analog (Reference Input) Power Supply.

Output Pin Type Mnemonic Description

Differential

input

Differential

input

Current set

resistor

LVPECL,

LVDS, or

CMOS

LVPECL,

LVDS, or

CMOS

LVPECL,

LVDS, or

CMOS

LVPECL,

LVDS, or

CMOS

Differential

input

Differential

input

Differential

input

Differential

input

CLKINN

CLKINP

OUT_RSET

OUT0P

OUT0N

OUT1P

OUT1N

SYSCLKN

SYSCLKP

TDC_VRB,

TDC_VRT

REFA

REFAA

Clock Distribution Input. In standard operating mode, this pin is connected to

the filtered DACOUTN output. This internally biased input is typically ac-coupled,

and, when configured as such, can accept any differential signal with a singleended swing of at least 400 mV.

Clock Distribution Input. In standard operating mode, this pin is connected to

the filtered DACOUTP output.

Connect an optional 3.12 kΩ resistor from this pin to ground (see the Output

Current Control with an External Resistor section).

Analog Supply for Output Driver. These pins are normally 3.3 V but can be

1.8 V. Pin 25 powers OUT0. Pin 31 powers OUT1. Apply power to these pins

even if the corresponding outputs (OUT0P/OUT0N, OUT1P/OUT1N) are not

used. See the Power Supply Partitions section.

Output 0. This output can be configured as LVPECL, LVDS, or single-ended

CMOS. LVPECL and LVDS operation require a 3.3 V output driver power

supply. CMOS operation can be either 1.8 V or 3.3 V, depending on the output

driver power supply.

Complementary Output 0. This output can be configured as LVPECL, LVDS, or

single-ended CMOS.

Output 1. This output can be configured as LVPECL, LVDS, or single-ended

CMOS. LVPECL and LVDS operation require a 3.3 V output driver power

supply. CMOS operation can be either 1.8 V or 3.3 V, depending on the output

driver power supply.

Complementary Output 1. This output can be configured as LVPECL, LVDS, or

single-ended CMOS.

System Clock Loop Filter Voltage Regulator. Connect a 0.1 F capacitor from

this pin to ground. This pin is also the ac ground reference for the integrated

external loop filter of the SYSCLK PLL multiplier (see the SYSCLK PLL Multiplier

section).

System Clock Multiplier Loop Filter. When using the frequency multiplier to

drive the system clock, an external loop filter can be attached to this pin.

Complementary System Clock Input. Complementary signal to SYSCLKP.

SYSCLKN contains internal dc biasing and should be ac-coupled with a 0.01 F

capacitor, except when using a crystal. When using a crystal, connect it across

SYSCLKP and SYSCLKN.

System Clock Input. SYSCLKP contains internal dc biasing and should be accoupled with a 0.01 F capacitor, except when using a crystal. When using a

crystal, connect it directly across SYSCLKP and SYSCLKN. Single-ended 1.8 V

CMOS is also an option but can introduce a spur if the duty cycle is not 50%.

When using SYSCLKP as a single-ended input, connect a 0.01 F capacitor

from SYSCLKN to ground.

Use capacitive decoupling on these pins (see Figure 36).

Reference A Input. This internally biased input is typically ac-coupled and,

when configured as such, can accept any differential signal with a singleended swing of up to 3.3 V. If dc-coupled, input can be LVPECL, CMOS, or LVDS.

Complementary Reference A Input. Complementary signal to the input provided on Pin 44. The user can configure this pin as a separate single-ended input.

Rev. B | Page 16 of 104

AD9547

Input/

Pin No.

47 I

48 I

51 I NC No Connection. This pin should be left floating.

52 O Logic IRQ Interrupt Request Line.

54, 55, 56, 57,

60, 61, 62, 63

EP O

Output Pin Type Mnemonic Description

Differential

input

Differential

input

I/O 3.3 V CMOS

Exposed

pad

REFB

REFBB

M0, M1, M2, M3,

M4, M5, M6, M7

Exposed pad The exposed pad must be connected to ground (VSS).

Reference B Input. This internally biased input is typically ac-coupled and,

when configured as such, can accept any differential signal with a single-ended

swing of up to 3.3 V. If dc-coupled, input can be LVPECL, CMOS, or LVDS.

Complementary Reference B Input. Complementary signal to the input provided

on Pin 47. The user can configure this pin as a separate single-ended input.

Configurable I/O Pins. These pins are configured under program control.

Rev. B | Page 17 of 104

AD9547

–

–

–

–

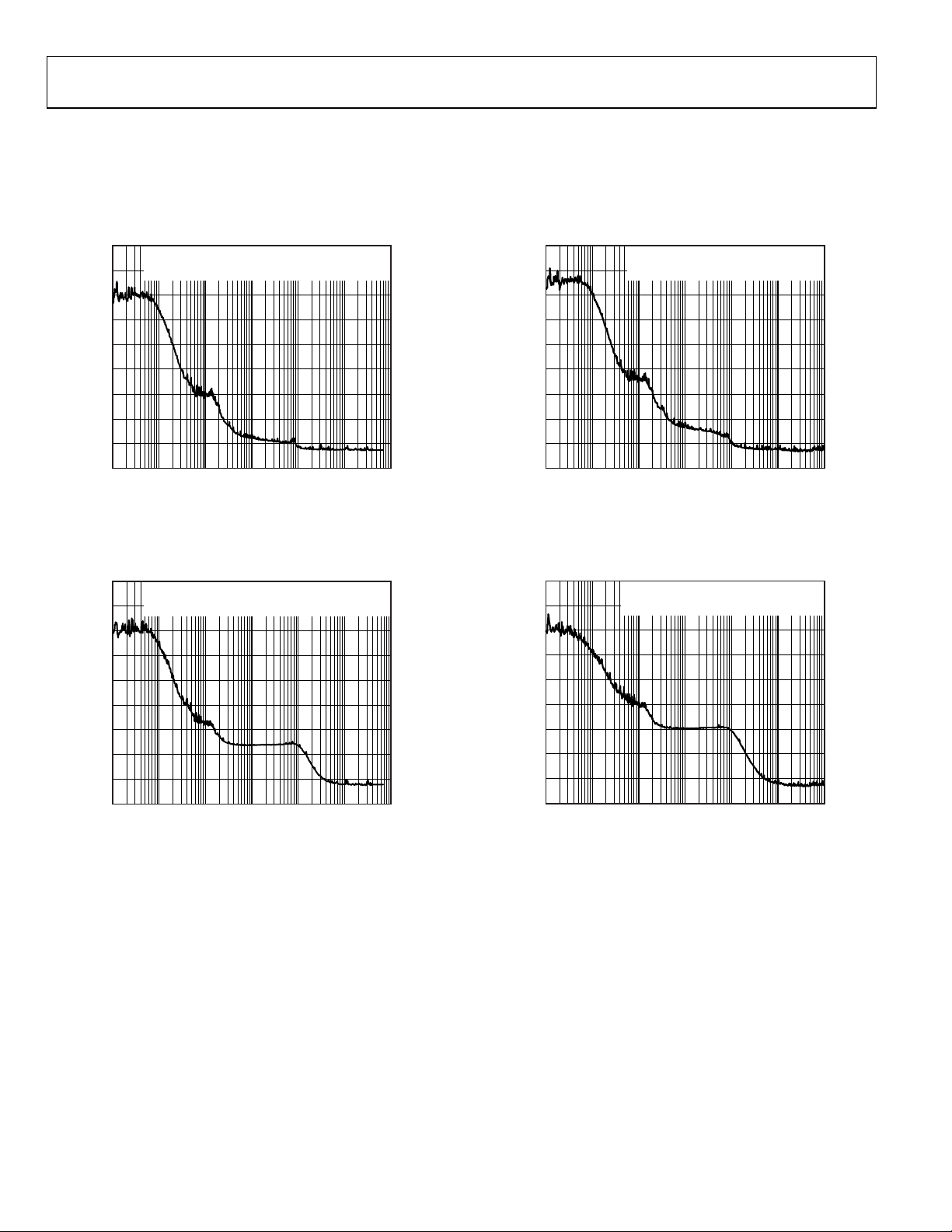

TYPICAL PERFORMANCE CHARACTERISTICS

f

= input reference clock frequency, fO = clock frequency, f

REF

DPLL loop bandwidth, PLL off = SYSCLK PLL bypassed, PLL on = SYSCLK PLL enabled, I

SYSCLK PLL loop filter. AVDD, AVDD3, and DVDD at nominal supply voltage, f

otherwise noted.

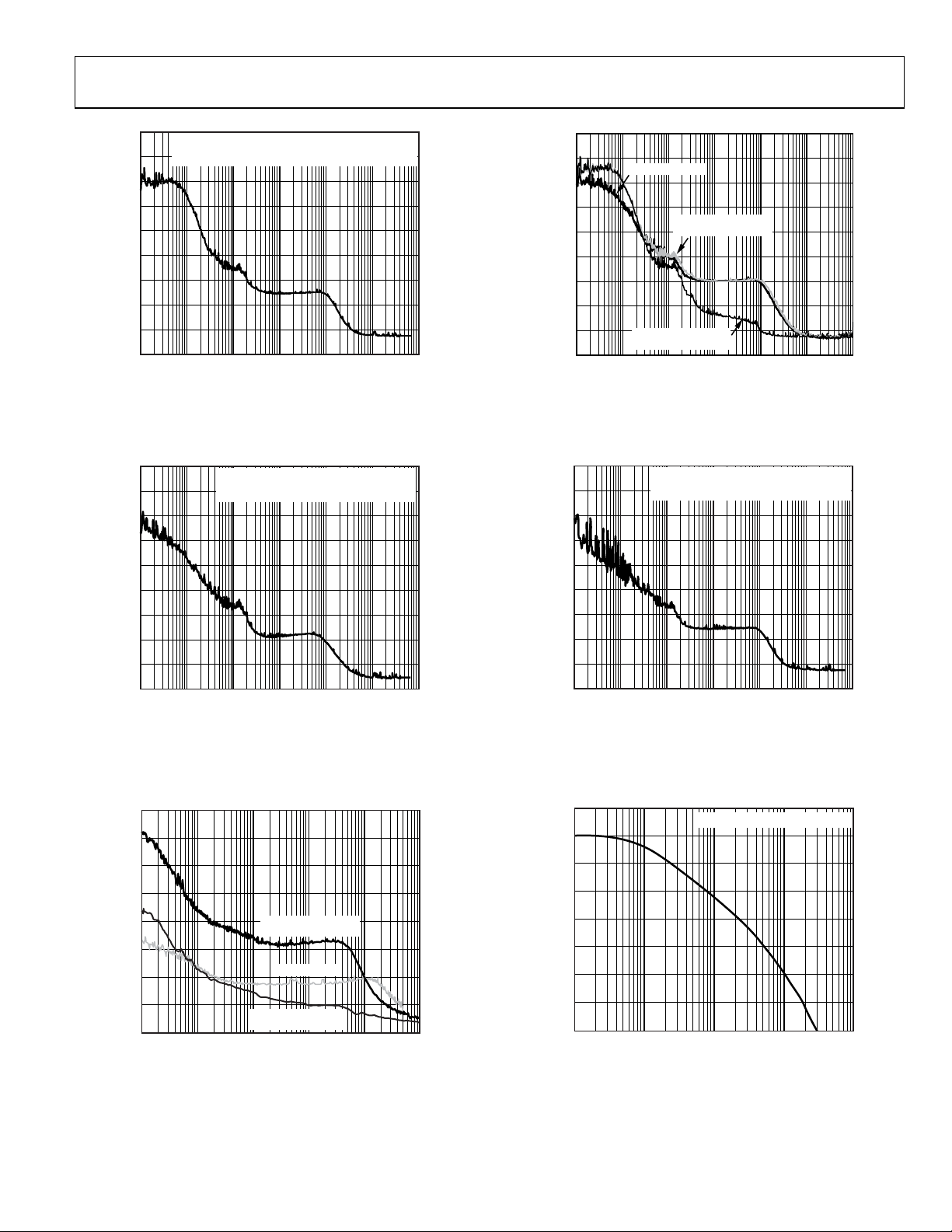

PHASE NOISE (dBc/Hz)

70

–80

–90

–100

–110

–120

–130

–140

–150

–160

INTEGRATED RMS JITTER (PHASE NOISE):

5kHz TO 20MHz: 173fs (–75.4d Bc )

20kHz TO 80MHz : 315 fs (–70.2dBc) ( EXTRAPOLATED)

100 1k 10k 100k 1M 10M 100M

FREQUENCY OFFSET (Hz)

Figure 3. Additive Phase Noise (Output Driver = LVPECL),

f

= 19.44 MHz, fO = 155.52 MHz,

REF

LBW = 1 kHz, f

= 1 GHz, PLL Off

SYSCLK

= SYSCLK input frequency, fS =internal system clock frequency, LBW =

SYSCLK

= SYSCLK PLL charge pump current, LF =

CP

= 1 GHz, ICP = automatic mode, LF = internal, unless

S

70

–80

–90

–100

–110

–120

–130

PHASE NOISE (dBc/Hz)

–140

–150

–160

100 1k 10k 100k 1M 10M 100M

8300-068

INTEGRATED RMS JITTER (PHASE NOISE):

5kHz TO 20MHz: 103fs (–74.0dBc)

20kHz TO 80MHz: 160fs (–70.1dBc)

FREQUENCY OFFSET (Hz)

Figure 5. Additive Phase Noise (Output Driver = LVPECL),

f

= 19.44 MHz, fO = 311.04 MHz,

REF

LBW = 1 kHz, f

= 1 GHz, PLL Off

SYSCLK

8300-066

PHASE NOISE ( dBc/Hz)

70

–80

–90

–100

–110

–120

–130

–140

–150

–160

INTEGRATE D RMS JI T T E R (PHAS E NO I S E) :

5kHz TO 20MHz: 333fs (–69.8dBc)

20kHz TO 80MHz: 430fs (–67.6dBc) (EXTRAPO LATED)

100 1k 10k 100k 1M 10M 100M

FREQUENCY OFFSET (Hz)

Figure 4. Additive Phase Noise (Output Driver = LVPECL),

f

= 19.44 MHz, fO = 155.52 MHz,

REF

LBW = 1 kHz, f

= 50 MHz (Crystal), PLL On

SYSCLK

70

–80

–90

–100

–110

–120

–130

PHASE NOISE (dBc/Hz)

–140

–150

–160

100 1k 10k 100k 1M 10M 100M

8300-056

INTEGRAT E D RM S JITTER (P HASE NOISE):

5kHz TO 20MHz: 310fs (–64.4dBc)

20kHz TO 80MHz: 330fs (–63.9dBc)

FREQUENCY OFFSET (Hz)

08300-067

Figure 6. Additive Phase Noise (Output Driver = LVPECL),

= 19.44 MHz, fO = 311.04 MHz,

f

REF

LBW = 1 kHz, f

= 50 MHz (Crystal), PLL On

SYSCLK

Rev. B | Page 18 of 104

AD9547

–

–

–

–

–

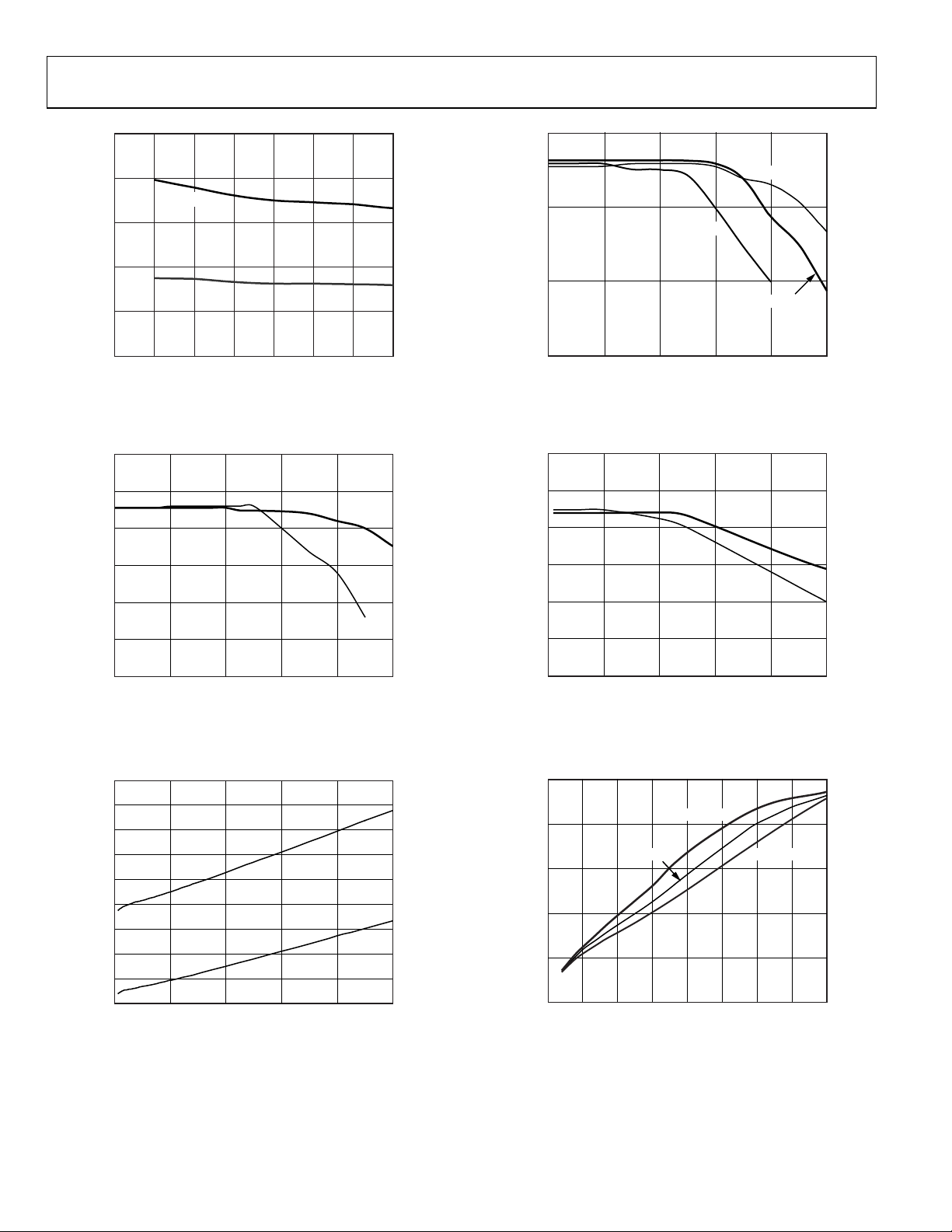

PHASE NOISE (dBc/Hz)

70

–80

–90

–100

–110

–120

–130

–140

–150

–160

INTEGRATED RMS JITTER (PHASE NOISE):

5kHz TO 20MHz: 361fs (–69.0d Bc )

20kHz TO 80MHz : 441 fs (–67.3dBc) ( EXTRAPOLATED)

100 1k 10k 100k 1M 10M 100M

FREQUENCY OFFSET (Hz)

Figure 7. Additive Phase Noise (Output Driver = LVPECL),

= 19.44 MHz, fO = 155.52 MHz,

f

REF

LBW = 1 kHz, f

= 50 MHz, PLL On

SYSCLK

08300-069

70

–80

–90

–100

–110

–120

–130

PHASE NOISE ( dBc/Hz)

–140

–150

–160

100 1k 10k 100k 1M 10M 100M

50MHz CRYSTAL

ROHDE & SCHWARZ

SMA100 (50MHz)

ROHDE & SCHWARZ

SMA100 (1GHz)

FREQUENCY OFFSET (Hz)

Figure 10. Additive Phase Noise Comparison of SYSCLK Input Options

(Output Driver = LVPECL),

f

= 19.44 MHz, fO = 311.04 MHz, LBW = 1 kHz

REF

08300-058

70

–80

–90

–100

–110

–120

–130

PHASE NOISE (dBc/Hz)

–140

–150

–160

100 1k 10k 100k 1M 10M 100M

INTEGRATED RMS JITTER (PHASE NOISE):

12kHz TO 20MHz: 245f s ( –65.0dBc)

20kHz TO 80MHz: 300f s ( –64.3dBc)

FREQUENCY OFFSET (Hz)

Figure 8. Additive Phase Noise (Output Driver = LVPECL),

LBW = 1 kHz, f

2× Frequency Multiplier, I

90

–100

–110

–120

–130

–140

PHASE NOISE (dBc/Hz)

–150

–160

–170

100 1k 10k 100k 1M 10M

= 50 MHz (Crystal), PLL On with

SYSCLK

= 375 μA, LF = External (350 kHz)

CP

ROHDE & SCHWARZ

SMA100 (1GHz)

20MHz OCXO

ROHDE & SCHWARZ

SMA100 (50MHz)

FREQUENCY OF FSET (Hz)

= 19.44 MHz, fO = 155.52 MHz,

f

REF

Figure 9. Phase Noise of SYSCLK Input Sources

70

–80

–90

–100

–110

–120

–130

PHASE NOISE (dBc/Hz)

–140

–150

–160

100 1k 10k 100k 1M 10M 100M

8300-051

INTEGRATED RMS JITTER (PHASE NO I SE):

5kHz TO 20MHz: 336fs (–69.7d Bc)

20kHz TO 80MHz : 425fs (–67.6dBc)

FREQUENCY OFFSET (Hz)

8300-052

Figure 11. Additive Phase Noise (Output Driver = LVPECL),

= 8 kHz, fO = 155.52 MHz,

f

LBW = 100 Hz, f

10

0

–10

–20

–30

–40

CLOSED-LOOP GAIN (dB)

–50

–60

–70

10 100 1k 10k 100k

8300-053

REF

= 50 MHz (Crystal), PLL On

SYSCLK

CLOSED-LOOPPEAKING: 0.04dB

FREQUENCY OFFSET (Hz)

8300-047

Figure 12. Jitter Transfer Bandwidth, Output Driver = LVPECL,

= 19.44 MHz, fO = 155.52 MHz,

f

LBW = 100 Hz (Phase Margin = 88°), f

REF

= 1 GHz, PLL Off

SYSCLK

Rev. B | Page 19 of 104

AD9547

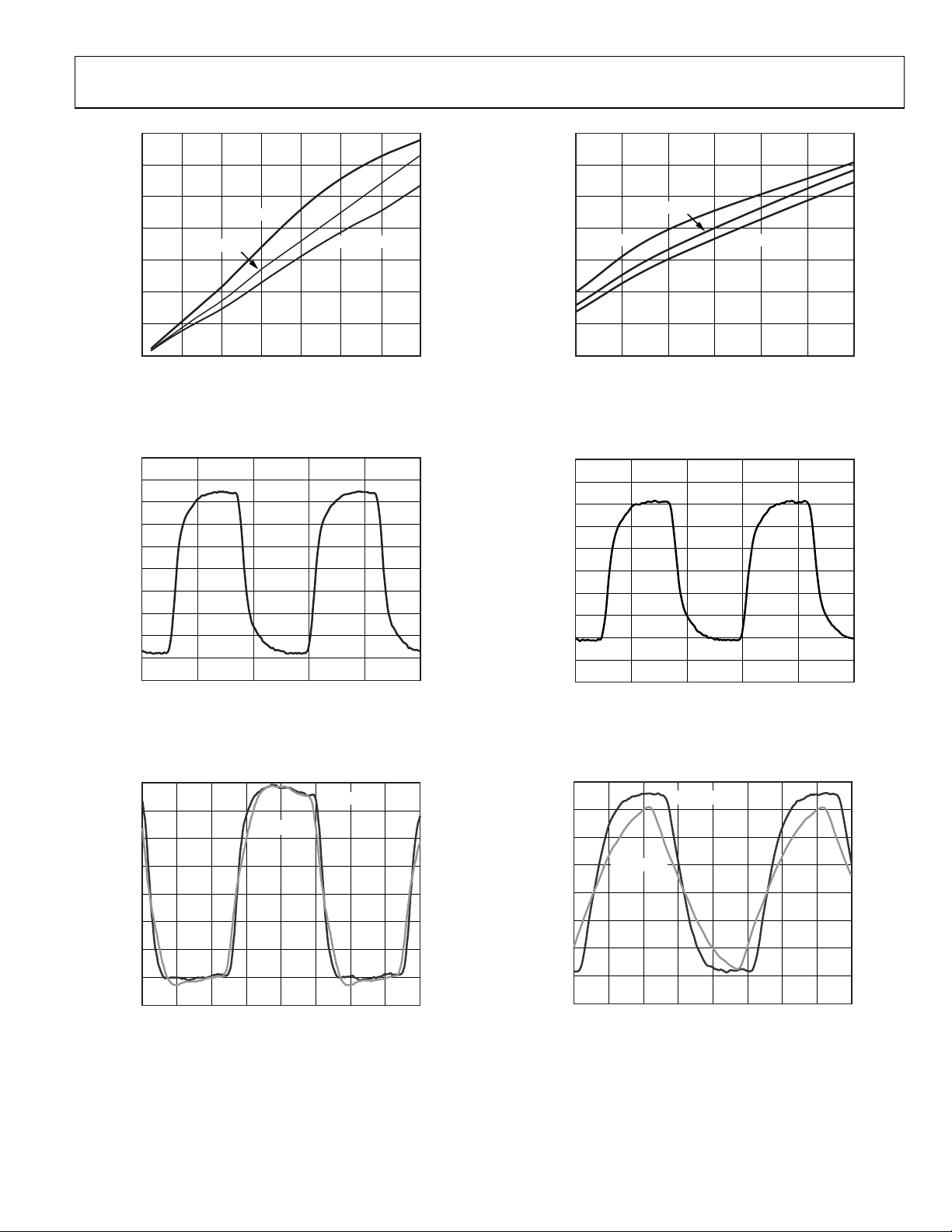

1.0

2.0

0.8

LVPECL

0.6

0.4

AMPLITUDE (V)

0.2

0

0 100 200 300 400 500 600 700

LVDS

FREQUENCY (MHz)

Figure 13. Amplitude vs. Toggle Rate,

LVPECL and LVDS

4.0

3.5

3.0

2.5

AMPLITUDE ( V )

2.0

10pF LO AD

20pF LOAD

5pF LO AD

1.5

20pF LOAD

AMPLITUDE (V)

1.0

10pF LOAD

0.5

0

8300-049

50 100 150 250200

FREQUENCY (MHz)

08300-062

Figure 16. Amplitude vs. Toggle Rate,

1.8 V CMOS

4.0

3.5

3.0

2.5

AMPLITUDE ( V )

2.0

5pF LOAD

10pF LOAD

1.5

1.0

0 100 200 300 400 500

FREQUENCY (M Hz)

Figure 14. Amplitude vs. Toggle Rate,

3.3 V CMOS (Strong Mode)

140

130

120

110

100

90

POWER (mW)

80

70

60

50

0 100 200 300 400 500

LVPECL

LVDS

FREQUENCY (M Hz)

Figure 15. Power Consumption vs. Frequency,

LVPECL and LVDS

(Single Channel)

1.5

1.0

0 102030405

8300-055

FREQUENCY (M Hz)

0

8300-063

Figure 17. Amplitude vs. Toggle Rate,

3.3 V CMOS (Weak Mode)

40

35

30

25

POWER (mW)

20

15

0 50 100 150 200

8300-064

10pF LOAD

20pF LOAD

FREQUENCY (MHz)

5pF LO AD

08300-061

Figure 18. Power Consumption vs. Frequency,

1.8 V CMOS

Rev. B | Page 20 of 104

AD9547

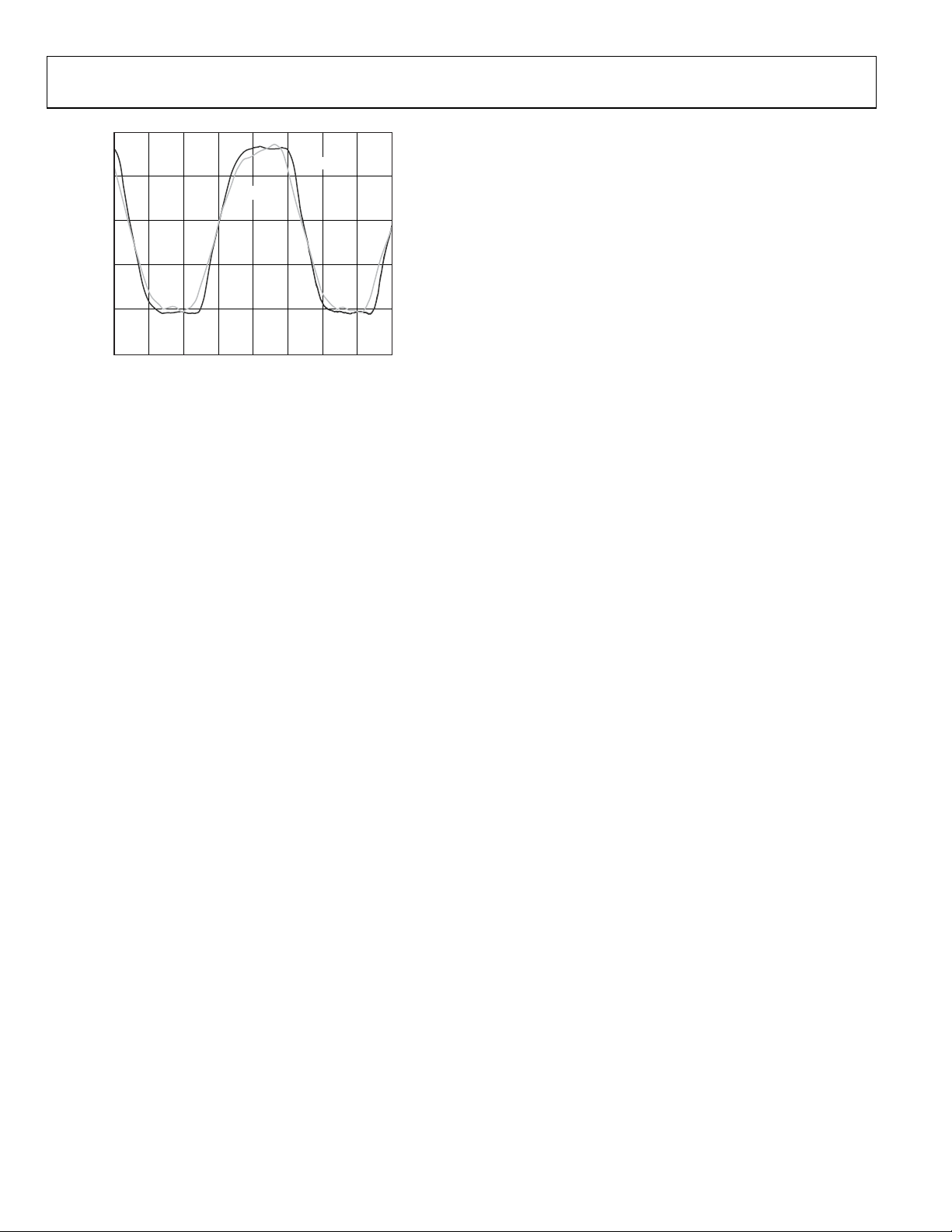

160

34

140

120

10pF LO AD

20pF LO AD

5pF LO AD

FREQUENCY ( M Hz )

100

80

POWER (mW)

60

40

20

0 50 100 150 200 250 300 350

Figure 19. Power Consumption vs. Frequency,

3.3 V CMOS (Strong Mode)

1.0

0.8

0.6

0.4

0.2

0

–0.2

–0.4

DIFFERENT IAL AMPLITUDE (V)

–0.6

–0.8

–1.0

012345

TIME (ns)

Figure 20. Output Waveform,

LVPECL (400 MHz)

32

30

28

20pF LO AD 5pF LOAD

26

POWER (mW)

24

22

20

10 15 20 25 30 35 40

08300-060

10pF LO AD

FREQUENCY ( M Hz )

08300-059

Figure 22. Power Consumption vs. Frequency,

3.3 V CMOS (Weak Mode)

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

DIFFERENT IAL AMPLITUDE (V)

–0.3

–0.4

–0.5

012345

08300-050

TIME (ns)

8300-048

Figure 23. Output Waveform,

LVDS (400 MHz)

3.5

3.0

2.5

2.0

1.5

1.0

AMPLITUDE (V)

0.5

0

–0.5

0246810121416

20pF LO AD

TIME (ns)

10pF LOAD

Figure 21. Output Waveform,

3.3 V CMOS (100 MHz, Strong Mode)

8300-057

Rev. B | Page 21 of 104

3.5

3.0

2.5

AMPLITUDE ( V )

2.0

1.5

1.0

0.5

0

–0.5

20 pF LOAD

0 1020304050607080

5pF LOAD

TIME (ns)

Figure 24. Output Waveform,

3.3 V CMOS (20 MHz, Weak Mode)

8300-046

AD9547

2.0

1.5

1.0

0.5

AMPLITUDE ( V)

0

–0.5

024

20pF LO AD

6 8 10 12 14 16

TIME (ns)

10pF LO AD

8300-065

Figure 25. Output Waveform,

1.8 V CMOS (100 MHz)

Rev. B | Page 22 of 104

AD9547

INPUT/OUTPUT TERMINATION RECOMMENDATIONS

0.1µF

0.1µF

AD9547

3.3V LVDS

OUTPUT

100Ω

IMPEDANCE

0.1µF

HIGH

INPUT

DOWNSTREAM

Figure 26. AC-Coupled LVDS or LVPECL Output Driver

AD9547

3.3V

LVPECL-

COMPATIBLE

OUTPUT

100Ω

DOWNSTREAM

Figure 27. DC-Coupled LVDS or LVPECL Output Driver

0.1µF

AD9547

SELF-BIASED

100Ω

REFERENCE

0.1µF

INPUT

(OPTIONAL)

Figure 28. Reference Input

DEVICE

DEVICE

08300-005

AD9547

(OPTIONAL)

SELF-BIASED

SYSCLKx

INPUT

08300-006

100Ω

0.1µF

08300-003

Figure 29. SYSCLKx Input

0.1µF

AD9547

(OPTIONAL)

SELF-BIASED

CLKINx

INPUT

08300-007

100Ω

0.1µF

08300-004

Figure 30. CLKINx Input

Rev. B | Page 23 of 104

AD9547

GETTING STARTED

POWER-ON RESET

The AD9547 monitors the voltage on the power supplies at powerup. When DVDD3 is greater than 2.35 V ± 0.1 V and DVDD

(Pin 1, Pin 6, Pin 8, Pin 53, Pin 59, and Pin 64) is greater than

1.4 V ± 0.05 V, the device generates a 75 ns reset pulse. The

power-up reset pulse is internal and independent of the RESET

pin. This internal power-up reset sequence eliminates the need for

the user to provide external power supply sequencing. Within 45 ns

after the leading edge of the internal reset pulse, the M0 to M7

multifunction pins function as high impedance digital inputs

and continue to do so until programmed otherwise.

INITIAL M0 TO M7 PIN PROGRAMMING

During a device reset (either via the power-up reset pulse or the

RESET pin), the multifunction pins (M0 to M7) function as

high impedance inputs, but upon removal of the reset condition,

level-sensitive latches capture the logic pattern present on the

multifunction pins. The AD9547 requires that the user supply

the desired logic state to the M0 to M7 pins by means of pull-up

and/or pull-down resistors (nominally 10 k to 30 k).

The initial state of the M0 to M7 pins following a reset is referred

to as FncInit, Bits[7:0]. Bits[7:0] of FncInit map directly to the

logic states of M[7:0], respectively. The three LSBs of FncInit

(FncInit, Bits[2:0]) determine whether the serial port interface

functions according to the SPI or the I

FncInit, Bits[2:0] = 000 selects the SPI interface. Any other value

selects the I

set to the value of FncInit, Bits[2:0].

The five MSBs of FncInit (FncInit, Bits[7:3]) determine the operation of the EEPROM loader. On the falling edge of RESET, if

FncInit, Bits[7:3] = 00000, then the EEPROM contents are not

transferred to the control registers and the device registers assume

their default values. However, if FncInit, Bits[7:3] ≠ 00000, then

the EEPROM controller transfers the contents of the EEPROM

to the control registers with CONDITION = FncInit, Bits[7:3]

(see the EEPROM section).

2

C port, with the three LSBs of the I2C bus address

2

C protocol. Specifically,

DEVICE REGISTER PROGRAMMING

The initial state of the M0 to M7 pins establishes the serial I/O

port protocol (SPI or I

tocol, and assuming that an EEPROM download is not used,

program the device according to the recommended sequence

that follows.

1. Program the system clock functionality.

The system clock parameters reside in the 0x100 register

address space. They include the following:

• System clock PLL controls

• System clock period

• System clock stability timer

It is essential to program the system clock period because many

of the AD9547 subsystems rely on this value. It is highly recom-

2

C). Using the appropriate serial port pro-

Rev. B | Page 24 of 104

mended that the system clock stability timer be programmed, as

well. This is especially important when using the system clock PLL

but also applies if using an external system clock source, especially

if the external source is not expected to be completely stable when

power is applied to the AD9547.

2. Initialize the system clock.

After the system clock functionality is programmed, issue an I/O

update using Register 0x0005, Bit 0 to invoke the system clock

settings.

3. Calibrate the system clock (only if using SYSCLK PLL).

Set the calibrate system clock bit in the cal/sync register

(Address 0x0A02, Bit 0) and issue an I/O update. Then clear the

calibrate system clock bit and issue another I/O update. This

action allows time for the calibration to proceed while programming the remaining device registers.

4. Program the multifunction pins (optional).

This step is required only if the user intends to use any of the

multifunction pins for status or control. The multifunction pin

parameters reside in the 0x0200 register address space. The

default configuration of the multifunction pins is as undesignated

high impedance input pins.

5. Program the IRQ functionality (optional).

This step is required only if the user intends to use the IRQ feature.

IRQ control resides in the 0x0200 register address space. It includes

the following:

• IRQ pin mode control

• IRQ mask

The IRQ mask default values prevent interrupts from being

generated. The IRQ pin mode default is open-drain NMOS.

6. Program the watchdog timer (optional).

This step is required only if the user intends to use the watchdog

timer. Watchdog timer control resides in the 0x0200 register

address space. The watchdog timer is disabled by default.

7. Program the DAC full-scale current (optional).

This step is required only if the user intends to use a full-scale

current setting other than the default value. DAC full-scale

current control resides in the 0x0200 register address space.

8. Program the digital phase-locked loop (DPLL).

The DPLL parameters reside in the 0x0300 register address

space. They include the following:

• Free-run frequency (DDS frequency tuning word)

• DDS phase offset

• DPLL pull-in range limits

• DPLL closed-loop phase offset

• Phase slew control (for hitless reference switching)

• Tuning word history control (for holdover operation)

AD9547

9. Program the clock distribution outputs.

The clock distribution parameters reside in the 0x0400 register

address space. They include the following:

• Output power-down control

• Output enable (disabled by default)

• Output synchronization

• Output mode control

• Output divider functionality

• Program the reference inputs.

10. The reference input parameters reside in the 0x0500

register address space. They include the following:

• Reference power-down

• Reference logic family

• Reference profile assignment control

• Phase build-out control

11. Program the reference profiles.

The reference profile parameters reside in the 0x0600 and

0x0700 register address spaces. They include the following:

• Reference priority

• Reference period

• Reference period tolerance

• Reference validation timer

• Reference redetect timer

• Digital loop filter coefficients

• Reference prescaler (R divider)

• Feedback dividers (S, U, and V)

• Phase and frequency lock detector controls

12. Generate reference acquisition.

After the registers are programmed, issue an I/O update using

Register 0x0005, Bit 0 to invoke all of the register settings that have

been programmed up to this point.

If the settings are programmed for manual profile assignment,

the DPLL locks to the first available reference that has the highest

priority. If the settings are programmed for automatic profile

assignment, then write to the reference profile selection register

(Address 0x0A0D) to select the state machines that require starting.

Next, issue an I/O update (Address 0x0005, Bit 0) to start the

selected state machines. Upon completion of the reference

detection sequence, the DPLL locks to the first available

reference with the highest priority.

13. Generate the output clock.

If the registers are programmed for automatic clock distribution

synchronization via DPLL phase or frequency lock, the synthesized

output signal appears at the clock distribution outputs (assuming

that the output is enabled and the DDS output signal has been

routed to the CLKINx input pins). Otherwise, set and then clear

the sync distribution bit (Address 0x0A02, Bit 1) or use a multifunction pin input (if programmed accordingly) to generate

a clock distribution sync pulse, which causes the synthesized

output signal to appear at the clock distribution outputs.

Rev. B | Page 25 of 104

AD9547

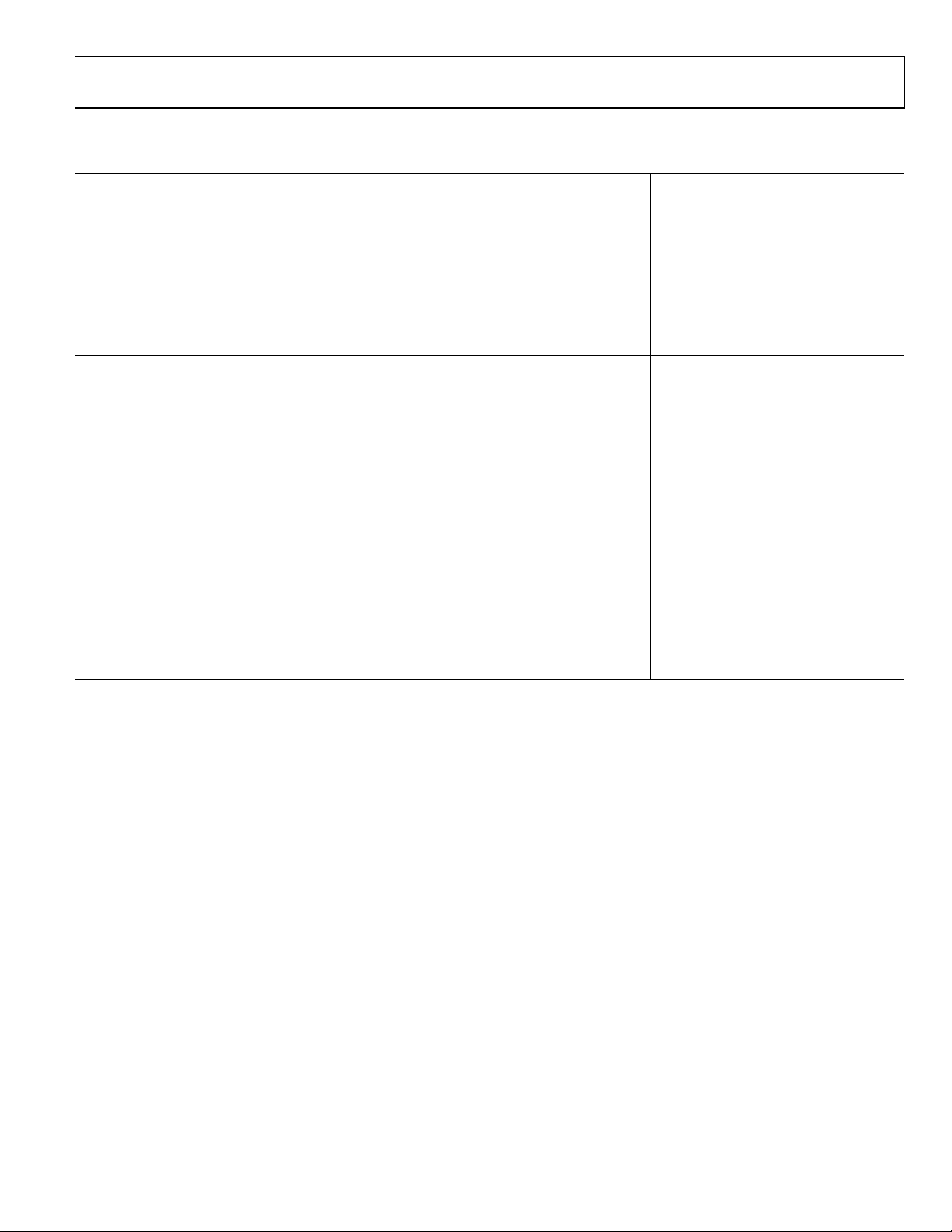

THEORY OF OPERATION

AD9547

OUT_RSET

OUT0P

OUT0N

OUT1P

OUT1N

CLKINP

CLKINN

EXTERNAL

ANALOG

FILTER

REFA

REFAA

REFB

REFBB

M0 TO M7

IRQ

DIFFERENTIAL

OR

SINGLE-ENDED

2 OR 4

INPUT

REF

MONITOR

IRQ AND

STATUS

LOGIC

DIGITAL PLL CORE

÷R

TDC/PFD

PHASE

CONTROLLER

PROG.

DIGITAL

LOOP

FILTER

CONTROL

LOGIC

÷S

TW CLAMP

AND

HISTORY

HOLDOVER

LOGIC

DDS/DAC

LOW NOISE

CLOCK

MULTIPLIER

SYSCLK PORT

POST

DIV

POST

DIV

CLOCK

DISTRIBUTION

AMP

DIGITAL

INTERFACE

Figure 31. Detailed Block Diagram

OVERVIEW

The AD9547 provides clocking outputs that are directly related

in phase and frequency to the selected (active) reference but with

jitter characteristics primarily governed by the system clock. The

AD9547 supports up to four reference inputs and a wide range of

reference frequencies. The core of this product is a digital phaselocked loop (DPLL). The DPLL has a programmable digital loop

filter that greatly reduces jitter transferred from the active

reference to the output. The AD9547 supports both manual and

automatic holdover modes. While in holdover mode, the AD9547

continues to provide an output as long as the DAC sample clock

is present. The holdover output frequency is a time average of

the output frequency history just prior to the transition to the

holdover condition.

The device offers manual and automatic reference switchover

capability if the active reference is degraded or fails completely.

A direct digital synthesizer (DDS) and integrated DAC constitute

a digitally controlled oscillator (DCO). The DCO output is

a sinusoidal signal (450 MHz maximum) at a frequency that is

determined by the active reference frequency and the programmed

values of the reference prescaler (R) and feedback divider (S).

Although not explicitly shown in Figure 31, the S divider has

both an integer and fractional component, which is similar to

a fractional-N synthesizer.

SYSCLKN SYSCLKP

The SYSCLKx input provides the sample clock for the DAC, which

is either a directly applied high frequency source or a low frequency

source coupled with the integrated PLL-based frequency multiplier.

The low frequency option also allows for the use of a crystal

resonator connected directly across the SYSCLKx inputs.

The DAC output routes directly off chip where an external filter

removes the sampling artifacts before returning the signal on chip

at the CLKINx inputs. Once on chip, an integrated comparator

converts the filtered sinusoidal signal to a clock signal (square

wave) with very fast rise and fall times.

The clock distribution section provides two output drivers. Each

driver is programmable either as a single differential LVPECL/

LVDS output or as a dual single-ended CMOS output. Furthermore, a dedicated 30-bit programmable divider precedes each

driver. The clock distribution section operates at up to 725 MHz.

This enables use of a band-pass reconstruction filter (for example,

a SAW filter) to extract a Nyquist image from the DAC output

spectrum, thereby allowing output frequencies that exceed the

typical 450 MHz limit at the DAC output.

08300-009

Rev. B | Page 26 of 104

AD9547

REFERENCE CLOCK INPUTS

Two pairs of pins provide access to the reference clock receivers.

Each pair is configurable either as a single differential receiver

or as two independent single-ended receivers. To accommodate

input signals with slow rising and falling edges, both the differential

and single-ended input receivers employ hysteresis. Hysteresis also

ensures that a disconnected or floating input does not cause the

receiver to oscillate spontaneously.

When configured for differential operation, the input receivers

accommodate either ac- or dc-coupled input signals. The receiver

is internally dc biased to handle ac-coupled operation.

When configured for single-ended operation, the input receivers

exhibit a pull-down load of 45 kΩ (typical). Three user-programmable threshold voltage ranges are available for each single-ended

receiver.

REFERENCE MONITORS

The reference monitors depend on a known and accurate system

clock period. Therefore, the functioning of the reference monitors

is not reliable until the system clock is stable. To avoid an incorrect

valid indication, the reference monitors indicate fault status until

the system clock stability timer expires (see the System Clock

Period section).

Reference Period Monitor

Each reference input has a dedicated monitor that repeatedly

measures the reference period. The AD9547 uses the reference

period measurements to determine the validity of the reference

based on a set of user provided parameters in the profile register

area of the register map (see the Profile Registers (Register

0X0600 to Register 0X07FF) section). The AD9547 also uses the

reference period monitor to assign a particular reference to a

profile when the user programs the device for automatic profile

assignment.

The monitor works by comparing the measured period of a particular reference input against the parameters stored in the profile

register assigned to that same reference input. The parameters

include the reference period, an inner tolerance, and an outer

tolerance. A 40-bit number defines the reference period in units

of femtoseconds (fs). The 40-bit range allows for a reference period

entry of up to 1.1 ms (909 Hz). A 20-bit number defines the inner

and outer tolerances. The value stored in the register is the reciprocal of the tolerance specification. For example, a tolerance

specification of 50 ppm yields a register value of 1/(50 ppm) =

1/0.000050 = 20,000 (0x04E20).

The use of two tolerance values provides hysteresis for the monitor

decision logic. The inner tolerance applies to a previously faulted

reference and specifies the largest period tolerance that a previously

faulted reference can exhibit before it qualifies as nonfaulted.

The outer tolerance applies to an already nonfaulted reference and

specifies the largest period tolerance that a nonfaulted reference

can exhibit before being faulted.

To produce decision hysteresis, the inner tolerance must be less

than the outer tolerance. That is, a faulted reference must meet

tighter requirements to become nonfaulted than a nonfaulted

reference must meet to become faulted.

Reference Validation Timer

Each reference input has a dedicated validation timer. The

validation timer establishes the amount of time that a previously

faulted reference must remain fault free before the AD9547

declares it to be nonfaulted. The timeout period of the validation

timer is programmable via a 16-bit register (see the validation

register contained within each of the eight profile registers in

the register map, Address 0x0600 to Address 0x07FF). The

16-bit number stored in the validation register represents units

of milliseconds, which yields a maximum timeout period of

65,535 ms.

Note that a validation period of zero must be programmed to

disable the validation timer. With the validation timer disabled,

the user must validate a reference manually via the force validation timeout register (Address 0x0A0E).

Reference Redetect Timer

Each reference input has a dedicated redetect timer. The redetect

timer is useful only when the device is programmed for automatic

profile selection. The redetect timer establishes the amount of

time that a reference must remain faulted before the AD9547

attempts to reassign it to a new profile. The timeout period of

the redetect timer is programmable via a 16-bit register (see the

redetect timer register contained within each of the eight profile

registers in the register map, Address 0x0600 to Address 0x07FF).

The 16-bit number stored in the redetect timer register represents

units of milliseconds, which yields a maximum timeout period

of 65,535 ms.

Note that a timeout period of 0 must be programmed to disable the

redetect timer.

Rev. B | Page 27 of 104

AD9547

REGISTER CONTROL BI TS

FORCE VALI DATION

TIMEOUT

REF MONITOR

BYPASS

REF MONITOR

OVERRIDE

REFERENCE

MONITOR

REF FAULT

REFERENCE VALIDATION LOGIC

(4 COPIES, 1 PER REFERENCE INPUT)

1

FAULTED

0

Figure 32. Reference Validation Override

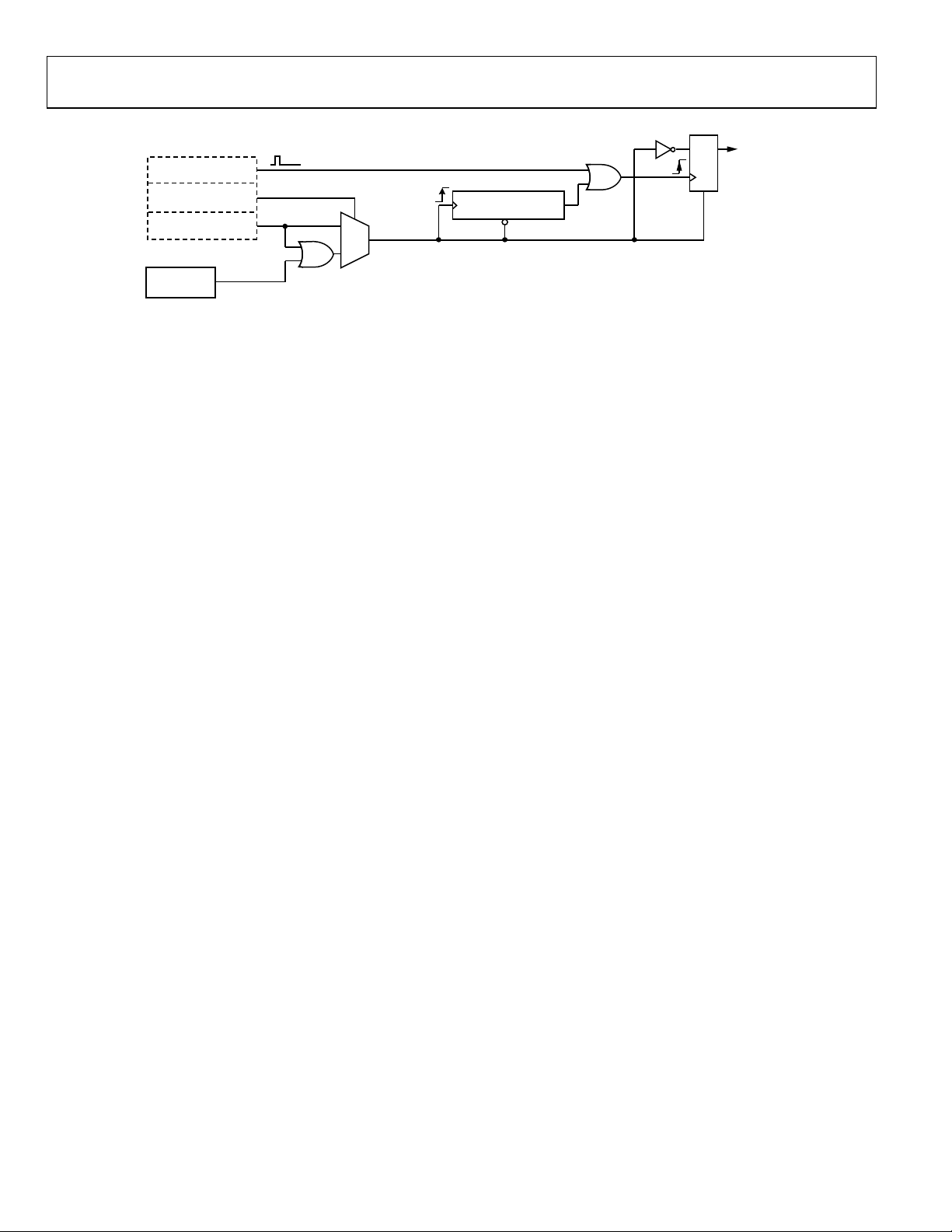

Reference Validation Override Control

Register 0x0A0E to Register 0x0A10 provide the user with the

ability to override the reference validation logic, enabling a

certain level of troubleshooting capability. Each of the four

input references has a dedicated block of validation logic, as

shown in Figure 32. The state of the valid signal at the output

defines a particular reference as valid (1) or not valid (0), which

includes the validation period (if activated) as prescribed by the

validation timer. The override controls are the three control bits

on the left side of the diagram.

The main feature to note is that when faulted = 1, the output latch

is reset, which forces valid = 0 (indicating an invalid reference),

regardless of the state of any other signal. Under the default condition (that is, all three control bits are set to 0), the reference

monitor is the primary source of the validation process. This is

because, under the default condition, the ref fault signal from the

reference monitor is identical to the faulted signal.

The function of the faulted signal is fourfold.

• When faulted = 1, valid = 0, regardless of the state of any

other control signal. Therefore, faulted = 1 indicates an

invalid reference.

• When the faulted signal transitions from 0 to 1 (that is, from

not faulted to faulted), the validation timer is momentarily

reset, which means that, when it is enabled, it must exhaust its

full counting sequence before it expires.

• When faulted = 0 (that is, the reference is not faulted), the

validation timer is allowed to perform its timing sequence.

When faulted = 1 (that is, the reference is faulted), the

validation timer is reset and halted.

• The faulted signal passes through an inverter, which converts

it to a not faulted signal that appears at the input of the valid

latch. This allows the valid latch to capture the state of the

not faulted signal when the validation timer expires.

The reference monitor bypass control bit (Address 0x0A10) enables

bypassing of the reference fault signal generated by the reference

monitor. When the reference monitor bypass bit = 1, the state of the

faulted signal is dictated by the reference monitor override control

bit. This is useful when the user relies on an external reference

monitor rather than the internal monitor resident in the device.

DQ

VALID

VALIDATION TIMER

R

EN

TIMEOUT

R

08300-010

The user programs the reference monitor override bit based on

the status of the external monitor. On the other hand, when the

reference monitor bypass bit = 0, the reference monitor override

control bit (Address 0x0A0F) allows the user to manually test

the operation of both the valid latch and the validation timer.

In this case, the user relies on the signal generated by the internal

reference monitor (reference fault) but uses the reference monitor

override bit to emulate a faulted reference. That is, when the

reference monitor override bit = 1, faulted = 1, but when the

reference monitor override bit = 0, faulted = reference fault.

In addition, the user can emulate a timeout of the validation timer

via the force validation timeout control register at Address 0x0A0E.

Writing a Logic 1 to this autoclearing bit triggers the valid latch,

which is identically equivalent to a timeout of the validation timer.

REFERENCE PROFILES

The AD9547 has eight independent profile registers. A profile

register contains 50 bytes that establish a particular set of device

parameters. Each of the four input references can be assigned to

any one of the eight profiles (that is, more than one reference can

be assigned to the same profile). The profiles allow the user to

prescribe the specific device functionality that should take effect

when one of the input references assigned to a profile becomes the

active reference. Each profile register has the same format and

stores the following device parameters:

• Reference priority

• Reference period value (in femtoseconds (fs))

• Inner tolerance value (1/tolerance)

• Outer tolerance value (1/tolerance)

• Validation timer value (milliseconds (ms))

• Redetect timer value (milliseconds (ms))

• Digital loop filter coefficients

• Reference prescaler setting (R divider)

• Feedback divider settings (S, U, and V)

• DPLL phase lock detector threshold level

• DPLL phase lock detector fill rate

• DPLL phase lock detector drain rate

• DPLL frequency lock detector threshold level

• DPLL frequency lock detector fill rate

• DPLL frequency lock detector drain rate

Rev. B | Page 28 of 104

AD9547

Reference-to-Profile Assignment Control

The user can manually assign a reference to a profile or let the

device make the assignment automatically. The manual reference

profile selection register (Address 0x0503 and Address 0x0504)

is used to program whether a reference-to-profile assignment is

manual or automatic. The manual reference profile selection register is a 2-byte register partitioned into four half bytes (or nibbles).

The four nibbles form a one-to-one correspondence with the four

reference inputs: one nibble for REF A, the next for REF AA, and

so on. For a reference configured as a differential input, however,