Analog Devices AD9244 b Datasheet

C

FEATURES

14-bit, 40/65 MSPS ADC

Low power:

550 mW at 65 MSPS

300 mW at 40 MSPS

On-chip reference and sample-and-hold

750 MHz analog input bandwidth

SNR > 73 dBc to Nyquist @ 65 MSPS

SFDR > 86 dBc to Nyquist @ 65 MSPS

Differential nonlinearity error = ±0.7 LSB

Guaranteed no missing codes over full temperature range

1 V to 2 V p-p differential full-scale analog input range

Single 5 V analog supply, 3.3 V/5 V driver supply

Out-of-range indicator

Straight binary or twos complement output data

Clock duty cycle stabilizer

Output-enable function

48-lead LQFP package

APPLICATIONS

Communication subsystems (Microcell, Picocell)

Medical and high-end imaging equipment

Test and measurement equipment

14-Bit, 40/65 MSPS A/D Converter

AD9244

FUNCTIONAL BLOCK DIAGRAM

VRCML

REFT REFB

TEN STAGE

PIPELINE ADC

REFERENCE

Figure 1.

REF

GND

14

OUTPUT

REGISTER

DFS

OTR

14

D13–D0

OEB

02404-001

AVDD DRVDD

AD9244

VIN+

VIN–

LK+

CLK–

DCS

SHA

TIMING

AGND DGNDVREF SENSE

Fabricated on an advanced CMOS process, the AD9244 is

available in a 48-lead low profile quad flatpack package (LQFP)

and is specified for operation over the industrial temperature

range (–40°C to +85°C).

GENERAL DESCRIPTION

The AD9244 is a monolithic, single 5 V supply, 14-bit,

40 MSPS/65 MSPS ADC with an on-chip, high performance

sample-and-hold amplifier and voltage reference.

The AD9244 uses a multistage differential pipelined architecture with output error correction logic to provide 14-bit

accuracy at 40 MSPS/65 MSPS data rates, and guarantees no

missing codes over the full operating temperature range.

The AD9244 has an on-board, programmable voltage reference.

An external reference can also be used to suit the dc accuracy

and temperature drift requirements of the application.

A differential or single-ended clock input controls all internal

conversion cycles. The digital output data can be presented in

straight binary or in twos complement format. An out-of-range

(OTR) signal indicates an overflow condition that can be used

with the most significant bit to determine low or high overflow.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

PRODUCT HIGHLIGHTS

1. Low Power—The AD9244, at 550 mW, consumes a

fraction of the power of currently available ADCs in

existing high speed solutions.

2. IF Sampling—The AD9244 delivers outstanding

performance at input frequencies beyond the first

Nyquist zone. Sampling at 65 MSPS with an input

frequency of 100 MHz, the AD9244 delivers 71 dB

SNR and 86 dB SFDR.

3. Pin Compatibility—The AD9244 offers a seamless

migration from the 12-bit, 65 MSPS AD9226.

4. On-Board Sample-and-Hold (SHA)—The versatile

SHA input can be configured for either single-ended

or differential inputs.

5. Out-of-Range (OTR) Indicator—The OTR output bit

indicates when the input signal is beyond the

AD9244’s input range.

6. Single Supply—The AD9244 uses a single 5 V power

supply, simplifying system power supply design. It also

features a separate digital output driver supply to

accommodate 3.3 V and 5 V logic families.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

www.analog.com

AD9244

TABLE OF CONTENTS

Specifications..................................................................................... 3

Theory of Operation ...................................................................... 17

DC Specifications ......................................................................... 3

AC Specifications.......................................................................... 4

Digital Specifications ................................................................... 5

Switching Specifications.............................................................. 6

Absolute Maximum Ratings............................................................ 7

Explanation of Test Levels........................................................... 7

ESD Caution.................................................................................. 7

Pin Configuration and Function Descriptions............................. 8

Terminology ...................................................................................... 9

Typical Application Circuits.......................................................... 11

Typical Performance Characteristics ........................................... 12

REVISION HISTORY

2/05 – Rev. A to Rev. B

Updated Format..................................................................Universal

Changes to Table 1............................................................................ 3

Changes to Table 2............................................................................ 4

Reformatted Table 5 ......................................................................... 7

Changes to Table 6............................................................................ 8

Changes to Figure 12...................................................................... 12

Changed Captions on Figure 18 and Figure 21.......................... 13

Changes to Figure 35, Figure 38, Figure 39 ................................. 16

Changes to Table 9.......................................................................... 21

Changes to Table 13........................................................................ 26

Changes to Ordering Guide.......................................................... 33

Analog Input and Reference Overview ................................... 17

Analog Input Operation............................................................ 18

Differentially Driving the Analog Inputs................................ 19

Reference Operation .................................................................. 20

Digital Inputs and Outputs ....................................................... 21

Evaluation Board............................................................................ 25

Analog Input Configuration..................................................... 25

Reference Configuration ........................................................... 25

Clock Configuration .................................................................. 25

Outline Dimensions....................................................................... 33

Ordering Guide .......................................................................... 33

6/03 – Rev. 0 to Rev. A

Changes to AC SPECIFICATIONS................................................ 3

Updated ORDERING GUIDE........................................................ 6

Updated OUTLINE DIMENSIONS ............................................ 33

6/02 – Revision 0: Initial Version

Rev. B | Page 2 of 36

AD9244

SPECIFICATIONS

DC SPECIFICATIONS

AVDD = 5 V, DRVDD = 3 V, f

differential analog inputs, unless otherwise noted.

Table 1.

Test AD9244BST-65 AD9244BST-40

Parameter Temp Level Min Typ Max Min Typ Max Unit

RESOLUTION Full VI 14 14 Bits

DC ACCURACY

No Missing Codes Full VI Guaranteed Guaranteed Bits

Offset Error Full VI ±0.3 ±1.4 ±0.3 ±1.4 % FSR

Gain Error1 Full VI ±0.6 ±2.0 ±0.6 ±2.0 % FSR

Differential Nonlinearity (DNL)2 Full VI ±1.0 ±1.0 LSB

25°C V ±0.7 ±0.6 LSB

Integral Nonlinearity (INL)2 Full V ±1.4 ±1.3 LSB

Full VI

TEMPERATURE DRIFT

Offset Error Full V ±2.0 ±2.0 ppm/°C

Gain Error (EXT VREF)1

Gain Error (INT VREF)3 Full V ±25 ±25 ppm/°C

INTERNAL VOLTAGE REFERENCE

Output Voltage Error (2 VREF) Full VI ±29 ±29 mV

Load Regulation @ 1 mA Full V 0.5 0.5 mV

Output Voltage Error (1 VREF) Full IV ±15 ±15 mV

Load Regulation @ 0.5 mA Full V 0.25 0.25 mV

Input Resistance Full V 5 5

INPUT REFERRED NOISE

VREF = 2 V 25°C V 0.8 0.8 LSB rms

VREF = 1 V 25°C V 1.5 1.5 LSB rms

ANALOG INPUT

Input Voltage Range (Differential)

VREF = 2 V Full V 2 2 V p-p

VREF = 1 V Full V 1 1 V p-p

Common-Mode Voltage Full V 0.5 4 0.5 4 V

Input Capacitance4 25°C V 10 10 pF

Input Bias Current5 25°C V 500 500 µA

Analog Bandwidth (Full Power) 25°C V 750 750 MHz

POWER SUPPLIES

Supply Voltages

AVDD Full IV 4.75 5 5.25 4.75 5 5.25 V

DRVDD Full IV 2.7 5.25 2.7 5.25 V

Supply Current

IAVDD Full V 109 64 mA

IDRVDD Full V 12 8 mA

PSRR Full V ±0.05 ±0.05 % FSR

POWER CONSUMPTION

DC Input6 Full V 550 300 mW

Sine Wave Input Full VI 590 640 345 370 mW

1

Gain error is based on the ADC only (with a fixed 2.0 V external reference).

2

Measured at maximum clock rate, fIN = 2.4 MHz, full-scale sine wave, with approximately 5 pF loading on each output bit.

3

Includes internal voltage reference error.

4

Input capacitance refers to the effective capacitance between one differential input pin and AGND. Refer to for the equivalent analog input structure. Figure 7

5

Input bias current is due to the input looking like a resistor that is dependent on the clock rate.

6

Measured with dc input at maximum clock rate.

= 65 MSPS (–65) or 40 MSPS (–40), differential clock inputs, VREF = 2 V, external reference,

SAMPLE

−4

+4

−4

+4 LSB

Full V ±2.3 ±2.3 ppm/°C

kΩ

Rev. B | Page 3 of 36

AD9244

AC SPECIFICATIONS

AVDD = 5 V, DRVDD = 3 V, f

= –0.5 dBFS, differential analog inputs, unless otherwise noted.

A

IN

Table 2.

Test AD9244BST-65 AD9244BST-40

Parameter Temp Level Min Typ Max Min Typ Max Unit

SNR1

fIN = 2.4 MHz Full VI 72.4 73.4 dBc

25°C I 74.8 75.3 dBc

fIN = 15.5 MHz (–1 dBFS) Full IV 72.0 dBc

25°C V 73.7 dBc

fIN = 20 MHz Full VI 72.1 dBc

25°C I 74.7 dBc

fIN = 32.5 MHz Full IV 70.8 dBc

25°C I 73.0 dBc

fIN = 70 MHz Full IV 69.9 dBc

25°C V 72.2 dBc

fIN = 100 MHz 25°C V 71.2 72.8 dBc

fIN = 200 MHz 25°C V 67.2 68.3 dBc

SINAD1

fIN = 2.4 MHz Full VI 72.2 73.2 dBc

25°C I 74.7 75.1 dBc

fIN = 20 MHz Full VI 72 dBc

25°C I 74.4 dBc

fIN = 32.5 MHz Full IV 70.6 dBc

25°C I 72.6 dBc

fIN = 70 MHz Full IV 69.7 dBc

25°C V 71.9 dBc

fIN = 100 MHz 25°C V 71 72.4 dBc

fIN = 200 MHz 25°C V 59.8 56.3 dBc

ENOB

fIN = 2.4 MHz Full VI 11.7 11.9 Bits

25°C I 12.1 12.2 Bits

fIN = 20 MHz Full VI 11.7 Bits

25°C I 12.1 Bits

fIN = 32.5 MHz Full IV 11.4 Bits

25°C I 11.8 Bits

fIN = 70 MHz Full IV 11.3 Bits

25°C V 11.7 Bits

fIN = 100 MHz 25°C V 11.5 11.7 Bits

fIN = 200 MHz 25°C V 9.6 9.1 Bits

THD1

fIN = 2.4 MHz Full VI

25°C I

fIN = 20 MHz Full VI

25°C I

fIN = 32.5 MHz Full IV

25°C I

fIN = 70 MHz Full IV

25°C V

fIN = 100 MHz 25°C V

fIN = 200 MHz 25°C V

= 65 MSPS (–65) or 40 MSPS (–40), differential clock inputs, VREF = 2 V, external reference,

SAMPLE

−89.7

−89.4

dBc

dBc

−83.2

−56.6

−90.0

−84.6

−84.1

−83.0

−60.7

−78.4

−79.2

dBc

−78.7

dBc

−80.7

dBc

−80.4

dBc

dBc

dBc

dBc

dBc

Rev. B | Page 4 of 36

AD9244

Test AD9244BST-65 AD9244BST-40

Parameter Temp Level Min Typ Max Min Typ Max Unit

WORST HARMONIC (2nd or 3rd)1

fIN = 2.4 MHz 25°C V

−94.5

fIN = 20 MHz 25°C V

fIN = 32.5 MHz 25°C V

fIN = 70 MHz 25°C V

fIN = 100 MHz 25°C V

fIN = 200 MHz 25°C V

−86.5

−86.1

−86.2

−60.7

SFDR1

fIN = 2.4 MHz Full VI 78.6 82.5 dBc

25°C I 94.5 93.7 dBc

fIN = 15.5 MHz (–1 dBFS) Full IV 83 dBc

25°C V 90 dBc

fIN = 20 MHz Full IV 81.4 dBc

25°C I 91.8 dBc

fIN = 32.5 MHz Full IV 80.0 dBc

25°C I 86.4 dBc

fIN = 70 MHz Full IV 79.5 dBc

25°C V 86.1 dBc

fIN = 100 MHz 25°C V 86.2 84.5 dBc

fIN = 200 MHz 25°C V 60.7 56.6 dBc

1

AC specifications may be reported in dBc (degrades as signal levels are lowered) or in dBFS (always related back to converter full scale).

−93.7

−92.8

dBc

dBc

dBc

dBc

−84.5

−56.6

dBc

dBc

DIGITAL SPECIFICATIONS

AVDD = 5 V, DRVDD = 3 V, VREF = 2 V, external reference, unless otherwise noted.

Table 3.

Test AD9244BST-65 AD9244BST-40

Parameter Temp Level Min Typ Max Min Typ Max Unit

DIGITAL INPUTS

Logic 1 Voltage (OEB, DRVDD = 3 V) Full IV 2 2 V

Logic 1 Voltage (OEB, DRVDD = 5 V) Full IV 3.5 3.5 V

Logic 0 Voltage (OEB) Full IV 0.8 0.8 V

Logic 1 Voltage (DFS, DCS) Full IV 3.5 3.5 V

Logic 0 Voltage (DFS, DCS) Full IV 0.8 0.8 V

Input Current Full IV 10 10 µA

Input Capacitance Full V 5 5 pF

CLOCK INPUT PARAMETERS

Differential Input Voltage Full IV 0.4 0.4 V p-p

CLK–Voltage1 Full IV 0.25 0.25 V

Internal Clock Common-Mode Full V 1.6 1.6 V

Single-Ended Input Voltage

Logic 1 Voltage Full IV 2 2 V

Logic 0 Voltage Full IV 0.8 0.8 V

Input Capacitance Full V 5 5 pF

Input Resistance Full V 100 100 kΩ

DIGITAL OUTPUTS (DRVDD = 5 V)

Logic 1 Voltage (IOH = 50 µA) Full IV 4.5 4.5 V

Logic 0 Voltage (IOL = 50 µA) Full IV 0.1 0.1 V

Logic 1 Voltage (IOH = 0.5 mA) Full IV 2.4 2.4 V

Logic 0 Voltage (IOL = 1.6 mA) Full IV 0.4 0.4 V

Rev. B | Page 5 of 36

AD9244

Test AD9244BST-65 AD9244BST-40

Parameter Temp Level Min Typ Max Min Typ Max Unit

DIGITAL OUTPUTS (DRVDD = 3 V)2

Logic 1 Voltage (IOH = 50 µA) Full IV 2.95 2.95 V

Logic 0 Voltage (IOL = 50 µA) Full IV 0.05 0.05 V

Logic 1 Voltage (IOH = 0.5 mA) Full IV 2.8 2.8 V

Logic 0 Voltage (IOL = 1.6 mA) Full IV 0.4 0.4 V

1

See Clock section of Theory of Operation for more details.

2

Output voltage levels measured with 5 pF load on each output.

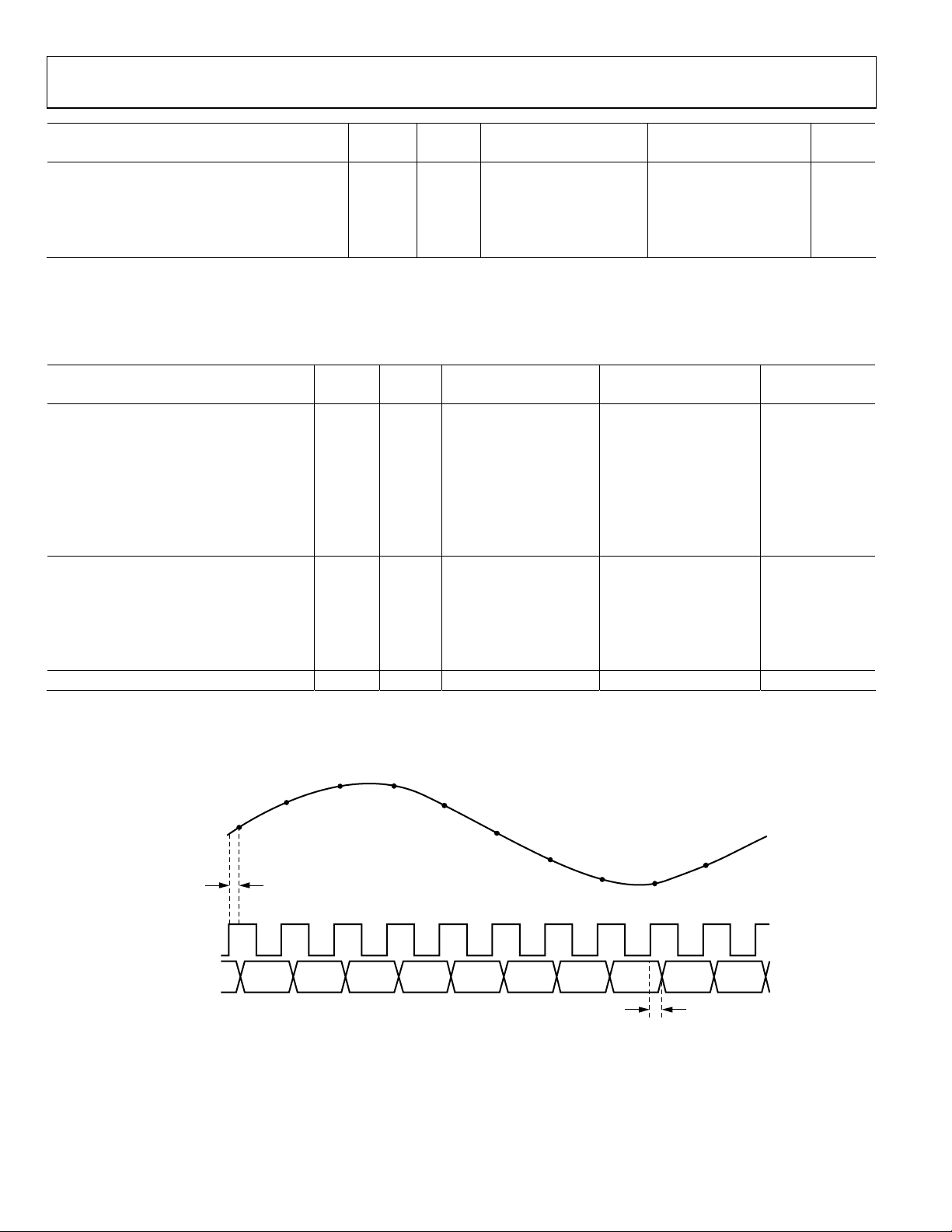

SWITCHING SPECIFICATIONS

AVDD = 5 V, DRVDD = 3 V, unless otherwise noted.

Table 4.

Test AD9244BST-65 AD9244BST-40

Parameter Temp Level Min Typ Max Min Typ Max Unit

CLOCK INPUT PARAMETERS

Maximum Conversion Rate Full VI 65 40 MHz

Minimum Conversion Rate Full V 500 500 kHz

Clock Period1 Full V 15.4 25 ns

Clock Pulse Width High2 Full V 4 4 ns

Clock Pulse Width Low2 Full V 4 4 ns

Clock Pulse Width High3 Full V 6.9 11.3 ns

Clock Pulse Width Low3 Full V 6.9 11.3 ns

DATA OUTPUT PARAMETERS

Output Delay (tPD)4 Full V 3.5 7 3.5 7 ns

Pipeline Delay (Latency) Full V 8 8 Clock cycles

Aperture Delay (tA) Full V 1.5 1.5 ns

Aperture Uncertainty (Jitter) Full V 0.3 0.3 ps rms

Output Enable Delay Full V 15 15 ns

OUT-OF-RANGE RECOVERY TIME Full V 2 1 Clock cycles

1

The clock period may be extended to 2 µs with no degradation in specified performance at 25°C.

2

With duty cycle stabilizer enabled.

3

With duty cycle stabilizer disabled.

4

Measured from clock 50% transition to data 50% transition with 5 pF load on each output.

ANALOG INPUT

CLOCK

DATA OUT

N + 2

N + 1

N

t

A

N – 9 N – 8 N – 7 N – 6 N – 5 N– 4 N – 3 N– 2 N– 1 N N + 1

N + 3

N + 4

N + 5

N + 6

N + 7

N + 8

N + 9

t

PD

Figure 2. Input Timing

Rev. B | Page 6 of 36

02404-002

AD9244

ABSOLUTE MAXIMUM RATINGS

Table 5.

With

Paremeter

ELECTRICAL

AVDD AGND –0.3 V to +6.5 V

DRVDD

AGND DGND –0.3 V to +0.3 V

AVDD DRVDD –6.5 V to +6.5 V

REFGND AGND –0.3 V to +0.3 V

CLK+, CLK–, DCS AGND –0.3 V to AVDD + 0.3 V

DFS AGND –0.3 V to AVDD + 0.3 V

VIN+, VIN– AGND –0.3 V to AVDD + 0.3 V

VREF AGND –0.3 V to AVDD + 0.3 V

SENSE AGND –0.3 V to AVDD + 0.3 V

REFB, REFT AGND –0.3 V to AVDD + 0.3 V

CML AGND –0.3 V to AVDD + 0.3 V

VR AGND –0.3 V to AVDD + 0.3 V

OTR DGND –0.3 V to DRVDD + 0.3 V

D0–D13 DGND –0.3 V to DRVDD + 0.3 V

OEB DGND –0.3 V to DRVDD + 0.3 V

ENVIRONMENTAL1

Junction Temperature

Storage Temperature

Operating Temperature

Lead Temperature (10 sec) 300°C

1

Typical thermal impedances; θJA = 50.0°C/W; θJC = 17.0°C/W. These

measurements were taken on a 4-layer board in still air, in accordance with

EIA/JESD51-7.

Respect to Rating

DGND

−0.3 V to +6.5 V

150°C

−65°C to +150°C

−40°C to +85°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to

absolute maximum ratings for extended periods may affect

device reliability.

EXPLANATION OF TEST LEVELS

Tes t Le v el

I. 100% production tested.

II. 100% production tested at 25°C and sample tested at

specified temperatures.

III. Sample tested only.

IV. Parameter is guaranteed by design and characterization

testing.

V. Parameter is a typical value only.

VI. 100% production tested at 25°C; guaranteed by design and

characterization testing for industrial temperature range;

100% production tested at temperature extremes for

military devices.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. B | Page 7 of 36

AD9244

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

VIN–46VIN+45CML44NIC43DCS42REFT41REFT40REFB39REFB38REFGND37VREF

48VR47

23

DGND

DRVDD

36

SENSE

35

DFS

34

AVDD

33

AGND

32

AGND

31

AVDD

30

DGND

29

DRVDD

28

OTR

27

D13 (MSB)

26

D12

25

D11

24

D10

02404-003

AGND

AGND

AVDD

AVDD

AGND

CLK–

CLK+

NIC

OEB

D0 (LSB)

1

PIN 1

2

3

4

5

6

7

8

9

10

11

D1

12

D2

13D314

AD9244

TOP VIEW

(Not to Scale)

15

16D417D518D619D720D821D922

DGND

DRVDD

Figure 3.

Table 6. Pin Function Descriptions

Pin No. Mnemonic Description

1, 2, 5, 32, 33 AGND Analog Ground.

3, 4, 31, 34 AVDD Analog Supply Voltage.

6, 7 CLK–, CLK+ Differential Clock Inputs.

8, 44 NIC No Internal Connection.

9 OEB Digital Output Enable (Active Low).

10 D0 (LSB) Least Significant Bit, Digital Output.

11–13, 16–21, 24–26 D1–D3, D4–D9, D10–D12 Digital Outputs.

14, 22, 30 DGND Digital Ground.

15, 23, 29 DRVDD Digital Supply Voltage.

27 D13 (MSB) Most Significant Bit, Digital Output.

28 OTR Out-of-Range Indicator (Logic 1 indicates OTR).

35 DFS Data Format Select. Connect to AGND for straight binary, AVDD for twos complement.

36 SENSE Internal Reference Control.

37 VREF Internal Reference.

38 REFGND Reference Ground.

39–42 REFB, REFT Internal Reference Decoupling.

43 DCS

50% Duty Cycle Stabilizer. Connect to AVDD to activate 50% duty cycle stabilizer, AGND

for external control of both clock edges.

45 CML Common-Mode Reference (0.5 × AVDD).

46, 47 VIN+, VIN– Differential Analog Inputs.

48 VR Internal Bias Decoupling.

Rev. B | Page 8 of 36

AD9244

TERMINOLOGY

Analog Bandwidth (Full Power Bandwidth)

The analog input frequency at which the spectral power of the

fundamental frequency (as determined by the FFT analysis) is

reduced by 3 dB.

Aperture Delay

The delay between the 50% point of the rising edge of the clock

and the instant at which the analog input is sampled.

Aperture Uncertainty (Jitter)

The sample-to-sample variation in aperture delay.

Differential Analog Input Voltage Range

The peak-to-peak differential voltage must be applied to the

converter to generate a full-scale response. Peak differential

voltage is computed by observing the voltage on a single pin

and subtracting the voltage from the other pin, which is

180 degrees out of phase. Peak-to-peak differential is computed

by rotating the input phase 180° and taking the peak measurement again. The difference is then found between the two peak

measurements.

Differential Nonlinearity (DNL, No Missing Codes)

An ideal ADC exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. Guaranteed no

missing codes to 14-bit resolution indicates that all 16,384 codes

must be present over all operating ranges.

1

Dual Tone SFDR

The ratio of the rms value of either input tone to the rms value

of the peak spurious component. The peak spurious component

may or may not be an IMD product.

Effective Number of Bits (ENOB)

The effective number of bits for a device for sine wave inputs at

a given input frequency can be calculated directly from its

measured SINAD using the following formula:

()

02.6/76.1−= SINADN

Gain Error

The first code transition should occur at an analog value

1/2 LSB above negative full scale. The last code transition

should occur at an analog value 1 1/2 LSB below the nominal

full scale. Gain error is the deviation of the actual difference

between first and last code transitions and the ideal difference

between first and last code transitions.

Common-Mode Rejection Ratio (CMRR)

Common-mode (CM) signals appearing on VIN+ and VIN–

are ideally rejected by the differential front end of the ADC.

With a full-scale CM signal driving both VIN+ and VIN–,

CMRR is the ratio of the amplitude of the full-scale input CM

signal to the amplitude of signal that is not rejected, expressed

1

in dBFS.

IF Sampling

Due to the effects of aliasing, an ADC is not necessarily limited

to Nyquist sampling. Higher sampled frequencies will be aliased

down into the first Nyquist zone (DC–f

/2) on the output of

CLOCK

the ADC. Care must be taken that the bandwidth of the sampled signal does not overlap Nyquist zones and alias onto itself.

Nyquist sampling performance is limited by the bandwidth of

the input SHA and clock jitter (noise caused by jitter increases

as the input frequency increases).

Integral Nonlinearity (INL)

INL refers to the deviation of each individual code from a line

drawn from negative full scale through positive full scale. The

point used as negative full scale occurs 1/2 LSB before the first

code transition. Positive full scale is defined as a level 1 1/2 LSB

beyond the last code transition. The deviation is measured from

the middle of each particular code to the true straight line.

Minimum Conversion Rate

The clock rate at which the SNR of the lowest analog signal

frequency drops by no more than 3 dB below the guaranteed

limit.

Maximum Conversion Rate

The clock rate at which parametric testing is performed.

Nyquist Sampling

When the frequency components of the analog input are below

the Nyquist frequency (f

CLOCK

/2).

Out-of-Range Recovery Time

The time it takes for the ADC to reacquire the analog input

after a transition from 10% above positive full scale to 10%

above negative full scale, or from 10% below negative full scale

to 10% below positive full scale.

Power Supply Rejection Ratio (PSRR)

The change in full scale from the value with the supply at its

minimum limit to the value with the supply at its maximum

limit.

1

Signal-to-Noise-and-Distortion (SINAD)

The ratio of the rms signal amplitude to the rms value of the

sum of all other spectral components below the Nyquist

frequency, including harmonics, but excluding dc.

1

Signal-to-Noise Ratio (SNR)

The ratio of the rms signal amplitude to the rms value of the

sum of all other spectral components below the Nyquist

frequency, excluding the first six harmonics and dc.

1

Spurious-Free Dynamic Range (SFDR)

The difference in dB between the rms amplitude of the input

signal and the peak spurious signal.

Rev. B | Page 9 of 36

AD9244

Temperature Drift

The temperature drift for offset error and gain error specifies

the maximum change from initial (25°C) value to the value at

T

or T

MIN

Total Harmonic Distortion (THD)

The ratio of the rms sum of the first six harmonic components

to the rms value of the measured input signal.

MAX

.

1

Offset Error

The major carry transition should occur for an analog value

1/2 LSB below VIN+ = VIN−. Offset error is defined as the

deviation of the actual transition from that point.

1

AC specifications may be reported in dBc (degrades as signal levels are

lowered) or in dBFS (always related back to converter full scale).

Rev. B | Page 10 of 36

AD9244

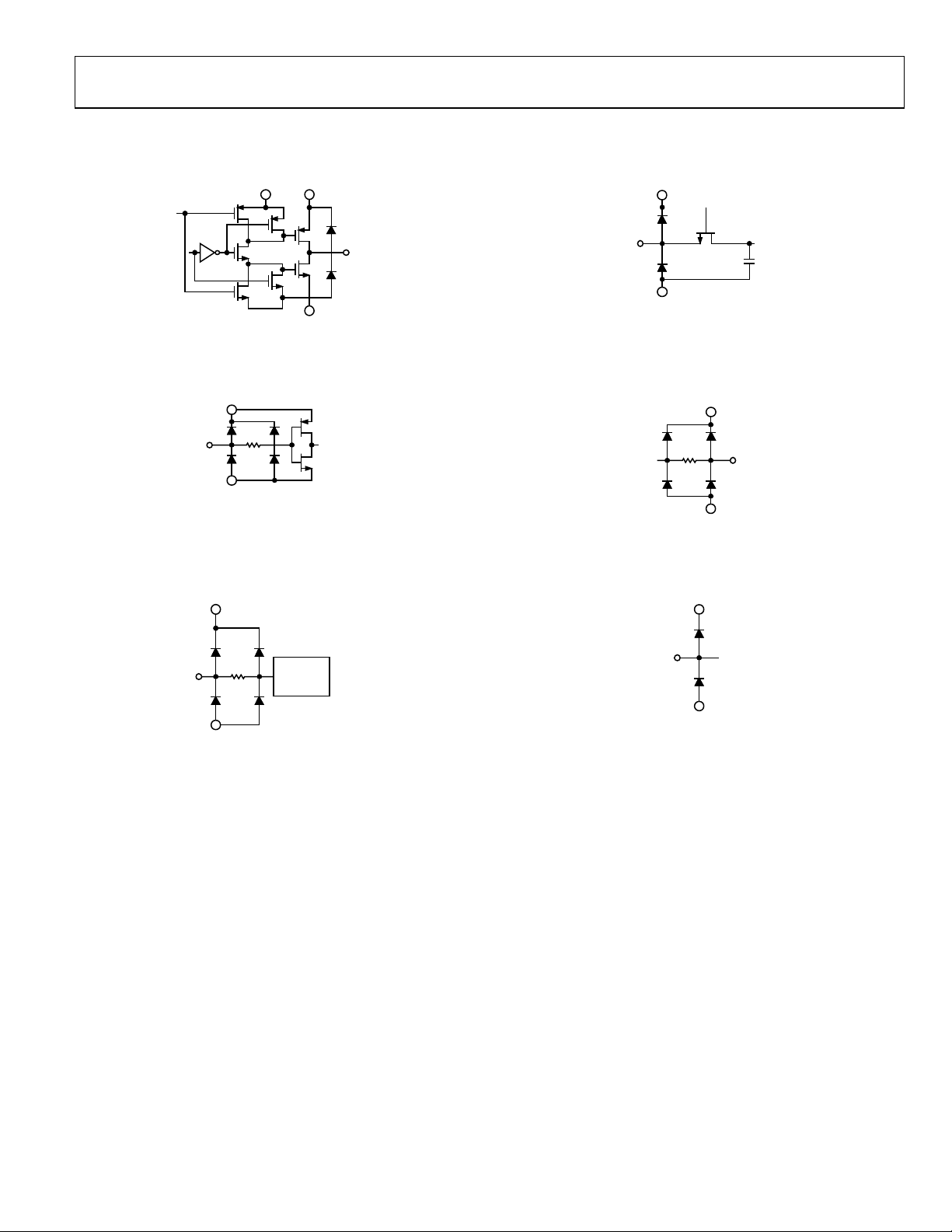

TYPICAL APPLICATION CIRCUITS

DRVDD DRVDD

DGND

Figure 4. D0-D13, OTR

DRVDD

200Ω

DGND

Figure 5. Three-State (OEB)

AVDD

02404-005

02404-004

AVDD

AGND

Figure 7. VIN+, VIN –

AVDD

200Ω

AGND

02404-008

Figure 8. DFS, DCS, SENSE

AVDD

02404-007

200Ω

AGND

Figure 6. CLK+, CLK –

CLK

BUFFER

02404-006

AGND

02404-009

Figure 9. VREF, REFT, REFB, VR, CML

Rev. B | Page 11 of 36

Loading...

Loading...