Analog Devices AD9071 Datasheet

10-Bit, 100 MSPS

a

FEATURES

10-Bit, 100 MSPS ADC

Low Power: 450 mW at 100 MSPS

On-Chip Track/Hold

280 MHz Analog Bandwidth

SINAD = 54 dB @ 41 MHz

On-Chip Reference

1 V p-p Analog Input Range

Single +5 V Supply Operation

+5 V/+3.3 V Outputs

APPLICATIONS

Digital Communications

Signal Intelligence

Digital Oscilloscopes

Spectrum Analyzers

Medical Imaging

Sonar

HDTV

GENERAL DESCRIPTION

The AD9071 is a monolithic sampling analog-to-digital converter with an on-chip track-and-hold circuit and TTL/CMOS

digital interfaces. The product operates at a 100 MSPS conversion rate with outstanding dynamic performance over its full

operating range.

The ADC requires only a single 5 V supply and an encode clock

for full performance operation. The digital outputs are TTL

compatible. Separate output power supply pins support

A/D Converter

AD9071

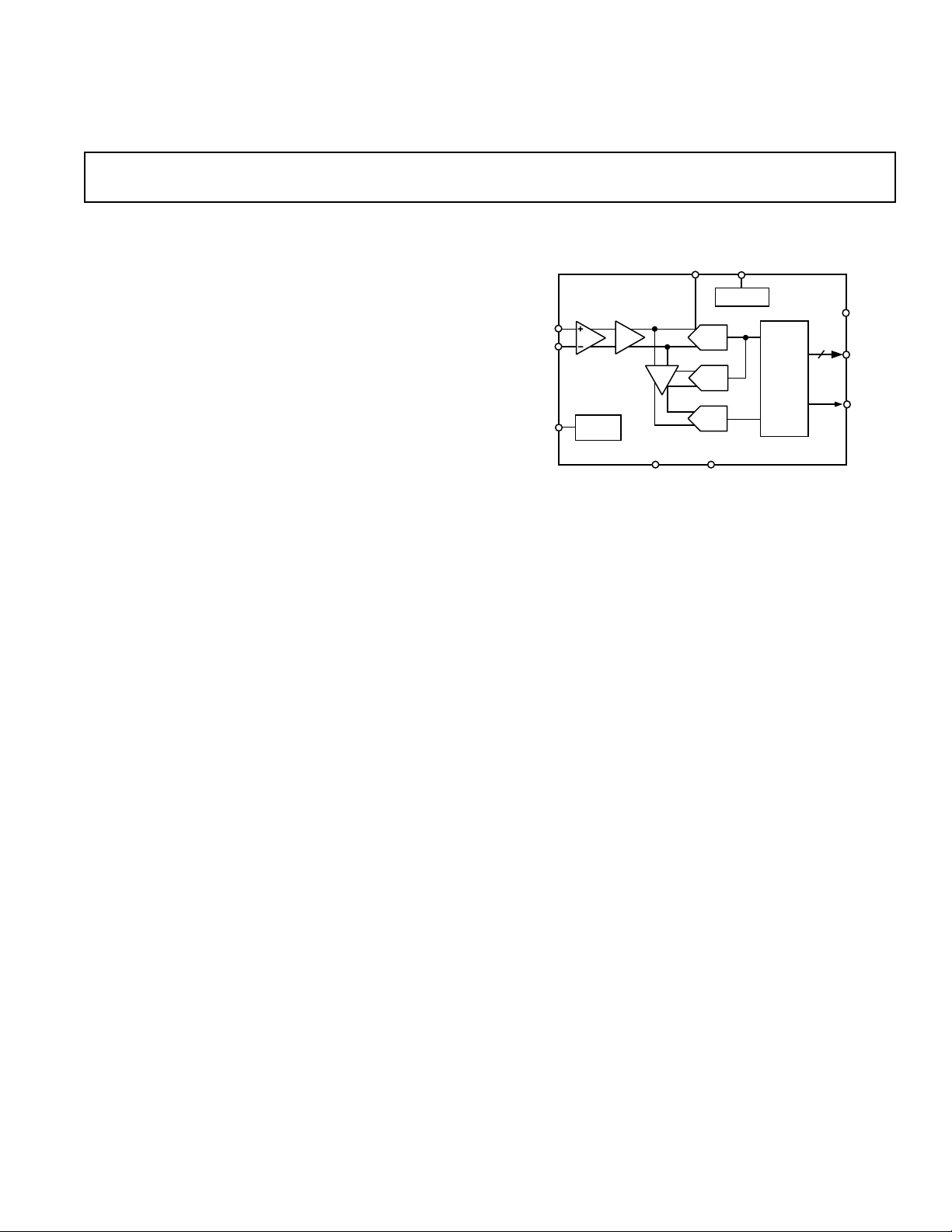

FUNCTIONAL BLOCK DIAGRAM

VREF

VREF

AD9071

AIN

AIN

ENCODE

TIMING

T/H

SUM

AMP

V

CC

interfacing with 3.3 V or 5 V logic. An out-of-range output

(OR) is available that indicates a conversion result is outside the

operating range. The output data are held at saturation levels

during an out-of-range condition.

The input amplifier supports differential or single-ended interfaces. An internal reference is included.

Fabricated on an advanced BiCMOS process, the AD9071 is

available in a plastic SOIC package specified over the industrial

temperature range (–40°C to +85°C).

IN

ADC

DAC

ADC

GND

OUT

VCC – 2.5V

ENCODE

LOGIC

V

DD

10

D0–D9

OR

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

(VCC = +5 V, VDD = +3.3 V, Differential Analog Input, ENCODE = 100 MSPS unless

AD9071–SPECIFICATIONS

otherwise noted)

Test AD9071BR

Parameter Temp Level Min Typ Max Units

RESOLUTION 10 Bits

DC ACCURACY

Differential Nonlinearity

Integral Nonlinearity

No Missing Codes

Gain Error

Gain Tempco

2

2

1

1

1

+25°CI ±0.8 +1.5/–1.0 LSB

Full VI ±1.0 +1.75/–1.0 LSB

+25°CI ±0.8 ±1.5 LSB

Full VI ±1.25 ±1.75 LSB

+25°C I ␣␣␣␣␣␣ Guaranteed ␣ ␣ ␣

+25°CI ±1 ±4% FS

Full VI ±2 ±8% FS

Full V 150 ppm/°C

ANALOG INPUT

Input Voltage Range

(With Respect to AIN) Full V ±512 mV p-p

Common-Mode Voltage Full V –2.5 ± 0.2 V

Input Offset Voltage +25°CI ±4 ±18 mV

Full VI ±5 ±20 mV

Input Resistance Full VI 15 35 kΩ

Input Capacitance +25°CV 3 pF

Input Bias Current +25°C I 55 90 µA

Full VI 65 115 µA

Analog Bandwidth, Full Power +25°C V 280 MHz

REFERENCE OUTPUT

Output Voltage Full VI VCC – 2.6 VCC – 2.5 VCC – 2.4 V

Temperature Coefficient Full V 130 ppm/°C

SWITCHING PERFORMANCE

Maximum Conversion Rate Full VI 100 MSPS

Minimum Conversion Rate Full IV 40 MSPS

Encode Pulsewidth High (t

Encode Pulsewidth Low (t

Aperture Delay (t

) +25°C V 1.1 ns

A

Aperture Uncertainty (Jitter) +25°C V 3.0 ps, rms

Output Valid Time (t

V

Output Propagation Delay (t

Output Rise Time (t

) Full V 1.4 ns

R

) +25°C IV 4.5 13 ns

EH

) +25°C IV 4.5 13 ns

EL

3

)

PD

3

)

Full VI 2.0 4.0 ns

Full VI 5.0 7.0 ns

Output Fall Time (tF) Full V 1.0 ns

DIGITAL INPUT

Logic “1” Voltage Full VI 2.0 V

Logic “0” Voltage Full VI 0.8 V

Logic “1” Current Full VI ±10 µA

Logic “0” Current Full VI –500 µA

Input Capacitance +25°CV 3 pF

DIGITAL OUTPUTS

Logic “1” Voltage Full VI V

– 0.5 V

DD

Logic “0” Voltage Full VI 0.05 V

Output Coding Offset Binary

POWER SUPPLY

V

Supply Current (VCC = 5 V)

CC

Supply Current (VDD = 3.3 V)

V

DD

Power Dissipation

4

Power Supply Sensitivity

5

4

4

Full VI 85 115 mA

Full VI 7.5 14 mA

Full VI 450 620 mW

+25°C I 0.002 0.010 V/V

–2–

REV. B

AD9071

Test AD9071BR

Parameter Temp Level Min Typ Max Units

DYNAMIC PERFORMANCE

Transient Response +25°CV 4 ns

Overvoltage Recovery Time +25°CV 5 ns

Signal-to-Noise Ratio (SNR)

(Without Harmonics)

= 10.3 MHz +25°C I 54 56 dB

f

IN

f

= 41 MHz +25°C I 53 55 dB

IN

Signal-to-Noise Ratio (SINAD)

(With Harmonics)

= 10.3 MHz +25°C I 54 56 dB

f

IN

f

= 41 MHz +25°C I 52 54 dB

IN

Effective Number of Bits

= 10.3 MHz +25°C I 8.8 9.2 Bits

f

IN

= 41 MHz +25°C I 8.5 8.8 Bits

f

IN

2nd Harmonic Distortion

f

= 10.3 MHz +25°C I 63 75 dBc

IN

= 41 MHz +25°C I 60 66 dBc

f

IN

3rd Harmonic Distortion

f

= 10.3 MHz +25°C I 65 75 dBc

IN

= 41 MHz +25°C I 57 65 dBc

f

IN

Two-Tone Intermodulation (IMD)

f

= 10.3 MHz +25°C V 70 dBc

IN

f

= 41 MHz +25°C V 60 dBc

IN

NOTES

1

Differential and integral nonlinearity based on FS = 80 MSPS.

2

Gain error and gain temperature coefficient are based on the ADC only (with a fixed 2.5 V external reference).

3

tV and tPD are measured from the threshold crossing of the ENCODE input to the 50% levels of the digital outputs. The output ac load during test is 5 pF.

4

Power dissipation is measured under the following conditions: FS @ 100 MSPS, analog input is –1 dBFS at 10.3 MHz.

5

A change in input offset voltage with respect to a change in VCC.

6

SNR/harmonics based on an analog input voltage of –1.0 dBFS referenced to a 1.024 V full-scale input range.

Typical thermal impedance for the R style (SOIC) 28-lead package: θJC = 23°C/W, θCA = 48°C/W, θJA = 71°C/W.

Specifications subject to change without notice.

6

Full V 55 dB

Full V 54 dB

Full V 55 dB

Full V 53 dB

ABSOLUTE MAXIMUM RATINGS*

VCC␣ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +6 V

Analog Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . V

Digital Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . V

VREF IN, VREF OUT . . . . . . . . . . . . . . . . . . . . V

to 0.0 V

CC

to 0.0 V

CC

to 0.0 V

CC

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . 10 mA

Operating Temperature . . . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

Maximum Junction Temperature . . . . . . . . . . . . . . . .+175°C

Maximum Case Temperature . . . . . . . . . . . . . . . . . . .+150°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum ratings

for extended periods may effect device reliability.

EXPLANATION OF TEST LEVELS

Test Level

I. 100% production tested.

II. 100% production tested at +25°C and sample tested at

specified temperatures.

III. Sample tested only.

IV. Parameter is guaranteed by design and characterization

testing.

V. Parameter is a typical value only.

VI. 100% production tested at +25°C; guaranteed by design

and characterization testing for industrial temperature range.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9071 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–3–REV. B

WARNING!

ESD SENSITIVE DEVICE

AD9071

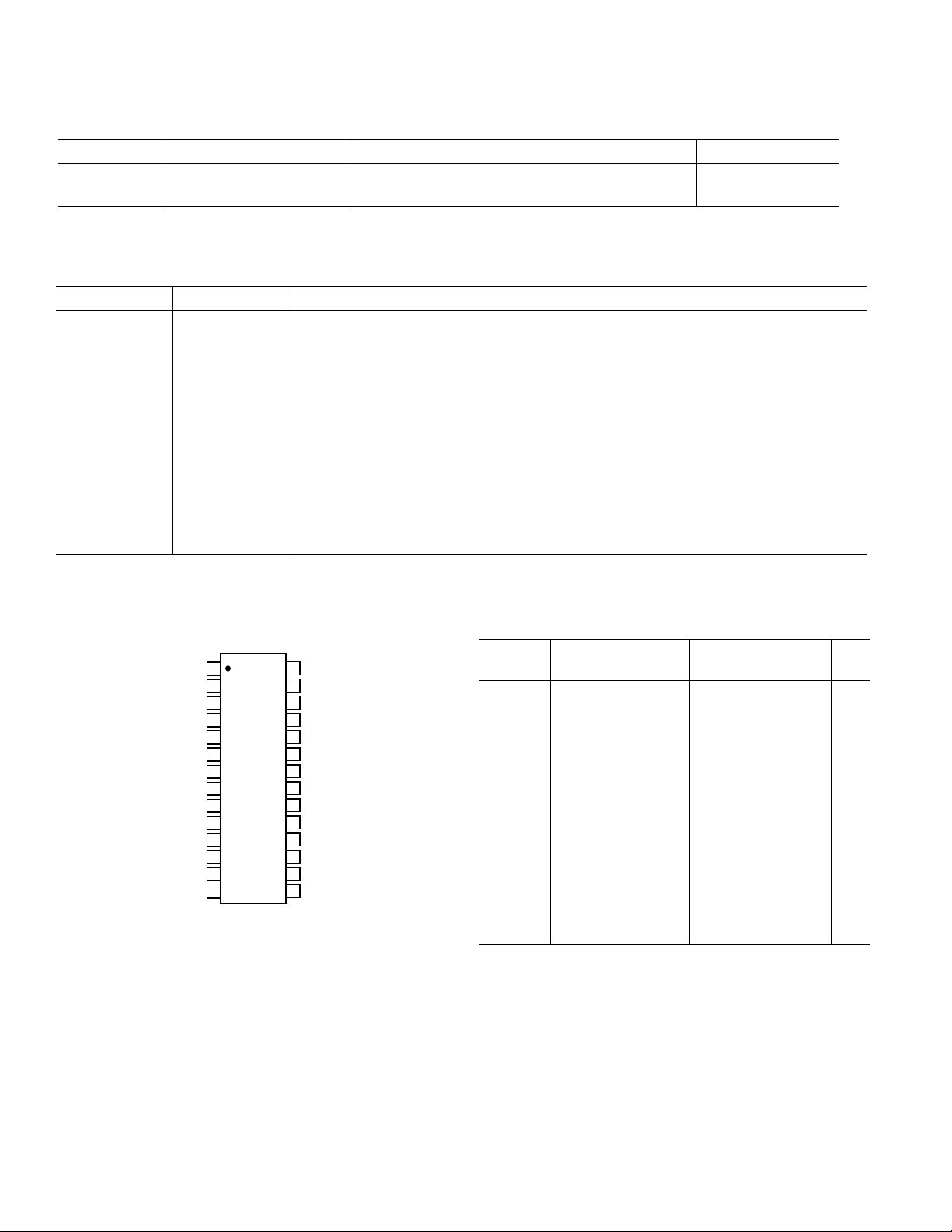

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD9071BR –40°C to +85°C 28-Lead Wide Body (SOIC) R-28

AD9071/PCB +25°C Evaluation Board

PIN FUNCTION DESCRIPTIONS

Pin No. Name Function

1, 7, 12, 21, 23 GND Ground.

2, 8, 11 V

CC

3 VREF OUT Internal Reference Output (V

4 VREF IN Reference Input for ADC (V

5, 6 DNC Do Not Connect.

9 AIN Analog Input – Complementary.

10 AIN Analog Input – True.

13 ENCODE Encode clock for ADC. (ADC Samples on Rising Edge of ENCODE.)

14 OR Out-of-Range Output. Goes HIGH when the converted sample is more positive than

15–19, 24–28 D9–D0 Digital outputs of ADC. D9 is the MSB. Data is offset binary.

20, 22 V

DD

Analog Power Supply. Nominally 5.0 V. (Tie together to prevent a possible latch-up condition.)

– 2.5 V typical); Bypass with 0.1 µF to V

CC

– 2.5 V typical).

CC

3FF

or more negative than 000H (offset binary coding).

H

CC

.

Digital Output Power Supply. User selectable range from 3 V to 5 V.

PIN CONFIGURATION

1

GND

V

2

CC

VREF OUT

VREF IN

ENCODE

3

4

5

DNC

6

DNC

7

GND

8

V

CC

9

AIN

AIN

10

V

11

CC

12

GND

13

14

OR

DNC = DO NOT CONNECT

AD9071BR

TOP VIEW

(Not to Scale)

28

27

26

25

24

23

22

21

20

19

18

17

16

15

D0

D1

D2

D3

D4

GND

V

DD

GND

V

DD

D5

D6

D7

D8

D9 (MSB)

Table I. Output Coding

Offset

Code AIN–AIN Binary OR

1023 ≥ 0.512 V 11 1111 1111 1

1023 0.511 V 11 1111 1111 0

1022 0.510 V 11 1111 1110 0

•• ••

•• ••

•• ••

513 0.001 V 10 0000 0001 0

512 0.000 V 10 0000 0000 0

511 –0.001 V 01 1111 1111 0

•• ••

•• ••

•• ••

1 –0.511 V 00 0000 0001 0

0 –0.512 V 00 0000 0000 0

0 ≤–0.513 V 00 0000 0000 1

–4–

REV. B

Loading...

Loading...