High Common-Mode Voltage,

FEATURES

High common-mode voltage range

−6 V to +30 V at a 5 V supply voltage

Operating temperature range: −40°C to +125°C

Supply voltage range: 3.5 V to 12 V

Low-pass filter (1-pole or 2-pole)

Excellent ac and dc performance

±1 mV voltage offset (8-lead SOIC)

±1 ppm/°C typical gain drift

80 dB CMRR minimum dc to 10 kHz

APPLICATIONS

Transmission control

Diesel injection control

Engine management

Adaptive suspension control

Vehicle dynamics control

GENERAL DESCRIPTION

The AD8203 is a single-supply difference amplifier for amplifying and low-pass filtering small differential voltages in the

presence of a large common-mode voltage (CMV). The input

CMV range extends from −6 V to +30 V at a typical supply

voltage of 5 V.

Single-Supply Difference Amplifier

AD8203

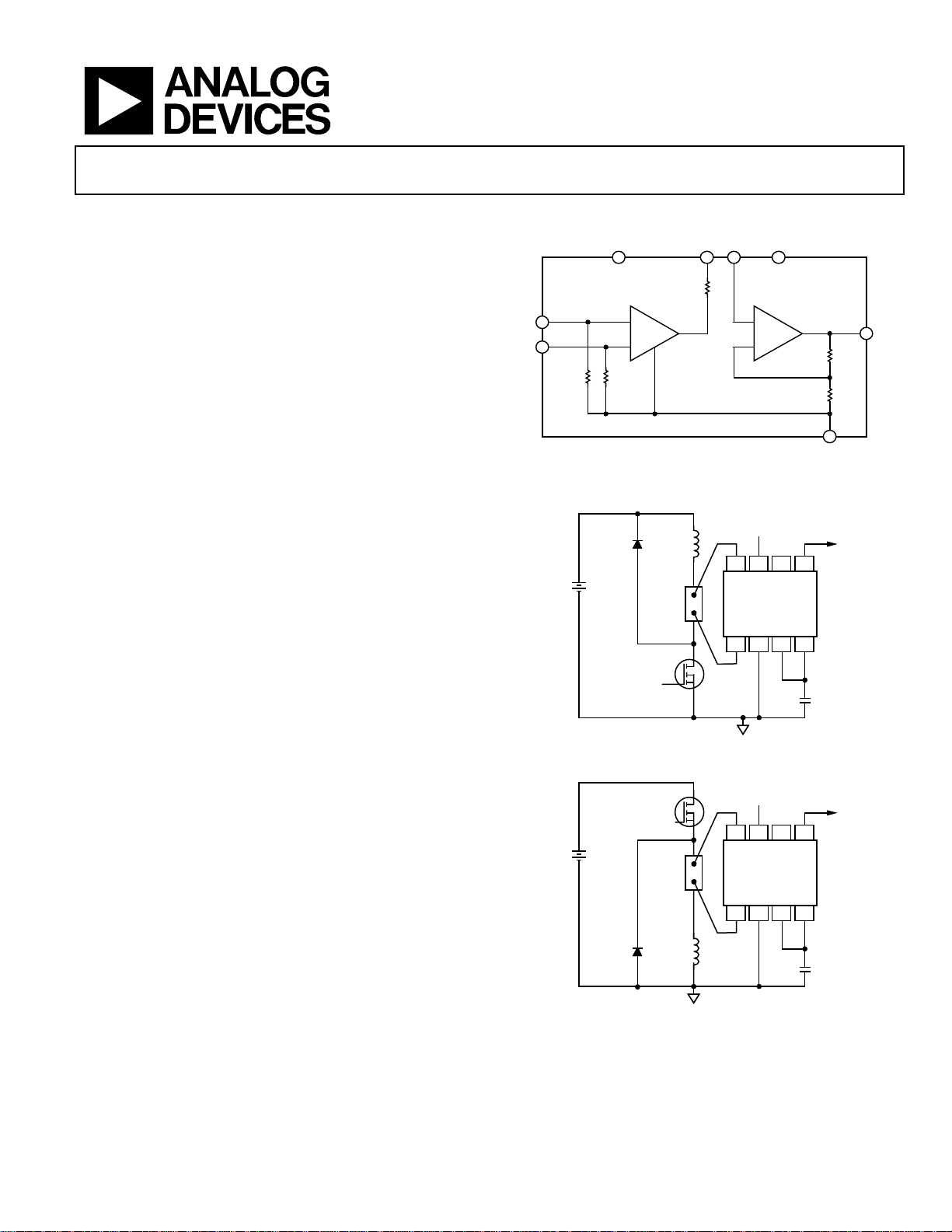

FUNCTIONAL BLOCK DIAGRAMS

+V

A2

3

INDUCTIVE

LOAD

+INA1+V

–IN

746

G = ×2

+IN

A2

–IN

5V

NC

S

AD8203

GND

S

AD8203

5

OUT

10kΩ

10kΩ

2

GND

OUT

A2

05013-001

OUTPUT

8

+IN

1

–IN

BATTERY

NC A1

200kΩ200kΩ

NC = NO CONNECT

Figure 1. Functional Block Diagram

CLAMP

DIODE

14V

G = ×7

+IN

A1

–IN

4-TERM

SHUNT

POWER

DEVICE

100kΩ

The AD8203 is available in die and packaged form. The MSOP

and SOIC packages are specified over a wide temperature range,

from −40°C to +125°C, while the die is specified over a wider

temperature range, from −40°C to +150°C, making the AD8203

well-suited for use in many automotive platforms.

Automotive platforms demand precision components for better

system control. The AD8203 provides excellent ac and dc

performance keeping errors to a minimum in the user’s system.

Typical offset and gain drift in the SOIC package are 0.3 µV/°C and

1 ppm/°C, respectively. Typical offset and gain drift in the MSOP

package are 2 V/°C and 1 ppm/°C, respectively. The device also

delivers a minimum CMRR of 80 dB from dc to 10 kHz.

The AD8203 features an externally accessible 100 kΩ resistor at

the output of the Preamp A1, which can be used for low-pass

filter applications and for establishing gains other than 14.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

COMMON

NC = NO CONNECT

Figure 2. High Line Current Sensor

POWER

BATTERY

DEVICE

14V

CLAMP

DIODE

COMMON NC = NO CONNECT

4-TERM

SHUNT

INDUCTIVE

LOAD

+INA1+V

AD8203

–IN

5V

GND

OUT

NC

S

A2

Figure 3. Low Line Current Sensor

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

OUTPUT

05013-002

05013-003

AD8203

TABLE OF CONTENTS

Features .............................................................................................. 1

Current Sensing .......................................................................... 14

Applications....................................................................................... 1

Functional Block Diagrams............................................................. 1

Specifications..................................................................................... 3

Single Supply ................................................................................. 3

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

Typical Performance Characteristics ............................................. 6

Theory of Operation ...................................................................... 12

Applications..................................................................................... 14

REVISION HISTORY

10/05—Rev. A to Rev. B

Added SOIC Package.........................................................Universal

Replaced Figure 23 ........................................................................... 8

Added Figure 24 to Figure 29.......................................................... 9

Changes to Theory of Operation Section ................................... 12

Added Figure 41.............................................................................. 12

Updated Outline Dimensions....................................................... 17

Changes to Ordering Guide.......................................................... 17

Gain Adjustment........................................................................ 14

Gain Trim.................................................................................... 15

Low-Pass Filtering ...................................................................... 15

High Line Current Sensing with LPF and

Gain Adjustment........................................................................ 16

Driving Charge Redistribution ADCs..................................... 16

Outline Dimensions ....................................................................... 17

Ordering Guide .......................................................................... 17

2/05—Rev. 0 to Rev. A

Changes to Specifications Table...................................................... 3

Changes to Caption on Figure 6 and Figure 8.............................. 6

Changes to Figure 12........................................................................ 7

Added Figure 14 to Figure 23.......................................................... 7

Changes to Figure 26 and Figure 27............................................. 10

Changes to Figure 29...................................................................... 11

Changes to Figure 32 and Figure 33............................................. 12

Changes to Ordering Guide.......................................................... 13

10/04—Revision 0: Initial Version

Rev. B | Page 2 of 20

AD8203

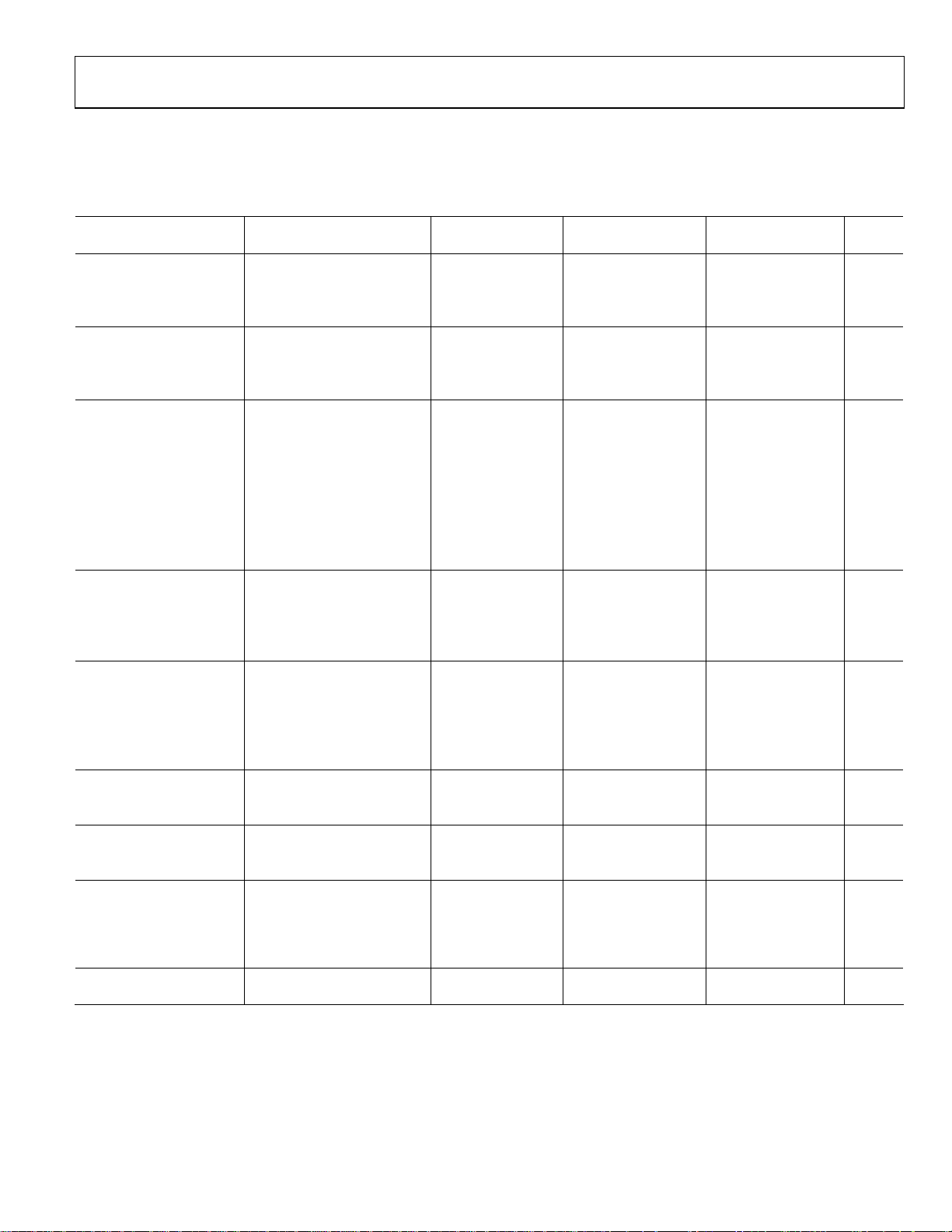

SPECIFICATIONS

SINGLE SUPPLY

TA = operating temperature range, VS = 5 V, unless otherwise noted.

Table 1.

AD8203 SOIC AD8203 MSOP AD8203 Die

Parameter Conditions Min Typ Max Min Typ Max Min Typ Max Unit

SYSTEM GAIN

Initial 14 14 14 V/V

Error 0.02 ≤ V

vs. Temperature 1 20 1 25 1 30 ppm/°C

VOLTAGE OFFSET

Input Offset (RTI) VCM = 0.15 V; 25°C −1 +1 −2 +2 −1 +1 mV

vs. Temperature −40°C to +125°C −10 +0.3 +10 −20 +2 +20 −10 +0.3 +10 μV/°C

−40°C to +150°C −15 +5 +15 μV/°C

INPUT

Input Impedance

Differential 260 320 380 260 320 380 260 320 380 kΩ

Common Mode 130 160 190 130 160 190 130 160 190 kΩ

CMV Continuous −6 +30 −6 +30 −6 +30 V

1

CMRR

VCM = −6 V to +30 V

f = dc 82 82 82 dB

f = 1 kHz 82 82 82 dB

f = 10 kHz

PREAMPLIFIER

Gain 7 7 7 V/V

Gain Error −0.3 +0.3 −0.3 +0.3 −0.3 +0.3 %

Output Voltage Range 0.02 4.8 0.02 4.8 0.02 4.8 V

Output Resistance 97 100 103 97 100 103 97 100 103 kΩ

OUTPUT BUFFER

Gain 2 2 2 V/V

Gain Error 0.02 ≤ V

Output Voltage Range 0.02 4.8 0.02 4.8 0.02 4.8 V

Input Bias Current 40 40 40 nA

Output Resistance 2 2 2 Ω

DYNAMIC RESPONSE

System Bandwidth VIN = 0.01 V p-p, V

Slew Rate VIN = 0.28 V, V

NOISE

0.1 Hz to 10 Hz 10 10 10 μV p-p

Spectral Density, 1 kHz (RTI) 300 300 300 nV/√Hz

POWER SUPPLY

Operating Range 3.5 12 3.5 12 3.5 12 V

Quiescent Current vs.

VO = 0.1 V dc 0.25 1.0 0.25 1.0 0.25 1.0 mA

Temperature

PSRR VS = 3.5 V to 12 V 75 83 75 83 75 83 dB

TEMPERATURE RANGE

For Specified Performance −40 +125 −40 +125 −40 +150 °C

1

Source imbalance <2 Ω.

2

The AD8203 preamplifier exceeds 80 dB CMRR at 10 kHz. However, since the signal is available only by way of a 100 kΩ resistor, even the small amount of pin-to-pin

capacitance between Pin 1, Pin 8 and Pin 3, Pin 4 may couple an input common-mode signal larger than the greatly attenuated preamplifier output. The effect of pinto-pin coupling may be neglected in all applications by using filter capacitors at Node 3.

≤ 4.8 V dc @ 25°C −0.3 +0.3 −0.3 +0.3 −0.3 +0.3 %

OUT

2

≤ 4.8 V dc −0.3 +0.3 −0.3 +0.3 −0.3 +0.3 %

OUT

= 0.14 V p-p 40 60 40 60 40 60 kHz

OUT

= 4 V step 0.33 0.33 0.33 V/μs

OUT

80 80 80 dB

Rev. B | Page 3 of 20

AD8203

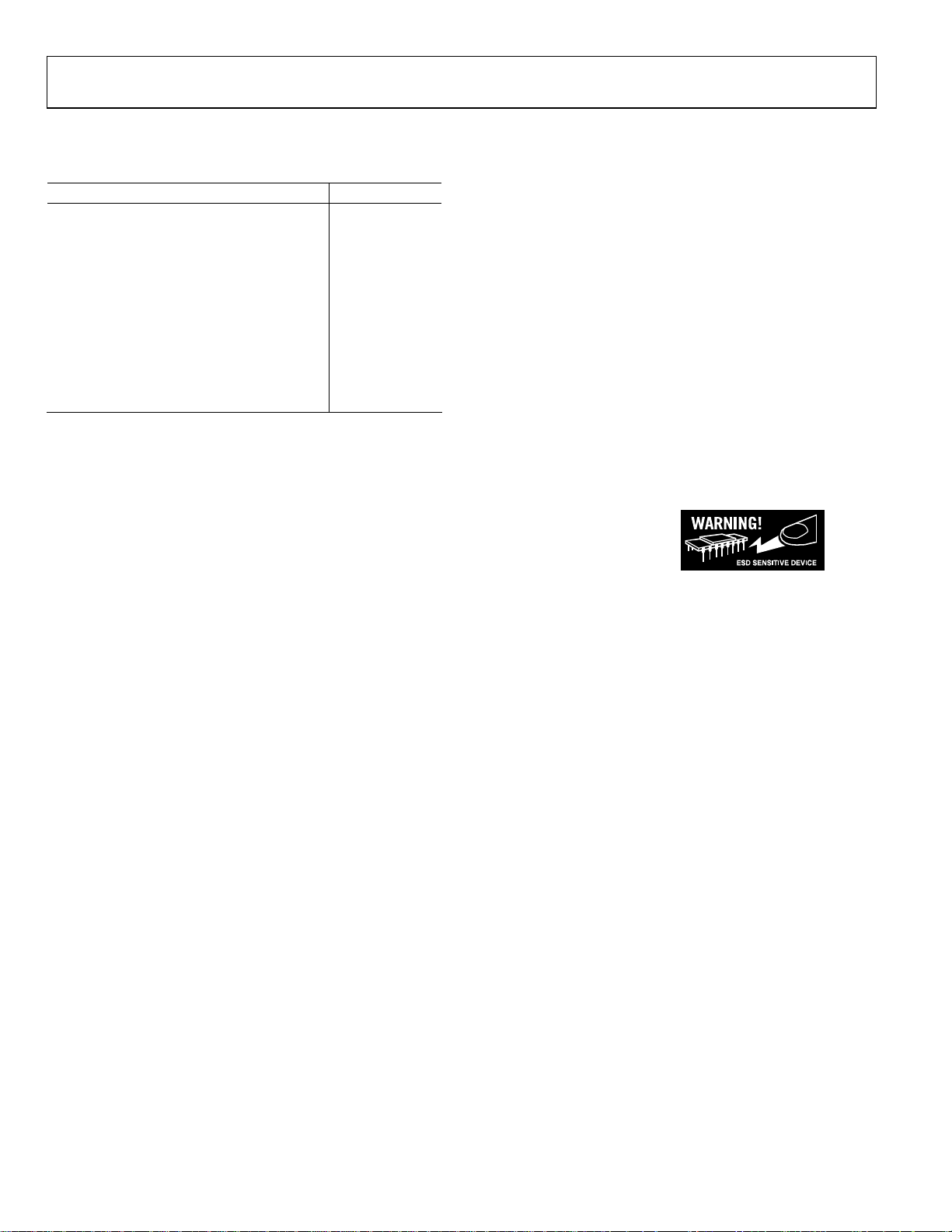

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage 12.5 V

Transient Input Voltage (400 ms) 44 V

Continuous Input Voltage (Common Mode) 35 V

Reversed Supply Voltage Protection 0.3 V

Operating Temperature Range

Die −40°C to +150°C

SOIC −40°C to +125°C

MSOP −40°C to +125°C

Storage Temperature −65°C to +150°C

Output Short-Circuit Duration Indefinite

Lead Temperature Range (Soldering 10 sec) 300°C

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate

on the human body and test equipment and can discharge without detection. Although this product

features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to

high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid

performance degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. B | Page 4 of 20

AD8203

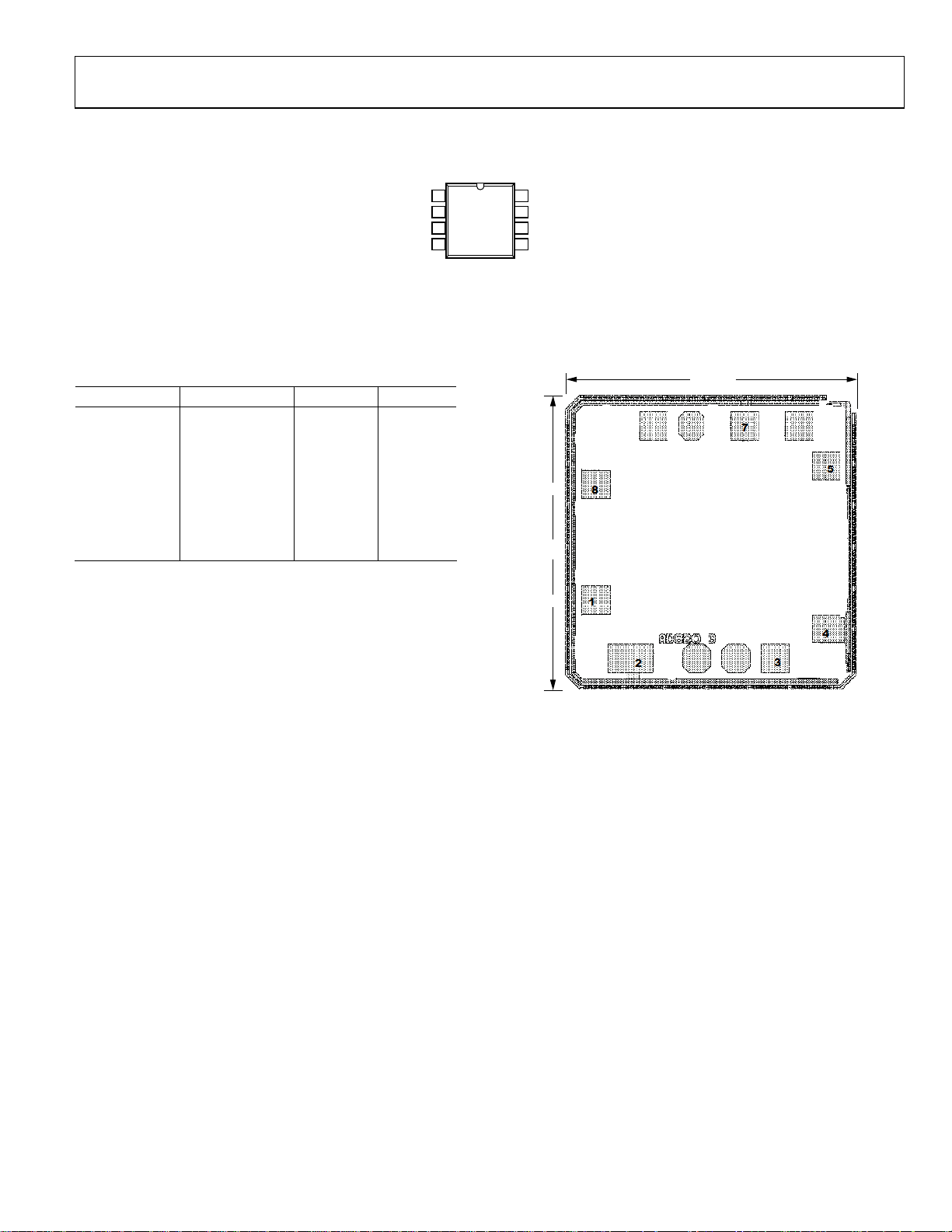

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

–IN

GND

AD8203

2

A1

3

TOP VIEW

(Not to Scale)

A2

4

NC = NO CONNECT

Figure 4. Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic X Y

1 −IN −205.2

−409.0

2 GND −244.6 −413.0

3 A1 +229.4 −413.0

4 A2 +410.0 −308.6

5 OUT +410.0 +272.4

6 NC NA NA

7 +V +121.0 S+417.0

8 +IN −409.0 +205.2

8

7

6

5

1048μm

+IN

+V

NC

OUT

S

+IN

–IN

05013-004

1036μm

+V

S

OUT

A2

A1GND

Figure 5. Metallization Photograph

05013-005

Rev. B | Page 5 of 20

AD8203

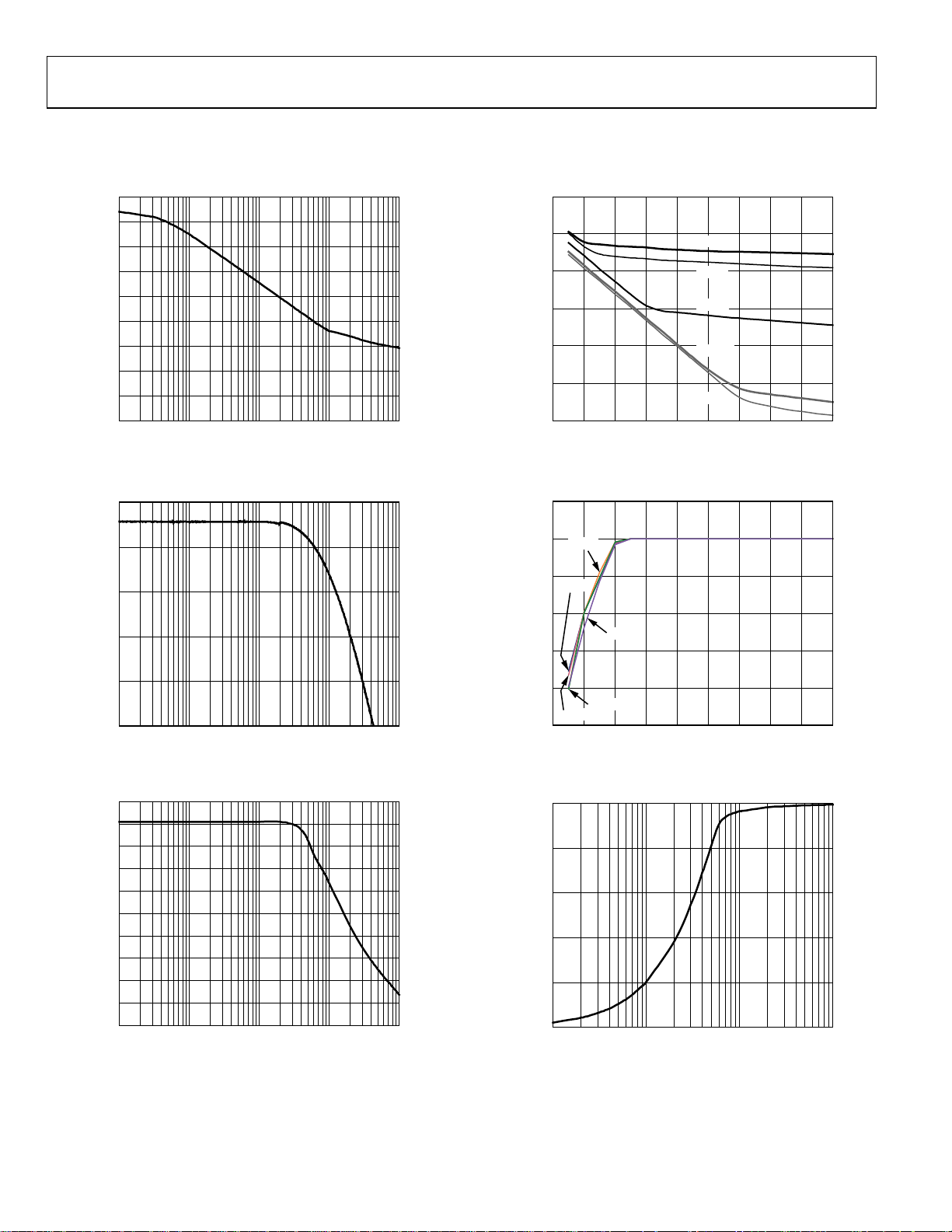

TYPICAL PERFORMANCE CHARACTERISTICS

T = 25°C, V = 5 V, V = 0 V, R

A S CM L

90

80

70

60

50

40

PSRR (dB)

30

20

10

0

10 100 1k 10k 100k

Figure 6. Power Supply Rejection Ratio vs. Frequency

for Common-Mode Range −6 V to +30 V

= 10 kΩ, unless otherwise noted.

FREQUENCY (Hz)

05013-006

0

–5

–10

–15

–20

COMMON-MODE VOLTAGE (V)

–25

–30

354876 9 10 11 12

POWER SUPPLY (V)

–55°C

–40°C

+25°C

+125°C

+150°C

Figure 9. Negative Common-Mode Voltage vs. Voltage Supply

05013-009

25

20

15

10

OUTPUT (dB)

5

0

100 1k 10k 100k 1M

FREQUENCY (Hz)

Figure 7. Bandwidth

100

95

90

85

80

75

CMRR (dB)

70

65

60

55

50

10 100 1k 10k 100k

FREQUENCY (Hz)

Figure 8. Common-Mode Rejection Ratio vs. Frequency

for Common-Mode Range −6 V to +30 V

05013-007

05013-008

40

35

+25°C

30

–55°C

25

+150°C

20

COMMON-MODE VOLTAGE (V)

15

+125°C

–40°C

10

354876 9 10 11 12

POWER SUPPLY (V)

Figure 10. Positive Common-Mode Voltage vs. Voltage Supply

5.0

4.0

3.0

2.0

OUTPUT VOLTAGE (dB)

1.0

0

10 100 1k 10k

LOAD RESISTANCE (Ω)

Figure 11. Output Swing vs. Load Resistance

05013-010

05013-011

Rev. B | Page 6 of 20

Loading...

Loading...