Analog Devices AD8108 9 a Datasheet

325 MHz, 8 8 Buffered Video

a

FEATURES

8 8 High-Speed Nonblocking Switch Arrays

AD8108: G = +1

AD8109: G = +2

Serial or Parallel Programming of Switch Array

Serial Data Out Allows “Daisy Chaining” of Multiple

8 8s to Create Larger Switch Arrays

Output Disable Allows Connection of Multiple Devices

Pin-Compatible with AD8110/AD8111 16 8 Switch

Arrays

For 16 16 Arrays See AD8116

Complete Solution

Buffered Inputs

Eight Output Amplifiers,

AD8108 (G = +1),

AD8109 (G = +2)

Drives 150 Loads

Excellent Video Performance

60 MHz 0.1 dB Gain Flatness

0.02%/0.02 Differential Gain/Differential Phase Error

= 150 )

(R

L

Excellent AC Performance

AD8108 AD8109

–3 dB Bandwidth 325 MHz 250 MHz

Slew Rate 400 V/s 480 V/s

Low Power of 45 mA

Low All Hostile Crosstalk of –83 dB @ 5 MHz

Reset Pin Allows Disabling of All Outputs (Connected

Through a Capacitor to Ground Provides “PowerOn” Reset Capability)

Excellent ESD Rating: Exceeds 4000 V Human Body

Model

80-Lead LQFP Package (12 mm 12 mm)

APPLICATIONS

Routing of High-Speed Signals Including:

Composite Video (NTSC, PAL, S, SECAM.)

Component Video (YUV, RGB)

Compressed Video (MPEG, Wavelet)

3-Level Digital Video (HDB3)

PRODUCT DESCRIPTION

The AD8108 and AD8109 are high-speed 8 × 8 video crosspoint switch matrices. They offer a –3 dB signal bandwidth

greater than 250 MHz and channel switch times of less than

25 ns with 1% settling. With –83 dB of crosstalk and –98 dB

isolation (@ 5 MHz), the AD8108/AD8109 are useful in many

high-speed applications. The differential gain and differential

Crosspoint Switches

AD8108/AD8109

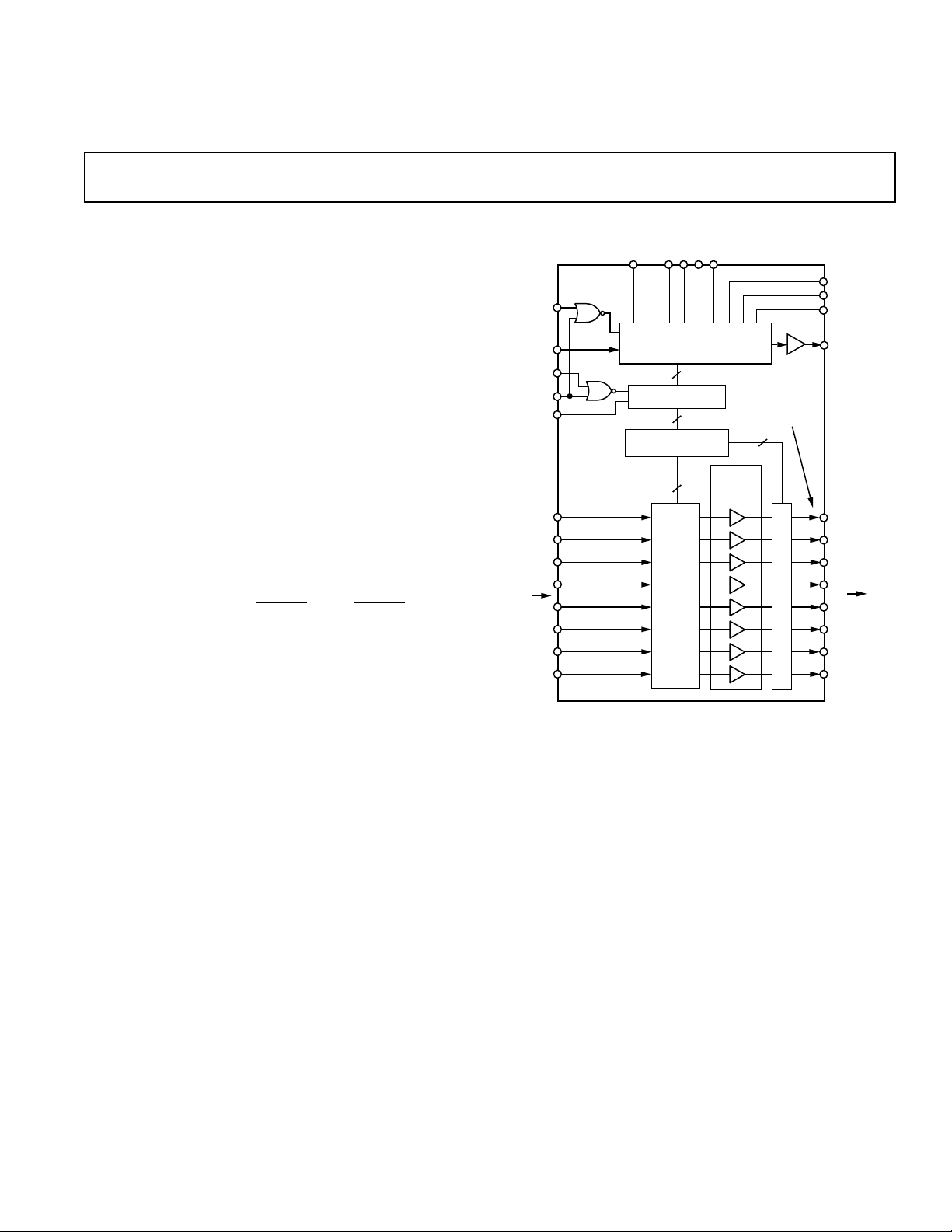

FUNCTIONAL BLOCK DIAGRAM

SER/PAR

CLK

DATA IN

UPDATE

CE

RESET

AD8108/AD8109

8 INPUTS

phase of better than 0.02% and 0.02° respectively along with

0.1 dB flatness out to 60 MHz make the AD8108/AD8109 ideal

for video signal switching.

The AD8108 and AD8109 include eight independent output buffers that can be placed into a high impedance state for paralleling

crosspoint outputs so that off channels do not load the output bus.

The AD8108 has a gain of +1, while the AD8109 offers a gain

of +2. They operate on voltage supplies of ±5 V while consuming

only 45 mA of idle current. The channel switching is performed via

a serial digital control (which can accommodate “daisy chaining”

of several devices) or via a parallel control allowing updating of

an individual output without re-programing the entire array.

The AD8108/AD8109 is packaged in an 80-lead LQFP package

and is available over the extended industrial temperature range

of –40°C to +85°C.

D0 D1 D2 D3

32-BIT SHIFT REGISTER

WITH 4-BIT

PARALLEL LOADING

32

PARALLEL LATCH

32

DECODE

8 4:8 DECODERS

OUTPUT

BUFFER

64

G = +1,

SWITCH

MATRIX

SET INDIVIDUAL

OR RESET ALL

OUTPUTS

TO "OFF"

8

G = +2

ENABLE/DISABLE

*

A0

A1

A2

DATA

OUT

8 OUTPUTS

*Patent Pending.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

AD8108/AD8109–SPECIFICATIONS

(VS = 5 V, TA = +25C, RL = 1 k unless otherwise noted)

AD8108/AD8109 Reference

Parameter Conditions Min Typ Max Unit Figure No.

DYNAMIC PERFORMANCE

–3 dB Bandwidth 200 mV p-p, R

2 V p-p, R

Propagation Delay 2 V p-p, R

Slew Rate 2 V Step, R

Settling Time 0.1%, 2 V Step, R

Gain Flatness 0.05 dB, 200 mV p-p, R

0.05 dB, 2 V p-p, R

0.1 dB, 200 mV p-p, R

0.1 dB, 2 V p-p, RL = 150 Ω 80/50 MHz TPC 1, 7

NOISE/DISTORTION PERFORMANCE

Differential Gain Error NTSC or PAL, R

NTSC or PAL, R

Differential Phase Error NTSC or PAL, R

NTSC or PAL, R

Crosstalk, All Hostile f = 5 MHz 83/85 dB TPC 2, 8

f = 10 MHz 76/83 dB TPC 2, 8

Off Isolation, Input-Output f = 10 MHz, R

Input Voltage Noise 0.01 MHz to 50 MHz 15 nV/√Hz TPC 14, 20

DC PERFORMANCE

Gain Error R

= 1 kΩ 0.04/0.1 0.07/0.5 %

L

R

= 150 Ω 0.15/0.25 %

L

Gain Matching No Load, Channel-Channel 0.02/1.0 %

= 1 kΩ, Channel-Channel 0.09/1.0 %

R

L

Gain Temperature Coefficient 0.5/8 ppm/°C

OUTPUT CHARACTERISTICS

Output Impedance DC, Enabled 0.2 Ω TPC 18, 24

Disabled 10/0.001 MΩ TPC 15, 21

Output Disable Capacitance Disabled 2 pF

Output Leakage Current Disabled, AD8108 Only 1/NA µA

Output Voltage Range No Load ±2.5 ± 3V

Output Current 20 40 mA

Short Circuit Current 65 mA

INPUT CHARACTERISTICS

Input Offset Voltage Worst Case (All Configurations) 5 20 mV TPC 29, 35

Temperature Coefficient 12 µV/°C TPC 30, 36

Input Voltage Range ±2.5/±1.25 ±3/±1.5 V

Input Capacitance Any Switch Configuration 2.5 pF

Input Resistance 1 10 MΩ

Input Bias Current Per Output Selected 2 5 µA

SWITCHING CHARACTERISTICS

Enable On Time 60 ns

Switching Time, 2 V Step 50% UPDATE to 1% Settling 25 ns

Switching Transient (Glitch) Measured at Output 20/30 mV p-p TPC 16, 22

POWER SUPPLIES

Supply Current AVCC, Outputs Enabled, No Load 33 mA

AVCC, Outputs Disabled 10 mA

AVEE, Outputs Enabled, No Load 33 mA

AVEE, Outputs Disabled 10 mA

DVCC 10 mA

Supply Voltage Range ±4.5 to ±5.5 V

PSRR f = 100 kHz 73/78 dB TPC 13, 19

f = 1 MHz 55/58 dB

OPERATING TEMPERATURE RANGE

Temperature Range Operating (Still Air) –40 to +85 °C

θ

JA

Specifications subject to change without notice.

Operating (Still Air) 48 °C/W

= 150 Ω 240/150 325/250 MHz TPC 1, 7

L

= 150 Ω 140/160 MHz TPC 1, 7

L

= 150 Ω 5ns

L

= 150 Ω 400/480 V/µs

L

= 150 Ω 40 ns TPC 6, 12

L

= 150 Ω 60/50 MHz TPC 1, 7

L

= 150 Ω 60/50 MHz TPC 1, 7

L

= 150 Ω 70/65 MHz TPC 1, 7

L

= 1 kΩ 0.01 %

L

= 150 Ω 0.02 %

L

= 1 kΩ 0.01 Degrees

L

= 150 Ω 0.02 Degrees

L

=150 Ω, One Channel 93/98 dB TPC 17, 23

L

–2–

REV. A

AD8108/AD8109

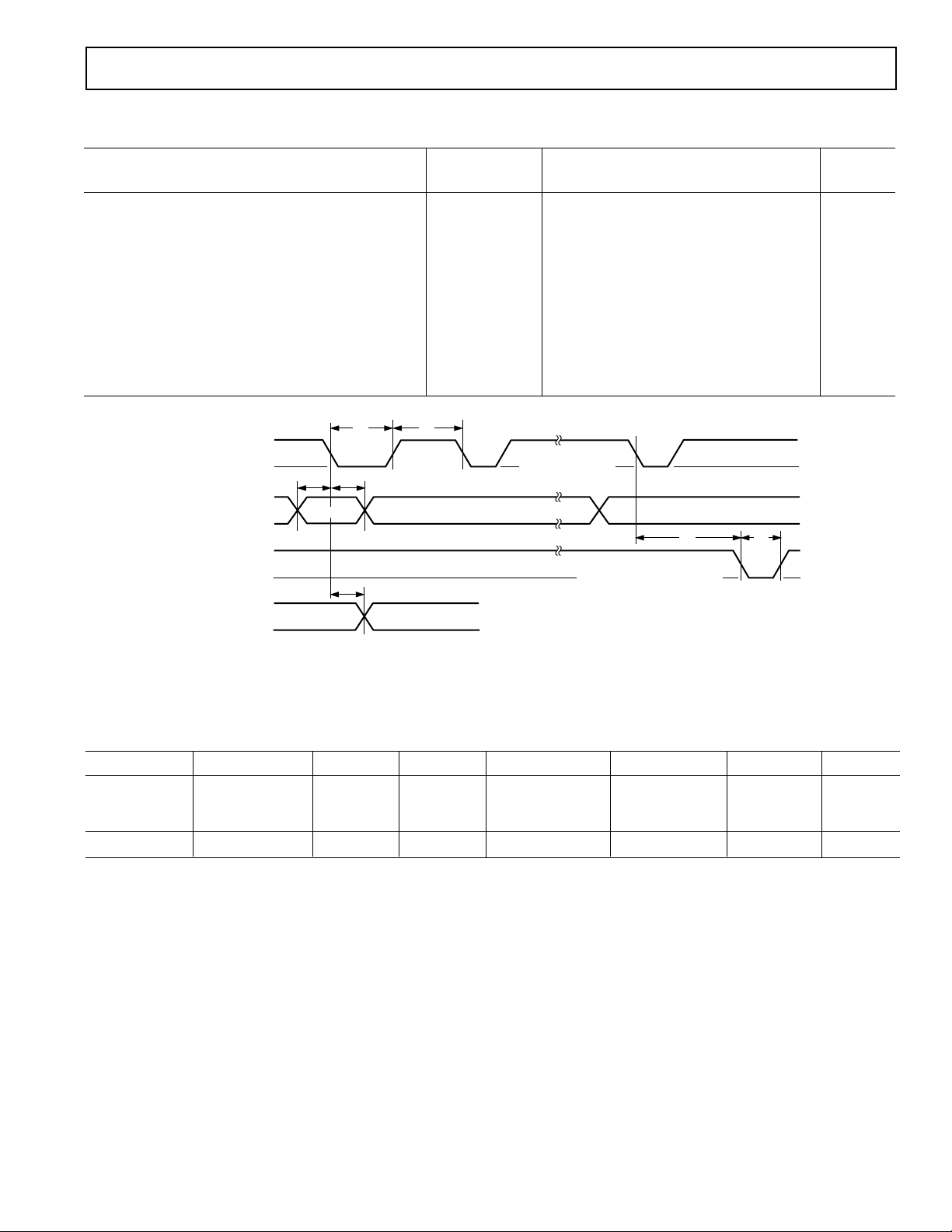

TIMING CHARACTERISTICS (Serial)

Limit

Parameter Symbol Min Typ Max Unit

Serial Data Setup Time t

CLK Pulsewidth t

Serial Data Hold Time t

CLK Pulse Separation, Serial Mode t

CLK to UPDATE Delay t

UPDATE Pulsewidth t

CLK to DATA OUT Valid, Serial Mode t

1

2

3

4

5

6

7

20 ns

100 ns

20 ns

100 ns

0ns

50 ns

180 ns

Propagation Delay, UPDATE to Switch On or Off – 8 ns

Data Load Time, CLK = 5 MHz, Serial Mode – 6.4 µs

CLK, UPDATE Rise and Fall Times – 100 ns

RESET Time – 200 ns

CLK

DATA IN

1 = LATCHED

UPDATE

0 = TRANSPARENT

DATA OUT

t

1

0

t

1

1

OUT7 (D3)

0

2

t

3

t

7

t

4

LOAD DATA INTO

SERIAL REGISTER

ON FALLING EDGE

OUT7 (D2) OUT00 (D0)

TRANSFER DATA FROM SERIAL

REGISTER TO PARALLEL

LATCHES DURING LOW LEVEL

t

5

t

6

Figure 1. Timing Diagram, Serial Mode

Table I. Logic Levels

V

IH

RESET, SER/PAR RESET, SER/PAR RESET, SER/PAR RESET, SER/PAR

CLK, DATA IN, CLK, DATA IN, CLK, DATA IN, CLK, DATA IN,

CE, UPDATE CE, UPDATE DATA OUT DATA OUT CE, UPDATE CE, UPDATE DATA OUT DATA OUT

2.0 V min 0.8 V max 2.7 V min 0.5 V max 20 µA max –400 µA min –400 µA max 3.0 mA min

V

IL

V

OH

V

OL

I

IH

I

IL

I

OH

I

OL

–3–REV. A

AD8108/AD8109

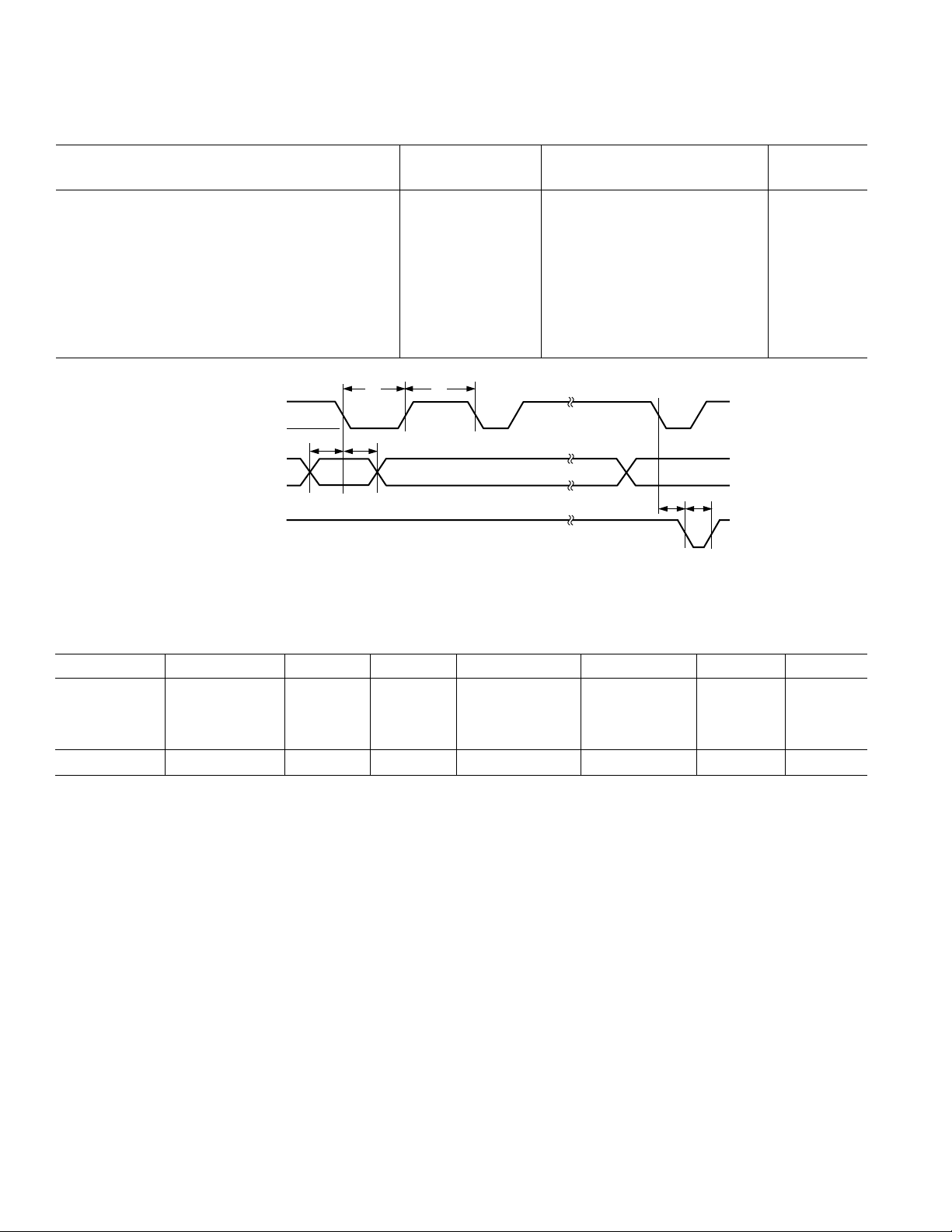

TIMING CHARACTERISTICS (Parallel)

Limit

Parameter Symbol Min Max Unit

Data Setup Time t

CLK Pulsewidth t

Data Hold Time t

CLK Pulse Separation t

CLK to UPDATE Delay t

UPDATE Pulsewidth t

1

2

3

4

5

6

20 ns

100 ns

20 ns

100 ns

0ns

50 ns

Propagation Delay, UPDATE to Switch On or Off – 8 ns

CLK, UPDATE Rise and Fall Times – 100 ns

RESET Time – 200 ns

CLK

D0–D3

A0–A2

1 = LATCHED

UPDATE

0 = TRANSPARENT

t

1

0

t

1

1

0

2

t

3

t

4

t6t

5

Figure 2. Timing Diagram, Parallel Mode

Table II. Logic Levels

V

IH

V

IL

V

OH

V

OL

I

IH

I

IL

I

OH

I

OL

RESET, SER/PAR RESET, SER/PAR RESET, SER/PAR RESET, SER/PAR

CLK, D0, D1, D2, CLK, D0, D1, D2, CLK, D0, D1, D2, CLK, D0, D1, D2,

D3, A0, A1, A2 D3, A0, A1, A2 D3, A0, A1, A2 D3, A0, A1, A2

CE, UPDATE CE, UPDATE DATA OUT DATA OUT CE, UPDATE CE, UPDATE DATA OUT DATA OUT

2.0 V min 0.8 V max 2.7 V min 0.5 V max 20 µA max –400 µA min –400 µA max 3.0 mA min

–4–

REV. A

AD8108/AD8109

AMBIENT TEMPERATURE – C

5.0

MAXIMUM POWER DISSIPATION – W

4.0

0

–50 80–40 –30 –20 –100 10203040506070

3.0

2.0

1.0

TJ = 150C

90

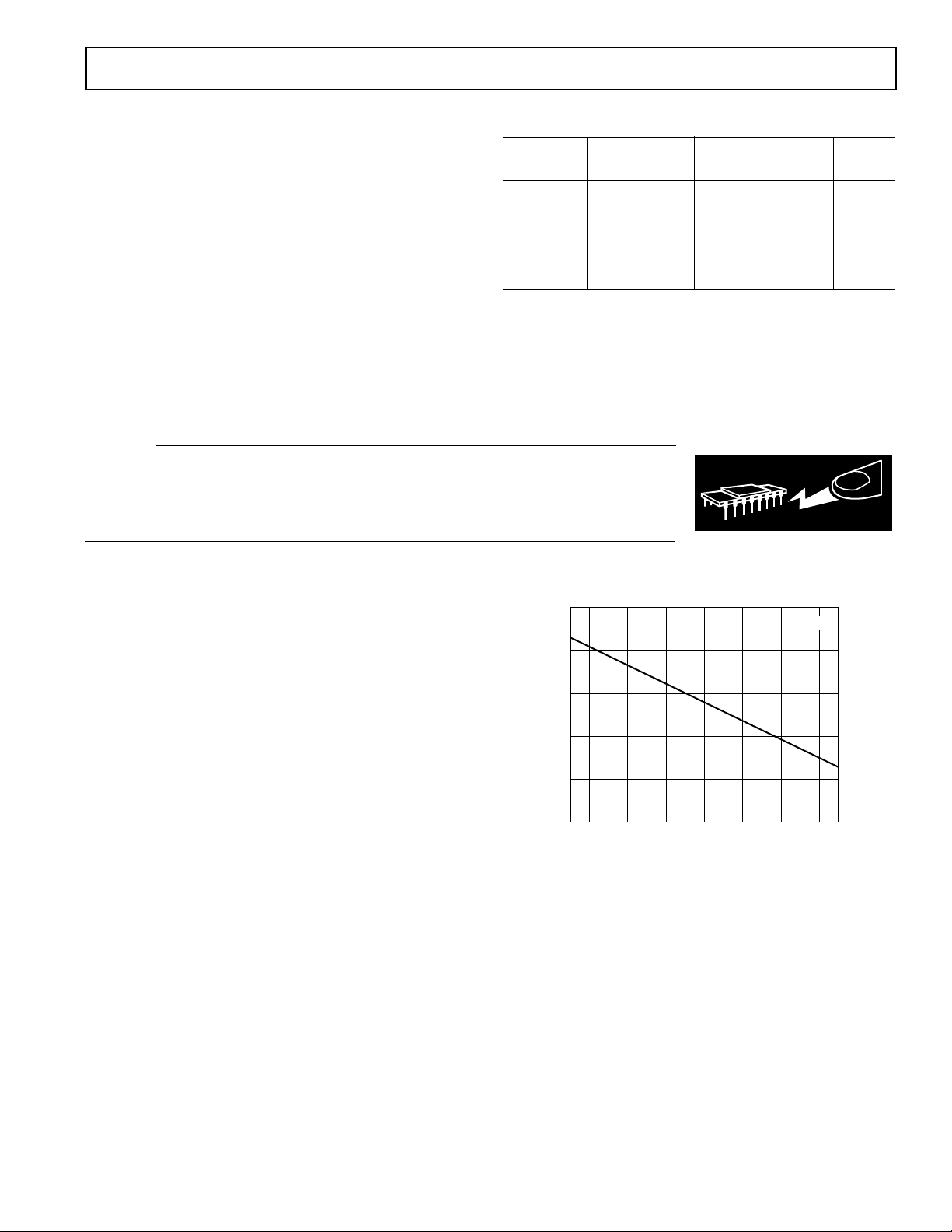

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12.0 V

Internal Power Dissipation

2

1

AD8108/AD8109 80-Lead Plastic LQFP (ST) . . . . . 2.6 W

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±V

S

Output Short Circuit Duration

. . . . . . . . . . . . . . . . . . . . . . . Observe Power Derating Curves

Storage Temperature Range . . . . . . . . . . . . –65°C to +125°C

Lead Temperature Range (Soldering 10 sec) . . . . . . . . . 300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Specification is for device in free air (TA = 25°C):

80-lead plastic LQFP (ST): θJA = 48°C/W.

Model Range Description Option

AD8108AST –40°C to +85°C 80-Lead Plastic LQFP ST-80A

AD8109AST –40°C to +85°C 80-Lead Plastic LQFP ST-80A

AD8108-EB Evaluation Board

AD8109-EB Evaluation Board

ORDERING GUIDE

Temperature Package Package

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD8108/AD8109 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper

ESD precautions are recommended to avoid performance degradation or loss of functionality.

(12 mm × 12 mm)

(12 mm × 12 mm)

WARNING!

ESD SENSITIVE DEVICE

MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the

AD8108/AD8109 is limited by the associated rise in junction

temperature. The maximum safe junction temperature for plastic

encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Temporarily

exceeding this limit may cause a shift in parametric performance

due to a change in the stresses exerted on the die by the package.

Exceeding a junction temperature of 175°C for an extended

period can result in device failure.

While the AD8108/AD8109 is internally short circuit protected,

this may not be sufficient to guarantee that the maximum junction

temperature (150°C) is not exceeded under all conditions. To

ensure proper operation, it is necessary to observe the maximum

power derating curves shown in Figure 3.

Figure 3. Maximum Power Dissipation vs. Temperature

–5–REV. A

AD8108/AD8109

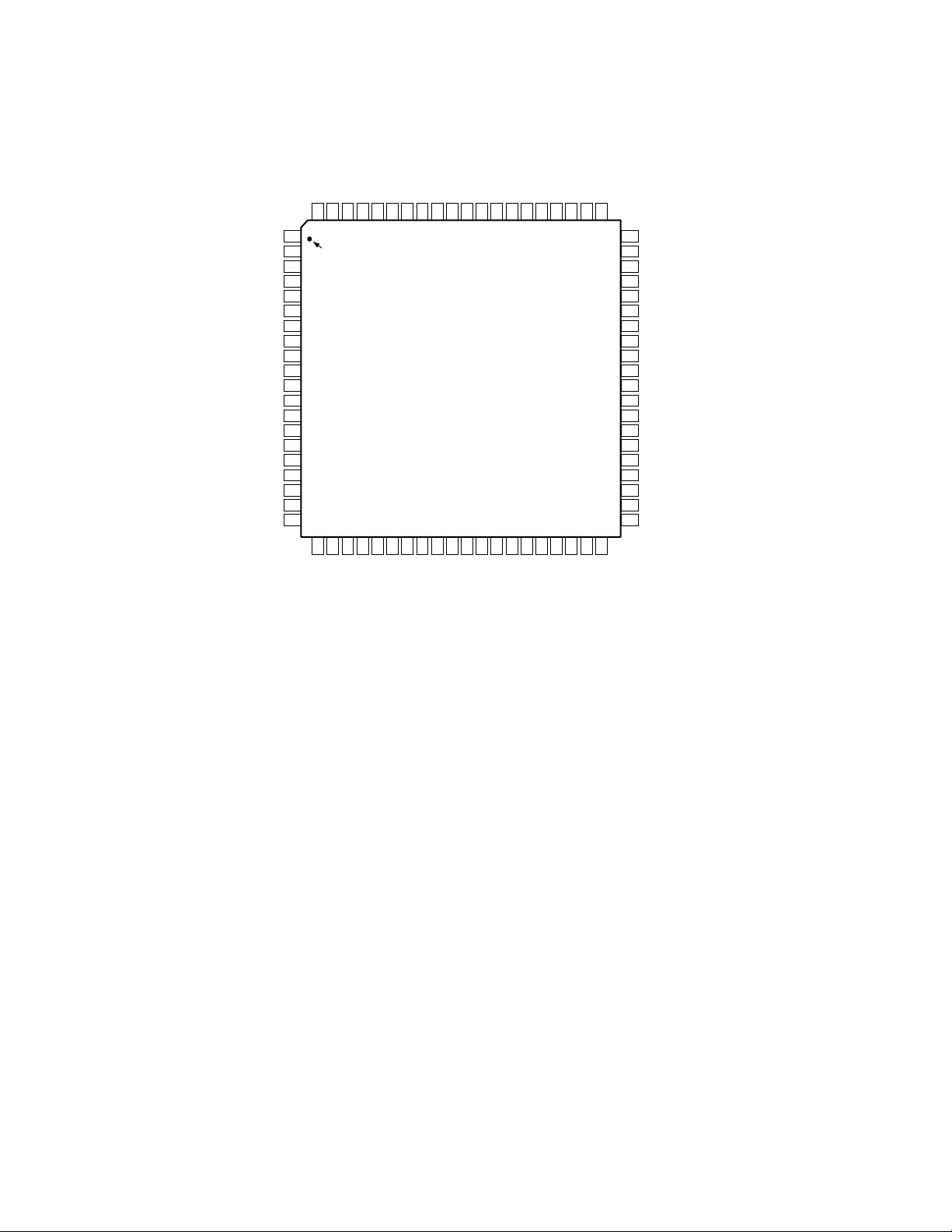

PIN CONFIGURATION

1

IN00

2

AGND

3

IN01

4

AGND

5

IN02

6

AGND

7

IN03

8

AGND

9

IN04

10

AGND

11

IN05

12

AGND

13

IN06

14

AGND

15

IN07

16

AGND

17

AVEE

18

AVCC

19

AVCC07

20

OUT07

NC = NO CONNECT

NC

NC

NC

NC

NC

DVCC

DGND

80

79787776757473727170696867

PIN 1

IDENTIFIER

NC

NC

NC

NC

AD8108/AD8109

TOP VIEW

(Not to Scale)

22

23

21

AGND07

AVEE06/07

24

OUT06

AGND06

25

26

OUT05

AVCC05/06

27

28

AGND05

AVEE04/05

30

29

OUT04

AGND04

31

AVCC03/04

NC

NC

33

32

OUT03

AGND03

NC

NC

NC

66

656463

35

36

34

OUT02

AGND02

AVEE02/03

DGND

DVCC

NC

62

37

38

39

OUT01

AGND01

AVCC01/02

RESET

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

AVEE00/01

CE

DATA OUT

CLK

DATA IN

UPDATE

SER/PAR

A0

A1

A2

D0

D1

D2

D3

NC

AGND

AVEE

AVCC

AVCC00

AGND00

OUT00

–6–

REV. A

AD8108/AD8109

PIN FUNCTION DESCRIPTIONS

Pin Name Pin Numbers Pin Description

INxx 1, 3, 5, 7, 9, 11, 13, 15 Analog Inputs; xx = Channel Numbers 00 Through 07.

DATA IN 57 Serial Data Input, TTL Compatible.

CLK 58 Clock, TTL Compatible. Falling Edge Triggered.

DATA OUT 59 Serial Data Output, TTL Compatible.

UPDATE 56 Enable (Transparent) “Low.” Allows serial register to connect directly to switch

matrix. Data latched when “High.”

RESET 61 Disable Outputs, Active “Low.”

CE 60 Chip Enable, Enable “Low.” Must be “low” to clock in and latch data.

SER/PAR 55 Selects Serial Data Mode, “Low” or Parallel Data Mode, “High.” Must be connected.

OUTyy 41, 38, 35, 32, 29, 26, 23, 20 Analog Outputs yy = Channel Numbers 00 Through 07.

AGND 2, 4, 6, 8, 10, 12, 14, 16, 46 Analog Ground for Inputs and Switch Matrix.

DVCC 63, 79 5 V for Digital Circuitry

DGND 62, 80 Ground for Digital Circuitry

AVEE 17, 45 –5 V for Inputs and Switch Matrix.

AVCC 18, 44 +5 V for Inputs and Switch Matrix.

AGNDxx 42, 39, 36, 33, 30, 27, 24, 21 Ground for Output Amp, xx = Output Channel Numbers 00 Through 07. Must be connected.

AVCCxx/yy 43, 37, 31, 25, 22, 19 +5 V for Output Amplifier that is shared by Channel Numbers xx and yy. Must be connected.

AVEExx/yy 40, 34, 28, 22 –5 V for Output Amplifier that is shared by Channel Numbers xx and yy. Must be connected.

A0 54 Parallel Data Input, TTL Compatible (Output Select LSB).

A1 53 Parallel Data Input, TTL Compatible (Output Select).

A2 52 Parallel Data Input, TTL Compatible (Output Select MSB).

D0 51 Parallel Data Input, TTL Compatible (Input Select LSB).

D1 50 Parallel Data Input, TTL Compatible (Input Select).

D2 49 Parallel Data Input, TTL Compatible (Input Select MSB).

D3 48 Parallel Data Input, TTL Compatible (Output Enable).

NC 47, 64–78 No Connect.

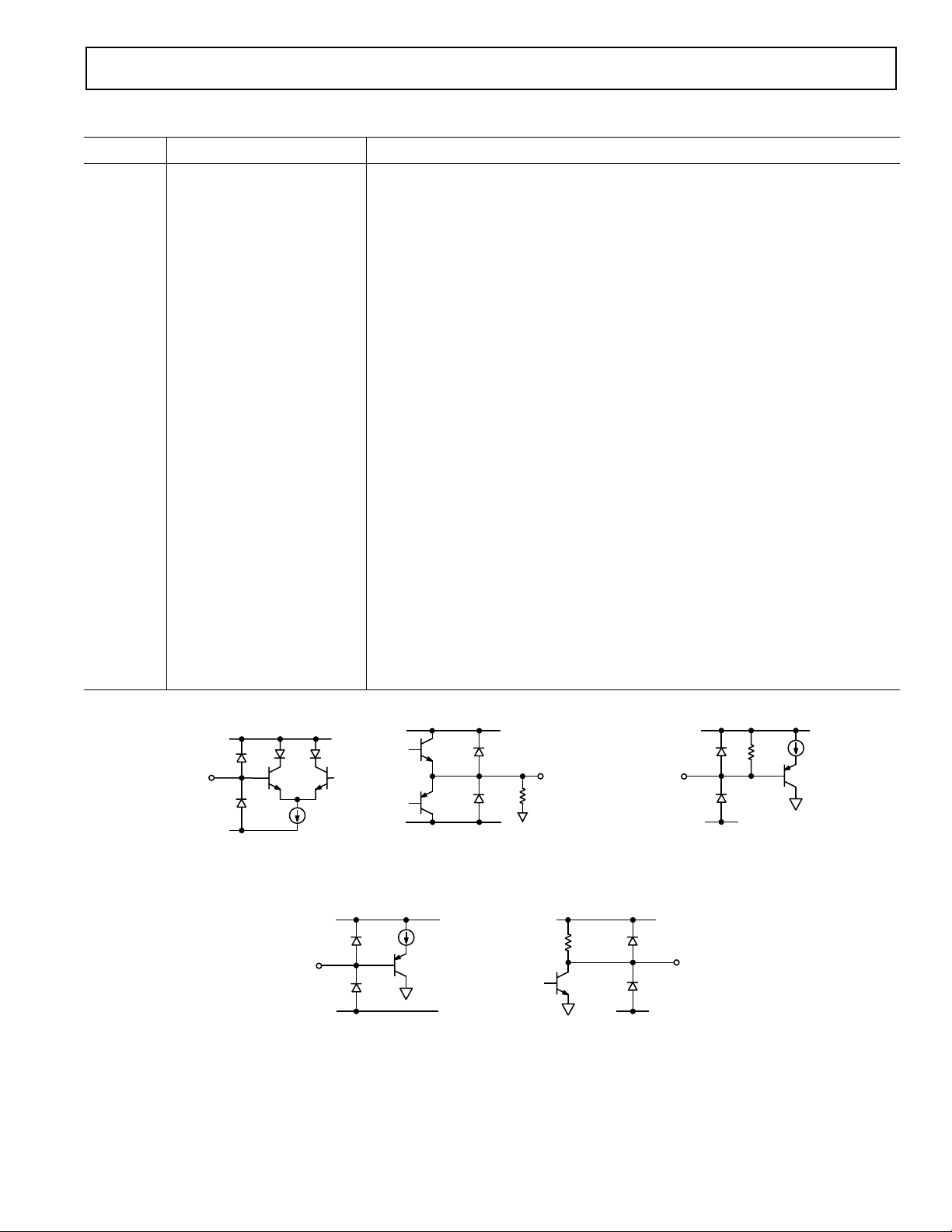

V

CC

AVEE

INPUT

ESD

ESD

V

CC

AVEE

a. Analog Input c. Reset Inputb. Analog Output

V

CC

ESD

INPUT

ESD

DGND

d. Logic Input e. Logic Output

Figure 5. I/O Schematics

ESD

ESD

OUTPUT

1k

(AD8109 ONLY)

2k

V

CC

DGND

RESET

ESD

ESD

V

CC

ESD

ESD

OUTPUT

20k

DGND

–7–REV. A

AD8108/AD8109

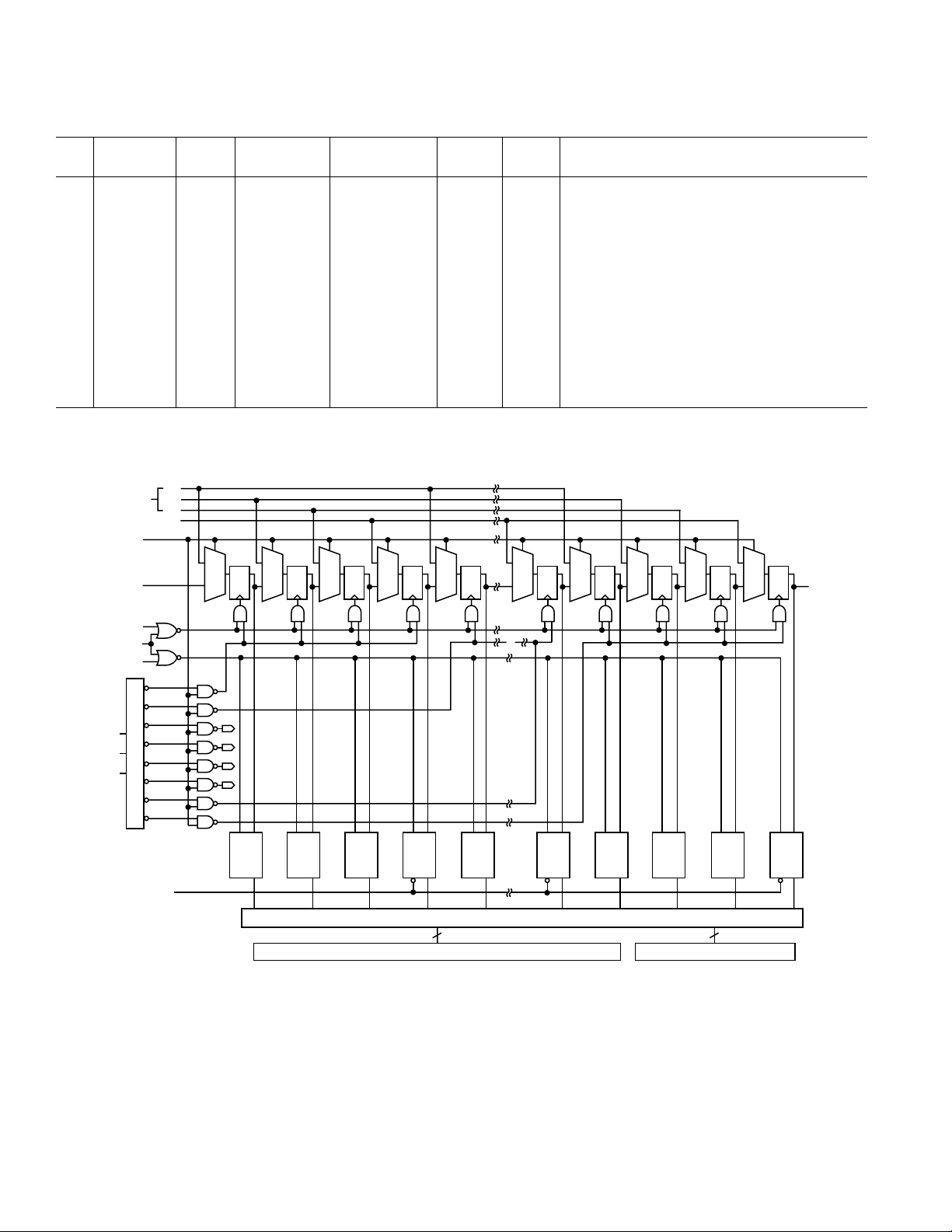

Table III. Operation Truth Table

SER/

CE UPDATE CLK DATA IN DATA OUT RESET PAR Operation/Comment

1 X X X X X X No change in logic.

01 f Data

i

01 f D0 . . . D3, NA in Parallel 1 1 The data on the parallel data lines, D0–D3, are

A0...A2 Mode loaded into the 32-bit serial shift register loca-

0 0 X X X 1 X Data in the 32-bit shift register transfers into the

X X X X X 0 X Asynchronous operation. All outputs are disabled.

D0

PARALLEL DATA

(OUTPUT ENABLE)

SER/PAR

DATA IN

(SERIAL)

D1

D2

D3

S

D1

Q

D0

D

CLK

S

D1

Q

DQ

Q

D0

CLK

D1

D0

S

Q

Data

DQ

CLK

i-32

1 0 The data on the serial DATA IN line is loaded

into serial register. The first bit clocked into

the serial register appears at DATA OUT 32

clocks later.

tion addressed by A0–A2.

parallel latches that control the switch array.

Latches are transparent.

Remainder of logic is unchanged.

S

D1

Q

D0

DQ

CLK

S

D1

DQ

Q

D0

CLK

S

D1

Q

D0

DQ

CLK

S

D1

Q

D0

DQ

CLK

S

D1

Q

D0

DQ

CLK

S

D1

Q

D0

DQ

CLK

S

D1

Q

Q

D

CLK

DATA

OUT

D0

CLK

CE

UPDATE

OUT0 EN

OUT1 EN

OUT2 EN

A0

OUT3 EN

A1

OUT4 EN

A2

OUT5 EN

3 TO 8 DECODER

OUT6 EN

OUT7 EN

(OUTPUT ENABLE)

RESET

LE

OUT0

LE

OUT0

B1

D

Q

D

B0

Q

LE

OUT0

B2

D

Q

LE

OUT0

EN

D

QCLR

LE

OUT1

B0

D

Q

LE

OUT6

EN

D

QCLR

LE

OUT7

B0

D

Q

LE

OUT7

D

B1

Q

LE

OUT7

D

B2

Q

LE

OUT7

EN

D

QCLR

DECODE

64

8

OUTPUT ENABLESWITCH MATRIX

Figure 4. Logic Diagram

–8–

REV. A

+1.0V

+0.5V

0

–0.5V

–1.0V

500mV/DIV

10ns/DIV

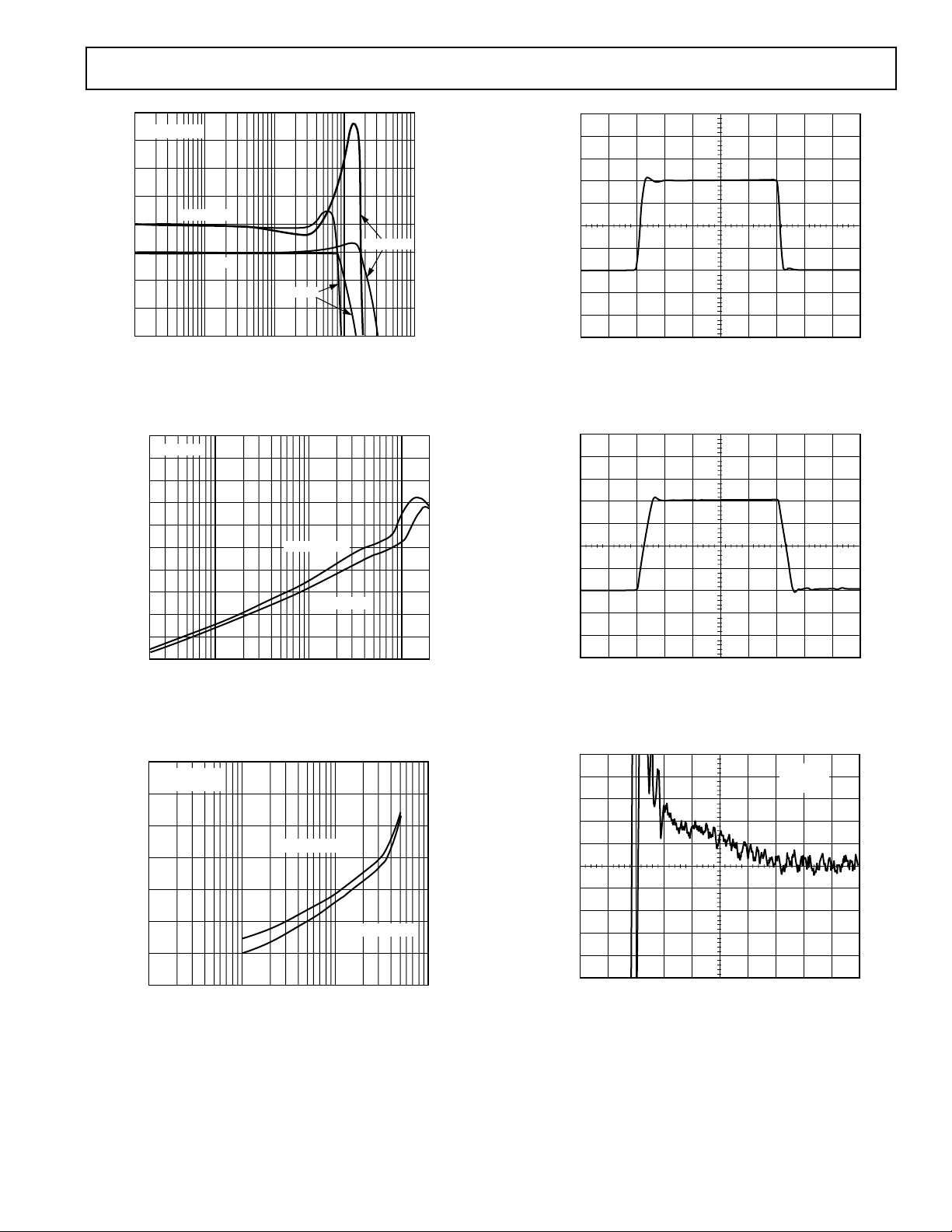

Typical Performance Characteristics—

AD8108/AD8109

5

RL = 150

4

3

2

1

GAIN – dB

0

–1

–2

–3

100k 1M 1G

FLATNESS

GAIN

2V p-p

10M 100M

FREQUENCY – Hz

200mV p-p

TPC 1. AD8108 Frequency Response

–10

RL = 1k

–20

–30

–40

–50

–60

–70

CROSSTALK – dB

–80

–90

–100

–110

0.2 1 20010 100

ALL HOSTILE

ADJACENT

FREQUENCY – MHz

TPC 2. AD8108 Crosstalk vs. Frequency

0.4

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

–0.4

FLATNESS – dB

+50mV

+25mV

0

25mV/DIV

–25mV

–50mV

10ns/DIV

TPC 4. AD8108 Step Response, 100 mV Step

TPC 5. AD8108 Step Response, 2 V Step

–30

RL = 150

V

= 2V p-p

OUT

–40

–50

–60

–70

DISTORTION – dB

–80

–90

–100

100k 1M 10M 100M

2ND HARMONIC

3RD HARMONIC

FREQUENCY – Hz

TPC 3. AD8108 Distortion vs. Frequency

2V STEP

= 150

R

L

0.2

0.1

0

0.1%/DIV

–0.1

–0.2

0 10203040 50607080

10ns/DIV

TPC 6. AD8108 Settling Time

–9–REV. A

Loading...

Loading...