Analog Devices AD809BR-REEL7, AD809BR Datasheet

a

155.52 MHz Frequency Synthesizer

AD809

FEATURES

Frequency Synthesis to 155.52 MHz

19.44 MHz or 9.72 MHz Input

Reference Signal Select Mux

Single Supply Operation: +5 V or –5.2 V

Output Jitter: 2.0 Degrees RMS

Low Power: 90 mW

10 KH ECL/PECL Compatible Output

10 KH ECL/PECL/TTL/CMOS Compatible Input

Package: 16-Pin Narrow 150 Mil SOIC

PRODUCT DESCRIPTION

The AD809 provides a 155.52 MHz ECL/PECL output clock from

either a 19.44 MHz or a 9.72 MHz TTL/CMOS/ECL/PECL reference frequency. The AD809 functionality supports a distributed

timing architecture, allowing a backplane or PCB 19.44 MHz or

9.72 MHz timing reference signal to be distributed to multiple

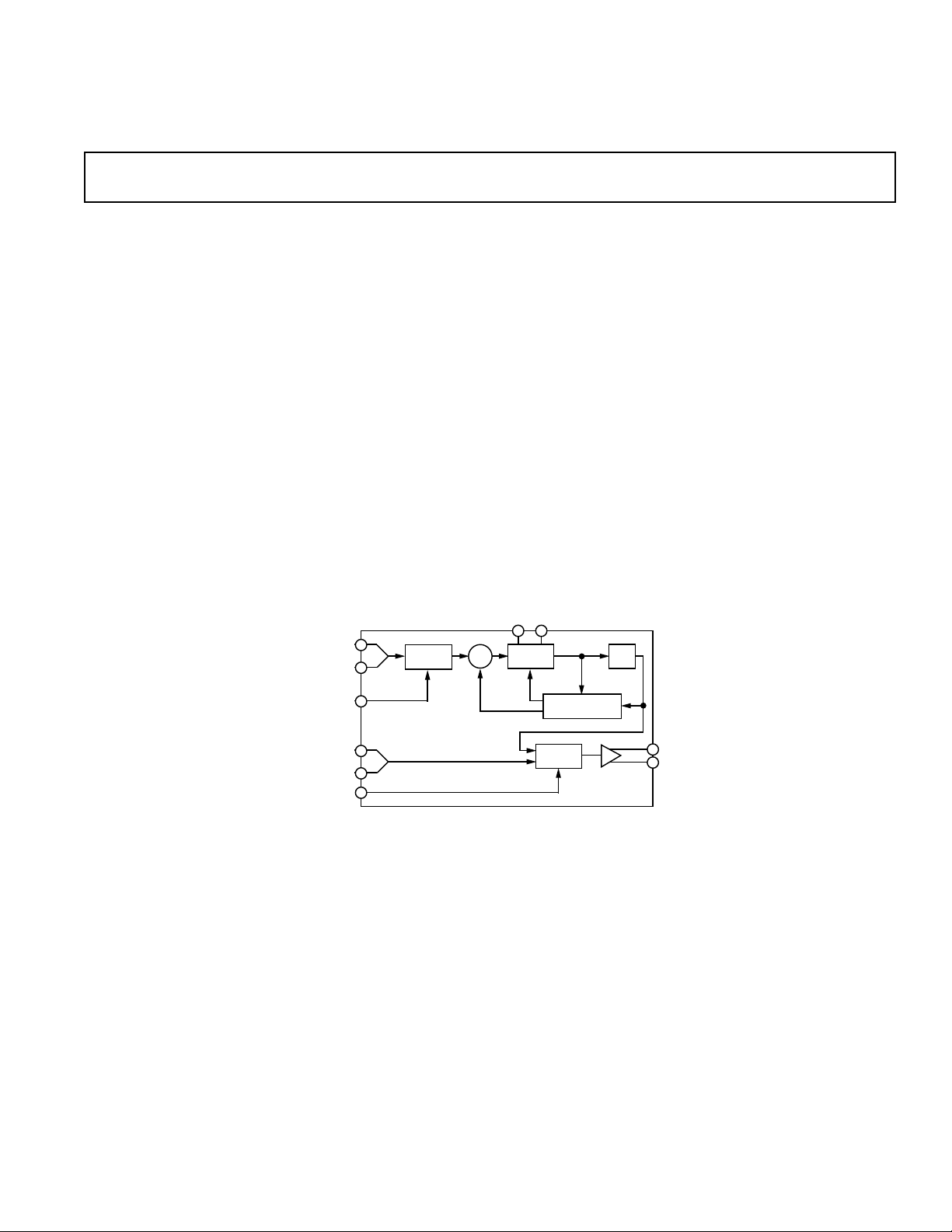

FUNCTIONAL BLOCK DIAGRAM

CLKIN

CLKINN

PECLIN

PECLINN

MUX

13

12

10

2

1

15

AUTO

SELECT

AD809

PFD

(19.44MHz

OR

9.72MHz)

TTL/CMOSIN

(155MHz)

155.52 Mbps ports. The AD809 can be applied to create the transmit bit clock for one or more ports.

An input signal multiplexer supports loop-timed applications

where a 155.52 MHz transmit bit clock is recovered from the

155.52 Mbps received data.

The low jitter VCO, low power and wide operating temperature

range make the device suitable for generating a 155.52 MHz bit

clock for SONET/SDH/Fiber in the Loop systems.

The device has a low cost, on-chip VCO that locks to either

8× or 16× the frequency at the 19.44 MHz or 9.72 MHz input.

No external components are needed for frequency synthesis; however, the user can adjust loop dynamics through selection of a

damping factor capacitor whose value determines loop damping.

The AD809 design guarantees that the clock output frequency

will drift low (by roughly 20%) in the absence of a signal at the

input.

The AD809 consumes 90 mW and operates from a single power

supply at either +5 V or –5.2 V.

CF1 CF2

8

7

LOOP

FILTER

BW

ADJUST

AUTO SELECT

DIVIDE BY 8/16

MUX

VCO

5

CLKOUT

4

CLKOUTN

(155MHz

PECL

OUTPUT)

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1997

AD809–SPECIFICATIONS

(TA = T

MIN

to T

MAX

, VS = V

MIN

to V

, CD = 22 nF, unless otherwise noted)

MAX

Parameter Condition Min Typ Max Units

TRACKING AND CAPTURE RANGE

1

×8 Synthesis 19.42 19.46 MHz

×16 Synthesis 9.71 9.73 MHz

OUTPUT JITTER ×8 Synthesis 1.6 2.9 Degrees RMS

×16 Synthesis 1.6 2.9 Degrees RMS

JITTER TRANSFER

Bandwidth 200 kHz

Peaking C

= 5.6 nF (ζ = 5) 0.08 dB

D

C

= 22 nF (ζ = 10) 0.02 dB

D

DUTY CYCLE TOLERANCE ×8 or ×16 Synthesis

Output Jitter ≤ 2.9 Degrees RMS 15 85 %

INPUT VOLTAGE LEVELS

PECL

Input Logic High, V

Input Logic Low, V

IL

IH

@ CLKIN/N and 3.8 V

CC

Volts

PECLIN/N Inputs 3.1 3.6 Volts

TTL

Input Logic High, V

Input Logic Low, V

IH

IL

OUTPUT VOLTAGE LEVELS Referenced to V

@ TTL/CMOSIN 2.0 Volts

and MUX Inputs 0.8 Volts

CC

PECL

Output Logic High, V

Output Logic Low, V

OL

OH

–1.2 –1.0 –0.7 Volts

–2.0 –1.8 –1.7 Volts

SYMMETRY (Duty Cycle) ×8 Synthesis or 46 52 62 %

×16 Synthesis %

OUTPUT RISE/FALL TIMES 1.5

Rise Time (t

) 20%–80% 1.1 1.5 ns

R

Fall Time (tF) 80%–20% 1.1 1.5 ns

POWER SUPPLY VOLTAGE V

MIN

to V

MAX

4.5 5.5 Volts

POWER SUPPLY CURRENT 17 26 mA

OPERATING TEMPERATURE RANGE T

NOTES

1

Device design is guaranteed for operation over Capture Ranges and Tracking Ranges, however the device has wider capture and tracking ranges

(for both ×8 and ×16 synthesis).

Specifications subject to change without notice.

MIN

to T

MAX

–40 +85 °C

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +12 V

Input Voltage (Pin 12 or Pin 13) . . . . . . . . . . . . . . V

+ 0.6 V

CC

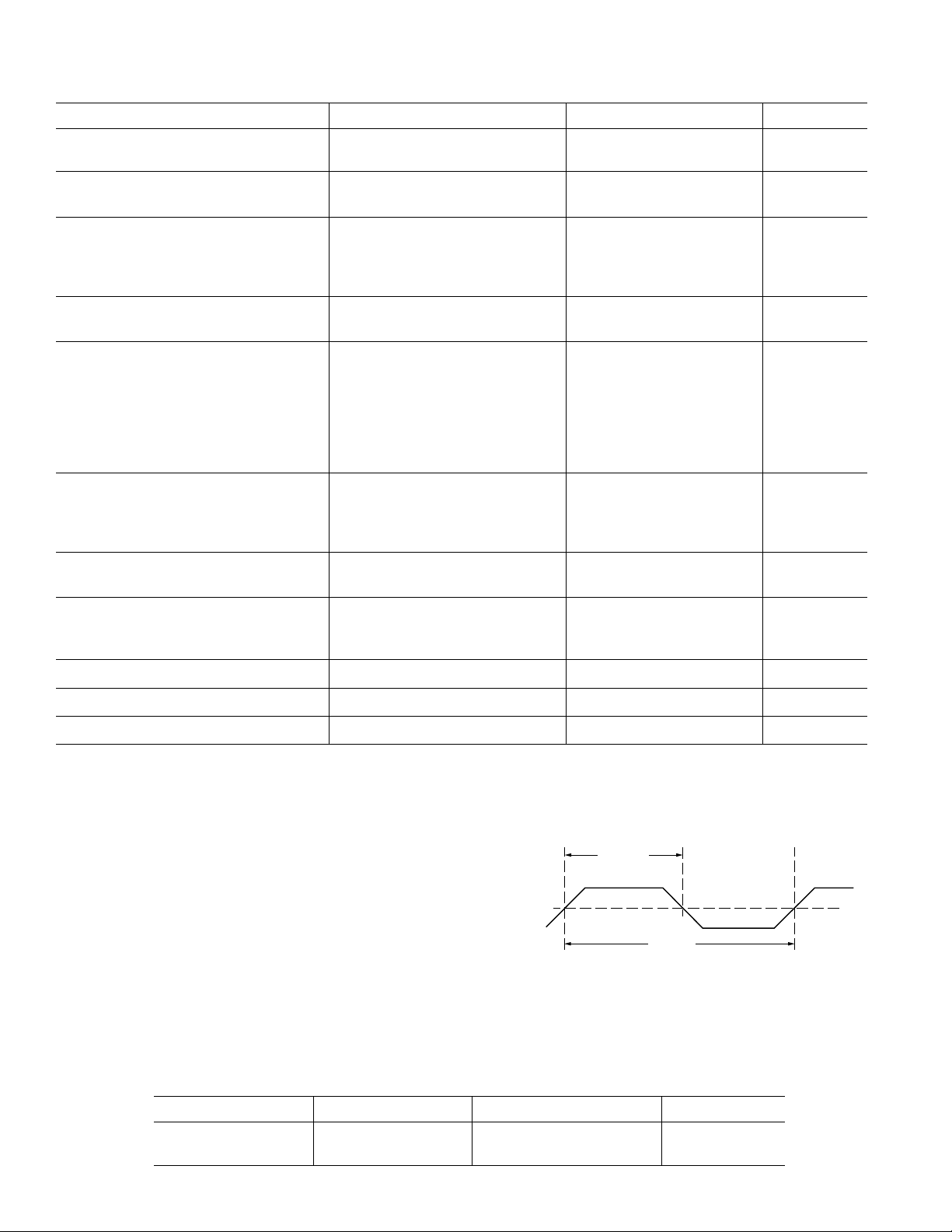

“ON” TIME

t

ON

Maximum Junction Temperature. . . . . . . . . . . . . . . . . +165°C

Storage Temperature Range . . . . . . . . . . . . .–65°C to +150°C

Lead Temperature Range (Soldering 10 sec) . . . . . . . . +300°C

ESD Rating (Human Body Model) . . . . . . . . . . . . . . . .1500 V

*Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

Thermal Characteristics:

16-Pin Narrow Body SOIC Package: θJA = 110°C/W.

OUTPUT 50%

(PINS 4 & 5)

PERIOD

SYMMETRY = (100 ×

τ

t

/τ)

ON

Figure 1. Symmetry

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD809BR –40°C to +85°C 16-Pin Narrow Body SOIC R-16A

AD809BR-REEL7 –40°C to +85°C 750 Pieces, 7" Reel R-16A

–2–

REV. A

AD809

WARNING!

ESD SENSITIVE DEVICE

PIN DESCRIPTIONS

Pin

No. Mnemonic Description

1 PECLINN Differential 155 MHz Input

2 PECLIN Differential 155 MHz Input

3V

CC2

Digital VCC for PECL Outputs

4 CLKOUTN Differential 155 MHz Output

5 CLKOUT Differential 155 MHz Output

6V

CC1

Digital VCC for Internal Logic

7 CF1 Loop Damping Capacitor

8 CF2 Loop Damping Capacitor

9AV

EE

Analog V

EE

10 TTL/CMOSIN TTL/CMOS Reference Clock Input

11 AV

CC1

Analog VCC for PLL

12 CLKINN PECL Differential Reference Clock Input

13 CLKIN PECL Differential Reference Clock Input

14 AV

CC2

Analog VCC for Input Stage

15 MUX Input Signal Mux Control Input

16 V

EE

Digital V

EE

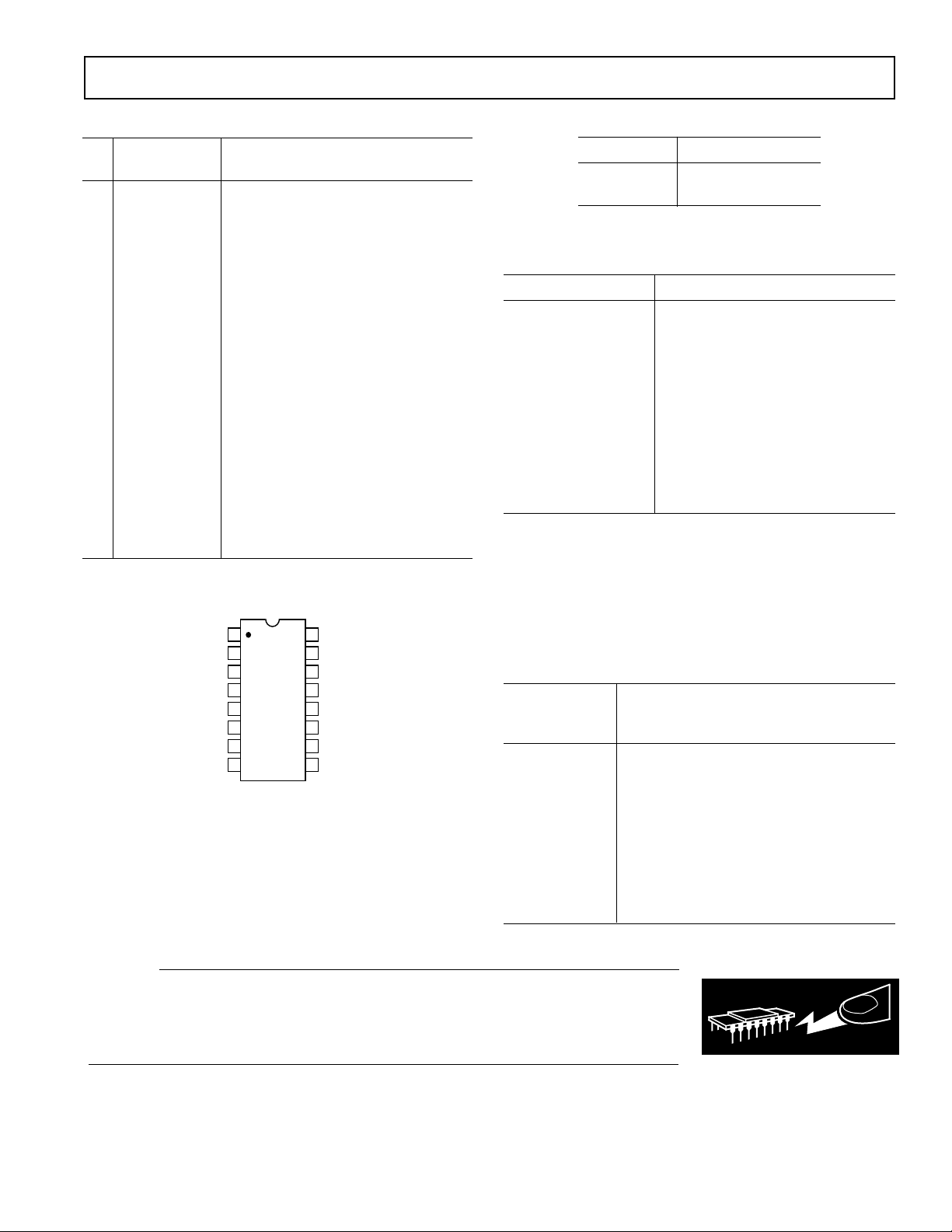

PIN CONFIGURATION

PECLINN

PECLIN

V

CC2

CLKOUTN

CLKOUT

V

CC1

CF1

CF2

1

2

3

AD809

4

TOP VIEW

5

(Not to Scale)

6

7

8

V

16

EE

MUX

15

AV

14

CLKIN

13

12

CLKINN

AV

11

TTL/CMOSIN

10

AV

9

CC2

CC1

EE

Table I.

MUX Input Input Selected

TTL “0” CLKIN/CLKINN

TTL “1” PECLIN/PECLINN

Table II. Applying a PECL/ECL or CMOS/TTL Reference

Input to the AD809

Input Reference AD809 Configuration

PECL/ECL Differential Apply the valid PECL–level reference

frequency to Pins 13 and 12.

AD809 frequency synthesizer ignores

the input at Pin 10.

TTL/CMOS Apply the reference frequency to

Single-Ended Pin 10.

Connect Pins 13 and 12 to AV

EE

(Pins 9 and 16). The AD809 senses

the common-mode signal at these pins

as less than valid PECL and selects the

TTL/CMOS input as active.

AD809 Phase Skew

The AD809 output is in phase with the input. The falling edge

at Pin 4, CLKOUTN, occurs 700 ps before the rising edge at

Pin 10, TTL/CMOSIN at 27°C. The phase skew remains relatively constant over temperature. Refer to Table III for phase

skew data.

Table III. Phase Skew vs. Temperature

Skew (CLKOUTN, Pin 4, Relative to

Temperature TTL/CMOSIN, Pin 10 Measured in

(8C) ps at Package Pins)

–35 –1000

–20 –950

0 –850

10 –750

30 –700

50 –600

70 –450

80 –450

90 –350

100 –250

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD809 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. A

–3–

Loading...

Loading...