Low Noise, High Speed Amplifier

www.BDTIC.com/ADI

FEATURES

Low noise

2.1 nV/√Hz input voltage noise

2.1 pA/√Hz input current noise

Custom compensation

Constant bandwidth from G = −1 to G = −10

High speed

200 MHz (G = −1)

190 MHz (G = −10)

Low power

34 mW or 6.7 mA typical for 5 V supply

Output disable feature, 1.3 mA

Low distortion

−93 dBc second harmonic, f

−108 dBc third harmonic, f

DC precision

1 mV maximum input offset voltage

0.5 μV/°C input offset voltage drift

Wide supply range, 5 V to 24 V

Low price

Small packaging

Available in SOIC-8 and MSOP-8

APPLICATIONS

ADC preamps and drivers

Instrumentation preamps

Active filters

Portable instrumentation

Line receivers

Precision instruments

Ultrasound signal processing

High gain circuits

GENERAL DESCRIPTION

The AD8021 is an exceptionally high performance, high speed

voltage feedback amplifier that can be used in 16-bit resolution

systems. It is designed to have both low voltage and low current

noise (2.1 nV/√Hz typical and 2.1 pA/√Hz typical) while operating

at the lowest quiescent supply current (7 mA @ ±5 V) among

today’s high speed, low noise op amps. The AD8021 operates

over a wide range of supply voltages from ±2.25 V to ±12 V, as

well as from single 5 V supplies, making it ideal for high speed,

low power instruments. An output disable pin allows further

reduction of the quiescent supply current to 1.3 mA.

Rev. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

= 1 MHz

C

= 1 MHz

C

for 16-Bit Systems

AD8021

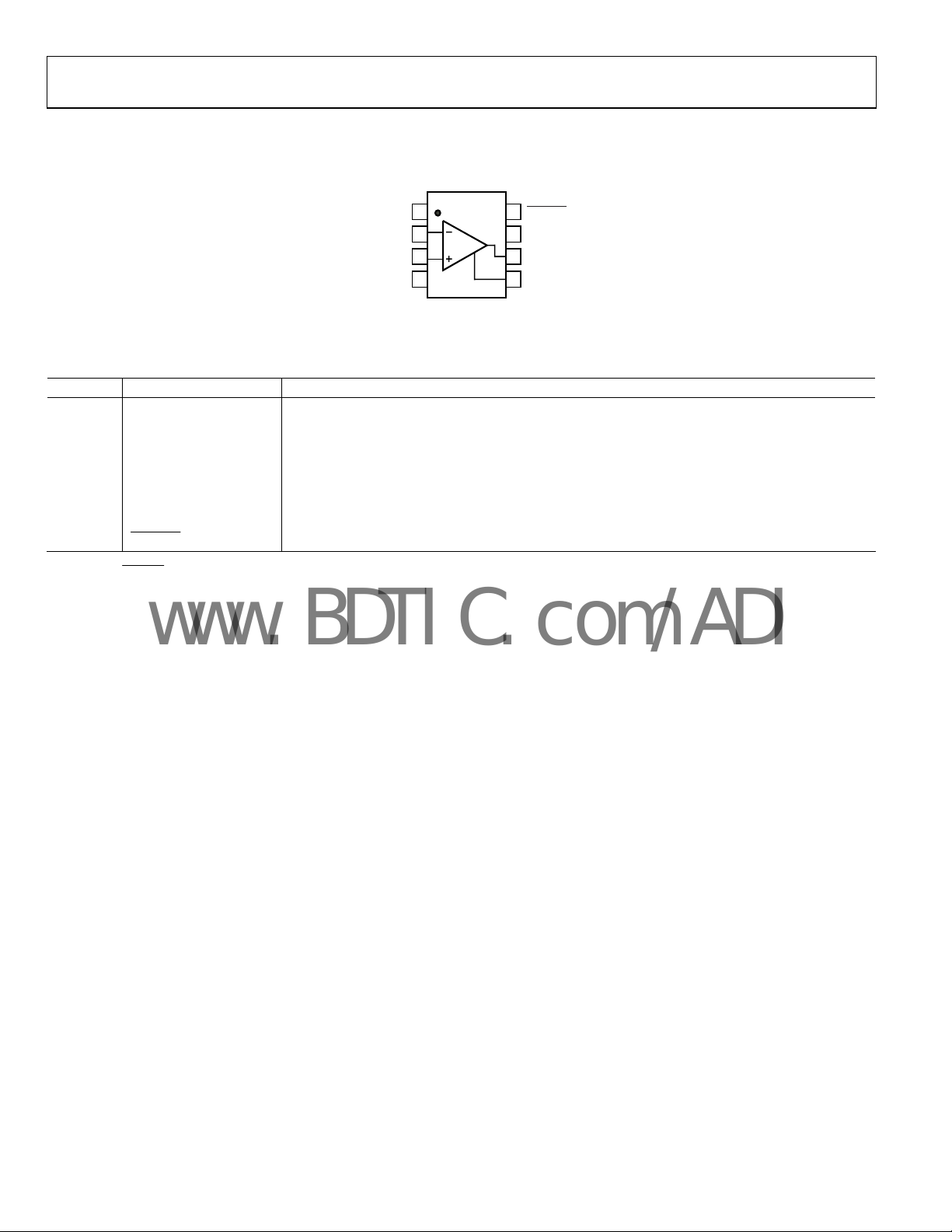

CONNECTION DIAGRAM

LOGIC

REFERENCE

–IN

+IN

–V

Figure 1. SOIC-8 (R-8) and MSOP-8 (RM-8)

The AD8021 allows the user to choose the gain bandwidth

p

roduct that best suits the application. With a single capacitor,

the user can compensate the AD8021 for the desired gain with

little trade-off in bandwidth. The AD8021 is a well-behaved

amplifier that settles to 0.01% in 23 ns for a 1 V step. It has a fast

overload recovery of 50 ns.

The AD8021 is stable over temperature with low input offset

v

oltage drift and input bias current drift, 0.5 μV/°C and 10 nA/°C,

respectively. The AD8021 is also capable of driving a 75 Ω line

with ±3 V video signals.

The AD8021 is both technically superior and priced considerably

l

ess than comparable amps drawing much higher quiescent

current. The AD8021 is a high speed, general-purpose amplifier,

ideal for a wide variety of gain configurations and can be used

throughout a signal processing chain and in control loops. The

AD8021 is available in both standard 8-lead SOIC and MSOP

packages in the industrial temperature range of −40°C to +85°C.

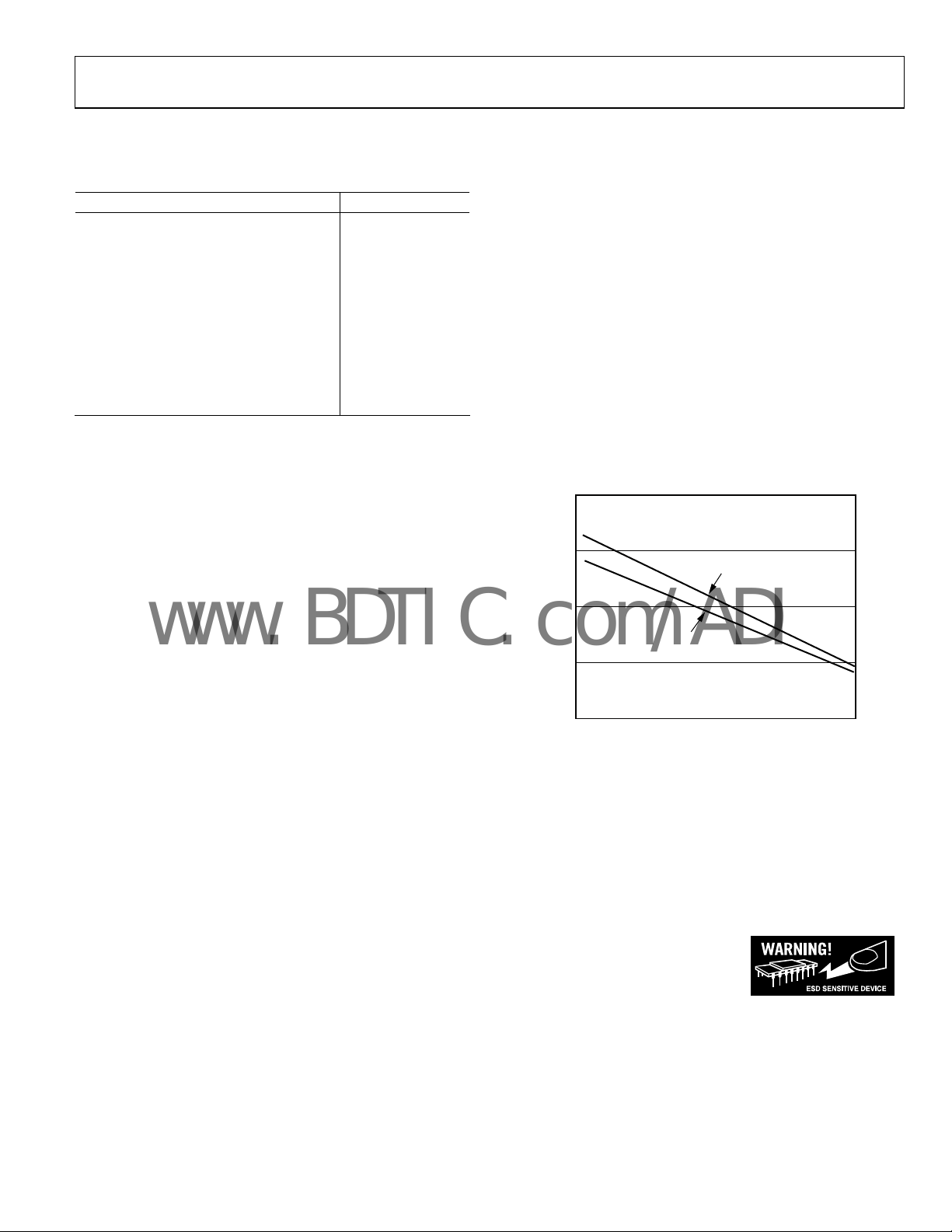

24

= 50mV p-p

V

OUT

21

G = –10, R

18

15

12

9

6

3

CLOSED-LOOP GAIN (dB)

0

–3

–6

0.1M 1G1M 10M 100M

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

F

R

= 100Ω, CC = 0pF

IN

G = –5, R

= 1kΩ, RG = 200Ω,

F

R

= 66.5Ω, CC = 1.5pF

IN

= 499Ω, RG = 249Ω,

G = –2, R

F

R

= 63.4Ω, CC = 4pF

IN

G = –1, R

= 499Ω, RG = 499Ω,

F

R

= 56.2Ω, CC = 7pF

IN

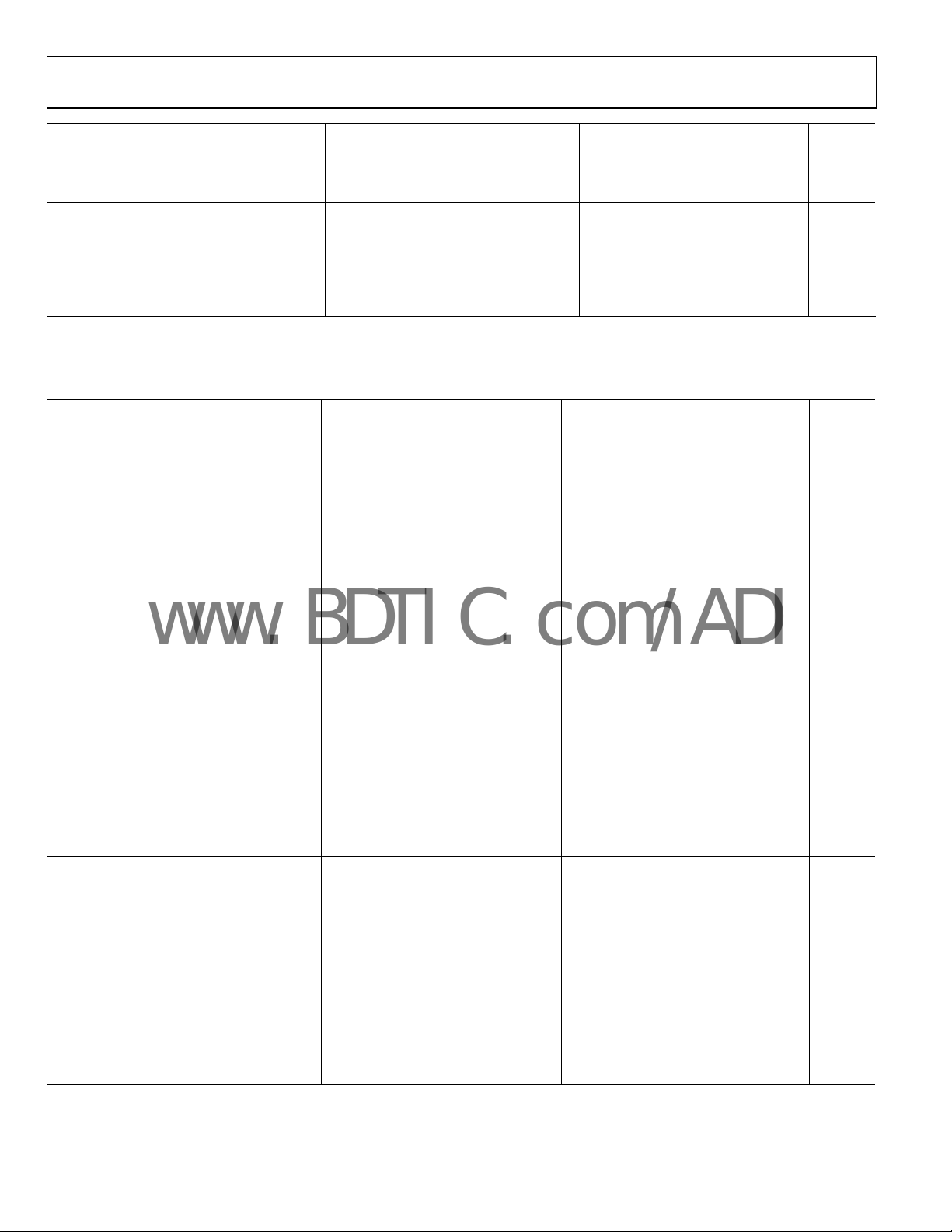

Figure 2. Small Signal Fr

AD8021

1

2

3

4

S

= 1kΩ, RG = 100Ω,

FREQUENCY (Hz)

8

DISABLE

+V

7

S

V

6

OUT

C

5

COMP

equency Response

01888-001

01888-002

AD8021

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications..................................................................................... 19

Applications....................................................................................... 1

General Description......................................................................... 1

Connection Diagram .......................................................................1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 7

Maximum Power Dissipation ..................................................... 7

ESD Caution.................................................................................. 7

Pin Configuration and Function Descriptions............................. 8

Typical Performance Characteristics............................................. 9

Test Circ uit s................................................................................. 17

REVISION HISTORY

5/06—Rev. E to Rev. F

Updated Format..................................................................Universal

Changes to General Description .................................................... 1

Changes to Figure 3.......................................................................... 7

Changes to Figure 60...................................................................... 19

Changes to Table 9.......................................................................... 23

3/05—Rev. D to Rev. E

U

pdated Format..................................................................Universal

Change to Figure 19 ....................................................................... 11

Change to Figure 25 ....................................................................... 12

Change to Table 7 and Table 8 ...................................................... 22

Change to Driving 16-Bit ADCs Section .................................... 22

Using the Disable Feature.......................................................... 20

Theory of Operation ...................................................................... 21

PCB Layout Considerations...................................................... 21

Driving 16-Bit ADCs................................................................. 22

Differential Driver...................................................................... 22

Using the AD8021 in Active Filters .........................................23

Driving Capacitive Loads.......................................................... 23

Outline Dimensions .......................................................................25

Ordering Guide .......................................................................... 25

7/03—Rev. B to Rev. C

eleted All References to Evaluation Board...................Universal

D

Replaced Figure 2 ..............................................................................5

Updated Outline Dimensions....................................................... 20

2/03—Rev. A to Rev. B

E

dits to Evaluation Board Applications....................................... 20

Edits to Figure 17 ........................................................................... 20

6/02—Rev. 0 to Rev. A

dits to Specifications.......................................................................2

E

10/03—Rev. C to Rev. D

U

pdated Format..................................................................Universal

Rev. F | Page 2 of 28

AD8021

www.BDTIC.com/ADI

SPECIFICATIONS

VS = ±5 V, @ TA = 25°C, RL = 1 kΩ, gain = +2, unless otherwise noted.

Table 1.

Parameter Conditions

DYNAMIC PERFORMANCE

−3 dB Small Signal Bandwidth

Slew Rate, 1 V Step

Settling Time to 0.01%

Overload Recovery (50%)

DISTORTION/NOISE PERFORMANCE

G = +1, C

G = +2, C

G = +5, C

G = +10, C

G = +1, C

G = +2, C

G = +5, C

G = +10, C

V

O

= 10 pF, VO = 0.05 V p-p 355 490

C

= 7 pF, VO = 0.05 V p-p 160 205

C

= 2 pF, VO = 0.05 V p-p 150 185

C

= 0 pF, VO = 0.05 V p-p 110 150

C

= 10 pF 95 120

C

= 7 pF 120 150

C

= 2 pF 250 300

C

= 0 pF 380 420

C

= 1 V step, RL = 500 Ω

±2.5 V input step, G = +2

AD8021AR/AD8021ARM

Min Typ Max Unit

23

50

f = 1 MHz

HD2

HD3

= 2 V p-p

V

O

= 2 V p-p

V

O

−93

−108

f = 5 MHz

HD2

HD3

Input Voltage Noise

Input Current Noise

Differential Gain Error

Differential Phase Error

DC PERFORMANCE

= 2 V p-p

V

O

= 2 V p-p

V

O

f = 50 kHz

f = 50 kHz

NTSC, R

NTSC, R

= 150 Ω

L

= 150 Ω

L

Input Offset Voltage

Input Offset Voltage Drift

Input Bias Current

to T

MAX

T

MIN

+Input or −input

Input Bias Current Drift

Input Offset Current

Open-Loop Gain

INPUT CHARACTERISTICS

Input Resistance

Common-Mode Input Capacitance

Input Common-Mode Voltage Range

Common-Mode Rejection Ratio

OUTPUT CHARACTERISTICS

= ±4 V −86 −98

V

CM

Output Voltage Swing

Linear Output Current

Short-Circuit Current

Capacitive Load Drive for 30% Overshoot

DISABLE CHARACTERISTICS

Off Isolation

Turn-On Time

Turn-Off Time

DISABLE Voltage—Off/On

Enabled Leakage Current

= 50 mV p-p/1 V p-p

V

O

f = 10 MHz

= 0 V to 2 V, 50% logic to 50% output

V

O

= 0 V to 2 V, 50% logic to 50% output

V

O

V

DISABLE

− V

LOGIC REFERENCE

LOGIC REFERENCE = 0.4 V

DISABLE

= 4.0 V

−70

−80

2.1 2.6 nV/√Hz

2.1

0.03

0.04

0.4 1.0 mV

0.5

7.5 10.5 μA

10

0.1 0.5 ±μA

82 86

10

1

−4.1 to +4.6

−3.5 to +3.2 −3.8 to +3.4

60

75

15/120

−40

45

50

1.75/1.90

70

2

MHz

MHz

MHz

MHz

V/μs

V/μs

V/μs

V/μs

ns

ns

dBc

dBc

dBc

dBc

pA/√Hz

%

Degrees

μV/°C

nA/°C

dB

MΩ

pF

V

dB

V

mA

mA

pF

dB

ns

ns

V

μA

μA

Rev. F | Page 3 of 28

AD8021

www.BDTIC.com/ADI

Parameter Conditions

Disabled Leakage Current

POWER SUPPLY

Operating Range

Quiescent Current

+Power Supply Rejection Ratio

−Power Supply Rejection Ratio

LOGIC REFERENCE = 0.4 V

DISABLE

Output enabled

Output disabled

V

V

= 0.4 V

= 4 V to 6 V, VEE = −5 V −86 −95

CC

= 5 V, VEE = −6 V to −4 V −86 −95

CC

AD8021AR/AD8021ARM

Min Typ Max Unit

±2.25 ±5 ±12.0 V

30

33

7.0 7.7 mA

1.3 1.6 mA

= ±12 V, @ TA = 25°C, RL = 1 kΩ, gain = +2, unless otherwise noted.

V

S

Table 2.

AD8021AR/AD8021ARM

Parameter Conditions Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Small Signal Bandwidth G = +1, CC = 10 pF, VO = 0.05 V p-p 520 560 MHz

G = +2, CC = 7 pF, VO = 0.05 V p-p 175 220 MHz

G = +5, CC = 2 pF, VO = 0.05 V p-p 170 200 MHz

G = +10, CC = 0 pF, VO = 0.05 V p-p 125 165 MHz

Slew Rate, 1 V Step G = +1, CC = 10 pF 105 130 V/μs

G = +2, CC = 7 pF 140 170 V/μs

G = +5, CC = 2 pF 265 340 V/μs

G = +10, CC = 0 pF 400 460 V/μs

Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 21 ns

Overload Recovery (50%) ±6 V input step, G = +2 90 ns

DISTORTION/NOISE PERFORMANCE

f = 1 MHz

HD2 VO = 2 V p-p −95 dBc

HD3 VO = 2 V p-p −116 dBc

f = 5 MHz

HD2 VO = 2 V p-p −71 dBc

HD3 VO = 2 V p-p −83 dBc

Input Voltage Noise f = 50 kHz 2.1 2.6 nV/√Hz

Input Current Noise f = 50 kHz 2.1 pA/√Hz

Differential Gain Error NTSC, RL = 150 Ω 0.03 %

Differential Phase Error NTSC, RL = 150 Ω 0.04 Degrees

DC PERFORMANCE

Input Offset Voltage 0.4 1.0 mV

Input Offset Voltage Drift T

Input Bias Current +Input or −input 8 11.3 μA

Input Bias Current Drift 10 nA/°C

Input Offset Current 0.1 0.5 ±μA

Open-Loop Gain 84 88 dB

INPUT CHARACTERISTICS

Input Resistance 10 MΩ

Common-Mode Input Capacitance 1 pF

Input Common-Mode Voltage Range −11.1 to +11.6 V

Common-Mode Rejection Ratio VCM = ±10 V −86 −96 dB

to T

MIN

0.2 μV/°C

MAX

μA

μA

dB

dB

Rev. F | Page 4 of 28

AD8021

www.BDTIC.com/ADI

AD8021AR/AD8021ARM

Parameter Conditions Min Typ Max Unit

OUTPUT CHARACTERISTICS

Output Voltage Swing −10.2 to +9.8 −10.6 to +10.2 V

Linear Output Current 70 mA

Short-Circuit Current 115 mA

Capacitive Load Drive for 30% Overshoot VO = 50 mV p-p/1 V p-p 15/120 pF

DISABLE CHARACTERISTICS

Off Isolation f = 10 MHz −40 dB

Turn-On Time VO = 0 V to 2 V, 50% logic to 50% output 45 ns

Turn-Off Time VO = 0 V to 2 V, 50% logic to 50% output 50 ns

V

DISABLE Voltage—Off/On

Enabled Leakage Current LOGIC REFERENCE = 0.4 V 70 μA

Disabled Leakage Current LOGIC REFERENCE = 0.4 V 30 μA

POWER SUPPLY

Operating Range ±2.25 ±5 ±12.0 V

Quiescent Current Output enabled 7.8 8.6 mA

Output disabled 1.7 2.0 mA

+Power Supply Rejection Ratio VCC = 11 V to 13 V, VEE = −12 V −86 −96 dB

−Power Supply Rejection Ratio VCC = 12 V, VEE = −13 V to −11 V −86 −100 dB

DISABLE

DISABLE

DISABLE

− V

LOGIC REFERENCE

= 4.0 V

= 0.4 V

1.80/1.95 V

2 μA

33 μA

V

= 5 V, @ TA = 25°C, RL = 1 kΩ, gain = +2, unless otherwise noted.

S

Table 3.

AD8021AR/AD8021ARM

Parameter Conditions Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Small Signal Bandwidth G = +1, CC = 10 pF, VO = 0.05 V p-p 270 305 MHz

G = +2, CC = 7 pF, VO = 0.05 V p-p 155 190 MHz

G = +5, CC = 2 pF, VO = 0.05 V p-p 135 165 MHz

G = +10, CC = 0 pF, VO = 0.05 V p-p 95 130 MHz

Slew Rate, 1 V Step G = +1, CC = 10 pF 80 110 V/μs

G = +2, CC = 7 pF 110 140 V/μs

G = +5, CC = 2 pF 210 280 V/μs

G = +10, CC = 0 pF 290 390 V/μs

Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 28 ns

Overload Recovery (50%) 0 V to 2.5 V input step, G = +2 40 ns

DISTORTION/NOISE PERFORMANCE

f = 1 MHz

HD2 VO = 2 V p-p −84 dBc

HD3 VO = 2 V p-p −91 dBc

f = 5 MHz

HD2 VO = 2 V p-p −68 dBc

HD3 VO = 2 V p-p −81 dBc

Input Voltage Noise f = 50 kHz 2.1 2.6 nV/√Hz

Input Current Noise f = 50 kHz 2.1 pA/√Hz

Rev. F | Page 5 of 28

AD8021

www.BDTIC.com/ADI

AD8021AR/AD8021ARM

Parameter Conditions Min Typ Max Unit

DC PERFORMANCE

Input Offset Voltage 0.4 1.0 mV

Input Offset Voltage Drift T

Input Bias Current +Input or −input 7.5 10.3 μA

Input Bias Current Drift 10 nA/°C

Input Offset Current 0.1 0.5 ±μA

Open-Loop Gain 72 76 dB

INPUT CHARACTERISTICS

Input Resistance 10 MΩ

Common-Mode Input Capacitance 1 pF

Input Common-Mode Voltage Range 0.9 to 4.6 V

Common-Mode Rejection Ratio 1.5 V to 3.5 V −84 −98 dB

OUTPUT CHARACTERISTICS

Output Voltage Swing 1.25 to 3.38 1.10 to 3.60 V

Linear Output Current 30 mA

Short-Circuit Current 50 mA

Capacitive Load Drive for 30% Overshoot VO = 50 mV p-p/1 V p-p 10/120 pF

DISABLE CHARACTERISTICS

Off Isolation f = 10 MHz −40 dB

Turn-On Time VO = 0 V to 1 V, 50% logic to 50% output 45 ns

Turn-Off Time VO = 0 V to 1 V, 50% logic to 50% output 50 ns

DISABLE Voltage—Off/On

Enabled Leakage Current LOGIC REFERENCE = 0.4 V 70 μA

Disabled Leakage Current LOGIC REFERENCE = 0.4 V 30 μA

POWER SUPPLY

Operating Range ±2.25 ±5 ±12.0 V

Quiescent Current Output enabled 6.7 7.5 mA

Output disabled 1.2 1.5 mA

+Power Supply Rejection Ratio VCC = 4.5 V to 5.5 V, VEE = 0 V −74 −82 dB

−Power Supply Rejection Ratio VCC = 5 V, VEE = −0.5 V to +0.5 V −76 −84 dB

to T

MIN

V

DISABLE

DISABLE

DISABLE

0.8 μV/°C

MAX

− V

LOGIC REFERENCE

= 4.0 V

= 0.4 V

1.55/1.70 V

2 μA

33 μA

Rev. F | Page 6 of 28

AD8021

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Supply Voltage 26.4 V

Power Dissipation

Observed power

ating curves

der

Input Voltage (Common Mode) ±VS ± 1 V

Differential Input Voltage

1

±0.8 V

Differential Input Current ±10 mA

Output Short-Circuit Duration

Observed power

ating curves

der

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +85°C

Lead Temperature (Soldering, 10 sec) 300°C

1

The AD8021 inputs are protected by diodes. Current-limiting resistors are

not used to preserve the low noise. If a differential input exceeds ±0.8 V, the

input current should be limited to ±10 mA.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

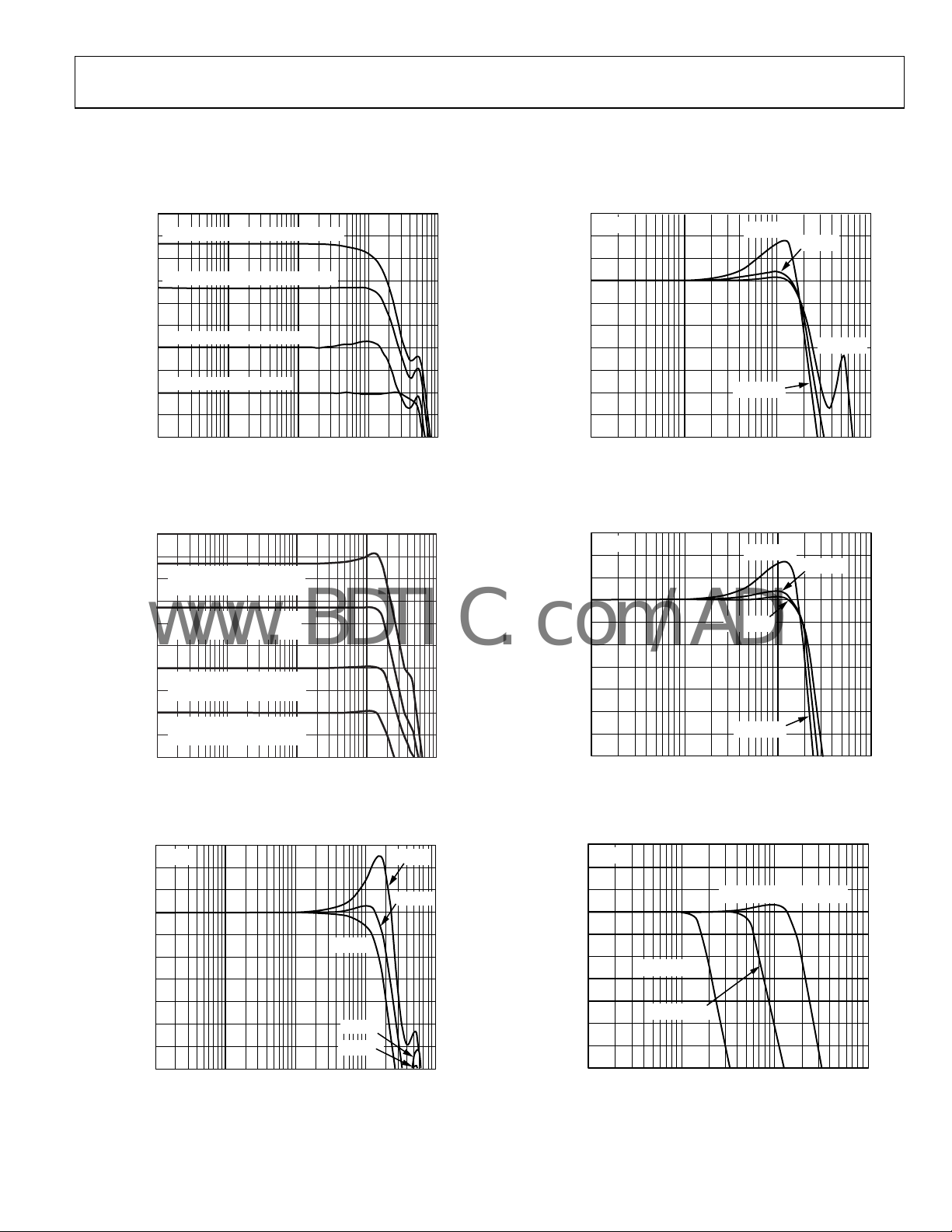

MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the

AD8021 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic

encapsulated devices is determined by the glass transition

temperature of the plastic, approximately 150°C. Temporarily

exceeding this limit can cause a shift in parametric performance

due to a change in the stresses exerted on the die by the package.

Exceeding a junction temperature of 175°C for an extended

period can result in device failure.

While the AD8021 is internally short-circuit protected, this can

ot be sufficient to guarantee that the maximum junction tem-

n

perature (150°C) is not exceeded under all conditions. To ensure

proper operation, it is necessary to observe the maximum

power derating curves.

2.0

1.5

8-LEAD SOIC

1.0

8-LEAD MSOP

0.5

MAXIMUM POW ER DISSIP ATION (W)

0.01

–55 –45 –35 –25 –15 –5 5 15 25 35 45 55 65

1

Specification is for device in free air: 8-lead SOIC: θJA = 125°C/W; 8-lead

Figure 3. Maximum Power Dissipation vs. Temperature

MSOP: θ

= 145°C/W.

JA

AMBIENT TEM PERATURE (°C)

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

01888-004

5

8

75

1

Rev. F | Page 7 of 28

AD8021

www.BDTIC.com/ADI

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

LOGIC

REFERENCE

–IN

+IN

–V

Figure 4. Pin Configuration

AD8021

1

2

3

4

S

8

DISABLE

+V

7

V

6

C

5

S

OUT

COMP

01888-003

Table 5. Pin Function Descriptions

Pin No. Mnemonic Description

1 LOGIC REFERENCE Reference for Pin 81 Voltage Level. Connect to logic low supply.

2 −IN Inverting Input.

3 +IN Noninverting Input.

4 −V

5 C

6 V

S

Compensation Capacitor. Tie to −VS. (See the Applications section for value.)

COMP

Output.

OUT

Negative Supply Voltage.

7 +VS Positive Supply Voltage.

8

1

When Pin 8 (

Pin 1, the part is disabled. (See the Specifications tables for exact disable and enable voltage levels.) If the disable feature is not going to be used, Pin 8 can be tied to

+VS or a logic high source, and Pin 1 can be tied to ground or logic low. Alternatively, if Pin 1 and Pin 8 are not connected, the part is in an enabled state.

DISABLE

DISABLE

) is higher than Pin 1 (LOGIC REFERENCE) by approximately 2 V or more, the part is enabled. When Pin 8 is brought down to within about 1.5 V of

Disable, Active Low.

Rev. F | Page 8 of 28

AD8021

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, VS = ±5 V, RL = 1 kΩ, G = +2, RF = RG = 499 Ω, RS = 49.9 Ω, RO = 976 Ω, RD = 53.6 Ω, CC = 7 pF, CL = 0, CF = 0, V

frequency = 1 MHz, unless otherwise noted.

24

G = +10, R

21

18

G = +5, R

15

12

9

G = +2, R

6

3

CLOSED-LOOP GAIN (dB)

G = +1, R

0

–3

–6

0.1M 1G1M 10M 100M

= 1kΩ, RG = 110Ω, CC = 0pF

F

= 1kΩ, RG = 249Ω, CC = 2pF

F

= RG = 499Ω, CC = 7pF

F

= 75Ω, CC = 10pF

F

FREQUENCY (Hz)

01888-005

9

G = +2

8

7

6

5

4

GAIN (dB)

3

2

1

0

–1

10M 100M

FREQUENCY (Hz)

VS = ±2.5V

VS = ±2.5V

OUT

VS = ±5V

VS = ±12V

= 2 V p-p,

01888-008

1G1M

Figure 5. Small S ignal Freq uency Respons e vs. Frequency and Gain,

V

= 50 mV p-p, Noninverting (See Figure 48)

OUT

24

21

G = –10, RF = 1kΩ, RG = 100Ω,

18

= 100Ω, CC = 0pF

R

IN

15

= 1kΩ, RG = 200Ω,

G = –5, R

12

9

GAIN (dB)

6

3

0

–3

–6

0.1M 1G1M 10M 100M

F

= 66.5Ω, CC = 1.5pF

R

IN

= 499Ω, RG = 249Ω,

G = –2, R

F

= 63.4Ω, CC = 4pF

R

IN

= 499Ω, RG = 499Ω,

G = –1, R

F

= 56.2Ω, CC = 7pF

R

IN

FREQUENCY (Hz)

Figure 6. Small S ignal Freq uency Respons e vs. Frequency and

in, V

Ga

9

G = +2

8

7

6

5

4

GAIN (dB)

3

2

1

0

–1

0.1M 1G1M

= 50 mV p-p Inverting (See Figure 48)

OUT

= 9pF

C

C

C

= 7pF

C

CC = 9pF

10M 100M

FREQUENCY (Hz)

C

C

C

C

= 5pF

= 7pF

Figure 7. Small S ignal Freq uency Respons e vs. Frequency and

ensation Capacitor, V

Comp

= 50 mV p-p (See Figu re 48)

OUT

01888-006

01888-007

Figure 8. Small S ignal Freq uency Respons e vs. Frequency and Supply,

= 50 mV p-p, Noninverting (See Figure 48)

V

OUT

3

G = –1

2

1

0

–1

–2

GAIN (dB)

–3

–4

–5

–6

–7

10M 100M

FREQUENCY (Hz)

VS = ±2.5V

VS = ±12V

VS = ±2.5V

VS = ±5V

01888-009

1G1M

Figure 9. Small S ignal Freq uency Respons e vs. Frequency and Supply,

V

= 50 mV p-p, Inverting (See Figure 50)

OUT

9

G = +2

8

7

6

5

4

GAIN (dB)

3

2

1

0

–1

V

= 4V p-p

OUT

V

= 1V p-p

OUT

10M 100M

Figure 10. Frequency Response v s. Frequency and V

V

= 0.1V AND 50mV p -p

OUT

FREQUENCY (Hz)

, Noninverting

OUT

01888-010

1G1M

(See Figure 48)

Rev. F | Page 9 of 28

Loading...

Loading...