ANALOG DEVICES AD80066 Service Manual

Complete 16-Bit

A

A

FEATURES

16-bit, 24 MSPS analog-to-digital converter (ADC)

4-channel operation up to 24 MHz (6 MHz/channel)

3-channel operation up to 24 MHz (8 MHz/channel)

Selectable input range: 3 V or 1.5 V peak-to-peak

Input clamp circuitry

Correlated double sampling

1×~6× programmable gain

±300 mV programmable offset

Internal voltage reference

Multiplexed byte-wide output

Optional single-byte output mode

3-wire serial digital interface

3 V/5 V digital I/O compatibility

Power dissipation: 490 mW at 24 MHz operation

Reduced power mode and sleep mode available

28-lead SSOP package

APPLICATIONS

Flatbed document scanners

Film scanners

Digital color copiers

Multifunction peripherals

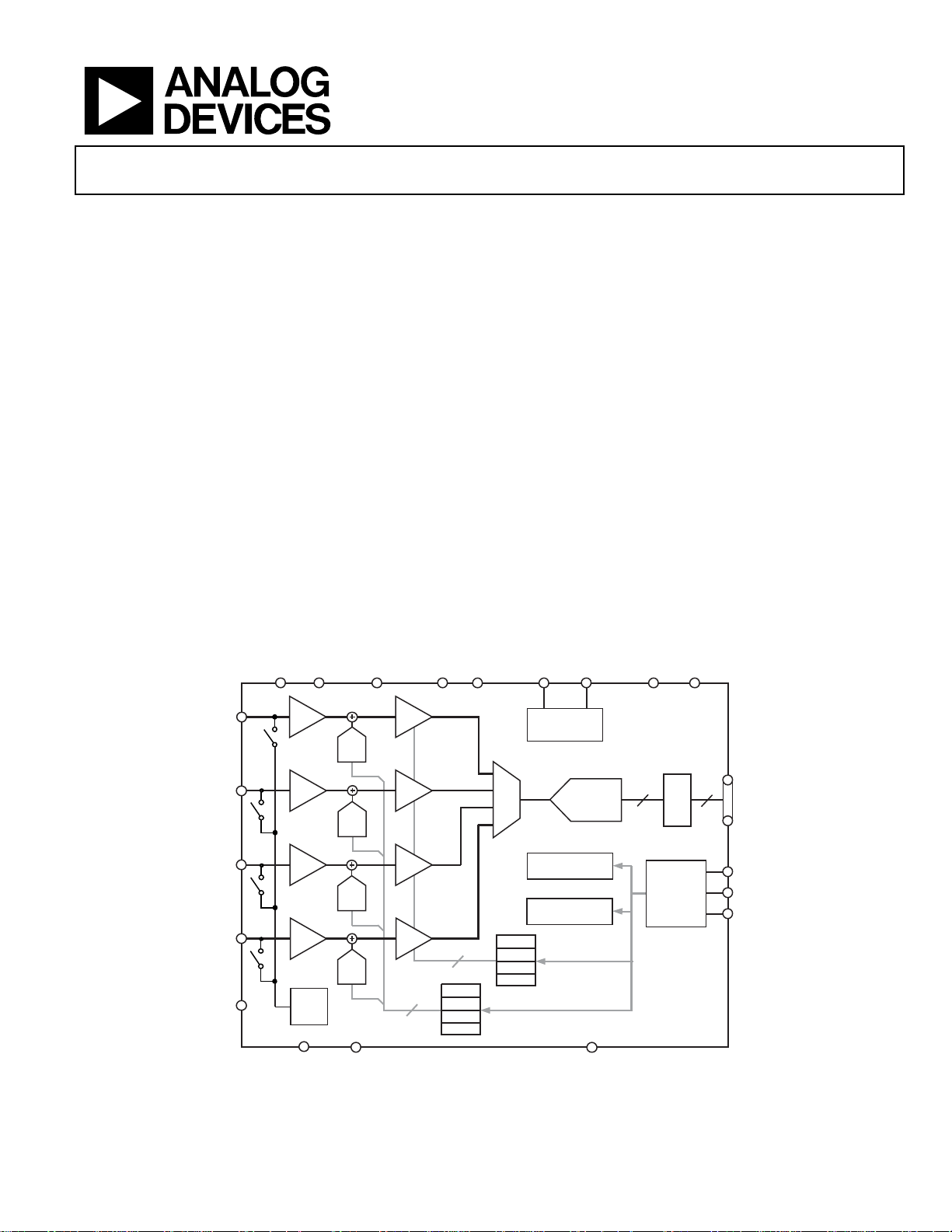

FUNCTIONAL BLOCK DIAGRAM

AVDD AVSS CML

CCD/CIS Signal Processor

GENERAL DESCRIPTION

The AD80066 is a complete analog signal processor for imaging

applications. It features a 4-channel architecture designed to sample

and condition the outputs of linear charged coupled device (CCD)

or contact image sensor (CIS) arrays. Each channel consists of

an input clamp, correlated double sampler (CDS), offset digitalto-analog converter (DAC), and programmable gain amplifier

(PGA), multiplexed to a high performance 16-bit ADC. For

maximum flexibility, the AD80066 can be configured as a

4-channel, 3-channel, 2-channel, or 1-channel device.

The CDS amplifiers can be disabled for use with sensors that

do not require CDS, such as CIS and CMOS sensors.

The 16-bit digital output is multiplexed into an 8-bit output word,

which is accessed using two read cycles. There is an optional

single-byte output mode. The internal registers are programmed

through a 3-wire serial interface and enable adjustment of the

gain, offset, and operating mode. The AD80066 operates from a

5 V power supply, typically consumes 490 mW of power, and is

packaged in a 28-lead SSOP.

VDD CAPT CAPB

VSS

AD80066

DRVDD DRVSS

VINA

VINB

VINC

VIND

OFFSET

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

CDS

CDS

CDS

CDS

INPUT

CLAMP

BIAS

CDSCLK2CDSCLK1

9-BIT

DAC

9-BIT

DAC

9-BIT

DAC

9-BIT

DAC

PGA

PGA

PGA

PGA

9

6

CH. A

CH. B

CH. C

CH. D

4:1

MUX

CONFIGURAT ION

CH. A

CH. B

CH. C

CH. D

OFFSET

REGISTERS

BAND GAP

REFERENCE

16-BIT

ADC

REGISTER

MUX

REGISTER

GAIN

REGISTERS

ADCCLK

AD80066

16

DIGITAL

CONTROL

INTERFACE

16:8

MUX

8

DOUT

(D[0:7])

SCLK

SLOAD

SDATA

8552-001

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

AD80066

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Analog Specifications ................................................................... 3

Digital Specifications ................................................................... 4

Timing Specifications .................................................................. 5

Absolute Maximum Ratings ............................................................ 9

Thermal Resistance ...................................................................... 9

ESD Caution .................................................................................. 9

Pin Configuration and Function Descriptions ........................... 10

Typical Performance Characteristics ........................................... 11

Terminology .................................................................................... 12

Theory of Operation ...................................................................... 13

4-Channel CDS Mode ................................................................ 13

4-Channel SHA Mode ................................................................ 13

1-Channel CDS Mode ............................................................... 13

1-Channel SHA Mode ............................................................... 13

Internal Register Map .................................................................... 14

Internal Register Details ................................................................ 15

Configuration Register .............................................................. 15

Mux Register ............................................................................... 15

PGA Gain Registers ................................................................... 15

Offset Registers ........................................................................... 15

Circuit Operation ........................................................................... 17

Analog Inputs—CDS Mode ...................................................... 17

External Input Coupling Capacitors ........................................ 17

Analog Inputs—SHA Mode ...................................................... 18

Programmable Gain Amplifiers (PGA) .................................. 18

Applications Information .............................................................. 19

Circuit and Layout Recommendations ................................... 19

Outline Dimensions ....................................................................... 20

Ordering Guide .......................................................................... 20

REVISION HISTORY

4/10—Revision A: Initial Version

Rev. A | Page 2 of 20

AD80066

SPECIFICATIONS

ANALOG SPECIFICATIONS

T

to T

MIN

, AVDD = 5 V, DRVDD = 5 V, CDS mode, f

MAX

Table 1.

Parameter Min Typ Max Unit

MAXIMUM CONVERSION RATE

4-Channel Mode with CDS 24 MSPS

3-Channel Mode with CDS 24 MSPS

2-Channel Mode with CDS 24 MSPS

1-Channel Mode with CDS 12 MSPS

ACCURACY (ENTIRE SIGNAL PATH)

ADC Resolution 16 Bits

Integral Nonlinearity (INL) +20/−5 LSB

Differential Nonlinearity (DNL) ±0.5 LSB

No Missing Codes Guaranteed

ANALOG INPUTS

Input Signal Range

1

1.5/3.0 V p-p

Allowable Reset Transient1 2.0 V

Input Limits

2

AVSS − 0.3 AVDD + 0.3 V

Input Capacitance 10 pF

Input Bias Current 10 nA

AMPLIFIERS

PGA Gain Range 1 5.9 V/V

PGA Gain Resolution2 64 Steps

PGA Gain Monotonicity Guaranteed

Programmable Offset Range −305 +295 mV

Programmable Offset Resolution 512 Steps

Programmable Offset Monotonicity Guaranteed

NOISE AND CROSSTALK

Total Output Noise at PGA Minimum 9.5 LSB rms

Total Output Noise at PGA Maximum 35 LSB rms

Channel-to-Channel Crosstalk

@ 24 MSPS 70 dB

@ 12 MSPS 90 dB

POWER SUPPLY REJECTION

AVDD = 5 V ± 0.25 V 0.1 % FSR

VOLTAGE REFERENCE (TA = 25°C)

CAPT − CAPB 0.75 V

TEMPERATURE RANGE

Operating 0 70 °C

Storage −65 +150 °C

POWER SUPPLIES

AVDD 4.5 5.0 5.25 V

DRVDD 3.0 3.3 5.25 V

OPERATING CURRENT

AVDD 95 mA

DRVDD 4 mA

Power-Down Mode Current 300 μA

ADCCLK

= 24 MHz, f

CDSCLK1

= f

= 6 MHz, PGA gain = 1, unless otherwise noted.

CDSCLK2

Rev. A | Page 3 of 20

AD80066

A

Parameter Min Typ Max Unit

POWER DISSIPATION

4-Channel Mode at 24 MHz 490 mW

1-Channel Mode at 12 MHz 300 mW

4-Channel Mode at 8 MHz, Slow Power Mode

1

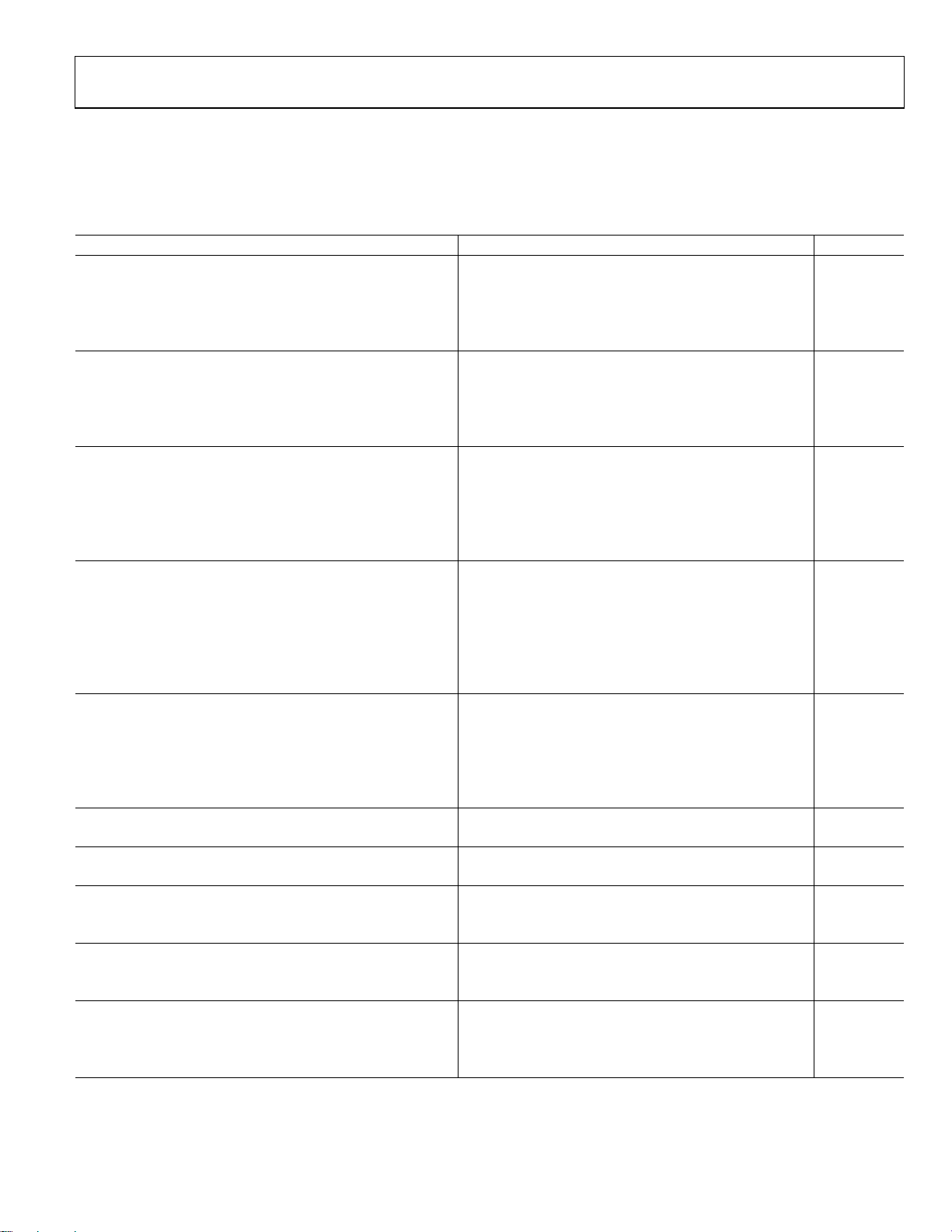

The linear input signal range is up to 3 V p-p when the CCD reference level is clamped to 3 V by the AD80066 input clamp (see ). Figure 2

2

The PGA gain is approximately linear-in-dB but varies nonlinearly with register code (see the section for more information). Programmable Gain Amplifiers (PGA)

3

Measured with Bit D1 of the configuration register set high for 8 MHz, low power operation.

2V TYP

RESET TRANSIENT

DIGITAL SPECIFICATIONS

T

to T

MIN

Table 2.

Parameter Symbol Min Typ Max Unit

LOGIC INPUTS

High Level Input Voltage VIH 2.0 V

Low Level Input Voltage VIL 0.8 V

High Level Input Current IIH 10 μA

Low Level Input Current IIL 10 μA

Input Capacitance CIN 10 pF

LOGIC OUTPUTS (DRVDD = 5 V)

High Level Output Voltage (IOH = 2 mA) VOH 4.5 V

Low Level Output Voltage (IOL = 2 mA) VOL 0.5 V

LOGIC OUTPUTS (DRVDD = 3 V)

High Level Output Voltage (IOH = 2 mA) VOH 2.5 V

Low Level Output Voltage (IOL = 2 mA) VOL 0.5 V

, AVDD = 5 V, DRVDD = 5 V, CDS mode, f

MAX

3

165 mW

VDD = 5V

3V BIAS SET BY INPUT CLAMP

1.5V OR 3V p-p MAX INPUT SIGNAL RANGE

GND

08552-002

Figure 2. Input Signal with the CCD Reference Level Clamped to 3 V

ADCCLK

= 24 MHz, f

CDSCLK1

= f

= 6 MHz, CL = 10 pF, unless otherwise noted.

CDSCLK2

Rev. A | Page 4 of 20

AD80066

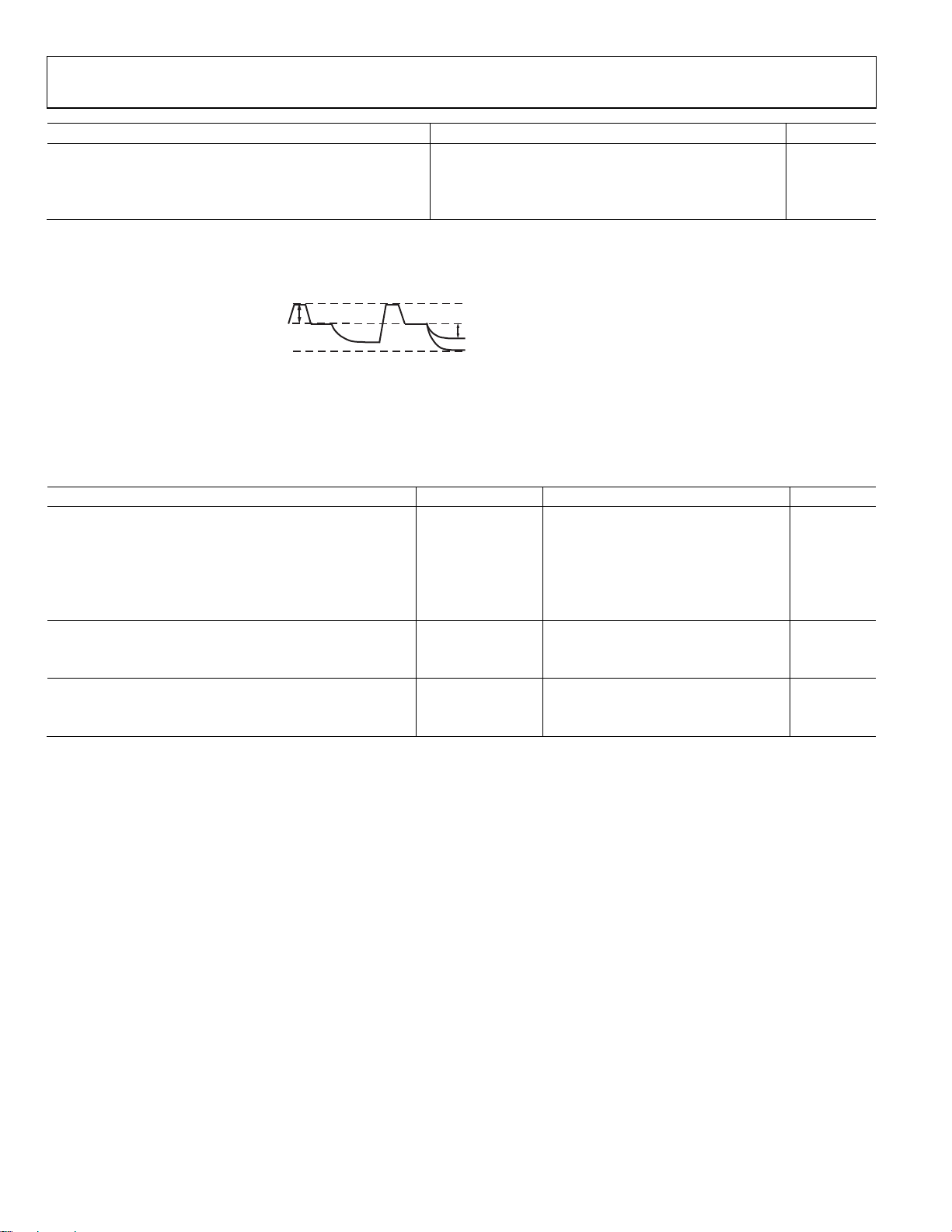

TIMING SPECIFICATIONS

T

to T

MIN

Table 3.

Parameter Symbol Min Typ Max Unit

CLOCK PARAMETERS

4-Channel Pixel Rate t

1-Channel Pixel Rate t

ADCCLK Pulse Width t

CDSCLK1 Pulse Width tC1 15 ns

CDSCLK2 Pulse Width tC2 15 ns

CDSCLK1 Falling1 to CDSCLK2 Rising t

ADCCLK Falling to CDSCLK2 Rising t

CDSCLK2 Rising to ADCCLK Rising t

CDSCLK2 Falling1 to ADCCLK Falling t

CDSCLK2 Falling1 to CDSCLK1 Rising t

Aperture Delay for CDS Clocks tAD 2 ns

SERIAL INTERFACE

Maximum SCLK Frequency, Write Operation f

Maximum SCLK Frequency, Read Operation f

SLOAD to SCLK Setup Time tLS 5 ns

SCLK to SLOAD Hold Time tLH 5 ns

SDATA to SCLK Rising Setup Time tDS 2 ns

SCLK Rising to SDATA Hold Time tDH 2 ns

SCLK Falling to SDATA Valid t

DATA OUTPUT

Output Delay tOD 8 ns

Latency (Pipeline Delay) 3 (fixed) Cycles

1

CDSCLKx falling edges should not occur within the first 10 ns following an ADCCLK edge.

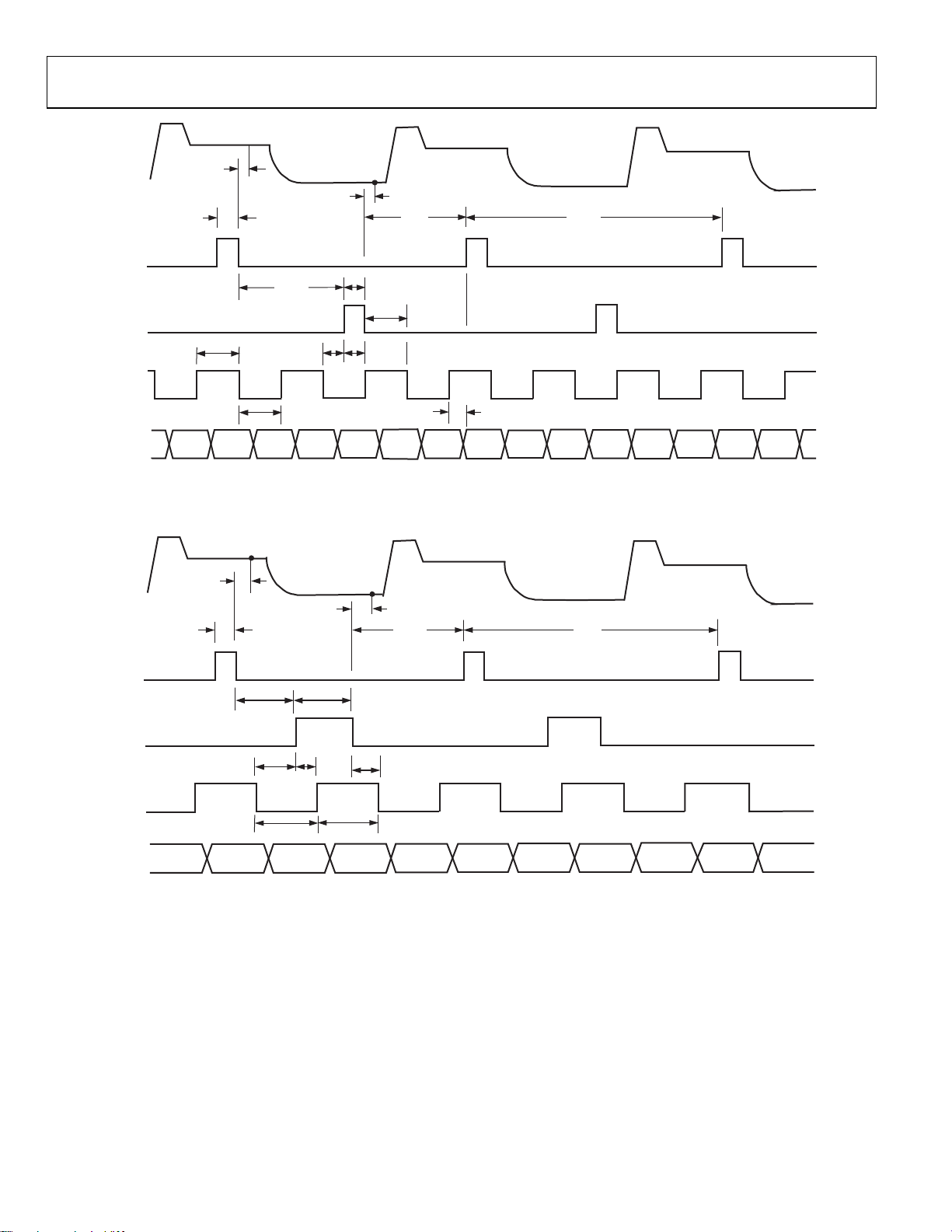

Timing Diagrams

, AVDD = 5 V, DRVDD = 5 V.

MAX

t

PRA

166 ns

PRA

83 ns

PRB

20 ns

ADCCLK

0 ns

C1C2

0 ns

ADC2

5 ns

C2ADR

20 ns

C2ADF

5 ns

C2C1

50 MHz

SCLK

25 MHz

SCLK

10 ns

RDV

ANALOG

INPUTS

CDSCLK1

CDSCLK2

ADCCLK

OUTPUT

DATA

(D[7:0])

t

ADCCLK

t

AD

t

C1

t

ADCCLK

C(n – 2)B(n – 2) C(n – 2) D(n – 2) D(n – 2) A(n – 1) A(n – 1) B(n – 1) B(n – 1) C( n – 1) C(n – 1) D(n – 1) D(n – 1) A(n) A(n) B(n )

HIGH

LOW

BYTE

HIGH

BYTE

BYTE

PIXEL n (A,B,C,D) PIXEL (n + 1)

t

AD

t

C2C1

t

C1C2

LOW

BYTE

t

ADC2

HIGH

BYTE

LOW

BYTE

t

C2

t

C2ADR

HIGH

BYTE

t

C2ADF

t

OD

LOW

HIGH

LOW

HIGH

BYTE

BYTE

BYTE

BYTE

LOW

BYTE

HIGH

BYTE

LOW

BYTE

HIGH

BYTE

Figure 3. 4-Channel CDS Mode Timing

Rev. A | Page 5 of 20

8552-003

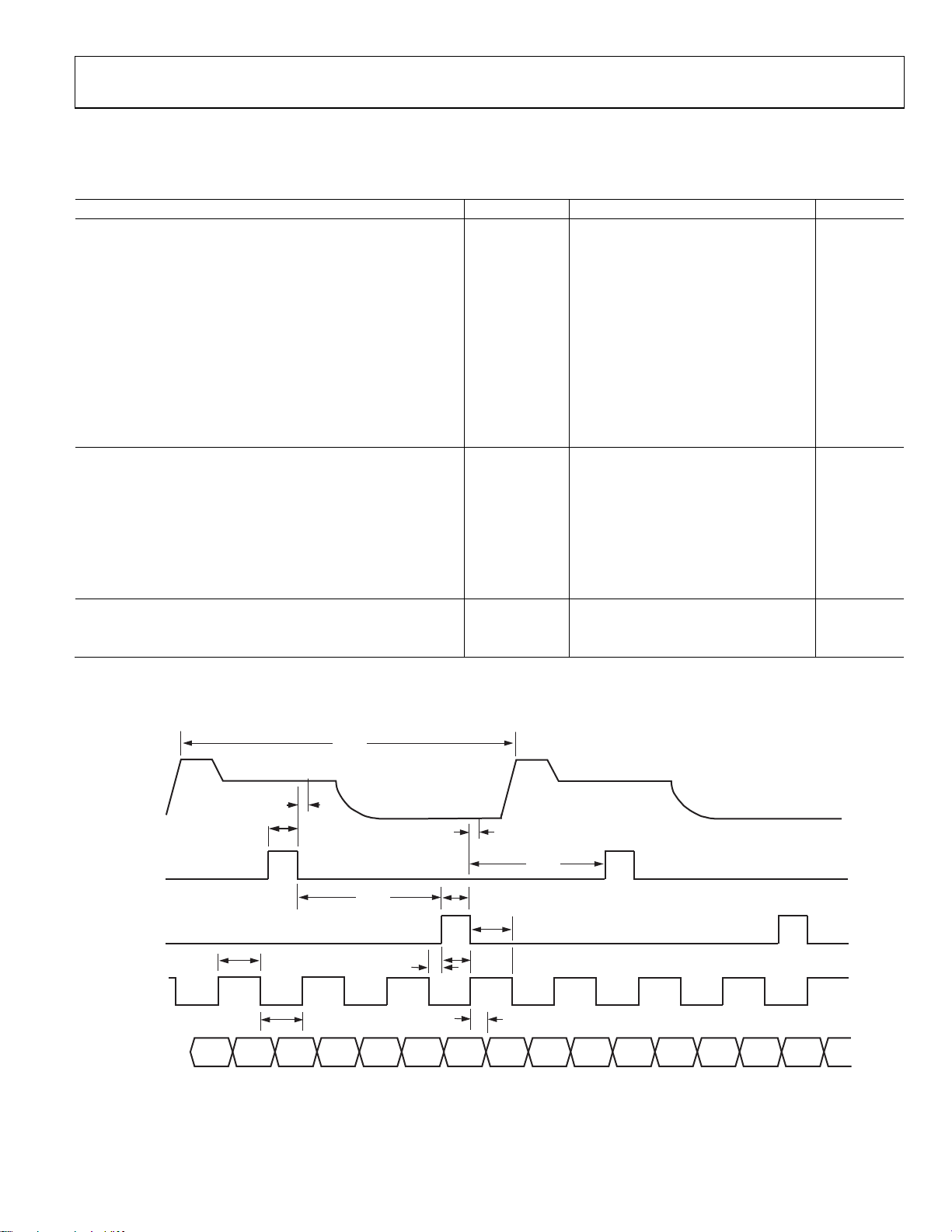

AD80066

ANALOG

INPUTS

CDSCLK1

CDSCLK2

ADCCLK

OUTPUT

DATA

(D[7:0])

t

ADCCLK

t

AD

t

C1

B(n – 2)A(n – 2) B(n – 2) C(n – 2) C(n – 2) A(n – 1) A(n – 1) B( n – 1) B(n – 1) C(n – 1) C(n – 1) A(n) A(n) B(n) B(n)

HIGH

BYTE

PIXEL n (A, B, C) PIXEL (n + 1) PIXEL (n + 2)

t

AD

LOW

BYTE

t

C1C2

t

t

ADC2

ADCCLK

HIGH

BYTE

LOW

BYTE

t

C2

t

C2ADF

t

C2ADR

HIGH

BYTE

t

C2C1

LOW

BYTE

HIGH

BYTE

t

OD

LOW

BYTE

HIGH

BYTE

t

PRA

LOW

HIGH

LOW

BYTE

BYTE

BYTE

HIGH

BYTE

LOW

BYTE

08552-004

Figure 4. 3-Channel CDS Mode Timing

ANALOG

INPUTS

PIXEL n

t

AD

t

AD

t

C1

t

C2C1

PIXEL (n + 1) PIXEL (n + 2)

t

PRA

CDSCLK1

CDSCLK2

ADCCLK

OUTPUT

DATA

(D[7:0])

t

C1C2

t

ADC2

t

CH 1 (n – 2) CH 2 (n – 2) CH 1 (n – 1) CH 2 (n – 1) CH 1 (n)

HIGH

BYTE

ADCCLK

LOW

BYTE

t

C2ADR

t

C2

t

ADCCLK

HIGH

BYTE

t

C2ADF

LOW

BYTE

HIGH

BYTE

LOW

BYTE

HIGH

BYTE

LOW

BYTE

HIGH

BYTE

LOW

BYTE

08552-005

Figure 5. 2-Channel CDS Mode Timing

Rev. A | Page 6 of 20

Loading...

Loading...