ANALOG DEVICES AD7918 Service Manual

8-Channel, 1 MSPS, 8-/10-/12-Bit ADCs

A

www.BDTIC.com/ADI

FEATURES

Fast throughput rate: 1 MSPS

Specified for AV

Low power

6.0 mW max at 1 MSPS with 3 V supply

13.5 mW max at 1 MSPS with 5 V supply

Eight (single-ended) inputs with sequencer

Wide input bandwidth

AD7928, 70 dB min SINAD at 50 kHz input frequency

Flexible power/serial clock speed management

No pipeline delays

High speed serial interface SPI®/QSPI™/

MICROWIRE™/DSP compatible

Shutdown mode: 0.5 μA max

20-lead TSSOP package

GENERAL DESCRIPTION

The AD7908/AD7918/AD7928 are, respectively, 8-bit, 10-bit, and

12-bit, high speed, low power, 8-channel, successive approximation

ADCs. The parts operate from a single 2.7 V to 5.25 V power

supply and feature throughput rates up to 1 MSPS. The parts

contain a low noise, wide bandwidth track-and-hold amplifier that

can handle input frequencies in excess of 8 MHz.

The conversion process and data acquisition are controlled using

CS

and the serial clock signal, allowing the device to easily interface

with microprocessors or DSPs. The input signal is sampled on the

falling edge of

There are no pipeline delays associated with the part.

of 2.7 V to 5.25 V

DD

CS

and conversion is also initiated at this point.

with Sequencer in 20-Lead TSSOP

AD7908/AD7918/AD7928

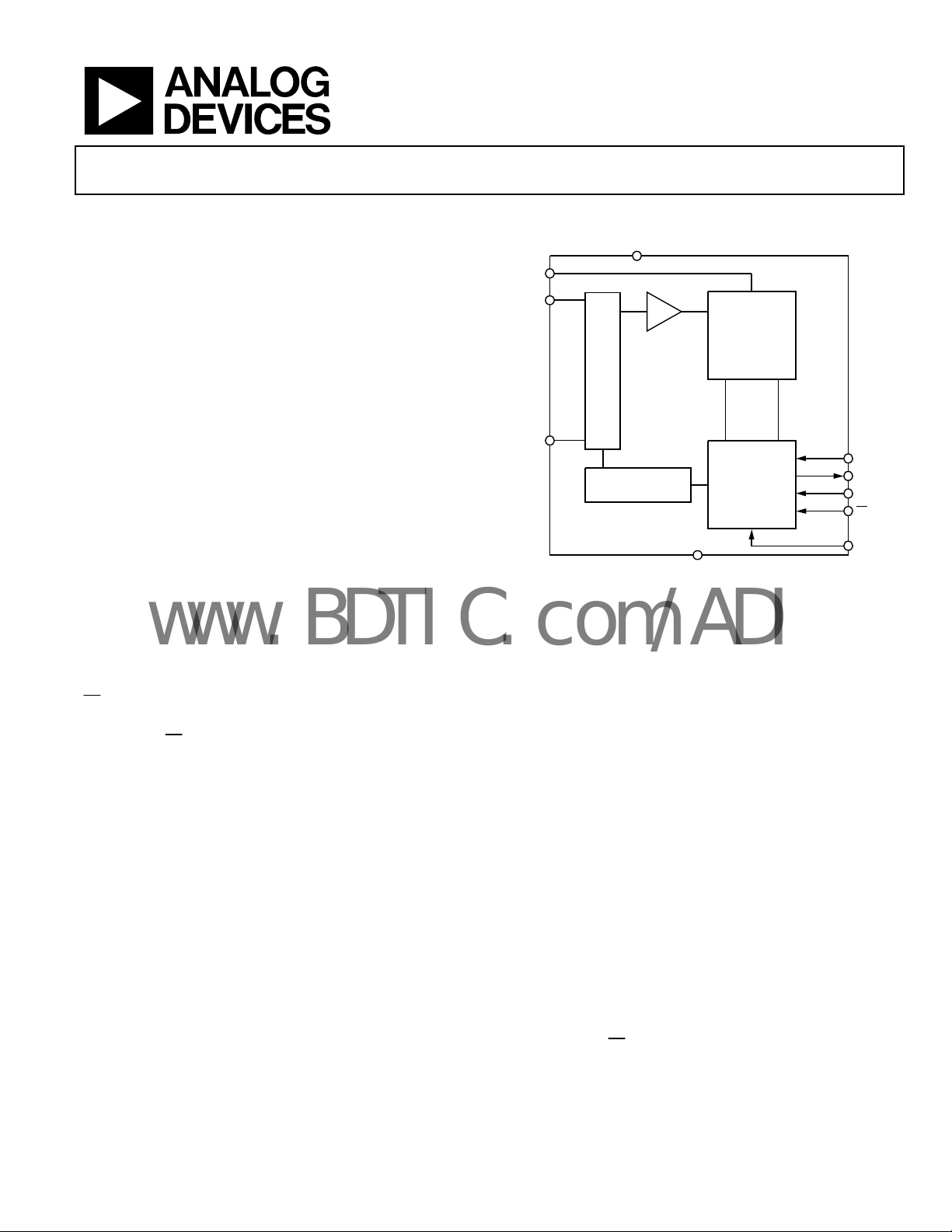

FUNCTIONAL BLOCK DIAGRAM

V

DD

REF

IN

VIN0

•

•

•

•

•

•

•

•

•

•

•

•

•

7

V

IN

I/P

MUX

AD7908/AD7918/AD7928

PRODUCT HIGHLIGHTS

1. High Throughput with Low Power Consumption. The AD7908/

AD7918/AD7928 offer up to 1 MSPS throughput rates. At the

maximum throughput rate with 3 V supplies, the AD7908/

AD7918/AD7928 dissipate just 6 mW of power maximum.

2. Eight Single-Ended Inputs with a Channel Sequencer.

A sequence of channels can be selected, through which

the ADC cycles and converts on.

T/H

SEQUENCER

APPROXIMATI ON

CONTROL LO GIC

GND

Figure 1.

8-/10-/12-BI T

SUCCESSIVE

ADC

SCLK

DOUT

DIN

CS

V

DRIVE

03089-001

The AD7908/AD7918/AD7928 use advanced design techniques to

achieve very low power dissipation at maximum throughput rates.

At maximum throughput rates, the AD7908/AD7918/AD7928

consume 2 mA maximum with 3 V supplies; with 5 V supplies, the

3. Single-Supply Operation with V

AD7918/AD7928 operate from a single 2.7 V to 5.25 V supply.

The V

function allows the serial interface to connect directly

DRIVE

to either 3 V or 5 V processor systems independent of AV

current consumption is 2.7 mA maximum.

4. Flexible Power/Serial Clock Speed Management. The conversion

Through the configuration of the control register, the analog input

range for the part can be selected as 0 V to REF

REF

, with either straight binary or twos complement output

IN

or 0 V to 2 ×

IN

coding. The AD7908/AD7918/AD7928 each feature eight singleended analog inputs with a channel sequencer to allow a

rate is determined by the serial clock, allowing the conversion

time to be reduced through the serial clock speed increase. The

parts also feature various shutdown modes to maximize power

efficiency at lower throughput rates. Current consumption is

0.5 μA max when in full shutdown.

preprogrammed selection of channels to be converted sequentially.

5. No Pipeline Delay. The parts feature a standard successive

The conversion time for the AD7908/AD7918/AD7928 is

determined by the SCLK frequency, which is also used as the

approximation ADC with accurate control of the sampling

instant via a

CS

input and once off conversion control.

master clock to control the conversion.

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006–2008 Analog Devices, Inc. All rights reserved.

Function. The AD7908/

DRIVE

.

DD

AD7908/AD7918/AD7928

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

AD7908 Specifications ................................................................. 3

AD7918 Specifications ................................................................. 5

AD7928 Specifications ................................................................. 7

Timing Specifications .................................................................. 9

Absolute Maximum Ratings .......................................................... 10

ESD Caution ................................................................................ 10

Pin Configuration and Function Descriptions ........................... 11

Terminology .................................................................................... 12

Typical Performance Characteristics ........................................... 13

Performance Curves ................................................................... 13

Control Register .............................................................................. 15

Sequencer Operation ................................................................. 16

SHADOW Register .................................................................... 17

Circuit Information .................................................................... 18

Converter Operation .................................................................. 18

ADC Transfer Function ............................................................. 19

Handling Bipolar Input Signals ................................................ 19

Typical Connection Diagram ................................................... 19

Modes of Operation ................................................................... 21

Power vs. Throughput Rate ....................................................... 23

Serial Interface ............................................................................ 23

Microprocessor Interfacing ....................................................... 24

Application Hints ....................................................................... 27

Outline Dimensions ....................................................................... 28

Ordering Guide .......................................................................... 28

REVISION HISTORY

11/08—Rev. B to Rev. C

Changes to ESD Parameter, Table 5 ............................................. 10

6/06—Rev. A to Rev. B

Updated Format .................................................................. Universal

Changes to Reference Section ....................................................... 21

9/03—Rev. 0 to Rev. A

Changes to Figure 3 ........................................................................ 15

Changes to Reference section ....................................................... 18

Rev. C | Page 2 of 28

AD7908/AD7918/AD7928

www.BDTIC.com/ADI

SPECIFICATIONS

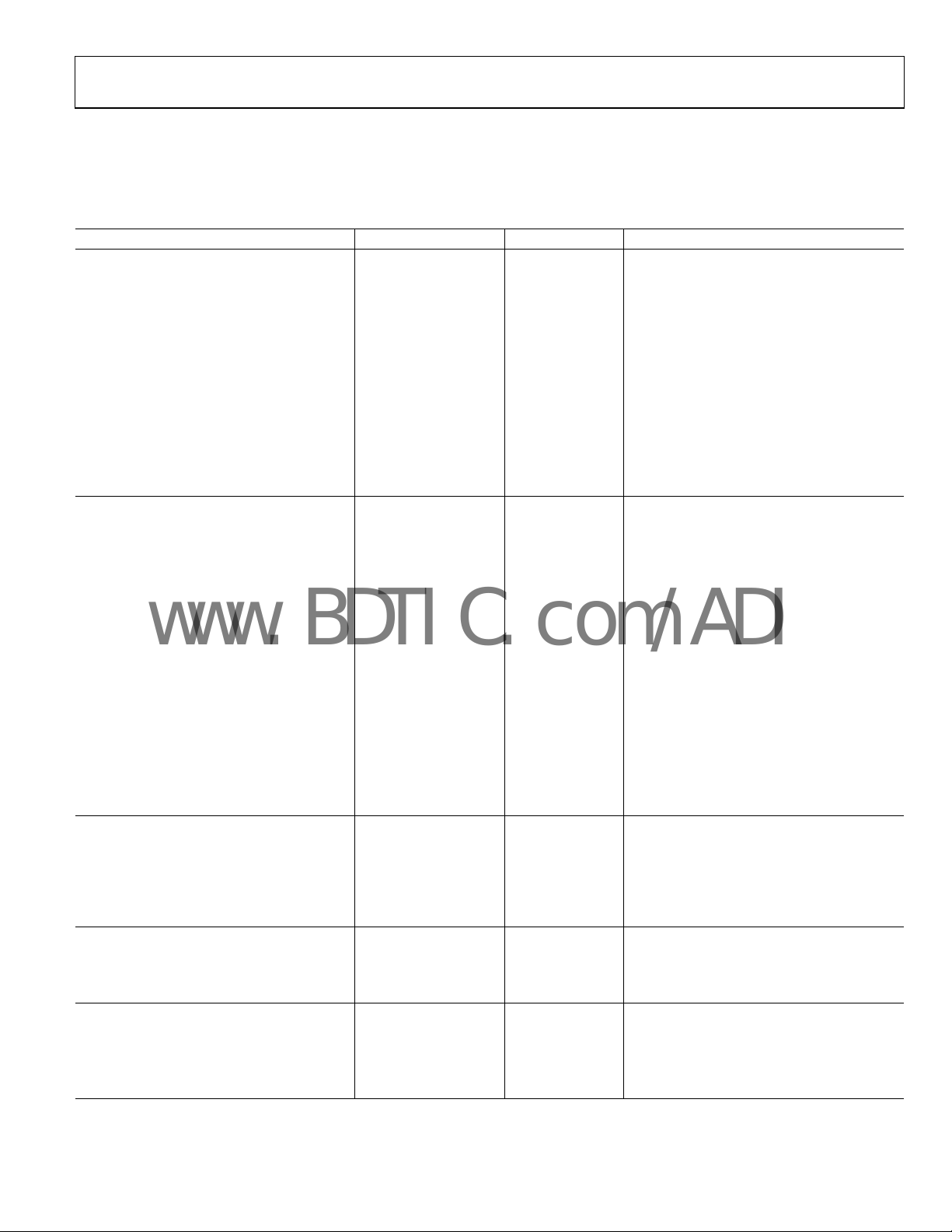

AD7908 SPECIFICATIONS

AVDD = V

Table 1.

Parameter B Version1 Unit Test Conditions/Comments

DYNAMIC PERFORMANCE fIN = 50 kHz sine wave, f

Signal-to-(Noise + Distortion) (SINAD)2 49 dB min

Signal-to-Noise Ratio (SNR)2 49 dB min

Total Harmonic Distortion (THD)2 −66 dB max

Peak Harmonic or Spurious Noise (SFDR)2 −64 dB max

Intermodulation Distortion (IMD)2 fa = 40.1 kHz, fb = 41.5 kHz

Second-Order Terms −90 dB typ

Third-Order Terms −90 dB typ

Aperture Delay 10 ns typ

Aperture Jitter 50 ps typ

Channel-to-Channel Isolation2 −85 dB typ fIN = 400 kHz

Full Power Bandwidth 8.2 MHz typ @ 3 dB

1.6 MHz typ @ 0.1 dB

DC ACCURACY2

Resolution 8 Bits

Integral Nonlinearity ±0.2 LSB max

Differential Nonlinearity ±0.2 LSB max Guaranteed no missed codes to 8 bits

0 V to REFIN Input Range Straight binary output coding

Offset Error ±0.5 LSB max

Offset Error Match ±0.05 LSB max

Gain Error ±0.2 LSB max

Gain Error Match ±0.05 LSB max

0 V to 2 × REFIN Input Range

Positive Gain Error ±0.2 LSB max

Positive Gain Error Match ±0.05 LSB max

Zero Code Error ±0.5 LSB max

Zero Code Error Match ±0.1 LSB max

Negative Gain Error ±0.2 LSB max

Negative Gain Error Match ±0.05 LSB max

ANALOG INPUT

Input Voltage Ranges 0 to REFIN V RANGE bit set to 1

0 to 2 × REFIN V

DC Leakage Current ±1 μA max

Input Capacitance 20 pF typ

REFERENCE INPUT

REFIN Input Voltage 2.5 V ±1% specified performance

DC Leakage Current ±1 μA max

REFIN Input Impedance 36 kΩ typ f

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, IIN ±1 μA max Typically 10 nA, VIN = 0 V or V

Input Capacitance, C

= 2.7 V to 5.25 V, REFIN = 2.5 V, f

DRIVE

0.7 × V

INH

0.3 × V

INL

3

10 pF max

IN

= 20 MHz, TA = T

SCLK

V min

DRIVE

V max

DRIVE

Rev. C | Page 3 of 28

MIN

to T

, unless otherwise noted.

MAX

−REF

twos complement output coding

RANGE bit set to 0, AV

5.25 V

SAMPLE

= 20 MHz

SCLK

to +REFIN biased about REFIN with

IN

= 4.75 V to

DD/VDRIVE

= 1 MSPS

DRIVE

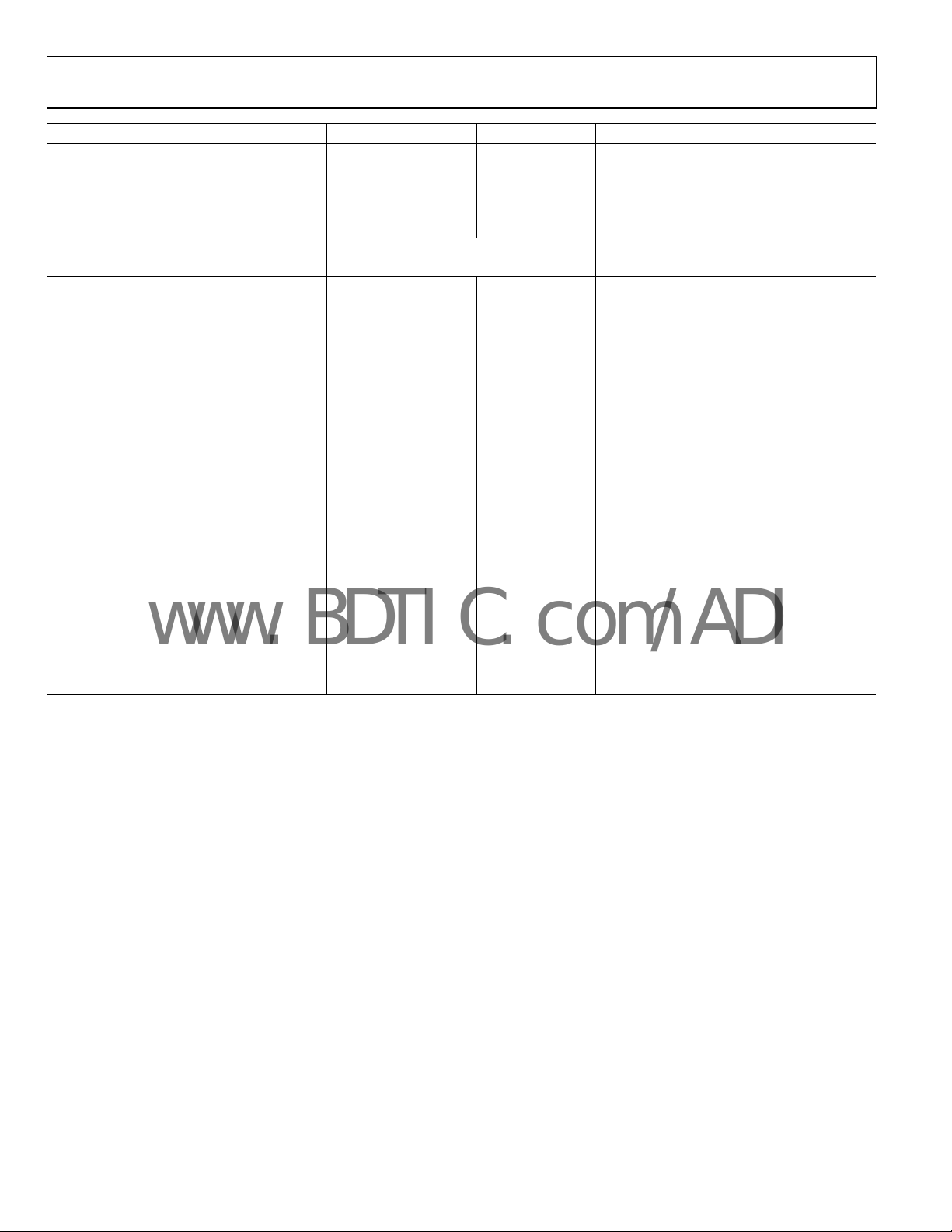

AD7908/AD7918/AD7928

www.BDTIC.com/ADI

Parameter B Version1 Unit Test Conditions/Comments

LOGIC OUTPUTS

Output High Voltage, VOH V

Output Low Voltage, VOL 0.4 V max I

Floating-State Leakage Current ±1 μA max

Floating-State Output Capacitance3 10 pF max

Output Coding Straight (natural) binary Coding bit set to 1

Twos complement Coding bit set to 0

CONVERSION RATE

Conversion Time 800 ns max 16 SCLK cycles with SCLK at 20 MHz

Track-and-Hold Acquisition Time 300 ns max Sine wave input

300 ns max Full-scale step input

Throughput Rate 1 MSPS max See Serial Interface section

POWER REQUIREMENTS

AVDD 2.7/5.25 V min/max

V

2.7/5.25 V min/max

DRIVE

4

I

Digital inputs = 0 V or V

DD

Normal Mode (Static) 600 μA typ AVDD = 2.7 V to 5.25 V, SCLK On or Off

Normal Mode (Operational) 2.7 mA max AVDD = 4.75 V to 5.25 V, f

2 mA max AVDD = 2.7 V to 3.6 V, f

Using Auto Shutdown Mode 960 μA typ f

0.5 μA max (Static)

Full Shutdown Mode 0.5 μA max SCLK on or off (20 nA typ)

Power Dissipation4

Normal Mode (Operational) 13.5 mW max AVDD = 5 V, f

6 mW max AVDD = 3 V, f

Auto Shutdown Mode (Static) 2.5 μW max AVDD = 5 V

1.5 μW max AVDD = 3 V

Full Shutdown Mode 2.5 μW max AVDD = 5 V

1.5 μW max AVDD = 3 V

1

Temperature ranges as follows: B version: −40°C to +85°C.

2

See Terminology section.

3

Sample tested @ 25°C to ensure compliance.

4

See Power vs. Throughput Rate section.

− 0.2 V min I

DRIVE

= 200 μA, AVDD = 2.7 V to 5.25 V

SOURCE

= 200 μA

SINK

DRIVE

SCLK

= 20 MHz

SCLK

= 250 kSPS

SAMPLE

= 20 MHz

SCLK

= 20 MHz

SCLK

= 20 MHz

Rev. C | Page 4 of 28

AD7908/AD7918/AD7928

www.BDTIC.com/ADI

AD7918 SPECIFICATIONS

AVDD = V

Table 2.

Parameter B Version1 Unit Test Conditions/Comments

DYNAMIC PERFORMANCE fIN = 50 kHz sine wave, f

Signal-to-(Noise + Distortion) (SINAD)2 61 dB min

Signal-to-Noise Ratio (SNR)2 61 dB min

Total Harmonic Distortion (THD)2 −72 dB max

Peak Harmonic or Spurious Noise (SFDR)2 −74 dB max

Intermodulation Distortion (IMD)2 fa = 40.1 kHz, fb = 41.5 kHz

Second-Order Terms −90 dB typ

Third-Order Terms −90 dB typ

Aperture Delay 10 ns typ

Aperture Jitter 50 ps typ

Channel-to-Channel Isolation2 −85 dB typ fIN = 400 kHz

Full Power Bandwidth 8.2 MHz typ @ 3 dB

1.6 MHz typ @ 0.1 dB

DC ACCURACY2

Resolution 10 Bits

Integral Nonlinearity ±0.5 LSB max

Differential Nonlinearity ±0.5 LSB max Guaranteed no missed codes to 10 bits

0 V to REFIN Input Range Straight binary output coding

Offset Error ±2 LSB max

Offset Error Match ±0.2 LSB max

Gain Error ±0.5 LSB max

Gain Error Match ±0.2 LSB max

0 V to 2 × REFIN Input Range

Positive Gain Error ±0.5 LSB max

Positive Gain Error Match ±0.2 LSB max

Zero Code Error ±2 LSB max

Zero Code Error Match ±0.2 LSB max

Negative Gain Error ±0.5 LSB max

Negative Gain Error Match ±0.2 LSB max

ANALOG INPUT

Input Voltage Ranges 0 to REFIN V RANGE bit set to 1

0 to 2 × REFIN V RANGE bit set to 0, AVDD/V

DC Leakage Current ±1 μA max

Input Capacitance 20 pF typ

REFERENCE INPUT

REFIN Input Voltage 2.5 V ±1% specified performance

DC Leakage Current ±1 μA max

REFIN Input Impedance 36 kΩ typ f

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, IIN ±1 μA max Typically 10 nA, VIN = 0 V or V

Input Capacitance, C

= 2.7 V to 5.25 V, REFIN = 2.5 V, f

DRIVE

0.7 × V

INH

0.3 × V

INL

3

10 pF max

IN

= 20 MHz, TA = T

SCLK

V min

DRIVE

V max

DRIVE

MIN

to T

, unless otherwise noted.

MAX

to +REFIN biased about REFIN with twos

−REF

IN

complement output coding

= 1 MSPS

SAMPLE

= 20 MHz

SCLK

= 4.75 V to 5.25 V

DRIVE

DRIVE

Rev. C | Page 5 of 28

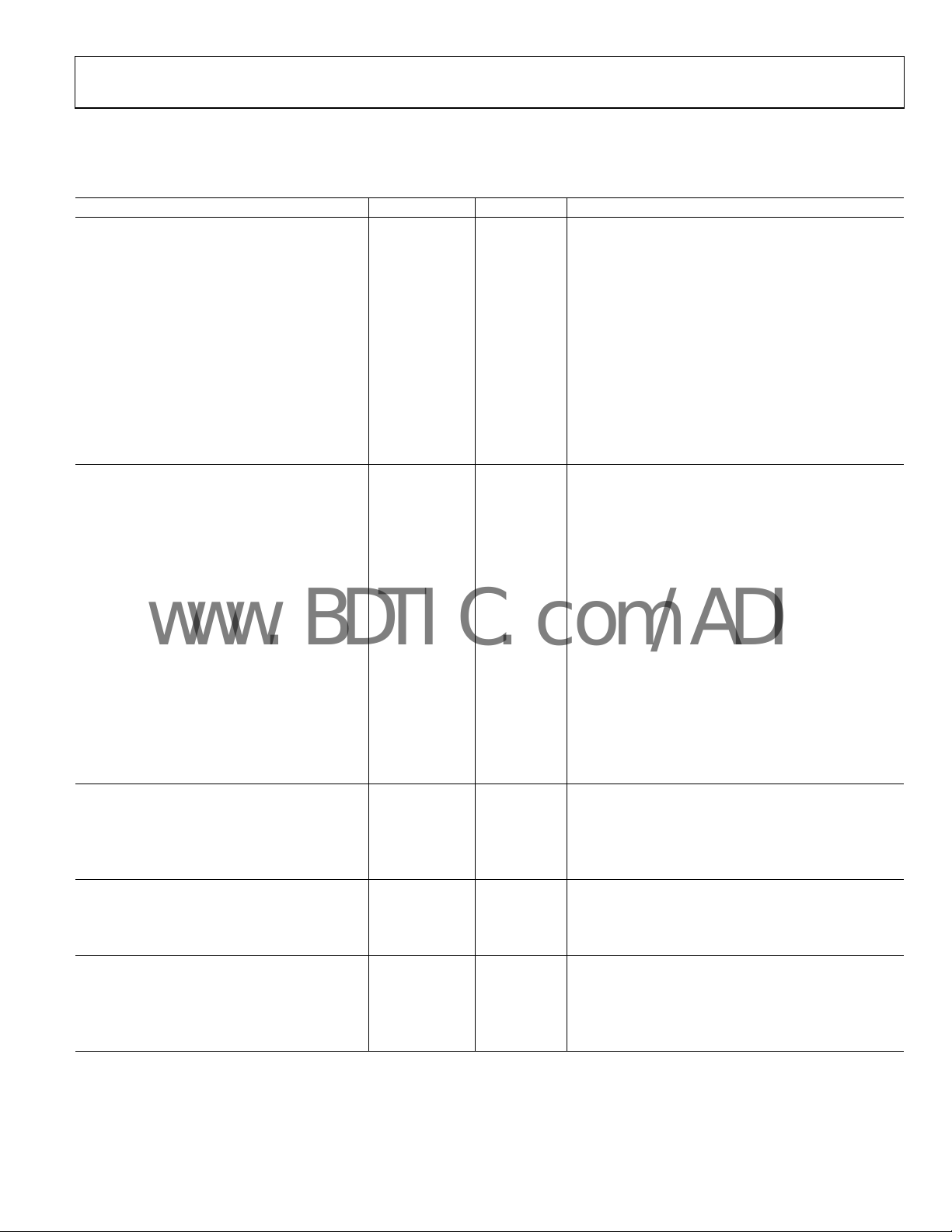

AD7908/AD7918/AD7928

www.BDTIC.com/ADI

Parameter B Version1 Unit Test Conditions/Comments

LOGIC OUTPUTS

Output High Voltage, VOH V

Output Low Voltage, VOL 0.4 V max I

Floating-State Leakage Current ±1 μA max

Floating-State Output Capacitance3 10 pF max

Output Coding Straight (natural) binary Coding bit set to 1

Twos complement Coding bit set to 0

CONVERSION RATE

Conversion Time 800 ns max 16 SCLK cycles with SCLK at 20 MHz

Track-and-Hold Acquisition Time 300 ns max Sine wave input

300 ns max Full-scale step input

Throughput Rate 1 MSPS max See Serial Interface section

POWER REQUIREMENTS

AVDD 2.7/5.25 V min/max

V

2.7/5.25 V min/max

DRIVE

4

I

Digital inputs = 0 V or V

DD

Normal Mode (Static) 600 μA typ AVDD = 2.7 V to 5.25 V, SCLK on or off

Normal Mode (Operational) 2.7 mA max AVDD = 4.75 V to 5.25 V, f

2 mA max AVDD = 2.7 V to 3.6 V, f

Using Auto Shutdown Mode 960 μA typ f

0.5 μA max (Static)

Full Shutdown Mode 0.5 μA max SCLK on or off (20 nA typ)

Power Dissipation4

Normal Mode (Operational) 13.5 mW max AVDD = 5 V, f

6 mW max AVDD = 3 V, f

Auto Shutdown Mode (Static) 2.5 μW max AVDD = 5 V

1.5 μW max AVDD = 3 V

Full Shutdown Mode 2.5 μW max AVDD = 5 V

1.5 μW max AVDD = 3 V

1

Temperature ranges as follows: B version: –40°C to +85°C.

2

See Terminology section.

3

Sample tested @ 25°C to ensure compliance.

4

See Power vs. Throughput Rate section.

− 0.2 V min I

DRIVE

= 200 μA, AVDD = 2.7 V to 5.25 V

SOURCE

= 200 μA

SINK

DRIVE

SCLK

= 20 MHz

SCLK

= 250 kSPS

SAMPLE

= 20 MHz

SCLK

= 20 MHz

SCLK

= 20 MHz

Rev. C | Page 6 of 28

AD7908/AD7918/AD7928

www.BDTIC.com/ADI

AD7928 SPECIFICATIONS

A

= V

VDD

Table 3.

Parameter B Version1 Unit Test Conditions/Comments

DYNAMIC PERFORMANCE fIN = 50 kHz sine wave, f

Signal-to-(Noise + Distortion) (SINAD)2 70 dB min @ 5 V

69 dB min @ 3 V typically 70 dB

Signal-to-Noise Ratio (SNR)2 70 dB min

Total Harmonic Distortion (THD)2 −77 dB max @ 5 V typically −84 dB

−73 dB max @ 3 V typically −77 dB

Peak Harmonic or Spurious Noise −78 dB max @ 5 V typically −86 dB

(SFDR)2 −76 dB max @ 3 V typically −80 dB

Intermodulation Distortion (IMD)2 fa = 40.1 kHz, fb = 41.5 kHz

Second-Order Terms −90 dB typ

Third-Order Terms −90 dB typ

Aperture Delay 10 ns typ

Aperture Jitter 50 ps typ

Channel-to-Channel Isolation2 −85 dB typ fIN = 400 kHz

Full Power Bandwidth 8.2 MHz typ @ 3 dB

1.6 MHz typ @ 0.1 dB

DC ACCURACY2

Resolution 12 Bits

Integral Nonlinearity ±1 LSB max

Differential Nonlinearity −0.9/+1.5 LSB max Guaranteed no missed codes to 12 bits

0 V to REFIN Input Range Straight binary output coding

Offset Error ±8 LSB max Typically ±0.5 LSB

Offset Error Match ±0.5 LSB max

Gain Error ±1.5 LSB max

Gain Error Match ±0.5 LSB max

0 V to 2 × REFIN Input Range

Positive Gain Error ±1.5 LSB max

Positive Gain Error Match ±0.5 LSB max

Zero Code Error ±8 LSB max Typically ±0.8 LSB

Zero Code Error Match ±0.5 LSB max

Negative Gain Error ±1 LSB max

Negative Gain Error Match ±0.5 LSB max

ANALOG INPUT

Input Voltage Ranges 0 to REFIN V RANGE bit set to 1

0 to 2 × REFIN V RANGE bit set to 0, AVDD/V

DC Leakage Current ±1 μA max

Input Capacitance 20 pF typ

REFERENCE INPUT

REFIN Input Voltage 2.5 V ±1% specified performance

DC Leakage Current ±1 μA max

REFIN Input Impedance 36 kΩ typ f

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, IIN ±1 μA max Typically 10 nA, VIN = 0 V or V

Input Capacitance, C

= 2.7 V to 5.25 V, REFIN = 2.5 V, f

DRIVE

0.7 × V

INH

0.3 × V

INL

3

10 pF max

IN

= 20 MHz, TA = T

SCLK

V min

DRIVE

V max

DRIVE

MIN

to T

, unless otherwise noted.

MAX

to +REFIN biased about REFIN with twos

−REF

IN

complement output coding

= 1 MSPS

SAMPLE

= 20 MHz

SCLK

= 4.75 V to 5.25 V

DRIVE

DRIVE

Rev. C | Page 7 of 28

AD7908/AD7918/AD7928

www.BDTIC.com/ADI

Parameter B Version1 Unit Test Conditions/Comments

LOGIC OUTPUTS

Output High Voltage, VOH V

Output Low Voltage, VOL 0.4 V max I

Floating-State Leakage Current ±1 μA max

Floating-State Output Capacitance3 10 pF max

Output Coding Straight (natural) binary Coding bit set to 1

Twos complement Coding bit set to 0

CONVERSION RATE

Conversion Time 800 ns max 16 SCLK cycles with SCLK at 20 MHz

Track-and-Hold Acquisition Time 300 ns max Sine wave input

300 ns max Full-scale step input

Throughput Rate 1 MSPS max See Serial Interface section

POWER REQUIREMENTS

AVDD 2.7/5.25 V min/max

V

2.7/5.25 V min/max

DRIVE

4

I

Digital inputs = 0 V or V

DD

Normal Mode (Static) 600 μA typ AVDD = 2.7 V to 5.25 V, SCLK on or off

Normal Mode (Operational) 2.7 mA max AVDD = 4.75 V to 5.25 V, f

2 mA max AVDD = 2.7 V to 3.6 V, f

Using Auto Shutdown Mode 960 μA typ f

0.5 μA max (Static)

Full Shutdown Mode 0.5 μA max SCLK on or off (20 nA typ)

Power Dissipation4

Normal Mode (Operational) 13.5 mW max AVDD = 5 V, f

6 mW max AVDD = 3 V, f

Auto Shutdown Mode (Static) 2.5 μW max AVDD = 5 V

1.5 μW max AVDD = 3 V

Full Shutdown Mode 2.5 μW max AVDD = 5 V

1.5 μW max AVDD = 3 V

1

Temperature ranges as follows: B Version: −40°C to +85°C.

2

See Terminology section.

3

Sample tested @ 25°C to ensure compliance.

4

See Power vs. Throughput Rate section.

− 0.2 V min I

DRIVE

= 200 μA, AVDD = 2.7 V to 5.25 V

SOURCE

= 200 μA

SINK

DRIVE

SCLK

= 20 MHz

SCLK

= 250 kSPS

SAMPLE

= 20 MHz

SCLK

= 20 MHz

SCLK

= 20 MHz

Rev. C | Page 8 of 28

AD7908/AD7918/AD7928

www.BDTIC.com/ADI

TIMING SPECIFICATIONS

AVDD = 2.7 V to 5.25 V, V

Table 4.

Limit at T

Parameter AVDD = 3 V AVDD = 5 V Unit Description

2

f

10 10 kHz min

SCLK

20 20 MHz max

t

16 × t

CONVER T

t

50 50 ns min

QUIET

t2

3

t

3

3

t

40 40 ns max Data access time after SCLK falling edge

4

t5 0.4 × t

t6 0.4 × t

SCLK

10 10 ns min

35 30 ns max

SCLK

SCLK

t7 10 10 ns min SCLK to DOUT valid hold time

4

t

15/45 15/35 ns min/max SCLK falling edge to DOUT high impedance

8

t9 10 10 ns min DIN setup time prior to SCLK falling edge

t

5 5 ns min DIN hold time after SCLK falling edge

10

t11

20 20 ns min

t12 1 1 μs max Power-up time from full power-down/auto shutdown mode

1

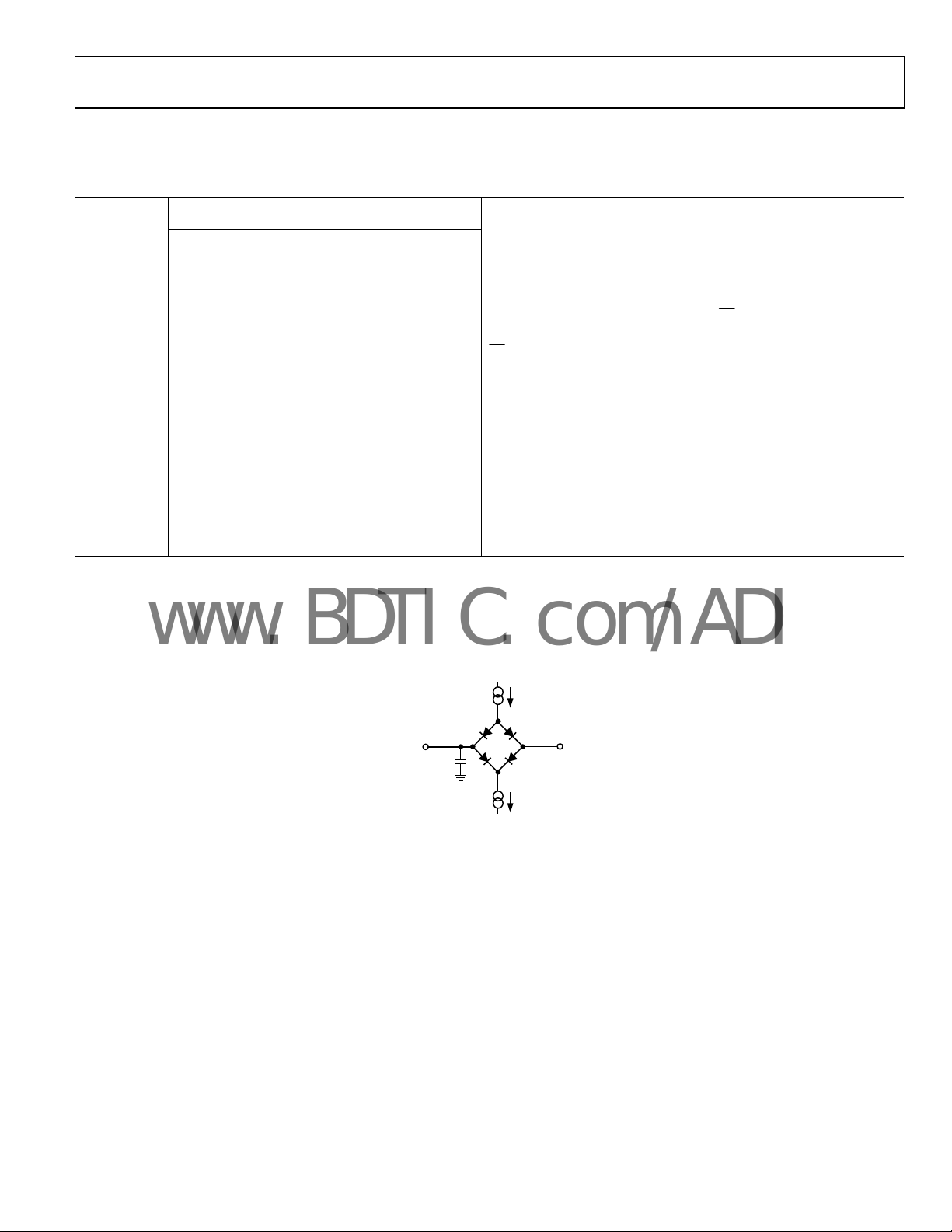

Sample tested at 25°C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of AVDD) and timed from a voltage level of 1.6 V. See Figure 2.

The 3 V operating range spans from 2.7 V to 3.6 V. The 5 V operating range spans from 4.75 V to 5.25 V.

2

Mark/space ratio for the SCLK input is 40/60 to 60/40.

3

Measured with the load circuit of Figure 2 and defined as the time required for the output to cross 0.4 V or 0.7 × V

4

t8 is derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 2. The measured number is then extrapolated

back to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, t8, quoted in the timing characteristics is the true bus relinquish

time of the part and is independent of the bus loading.

≤ AVDD, REFIN = 2.5 V, TA = T

DRIVE

, T

MIN

16 × t

0.4 × t

0.4 × t

AD7908/AD7918/AD7928

MAX

SCLK

ns min SCLK low pulse width

SCLK

ns min SCLK high pulse width

SCLK

MIN

to T

, unless otherwise noted.1

MAX

Minimum quiet time required between CS

next conversion

CS

to SCLK setup time

Delay from CS

th

SCLK falling edge to CS high

16

until DOUT three-state disabled

DRIVE

rising edge and start of

.

I

200µA

TO

OUTPUT

Figure 2. Load Circuit for Digital Output Timing Specifications

PIN

C

50pF

L

200µA

OL

1.6V

I

OH

3089-002

Rev. C | Page 9 of 28

Loading...

Loading...