Analog Devices AD7898 a Datasheet

5 V, 12-Bit, Serial 220 kSPS

a

FEATURES

Fast 12-Bit ADC with 220 kSPS Throughput Rate

8-Lead SOIC

Single 5 V Supply Operation

High Speed, Flexible, Serial Interface that

Allows Interfacing to 3 V Processors

On-Chip Track/Hold Amplifier

Selection of Input Ranges

ⴞ10 V for AD7898-10

ⴞ2.5 V for AD7898-3

High Input Impedance

Low Power: 22.5 mW Max

GENERAL DESCRIPTION

The AD7898 is a fast 12-bit ADC that operates from a single

5V supply and is housed in a small 8-lead SOIC package. The

part contains a successive approximation A/D converter, an onchip track/hold amplifier, an on-chip clock, and a high speed

serial interface.

The AD7898 offers two modes of operation. In Mode 0, conversion is initiated by the CONVST input and the conversion

process is controlled by an internal clock oscillator. In this mode,

the serial interface consists of three wires and the AD7898 is

capable of throughput rates up to 220 kSPS. In Mode 1, the

conversion process is controlled by an externally applied SCLK

with data being accessed from the part during conversion. In

this mode, the serial interface consists of three wires and the

AD7898 is capable of throughput rates up to 220 kSPS.

In addition to the traditional dc accuracy specifications, such as

linearity and full-scale and offset errors, the AD7898 is specified

for dynamic performance parameters, including harmonic distortion and signal-to-noise ratio.

The part accepts an analog input range of ±10 V (AD7898-10)

and ± 2.5 V (AD7898-3), and operates from a single 5 V supply,

consuming only 22.5 mW max.

The part is available in an 8-lead Standard Small Outline

Package (SOIC).

ADC in an 8-Lead Package

AD7898

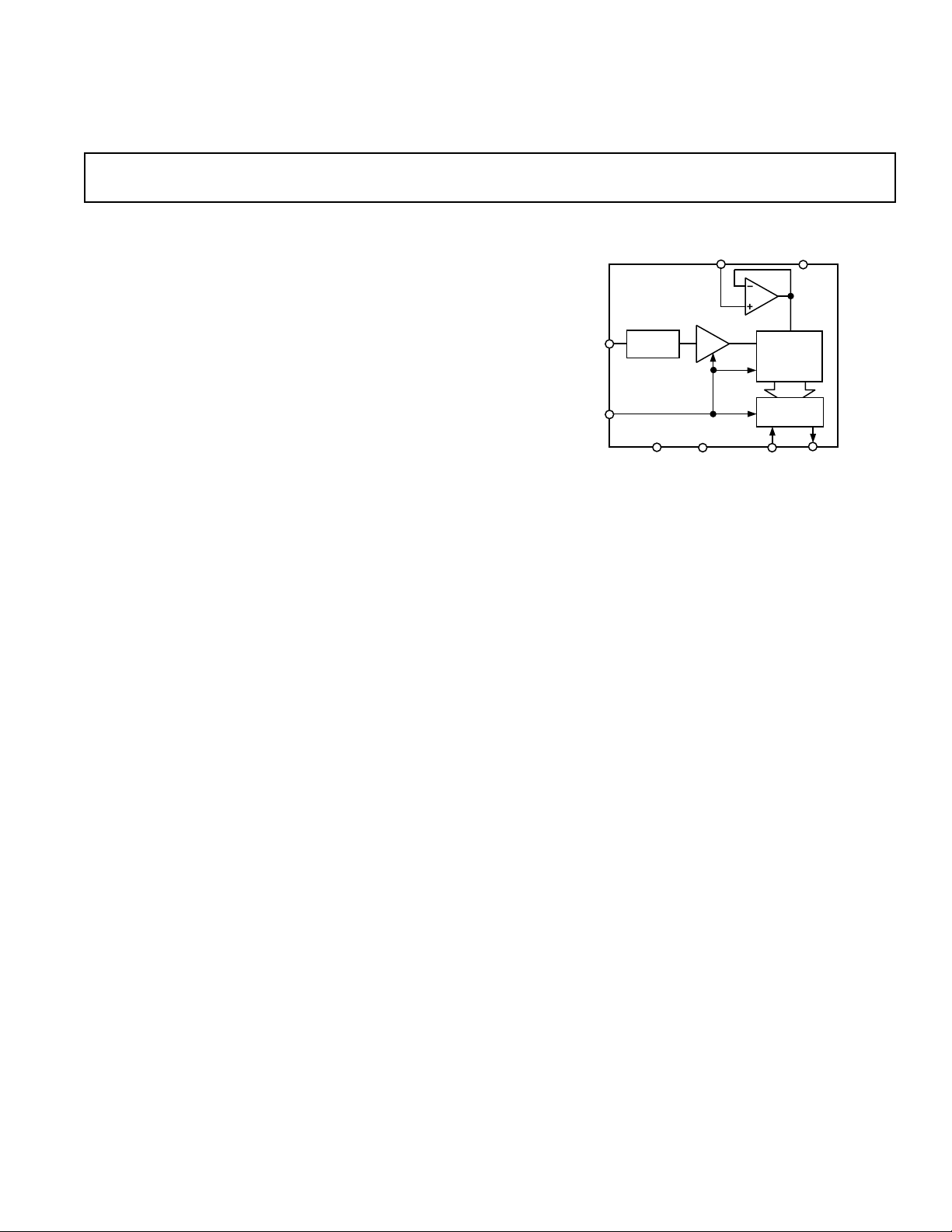

FUNCTIONAL BLOCK DIAGRAM

12-BIT

ADC

OUTPUT

REGISTER

SCLK

V

DD

SDATA

REF IN

AD7898

TRACK/HOLD

V

CONVST

PRODUCT HIGHLIGHTS

SIGNAL

IN

SCALING*

GND

*AD7898-10, AD7898-3

VDRIVE

1. Fast, 12-Bit ADC in 8-Lead Package

The AD7898 contains a 220 kSPS ADC, a track/hold amplifier, control logic, and a high speed serial interface, all in an

8-lead package. This offers considerable space saving over

alternative solutions.

2. Low Power, Single-Supply Operation

The AD7898 operates from a single 5 V supply and consumes only 22.5 mW. The V

function allows the serial

DRIVE

interface to connect directly to either 3 V or 5 V processor

systems independent of V

DD

.

3. Flexible, High Speed Serial Interface

The part provides a flexible, high speed serial interface that

has two distinct modes of operation. Mode 0 provides a threewire interface with data being accessed from the AD7898

when conversion is complete. Mode 1 offers a three-wire

interface with data being accessed during conversion.

4. Power-Down Mode

The AD7898 offers a proprietary power-down capability

when operated in Mode 1, making the part ideal for portable

or hand-held applications.

*

*Protected by U.S. Patent No. 6,681,332

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

(VDD = 4.75 V to 5.25 V, V

1

AD7898–SPECIFICATIONS

to both Mode 0 and Mode 1 operations; TA = T

Parameter A Version

DYNAMIC PERFORMANCE

Signal to (Noise + Distortion) Ratio

T

to T

MIN

MAX

Total Harmonic Distortion (THD)

Peak Harmonic or Spurious Noise

Intermodulation Distortion (IMD)

2

2

2

2

71 dB min fIN = 30 kHz Sine Wave

–78 dB max fIN = 30 kHz Sine Wave

–89 dB typ fIN = 30 kHz Sine Wave

l

Unit Test Conditions/Comments

= 2.7 V to 5.25 V; REF IN = 2.5 V. Specifications apply

DRIVE

to T

MIN

, unless otherwise noted.)

MAX

fa = 29.1 kHz, fb = 29.9 kHz

2nd Order Terms –88 dB typ

3rd Order Terms –88 dB typ

Aperture Delay 20 ns typ

Aperture Jitter 75 ps typ

Full Power Bandwidth–AD7898-10 3.6 MHz typ @ 3 dB

Full Power Bandwidth–AD7898-3 4.7 MHz typ @ 3 dB

Full Power Bandwidth–AD7898-10 2.15 MHz typ @ 1 dB

Full Power Bandwidth–AD7898-3 2.4 MHz typ @ 1 dB

DC ACCURACY

Resolution 12 Bits

Minimum Resolution for Which 12 Bits

No Missing Codes are Guaranteed

Relative Accuracy

Differential Nonlinearity

Positive Full-Scale Error

Negative Full-Scale Error

2

2

2

2

± 1 LSB max

± 0.9 LSB max

± 3 LSB max

± 3 LSB max

Bipolar Zero Error ± 4 LSB max

ANALOG INPUT

AD7898-10

Input Voltage Range ± 10 Volts

Input Resistance 24 kΩ min

AD7898-3

Input Voltage Range ± 2.5 Volts

Input Resistance 5 kΩ min

REFERENCE INPUT

REF IN Input Voltage Range 2.375/2.625 V min/V max 2.5 V ± 5%

Input Current 1 µA max

Input Capacitance

2, 3

10 pF max

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, I

Input Capacitance, C

INL

IN

IN

INH

2, 3

4

V

× 0.7 V min

DRIVE

V

× 0.3 V max

DRIVE

± 1 µA max Typically 10 nA, VIN = 0 V or V

10 pF max

DRIVE

LOGIC OUTPUTS

Output High Voltage, V

Output Low Voltage, V

Floating-State Leakage Current ±10 µA max

Floating-State Output Capacitance

OH

OL

2, 3

V

– 0.4 V min I

DRIVE

0.4 V max I

10 pF max

SOURCE

= 200 µA

SINK

= 200 µA; V

= 2.7 V to 5.25 V

DRIVE

Output Coding Twos Complement

CONVERSION RATE

Mode 0 Operation 220 kSPS max With V

215 kSPS max With V

= 5 V ± 5%

DRIVE

= 2.7 V to 3.6 V

DRIVE

Mode 1 Operation 220 kSPS max

POWER REQUIREMENTS

V

DD

V

DRIVE

I

Static 4.25 mA max Digital Inputs @ V

DD

IDD Operational 4.5 mA max Digital Inputs @ V

4.75 to 5.25 V min to V max For Specified Performance

2.7 to 5.25 V min to V max For Specified Performance

DRIVE

DRIVE

Power Dissipation 22.5 mW max

POWER-DOWN MODE

IDD @ 25°C5µA max Digital Inputs @ GND, VDD = 5 V ± 5%

T

MIN

to T

MAX

20 µA max Digital Inputs @ GND, VDD = 5 V ± 5%

Power Dissipation @ 25°C (Operational) 25 µW max VDD = 5 V

NOTES

1

Temperature ranges are as follows: A Version: –40°C to +85°C.

2

See Terminology.

3

Sample tested @ 25°C to ensure compliance.

4

Operational with V

Specifications subject to change without notice.

= 2.35 V, with Input Low Voltage, V

DRIVE

= 0.4 V

INL

–2– REV. A

AD7898

TIMING SPECIFICATIONS

Parameter Limit at T

MIN

(VDD = 4.75 V to 5.25 V; V

1

noted.)

, T

Unit Description

MAX

= 2.7 V to 5.25 V; REF IN = 2.5 V; TA = T

DRIVE

MIN

to T

, unless otherwise

MAX

Mode 0 Operation

t

1

t

2

t

3

t

4

t

4

t

5

t

6

t

CONVERT

Mode 1 Operation

5

f

SCLK

40 ns min CONVST Pulse Width

2

26

2

26

2

30

2

30

3

60

3

70

20 ns min Data Hold Time after Falling Edge of SCLK

4

50

ns min SCLK High Pulse Width, V

ns min SCLK Low Pulse Width, V

ns min SCLK High Pulse Width V

ns min SCLK Low Pulse Width V

= 5 V ± 5%

DRIVE

= 5 V ± 5%

DRIVE

= 2.7 V to 3.6 V

DRIVE

= 2.7 V to 3.6 V

DRIVE

ns max Data Access Time after Falling Edge of SCLK, V

ns max Data Access Time after Falling Edge of SCLK, V

ns max Bus Relinquish Time after Falling Edge of SCLK

3.3 µs

1kHz min

= 5 V ± 5%

DRIVE

= 2.7 V to 3.6 V

DRIVE

3.7 MHz max

t

CONVERT

t

QUIET

t

2

3

t

3

3

t

4

t

5

t

6

t

7

4

t

8

16 × t

SCLK

4.33 µs max f

100 ns min Minimum Quiet Time Required between Conversions

70 ns min CS to SCLK Setup Time

40 ns max Delay from CS Until SDATA Three-State Disabled

80 ns max Data Access Time after SCLK Falling Edge

108 ns min SCLK High Pulse Width

108 ns min SCLK Low Pulse Width

60 ns min SCLK to Data Valid Hold Time

20 ns min SCLK Falling Edge to SDATA High Impedance

t

= 1/f

SCLK

= 3.7 MHz

SCLK

SCLK

60 ns max SCLK Falling Edge to SDATA High Impedance

t

POWER-UP

NOTES

1

Sample tested at 25°C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of VDD) and timed from a voltage level of 1.6 V.

2

The SCLK maximum frequency is 15 MHz for Mode 0 operation for 220 kSPS throughput with V

The mark/space ratio for SCLK is specified for at least 40% high time (with corresponding 60% low time) or 40% low time (with corresponding 60% high time). As

the SCLK frequency is reduced, the mark/space ratio may vary, provided limits are not exceeded. Care must be taken when interfacing to account for the data access

time, t4, and the set-up time required for the users processor. These two times will determine the maximum SCLK frequency that the user’s system can operate with.

See Serial Interface section.

3

Measured with the load circuit of Figure 1 and defined as the time required for the output to cross 0.8 V or 2.0 V.

4

t6 and t8 are derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, t

relinquish time of the part and is independent of the bus loading.

5

Mark/Space ratio for the SCLK input is 40/60 to 60/40.

Specifications subject to change without notice.

4.33 µs max Power-Up Time from Power-Down Mode

= 5 V ± 5%, SCLK = 13 MHz with V

DRIVE

and t8, quoted in the timing characteristics is the true bus

6

= 2.7 V to 3.6 V.

DRIVE

–3–REV. A

AD7898

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C unless otherwise noted)

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

Analog Input Voltage to GND

AD7898-10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±17 V

AD7898-3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10 V

Reference Input Voltage to GND . . . . –0.3 V to V

+ 0.3 V

DD

Digital Input Voltage to GND . . . . . . . –0.3 V to VDD + 0.3 V

Digital Output Voltage to GND . . . . . –0.3 V to V

+ 0.3 V

DD

Operating Temperature Range

Commercial (A, B Versions) . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

SOIC Package, Power Dissipation . . . . . . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . 170°C/W

θ

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . 215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C

ESD

AD7898-10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.5 kV

AD7898-3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 kV

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating; functional operation of the device

at these or any other conditions above those listed in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

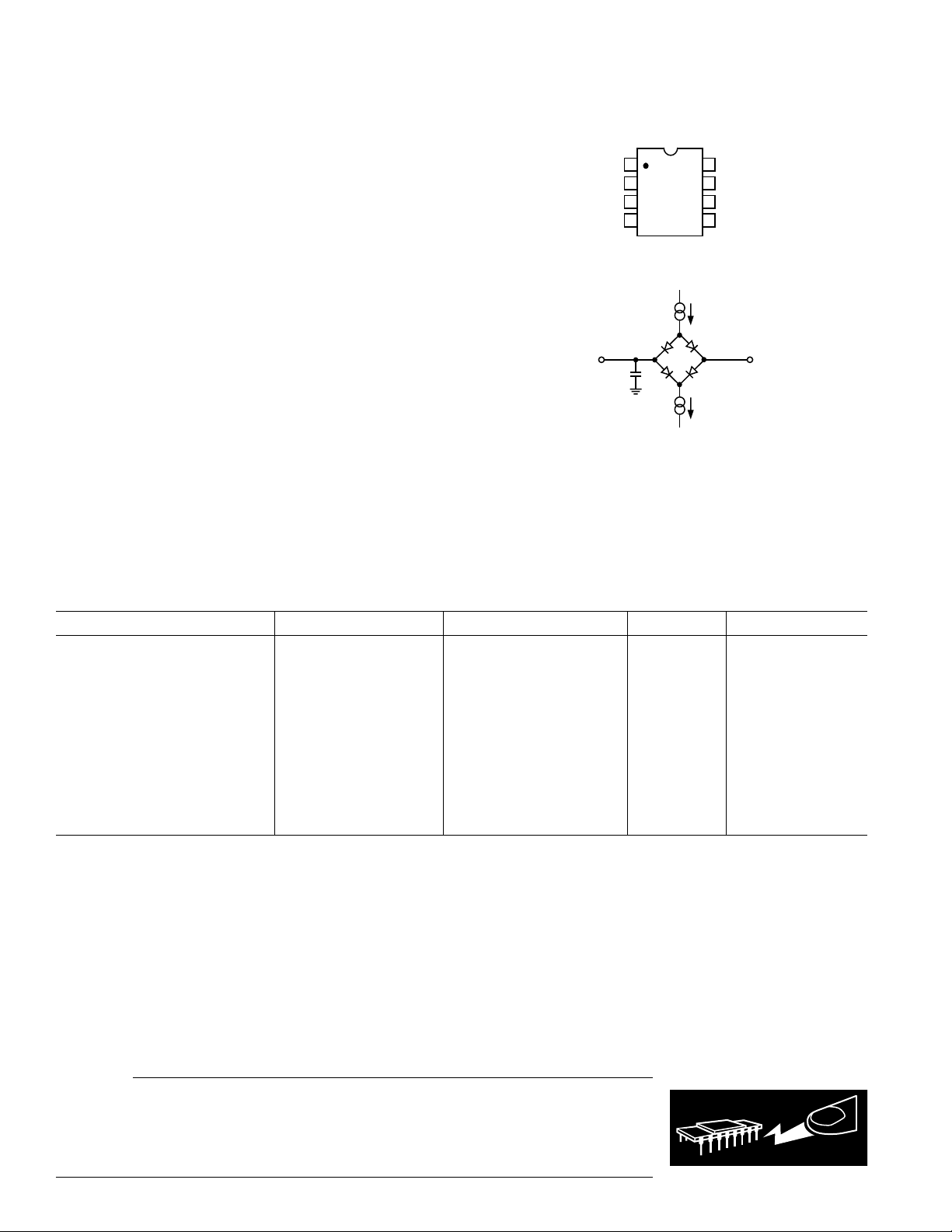

PIN CONFIGURATION

8

V

7

CS / CONVST

6

V

5

SDATA

I

OL

I

OH

DD

DRIVE

1.6V

OUTPUT

PIN

REF IN

TO

V

GND

SCLK

50pF

1

2

IN

3

4

C

L

AD7898

TOP VIEW

(Not to Scale)

200A

200A

Figure 1. Load Circuit for Digital Output Timing

Specifications

ORDERING GUIDE

Model Temperature Range Linearity Error

1

SNR Package Option

AD7898AR-10 –40°C to +85°C ± 1 LSB 71 dB R-8

AD7898AR-10REEL –40°C to +85°C ± 1 LSB 71 dB R-8

AD7898AR-10REEL7 –40°C to +85°C ± 1 LSB 71 dB R-8

AD7898ARZ-10

AD7898ARZ-10REEL

AD7898ARZ-10REEL7

3

3

3

–40°C to +85°C ± 1 LSB 71 dB R-8

–40°C to +85°C ± 1 LSB 71 dB R-8

–40°C to +85°C ± 1 LSB 71 dB R-8

AD7898AR-3 –40°C to +85°C ± 1 LSB 71 dB R-8

AD7898AR-3REEL –40°C to +85°C ± 1 LSB 71 dB R-8

AD7898AR-3REEL7 –40°C to +85°C ± 1 LSB 71 dB R-8

EVAL-AD7898CB

EVAL-CONTROL BRD2

NOTES

1

Linearity Error refers to integral linearity error.

2

R = SOIC.

3

Z = Pb-Free part.

4

This board is a complete unit allowing a PC to control and communicate with all Analog Devices evaluation boards ending in the CB designators.

4

2

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7898 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

–4– REV. A

WARNING!

ESD SENSITIVE DEVICE

AD7898

PIN FUNCTION DESCRIPTIONS

Pin Pin

No. Mnemonic Function

1 REF IN Voltage Reference Input. An external reference source should be connected to this pin to provide the

reference voltage for the AD7898’s conversion process. The REF IN input is buffered on-chip. The

nominal reference voltage for correct operation of the AD7898 is 2.5 V ± 5%. A 0.1 µF capacitor

should be placed on the REF IN pin.

2V

IN

3 GND Analog Ground. Ground reference for track/hold, comparator, digital circuitry, and DAC.

4 SCLK Serial Clock Input. An external serial clock is applied to this input to obtain serial data from the AD7898.

5 SDATA Serial Data Output. Serial data from the AD7898 is provided at this output. The serial data is clocked

6V

DRIVE

7 CS/CONVST Chip Select/Convert Start. This pin is CONVST, an edge-triggered logic input when in Mode 0 operation.

8V

DD

Analog Input Channel. The analog input range is ±10 V (AD7898-10) and ±2.5 V (AD7898-3).

When in Mode 0 operation, a new serial data bit is clocked out on the falling edge of this serial clock.

In Mode 0, data is guaranteed valid for 20 ns after this falling edge so that data can be accepted on the

falling edge when a fast serial clock is used. The serial clock input should be taken low at the end of

the serial data transmission. When in Mode 1 operation, SCLK also provides the serial clock for

accessing data from the part as in Mode 0, but this clock input is also used as the clock source for the

AD7898’s conversion process when in Mode 1.

out by the falling edge of SCLK, but the data can also be read on the falling edge of SCLK. This is

possible because data bit N is valid for a specified time after the falling edge of SCLK (data hold time).

Sixteen bits of serial data are provided with four leading zeros followed by the 12 bits of conversion data,

which is provided MSB first. On the 16th falling edge of SCLK, the SDATA line is held for the data

hold time and then is disabled (three-stated). Output data coding is two’s complement for the AD7898.

Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the serial interface of the AD7898 will operate.

On the falling edge of this input, the track/hold goes into its hold mode, and conversion is initiated.

When in Mode 1 operation, this pin is Chip Select, an active low logic input. This input provides the

dual function of initiating conversions on the AD7898 and also frames the serial data transfer.

Power Supply Input, 5 V ± 5%.

–5–REV. A

Loading...

Loading...