LC2MOS

a

12-Bit, 750 kHz/1 MHz, Sampling ADC

FEATURES

750 kHz/1 MHz Throughput Rate

1 ms/750 ns Conversion Time

12-Bit No Missed Codes Over Temperature

67 dB SNR at 100 kHz Input Frequency

Low Power—250 mW typ

Fast Bus Access Time—57 ns max

APPLICATIONS

Digital Signal Processing

Speech Recognition and Synthesis

Spectrum Analysis

DSP Servo Control

GENERAL DESCRIPTION

The AD7886 is a 12-bit ADC with a sample-and-hold amplifier

offering high speed performance combined with low power dissipation. The AD7886 is a triple pass flash ADC that uses 15

comparators in a 4-bit flash technique to achieve 12-bit accuracy

in 1 µs/750 ns conversion time. An on-chip clock oscillator pro-

vides the appropriate timing for each of the three conversion

stages, eliminating the need for any external clocks. Acquisition

time of the sample-and-hold amplifier gives a resulting throughput rate of 750 kHz/1 MHz.*

The AD7886 operates from ±5 V power supplies. Pin-strappable

inputs offer a choice of three analog input ranges: 0 V to 5 V,

0 V to 10 V or ±5 V.

In addition to the traditional dc accuracy specifications such as

linearity, offset and full-scale errors, the AD7886 is also specified for dynamic performance parameters, including harmonic

distortion and signal-to-noise ratio.

The AD7886 has a high speed digital interface with three-state

data outputs. Conversion control is provided by a

put. Data access is controlled by

CS and RD inputs, standard

CONVST in-

microprocessor signals. The data access time of less than 57 ns

means that the AD7886 can interface directly to most modern

microprocessors, including DSP processors.

*Contact your local salesperson for further information on the 1 MHz

version.

AD7886

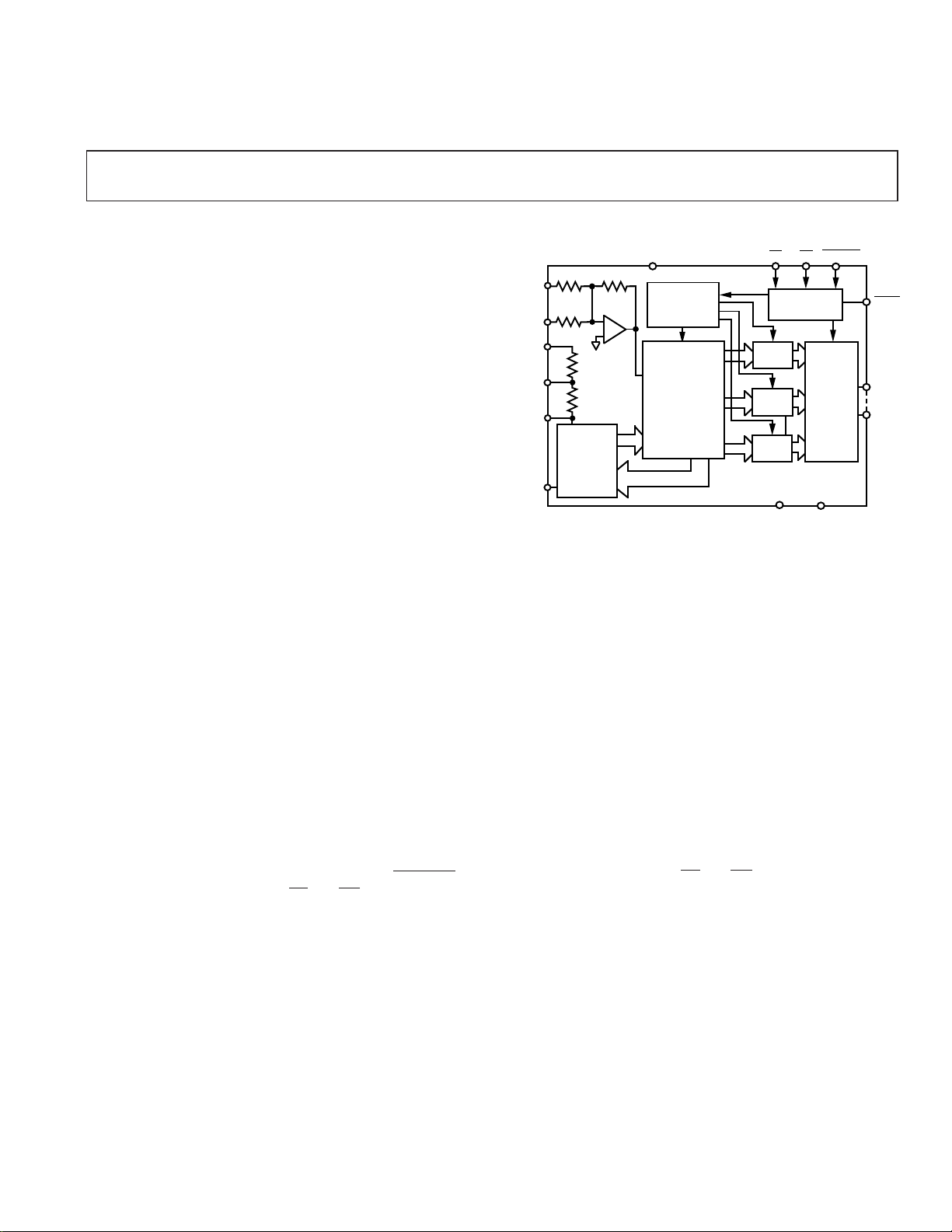

FUNCTIONAL BLOCK DIAGRAM

V

DD

R3

R4

R1

9k

R2

6.3k

4096

RESISTOR

DAC

R5

OSCILLATOR

–

+

AND TIMER

T/H

COMPARATORS

4-BIT FLASH

SEGMENT SELECT

CLOCK

15

AND

LOGIC

VIN1

VIN2

+5REF

SUM

V

REF

AGND

10k 3.5k

10k

The AD7886 is fabricated in Analog Devices’ Linear Compatible CMOS process, a mixed technology process that

combines precision bipolar circuits with low power CMOS

logic.

The AD7886 is available in both a 28-pin DIP and a 28-pin

leaded chip carrier.

PRODUCT HIGHLIGHTS

1. Fast 1.33 µs/1 µs Throughput Time.

Fast throughput time makes the AD7886 suitable for a

wide range of data acquisition applications.

2. Dynamic Specifications for DSP Users.

The AD7886 is specified for ac parameters, including

signal-to-noise ratio, harmonic distortion and intermodulation distortion. Key digital timing parameters are

also tested and guaranteed over the full operating temperature range.

3. Fast Microprocessor Interface.

Standard control signals,

CS and RD, and fast bus access times make the AD7886 easy to interface to microprocessors.

4. Low Power.

2

LC

MOS fabrication process gives low power dissipa-

tion of 250 mW.

CS RD CONVST

CONTROL

TIMER

4-BIT

LATCH

4-BIT

LATCH

4-BIT

LATCH

THREE

STATE

OUTPUTS

AD7886

V

DGND

SS

BUSY

DB11

DB0

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1997

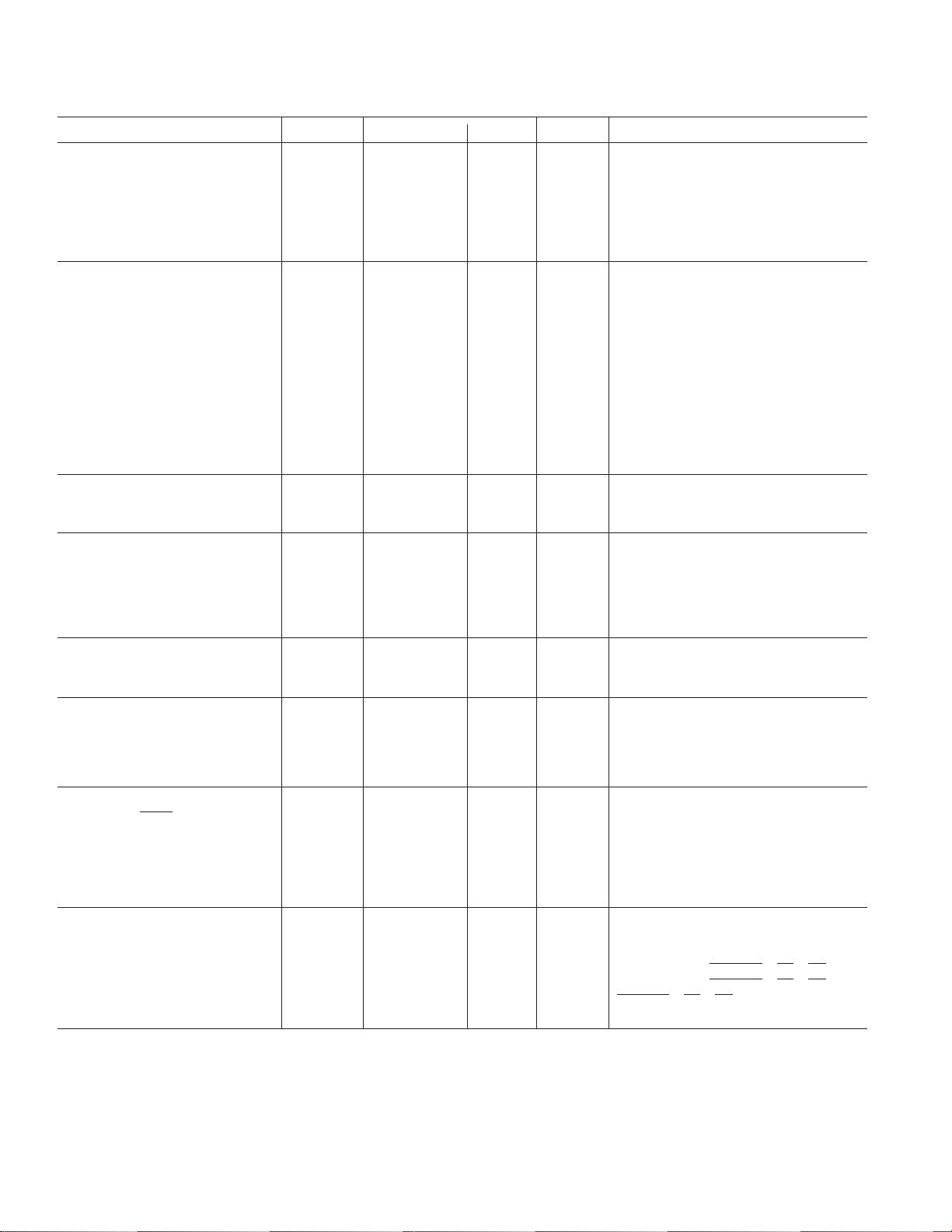

AD7886–SPECIFICATIONS

as shown in Figure 2. All Specifications T

MIN

to T

unless otherwise noted. Specifications apply for 750 kHz version.)

MAX

(VDD = +5 V 6 5%, VSS = –5 V 6 5%, A6ND = DGND = O V, V

= –3.5 V, connected

REF

Parameter J Version1K, B Versions1T Version1Units Test Conditions/Comments

DYNAMIC PERFORMANCE

Signal-to-Noise Ratio3 (SNR) 65 67 65 dB min VIN = 100 kHz Sine Wave, f

Total Harmonic Distortion (THD) –75 –75 –75 dB typ VIN = 100 kHz Sine Wave, f

Peak Harmonic or Spurious Noise –77 –77 –77 dB typ VIN = 100 kHz Sine Wave, f

2

SAMPLE

SAMPLE

SAMPLE

Intermodulation Distortion (IMD)

Second Order Terms –80 –80 –80 dB typ fa = 96 kHz, fb = 103 kHz, f

SAMPLE

= 750 kHz

Third Order Terms –80 –80 –80 dB typ

ACCURACY

Resolution 12 12 12 Bits

Integral Linearity T

MIN

to T

MAX

±2 ±2 LSB max

Minimum Resolution for Which

No Missing Codes Are Guaranteed 12 12 12 Bits

Unipolar Offset Error @ +25°C ±5 ±5 ±5 LSB max Input Range: 0 V to 5 V or 0 V to 10 V

T

MIN

to T

MAX

±5 ±5 ±5 LSB max

Bipolar Offset Error @ +25°C ±5 ±5 ±5 LSB max Input Range: ± 5 V

T

MIN

to T

MAX

±5 ±5 ±5 LSB max

Unipolar Gain Error @ +25°C ±5 ±5 ±5 LSB max Input Range: 0 V to 5 V or 0 V to 10 V

T

MIN

to T

MAX

±5 ±5 ±5 LSB max

Bipolar Gain Error @ +25°C ±5 ±5 ±5 LSB max Input Range: ± 5 V

T

MIN

to T

MAX

±5+5 ±5 LSB max

ANALOG INPUT

Unipolar Input Current 1.5 1.5 1.5 mA max Input Ranges: 0 V to 5 V or 0 V to 10 V

Bipolar Input Current ±0.75 ±0.75 ±0.75 mA max Input Range: ±5 V

= 750 kHz

= 750 kHz

= 750 kHz

REFERENCE INPUT

V

REF

–3.5 –3.5 –3.5 Volts ± 2% For Specified Performance

Input Reference Current –10 –10 –10 mA max

R1, Resistance 9 9 9 kΩ nom ±25%

R2, Resistance 6.3 6.3 6.3 kΩ nom ±25%

R2/R1 Ratio 0.7 0.7 0.7 nom ±0.1%

POWER SUPPLY REJECTION

VDD Only, (FS Change) 0.5 0.5 0.5 LSB typ VSS = –5 V, VDD = +4.75 V to +5.25 V

VSS Only, (FS Change) 0.5 0.5 0.5 LSB typ VDD = +5 V, VSS = –4.75 V to –5.25 V

LOGIC INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, I

Input Capacitance, C

INH

INL

IN

4

IN

LOGIC OUTPUTS

DB11–DB0, BUSY

Output High Voltage, V

Output Low Voltage, V

OH

OL

DB11–DB0

Floating-State Leakage Current ±10 ±10 ±10 pA max

Floating-State Output Capacitance415 15 15 pF max

POWER REQUIREMENTS

V

DD

V

SS

I

DD

I

SS

Power Dissipation 250 250 250 mW typ CONVST = CS = RD = V

NOTES

I

Temperature ranges are as follows: J, K Versions: 0°C to +70°C; B Version: –40°C to +85°C; T Version: –55°C to + 125°C.

2

Applies to all three input ranges, VIN = 0 to FS, pk-to-pk V.

3

SNR calculation includes distortion and noise components.

4

Sample tested @ +25°C to ensure compliance.

Specifications subject to change without notice.

2.4 2.4 2.4 V min VDD = 5 V ± 5%

0.8 0.8 0.8 V max VDD = 5 V ± 5%

±10 ±10 ±10 µA max VIN = 0 V to V

DD

10 10 10 pF max

4 4 4 V min I

0.4 0.4 0.4 V max I

SOURCE

= 1.6 mA

SINK

= 200 µA

+5 +5 +5 V nom ±5% for Specified Performance

–5 –5 –5 V nom ±5% for Specified Performance

35 35 35 mA max Typically 25 mA, CONVST = CS = RD = V

–35 –35 –35 mA max Typically 25 mA, CONVST = CS = RD = V

350 350 350 mW max

DD

DD

DD

–2–

REV. B

1

WARNING!

ESD SENSITIVE DEVICE

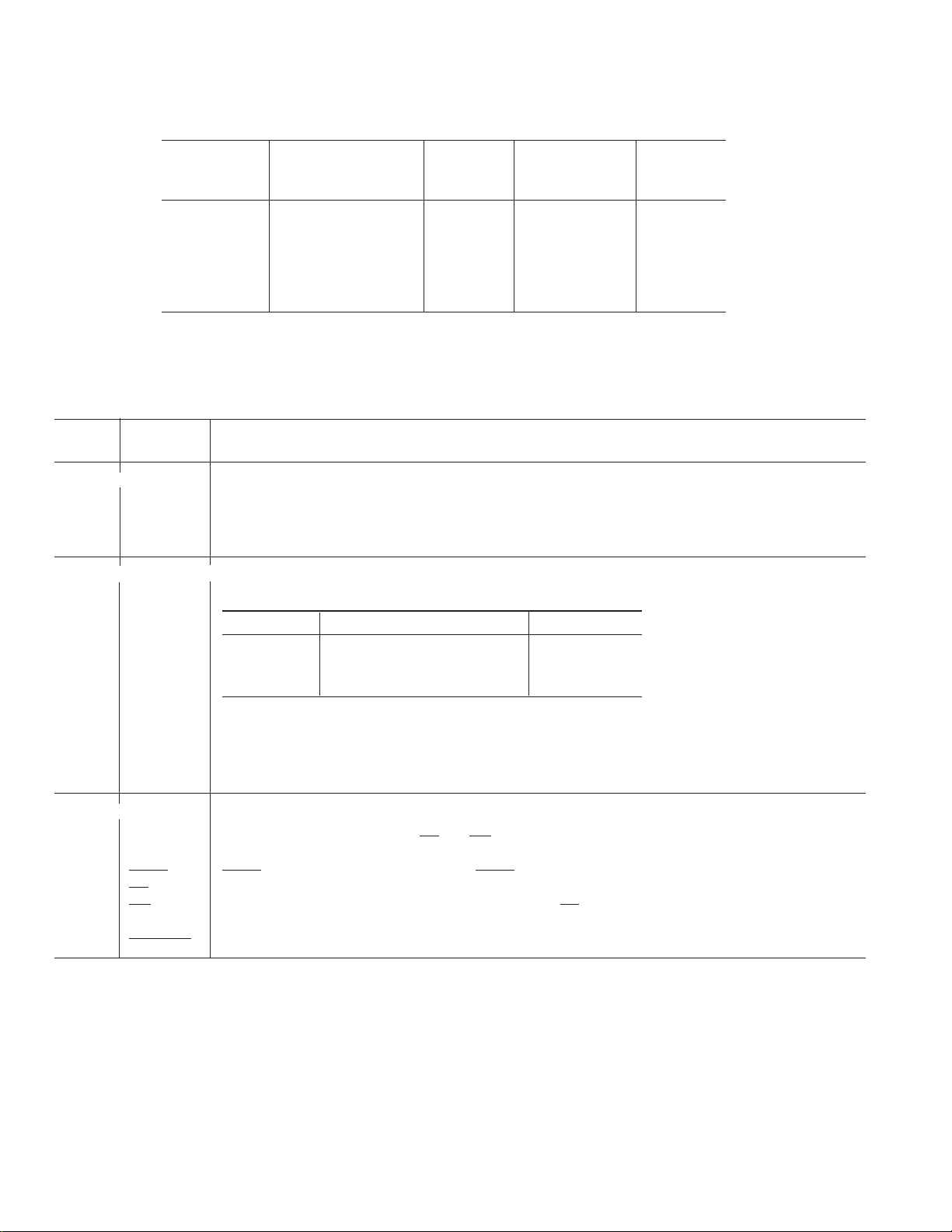

TIMING CHARACTERISTICS

(VDD = +5 V 6 5%, VSS = –5 V 6 5%, AGND = DGND = 0 V)

Limit at Limit at Limit at

T

MIN

, T

MAX

T

MIN

, T

MAX

T

, T

MIN

MAX

Parameter (J, K Versions) (B Version) (T Version) Units Conditions/Comments

AD7886

t

1

50 50 50 ns min CONVST Pulse Width

1 1 1 Fs max

t

2

t

3

t

4

t

5

t

6

3

t

7

0 0 0 ns min CS to RD Setup Time

0 0 0 ns min CS to RD Hold Time

60 60 75 ns min RD Pulse Width

100 100 100 ns max CONVST to BUSY Propagation Delay, (CL = 10 pF)

57 57 70 ns max Data Access Time After RD

10 10 10 ns min Bus Relinquish Time After RD

50 50 60 ns max

t

8

3

t

9

20 20 14 ns min Data Setup Time Prior to BUSY, (CL = 20 pF)

10 10 0 ns min Data Setup Time Prior to

BUSY, (CL = 100 pF)

10 10 10 ns min Bus Relinquish Time After CONVST

100 100 100 ns max

t

10

t

11

t

12

t

13

t

CONV

0 0 0 ns min CS High to CONVST Low

0 0 0 ns min BUSY High to RD Low

250 250 250 ns typ BUSY High to CONVST Low, SHA Acquisition Time

1.333 1.333 1.333 µs min Sampling Interval

950 950 950 ns typ Conversion Time

1000 1000 1000 ns max

NOTES

1

Timing specifications in bold print are 100% production tested. All other times are sample tested at +25°C to ensure compliance. All input signals are specified with tr =

tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

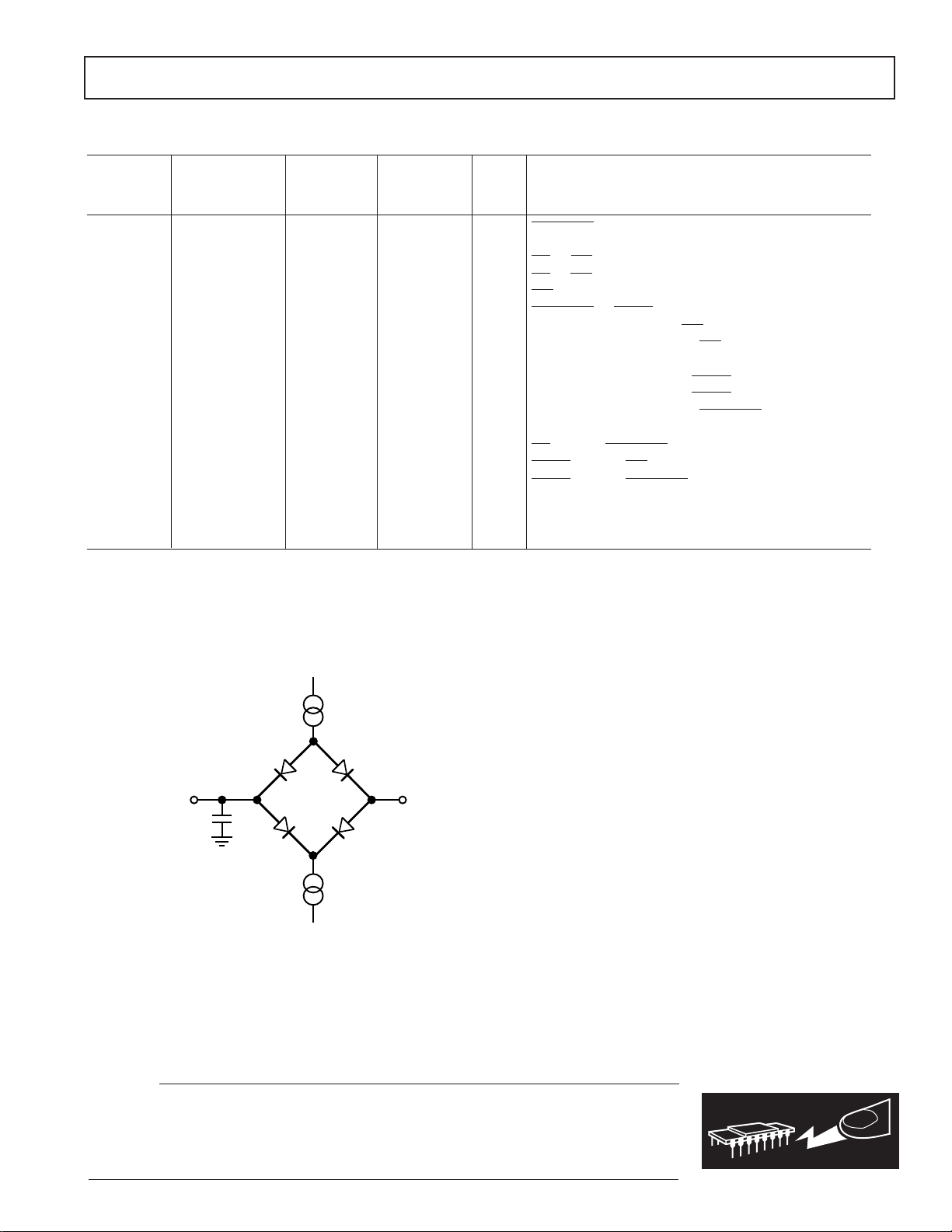

2

t6 is measured with the load circuit of Figure 1 and defined as the time required for an output to cross 0.8 V or 2.4 V.

3

t7 and t9 are derived from the measured time taken by the data outputs to change by 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the load capacitor, C

relinquish times of the part and as such are independent of external bus loading capacitances.

Specifications subject to change without notice.

. This means that the times, t7 and t9, quoted in the timing characteristics are the true bus

L

Figure 1. Load Circuit for Bus Access and Relinquish Time

ABSOLUTE MAXIMUM RATINGS

(T

V

DD

V

SS

AGND to DGND . . . . . . . . . . . . . . . . . –0.3 V to V

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7886 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. B

I

OL

TO OUTPUT

PIN

= +25°C unless otherwise noted)

A

C

L

1, 2

I

OH

+2.1V

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V to –7 V

+0.3 V

DD

VIN1, VIN2, SUM, +5REF to AGND . . . . . . –15 V to +15 V

V

to AGND . . . . . . . . . . . . . . . . VSS –0.3 V to V

REF

DD

+0.3 V

Digital Inputs to DGND

CS, RD, CONVST . . . . . . . . . . . . . . –0.3 V to V

+0.3 V

DD

Digital Outputs to DGND

DB0 to DB11, BUSY . . . . . . . . . . . . . –0.3 V to V

+0.3 V

DD

Operating Temperature Range

Commercial (J, K Versions) . . . . . . . . . . . . . . 0°C to +70°C

Industrial (B Version) . . . . . . . . . . . . . . . . –40°C to +85°C

Extended (T Version) . . . . . . . . . . . . . . . –55°C to +125°C

Storage Temperature Range . . . . . . . . . . . .–65°C to + 150°C

Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . .+300°C

Power Dissipation (Any Package) to +75°C . . . . . . 1000 mW

Derates above +75°C by . . . . . . . . . . . . . . . . . . . . 10 mW/°C

NOTES

1

Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

If VSS is open circuited with VDD and AGND applied, the VSS pin will be pulled

positive, exceeding the Absolute Maximum Ratings. If this possibility exists, a

Schottky diode from VSS to DGND (cathode end to GND) ensures that the

–3–

AD7886

ORDERING GUIDE

Integral

1, 2

Model

AD7886JD 0°C to +70°C 65 D-28

AD7886KD 0°C to +70°C67±2.0 D-28

AD7886JP 0°C to +70°C 65 P-28A

AD7886KP 0°C to +70°C67±2.0 P-28A

AD7886BD –40°C to +85°C67 ±2.0 D-28

AD7886TD –55°C to +125°C65 ±2.0 D-28

NOTES

1Contact your sales office for availability of AD7886BD, AD7886TD and 1 MHz version.

2

Analog Devices reserves the right to ship J-Leaded Ceramic Chip Carrier (JLCCC) in lieu of PLCC packages.

3

D = Ceramic DIP; P = Plastic Leaded Chip Carrier.

DIP Pin

Number Mnemonic Description

Power Supply

10 & 19 V

15 & 24 V

DD

SS

Positive Power Supply, +5 V ± 5%. Both V

Negative Power Supply, –5 V ± 5%. Both V

16 & 23 AGND Analog Ground. Both AGND pins must be tied together.

5 DGND Digital Ground.

Temperature SNR Nonlinearity Package

Range (dBs) (LSBs) Option

PIN FUNCTION DESCRIPTION

pins must be tied together.

DD

pins must be tied together.

SS

3

2

2

Analog and Reference Inputs

17 & 18 VIN Analog Inputs, VIN1 and VIN2. The part can be pin strapped for any one of three analog input ranges;

Range Pin Strap Signal Input

0 V to 5 V Connect VIN2 to VIN1 VIN1 & VIN2

0 V to 10 V Connect VIN2 to GND VIN1

±5 V Connect VIN2 to +5 V VIN1

20 +5REF +5 V Reference input. This input is used in conjunction with SUM and V

inputs to scale an external

REF

+5 V reference to –3.5 V, the required reference for the part (see Figure 2).

21 SUM Summing Point. This input is used in conjunction with +5REF and V

inputs to scale an external

REF

+5 V reference to –3.5 V, the required reference for the part (see Figure 2).

22 V

REF

Voltage Reference Input. The AD7886 is specified with V

REF

= –3.5 V.

Interface and Control

1–4, DB7–DB4 Three-state data outputs.

6–9, DB3–DB0 These outputs are controlled by

CS and RD. DB11 is the Most Significant Bit (MSB).

25–28 DB11–DB8

11

12

13

BUSY BUSY Output indicates converter status. BUSY is low during conversion.

CS Chip Select Input. The device is selected when this input is low.

RD Read Input. This active low signal, in conjunction with CS, is used to enable the output data three-state

drivers.

14 CONVST Conversion Start Input. This input is used to start conversion.

–4–

REV. B

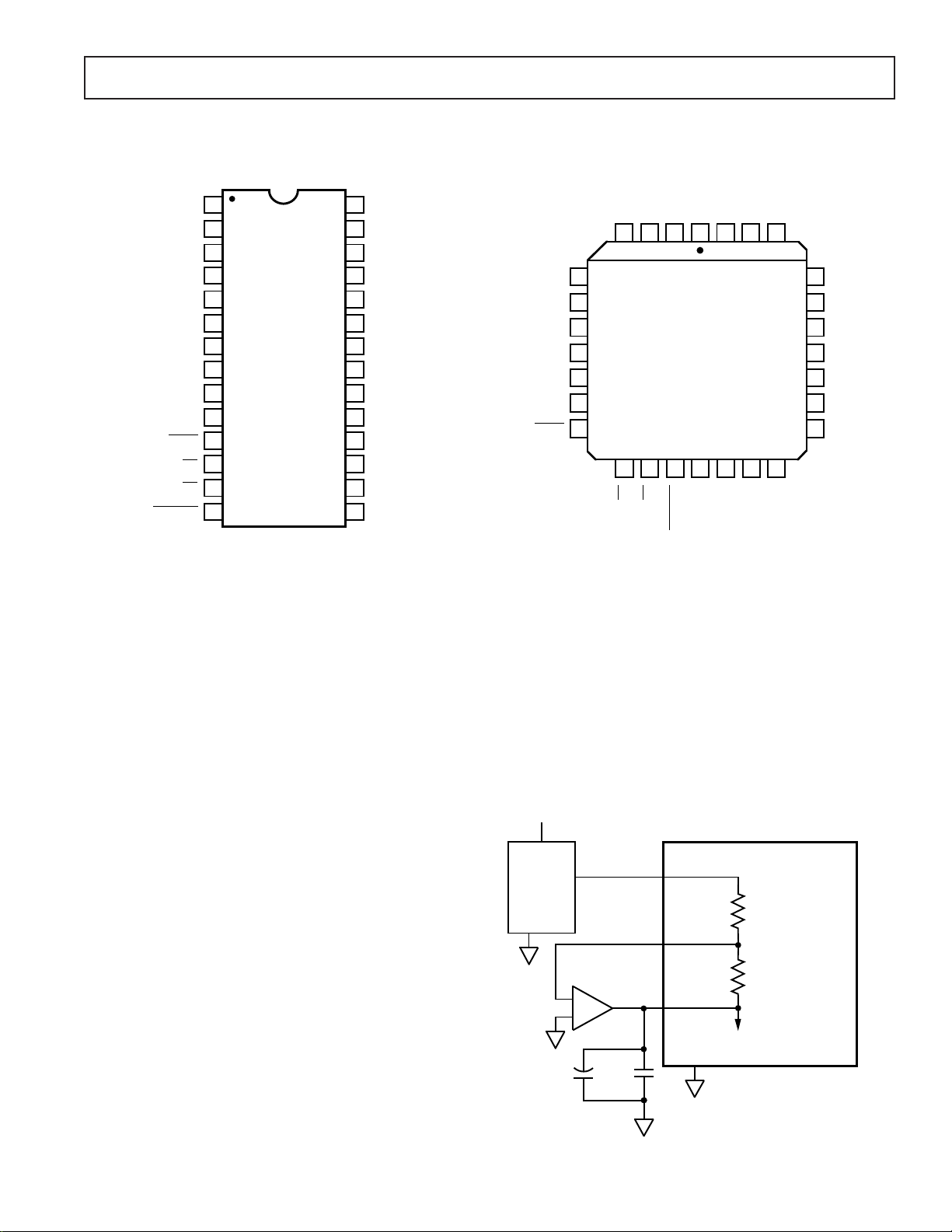

PIN CONFIGURATIONS

AGND

VIN1

VIN2

DB4

DB5

DB6

DB11

DB10

DB9

DB8

DB7

AGND

SUM

+5REF

DB2

DB1

DB0

DGND

DB3

V

SS

V

REF

V

DD

CS

RD

CONVST

V

SS

V

DD

BUSY

AD7886

TOP VIEW

(Not to Scale)

5

6

7

8

9

10

11

28 27 2612

3

4

25

24

23

22

21

20

19

12

13 14 15 16 17 18

AD7886

DIP

DB7

DB6

DB5

DB4

DGND

DB3

DB2

DB1

DB0

V

DD

BUSY

CS

RD

CONVST

1

2

3

4

5

6

7

8

9

10

11

12

13

14

AD7886

TOP VIEW

(Not to Scale)

28

27

26

25

24

23

22

21

20

19

18

17

16

15

DB8

DB9

DB10

DB11

V

SS

AGND

V

REF

SUM

+5REF

V

DD

VIN2

VIN1

AGND

V

SS

TERMINOLOGY

Unipolar Offset Error

The ideal first code transition should occur when the analog

input is 1 LSB above AGND. The deviation of the actual transition from that point is termed the offset error.

Bipolar Zero Error

The ideal midscale transition (i.e., 0111 1111 1111 to 1000

0000 0000) for the +5 V range should occur when the analog

input is at zero volts. Bipolar zero error is the deviation of the

actual transition from that point.

Gain Error

In the unipolar mode, gain error is measured with respect to the

first and last code transition points. The ideal difference between these points is FS–2 LSBs. For bipolar applications, the

gain error is measured from the midscale transition to both the

first and last code transitions. The ideal difference in this case is

FS/2–1 LSB. The gain error is defined as the deviation between

the ideal difference, given above, and the measured difference.

For the bipolar case, there are two gain errors; the figure in the

specification page represents the worst case. Ideal FS depends

on the +5REF input; for the 0 V to 5 V input, ideal FS = +5REF

and for the 0 V to 10 V and +5 V ranges, ideal FS = 2 × + 5REF.

CONVERTER DETAILS

The AD7886 is a triple-pass flash ADC that uses 15 comparators in a 4-bit flash technique to perform the 12-bit conversion

procedure. Each of the 4096 quantization levels is realized internally with a precision resistor DAC.

The fifteen comparators first compare the analog input voltage

to the V

four most significant bits and selects 1 out of 16 voltage segments. The comparators are then switched to 15 subvoltages on

that segment to determine the next four bits and select 1 out of

/16 voltages of the resistor array. This determines the

REF

256 voltage segments. A further switching of the comparators to

another 15 subvoltages produces the complete 12-bit conversion

REV. B

PLCC

result. The 12 bits of data are then stored internally in a threestate output latch.

REFERENCE INPUT

The AD7886 operates from a 3.5 V reference, which must be

provided at the V

input. Two on-chip resistors for use with

REF

an external amplifier can be used for deriving 3.5 V from standard 5 V references. Figure 2 shows an example with the AD586

which a is a high performance voltage reference exhibiting

excellent stability performance, 5 ppm/°C max. The external

amplifier serves a second function of force/sensing the V

REF

input. Force/sensing minimizes error contributions from

+V

+V

AD586

GND

IN

+5V

V

OUT

AD707

–

–3.5V

+5REF

SUM

V

REF

R1

9k

R2

6.3k

AD7886*

+

TO DAC

C1

10µF

C2

0.1µF

AGND

*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 2. Typical Reference Circuitry

–5–

Loading...

Loading...