LC2MOS

a

FEATURES

Battery-Compatible Supply Voltage: Guaranteed Specs

for V

of 3 V to 3.6 V

DD

12-Bit Monolithic A/D Converter

50 kHz Throughput Rate

15 ms Conversion Time

5 ms On-Chip Track/Hold Amplifier

Low Power

Power Save Mode: 1 mW typ

Normal Operation: 8 mW typ

70 dB SNR

Small 24-Lead SOIC and 0.3" DIP Packages

APPLICATIONS

Battery Powered Portable Systems

Laptop Computers

GENERAL DESCRIPTION

The AD7883 is a high speed, low power, 12-bit A/D converter

which operates from a single +3 V to +3.6 V supply. It consists

of a 5 µs track/hold amplifier, a 15 µs successive-approximation

ADC, versatile interface logic and a multiple-input-range circuit.

The part also includes a power save feature.

Fast bus access times and standard control inputs ensure easy

interfacing to modern microprocessors and digital signal

processors.

The AD7883 features a total throughput time of 20 µs and can

convert full power signals up to 25 kHz with a sampling frequency of 50 kHz.

In addition to the traditional dc accuracy specifications such as

linearity, full-scale and offset errors, the AD7883 is also fully

specified for dynamic performance parameters including harmonic distortion and signal-to-noise ratio.

The AD7883 is fabricated in Analog Devices’ Linear Compatible CMOS (LC

that combines precision bipolar circuits with low power CMOS

logic. The part is available in a 24-pin, 0.3 inch-wide, plastic

dual-in-line package (DIP) as well as a small 24-lead SOIC

package.

2

MOS) process, a mixed technology process

12-Bit, 3.3 V Sampling ADC

AD7883

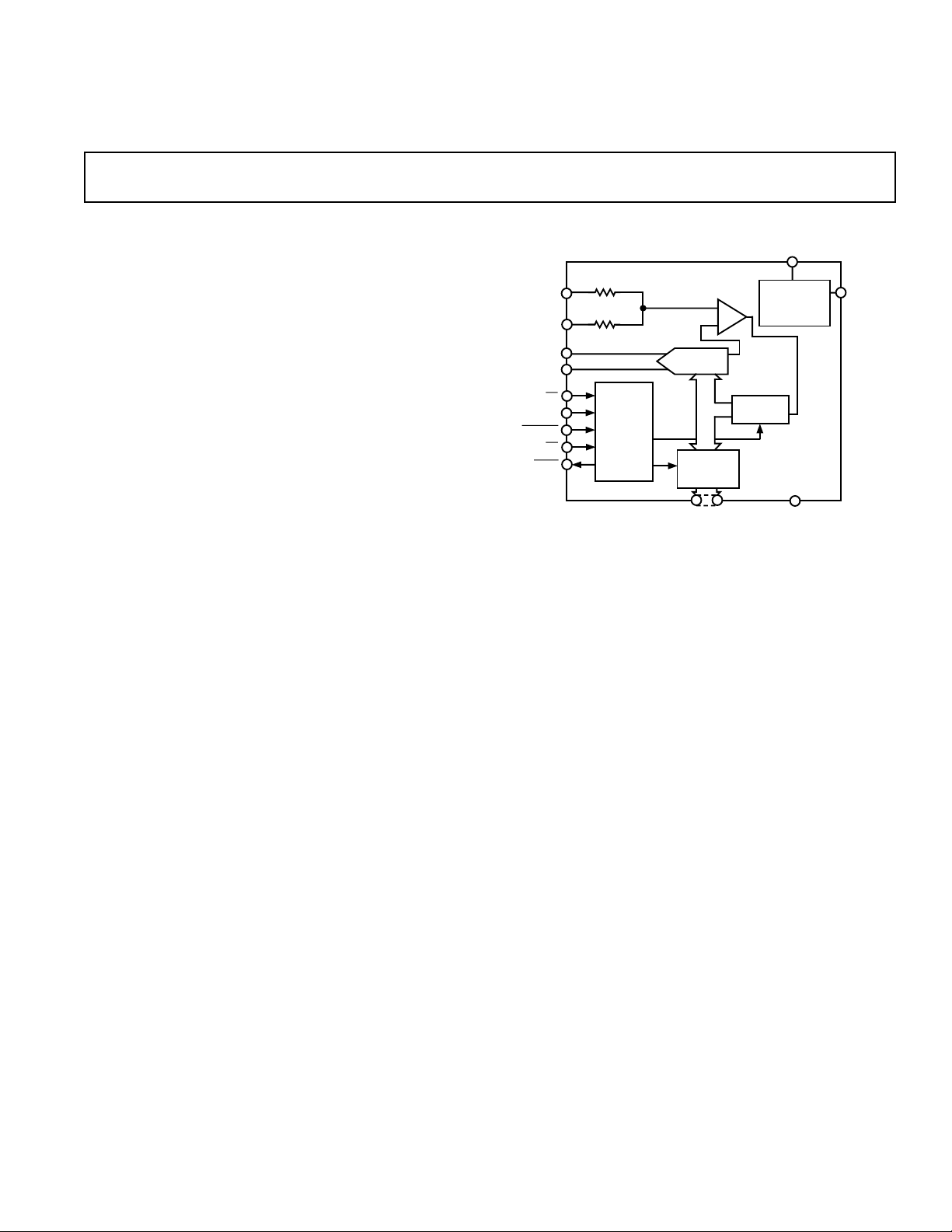

FUNCTIONAL BLOCK DIAGRAM

V

DD

V

INA

V

INB

V

REF

AGND

CS

CLKIN

CONVST

RD

BUSY

CONTROL

LOGIC

PRODUCT HIGHLIGHTS

1. 3 V Operation

The AD7883 is guaranteed and tested with a supply voltage

of 3 V to 3.6 V. This makes it ideal for battery-powered applications where 12-bit A/D conversion is required.

2. Fast Conversion Time

15 µs conversion time and 5 µs acquisition time allow for

large input signal bandwidth. This performance is ideally

suited for applications in areas such as telecommunications,

audio, sonar and radar signal processing.

3. Low Power Consumption

1 mW power consumption in the power-down mode makes

the part ideally suited for portable, hand held, battery powered applications.

SAMPLING

COMPARATOR

12-BIT DAC

THREE

STATE

BUFFERS

+

–

DB0DB11

LOW POWER

SAR +

COUNTER

CONTROL

CIRCUIT

AD7883

DGND

MODE

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD7883–SPECIFICATIONS

MODE = Logic High. All specifications T

MIN

to T

unless othewise noted.)

MAX

(VDD = +3 V to +3.6 V, V

= VDD, AGND = DGND = 0 V, f

REF

CLKIN

= 2 MHz,

Parameter B Versions1Units Test Conditions/Comments

DYNAMIC PERFORMANCE

2

Signal-to-Noise Ratio3 (SNR) 69 dB min Typically SNR Is 71 dB

Total Harmonic Distortion (THD) –80 dB typ V

Peak Harmonic or Spurious Noise –80 dB typ V

= 1 kHz Sine Wave, f

V

IN

= 1 kHz Sine Wave, f

IN

= 1 kHz, f

IN

SAMPLE

= 50 kHz

SAMPLE

SAMPLE

= 50 kHz

= 50 kHz

Intermodulation Distortion (IMD)

Second Order Terms –80 dB typ fa = 0.983 kHz, fb = 1.05 kHz, f

Third Order Terms –80 dB typ fa = 0.983 kHz, fb = 1.05 kHz, f

SAMPLE

SAMPLE

= 50 kHz

= 50 kHz

DC ACCURACY

Resolution 12 Bits All DC ACCURACY Specifications Apply for the Two

Analog Input Ranges

Integral Nonlinearity ± 2 LSB max

Differential Nonlinearity ± 1 LSB max Guaranteed Monotonic

Full-Scale Error ±20 LSB max

Bipolar Zero Error ±12 LSB max

Unipolar Offset Error ±3 LSB max

ANALOG INPUT

Input Voltage Ranges 0 to V

±V

REF

REF

Input Resistance 10 MΩ min 0 to V

5/12 kΩ min/max 8 kΩ typical: ±V

Volts See Figure 4

Volts See Figure 5

Range

REF

REF

Range

REFERENCE INPUT

(For Specified Performance) V

V

REF

I

REF

DD

1.2 mA max

V

LOGIC INPUTS

CONVST, RD, CS, CLKIN

Input High Voltage, V

Input Low Voltage, V

Input Current, I

IN

Input Capacitance, C

INH

INL

IN

4

2.1 V min

0.6 V max

±10 µA max VIN = 0 V or V

10 pF max

DD

MODE INPUT

Input High Voltage, V

Input Low Voltage, V

Input Current, I

IN

Input Capacitance, C

INH

INL

IN

4

VDD –0.2 V

0.2 V

±100 µA max VIN = 0 V or V

10 pF max

DD

LOGIC OUTPUTS

DB11–DB0,

Output High Voltage, V

Output Low Voltage, V

BUSY

OL

OH

2.4 V min I

0.4 V max I

SOURCE

= 0.8 mA

SINK

= 200 µA

DB11–DB0

Floating-State Leakage Current ±10 µA max

Floating-State Output Capacitance410 pF max

CONVERSION

Conversion Time 15 µs max f

CLKIN

= 2 MHz

Track/Hold Acquisition Time 5 µs max

POWER REQUIREMENTS

V

DD

I

DD

Normal Power Mode @ +25°C 3 mA max Typically 2 mA; MODE = V

T

to T

MIN

MAX

+3.3 V nom +3 V to +3.6 V for Specified Performance

4 mA max Typically 2.5 mA; MODE = V

DD

DD

Power Save Mode @ +25°C 400 µA max Logic Inputs @ 0 V or VDD; MODE = 0 V; Typically 250 µA

to T

T

MIN

MAX

800 µA max Logic Inputs @ 0 V or VDD; MODE = 0 V; Typically 300 µA

Power Dissipation

Normal Power Mode @ +25°C 11 mW max V

T

MIN

to T

MAX

15 mW max VDD = 3.6 V: Typically 9 mW; MODE = V

= 3.6 V: Typically 8 mW; MODE = V

DD

DD

DD

Power Save Mode @ +25°C 1.5 mW max VDD = 3.6 V: Typically 1 mW; MODE = 0 V

T

to T

MIN

NOTES

1

Temperature range is as follows: B Versions, –40°C to +85°C.

2

VIN = 0 to V

3

SNR calculation includes distortion and noise components.

4

Sample tested @ +25°C to ensure compliance.

Specifications subject to change without notice.

REF

MAX

.

3 mW max VDD = 3.6 V: Typically 1 mW; MODE = 0 V

REV. 0–2–

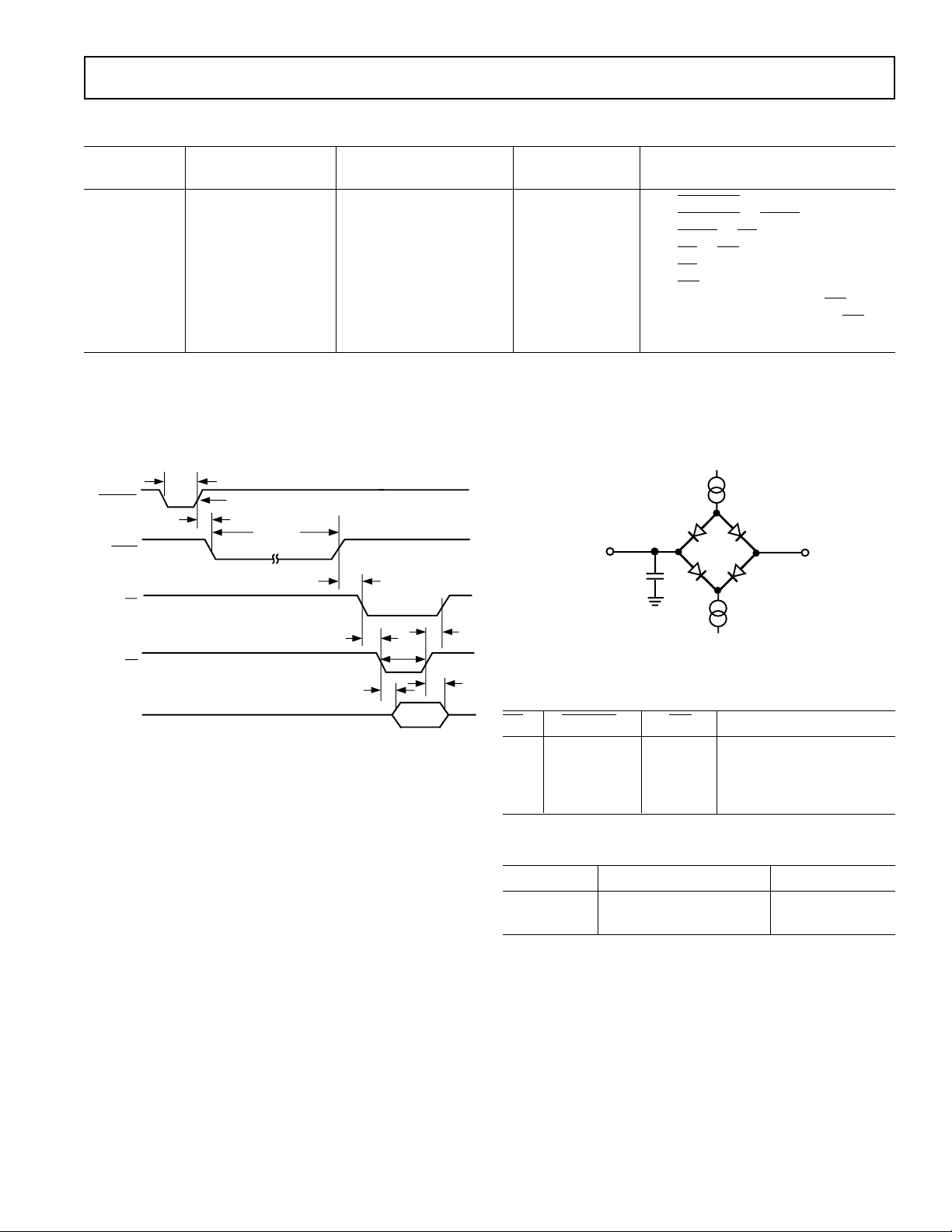

TIMING CHARACTERISTICS

1

(VSS = +3 V to +3.6 V, V

= VDD, AGND = DGND = 0 V)

REF

AD7883

Limit at +258C Limit at T

MIN

, T

MAX

Parameter (All Versions) (All Versions) Units Conditions/Comments

t

1

t

2

t

3

t

4

t

5

t

6

2

t

7

3

t

8

50 60 ns min CONVST Pulse Width

200 200 ns max CONVST to BUSY Falling Edge

0 0 ns min BUSY to CS Setup Time

0 0 ns min CS to RD Setup Time

0 0 ns min CS to RD Hold Time

110 150 ns min RD Pulse Width

100 140 ns max Data Access Time after RD

55 ns min Bus Relinquish Time after RD

90 90 ns max

NOTES

1

Timing specifications in bold print are 100% production tested. All other times are sample tested at +25 ° C to ensure compliance. All input signals are specified with

tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2

t7 is measured with the load circuit of Figure 2 and defined as the time required for an output to cross 0.8 V or 2.4 V.

3

t8 is derived from the measured time taken by the data outputs to change by 0.5 V when loaded with the circuit of Figure 2. The measured number is then extrapolated back to remove the effects of charging the 50 pF capacitor. This means that the time, t8, quoted in the timing characteristics is the true bus relinquish time of

the part and as such is independent of external bus loading capacitances.

t

CONVST

BUSY

CS

RD

DB0 – DB11

1

TRACK/HOLD

GOES INTO HOLD

t

2

t

CONVERT

THREE-STATE

TO

OUTPUT

PIN

t

3

t

t

4

t

5

t

6

t

DATA

VALID

8

7

Figure 2. Load Circuit for Access and Relinquish Time

CS CONVT RD Function

50pF

Table I. Truth Table

0.8mA

+1.6V

200µA

Figure 1. Timing Diagram

REV. 0 –3–

1 1 X Not Selected

1 j 1 Start Conversion g

0 1 0 Enable ADC Data

0 1 1 Data Bus Three Stated

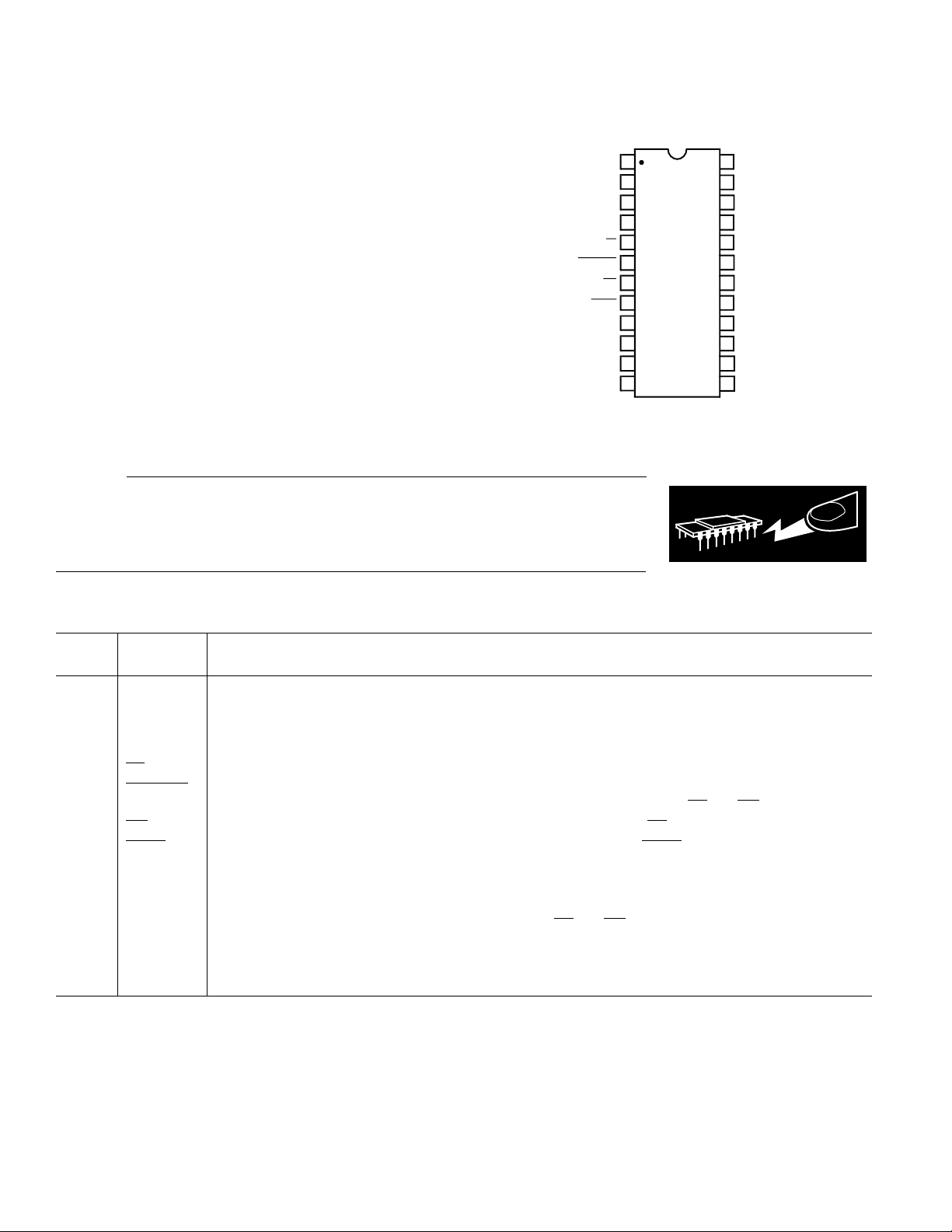

ORDERING GUIDE

Model Temperature Range Package Option*

AD7883BN –40°C to +85°C N-24

AD7883BR –40°C to +85°C R-24

*N = Plastic DIP; R = SOIC (Small Outline Integrated Circuit).

AD7883

TOP VIEW

(Not to Scale)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

24

23

22

21

20

19

18

17

16

15

AD7883

AGND

CLKIN

DGND

DB0

DB1

DB2

DB3

DB4

DB5

DB6

V

DD

DB8

V

INA

V

INB

DB7

DB9

DB10

DB11

MODE

CS

CONVST

RD

BUSY

V

REF

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

PIN CONFIGURATION

VDD to AGND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

to DGND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

V

DD

AGND to DGND . . . . . . . . . . . . . . . . –0.3 V to V

, V

V

INA

V

INA

V

REF

to AGND (Figure 4) . . . . . –0.3 V to VDD + 0.3 V

INB

to AGND (Figure 5) . . . . . . –VDD –0.3 V to V

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to V

+ 0.3 V

DD

+ 0.3 V

DD

DD

Digital Inputs to DGND . . . . . . . . . . . –0.3 V to VDD + 0.3 V

Digital Outputs to DGND . . . . . . . . . . –0.3 V to V

+ 0.3 V

DD

Operating Temperature Range

Industrial (B Version) . . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . .+300°C

Power Dissipation (Any Package) to +75°C . . . . . . . 450 mW

Derates above +75°C by . . . . . . . . . . . . . . . . . . . . 10 mW/°C

*Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those listed in the

operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7883 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

Pin Pin

No. Mnemonic Function

11V

12V

13 AGND Analog Ground.

14V

15 CS Chip Select. Active Low Logic input. The device is selected when this input is active.

16

17

18

19 CLKIN Clock Input. TTL-compatible logic input. Used as the clock source for the A/D converter. The mark/

10 DGND Digital Ground.

11 . . . 22 DB0–DB11 Three-State Data Outputs. These become active when

23 MODE MODE Input. This input is used to put the device into the power save mode (MODE = 0 V). During

24 V

INA

INB

REF

CONVST Convert Start. A low to high transition on this input puts the track/hold into hold mode and starts

RD Read. Active Low Logic Input. This input is used in conjunction with CS low to enable data outputs.

BUSY Active Low Logic Output. This status line indicates converter status. BUSY is low during conversion.

DD

PIN FUNCTION DESCRIPTION

Analog Input.

Analog Input.

Voltage Reference Input. This is normally tied to V

conversion. This input is asynchronous to the CLKIN and is independent of

DD.

CS and RD.

space ratio of the clock can vary from 40/60 to 60/40.

CS and RD are brought low.

normal operation, the MODE input will be a logic high (MODE = V

Power Supply. This is nominally +3.3 V.

–4–

DD

).

REV. 0

Loading...

Loading...